# Élan™SC310 Microcontroller Programmer's Reference Manual

**Rev. A, April 1996**

| ⊚ 1996 by Advanced Micro Devices, Inc.                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.                                                                                                                                                                                                                                                                                |

| This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.                                                                                                                                             |

| The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Trademarks  AMD, the AMD logo and combinations thereof are trademarks of Advanced Micro Devices, Inc.  Am386 and Am486 are registered trademarks, Élan and E86 are trademarks, and FusionE86 is a service mark of Advanced Micro Devices, Inc.  Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# **TABLE OF CONTENTS**

| Chapter 1 | INTRODUCTION  Purpose of this Manual |                |                                              |        |

|-----------|--------------------------------------|----------------|----------------------------------------------|--------|

| Chapter 2 | POV                                  | VER MA         | NAGEMENT                                     |        |

|           | 1.1                                  |                | Management Unit                              | 1-2    |

|           |                                      | 1.1.1          | Power-Management Modes                       |        |

|           |                                      | 1.1.2          | PMU Operating-Mode Transitions               |        |

|           |                                      | 1.1.3          | PMU Clock Sources                            |        |

|           |                                      | 1.1.4          | Reading the PMU Mode                         |        |

|           |                                      | 1.1.5          | Merging of PMU Modes                         |        |

|           |                                      | 1.1.6          | Programming Example: Power-Management Setup  |        |

|           |                                      | 1.1.7          | Programming Example: Peripheral-Device Power |        |

|           | 1.2                                  | Externa        | al-Device Control Interface                  |        |

|           |                                      | 1.2.1          | Power-Management Control Pins                |        |

|           |                                      | 1.2.2          | Programmable General-Purpose Pins 2 and 3    | . 1-15 |

|           |                                      | 1.2.3          | Latched Power Pin                            | . 1-15 |

|           | 1.3                                  | Clock-S        | Switching Logic                              | . 1-16 |

|           |                                      | 1.3.1          | CPU/Memory Clock Switching                   |        |

|           |                                      | 1.3.2          | Clock Startup and Shutdown Logic             |        |

|           | 1.4                                  | -              | Monitors                                     |        |

|           | 1.5                                  |                | ransition Timer                              |        |

|           | 1.6                                  |                | Jp Logic                                     |        |

|           | 1.7                                  |                | d NMI Control                                |        |

|           |                                      | 1.7.1          | Temporary-On Mode                            |        |

|           |                                      | 1.7.2          | Enabling SMIs                                |        |

|           |                                      | 1.7.3          | Processing NMI or SMI Source                 |        |

|           |                                      | 1.7.4<br>1.7.5 | Accesses to Powered-Down Device SMI          |        |

|           |                                      | 1.7.5          | Treatment of Pending SMIs                    |        |

|           |                                      | 1.7.0          | External SMI with a Single Device            |        |

|           |                                      | 1.7.7          | External SMI with Multiple Devices           |        |

|           | 1.8                                  |                | -Management Logic                            |        |

|           | 1.0                                  | 1.8.1          | Battery Level 1                              |        |

|           |                                      | 1.8.2          | Battery Level 2                              |        |

|           |                                      | 1.8.3          | Battery Level 3                              |        |

|           |                                      | 1.8.4          | Battery Level 4                              |        |

|           |                                      | 1.8.5          | AC Input Status Pin                          |        |

|           | 1.9                                  | Susper         | nd/Resume Pin Logic                          |        |

|           |                                      | 1.9.1          | Required Initialization                      | . 1-37 |

|           |                                      | 1.9.2          | Start of SMI Handler                         | . 1-37 |

|           |                                      | 1.9.3          | Suspend Input Caused the SMI                 |        |

|           |                                      | 1.9.4          | Suspend Pseudocode                           |        |

|           |                                      | 1.9.5          | Resume Input Caused the SMI                  |        |

|           |                                      | 1.9.6          | Resume Pseudocode                            |        |

|           |                                      | 1.9.7          | Things to Avoid                              | . 1-39 |

|           | 1.10           | Auto Lo                                                                                                                                                                                              | w-Speed Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 1-40                                                                                                                                 |

|-----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|           | 1.11           | Micro Po                                                                                                                                                                                             | ower-Off Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 1-40                                                                                                                                 |

|           | 1.12           | Other Po                                                                                                                                                                                             | ower-Saving Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 1-41                                                                                                                                 |

|           |                | 1.12.1                                                                                                                                                                                               | DMA Clock Stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

|           |                | 1.12.2                                                                                                                                                                                               | Data-Path Disabling Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|           |                | 1.12.3                                                                                                                                                                                               | Slow Refresh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                        |

|           |                | 1.12.4                                                                                                                                                                                               | Quiet Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|           |                |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                        |

| Chapter 3 | MEN            | ORY MA                                                                                                                                                                                               | ANAGEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|           | 2.1            | System                                                                                                                                                                                               | Memory: DRAM and Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 2-2                                                                                                                                  |

|           |                | 2.1.1                                                                                                                                                                                                | DRAM Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

|           |                | 2.1.2                                                                                                                                                                                                | Refresh and Wait States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

|           |                | 2.1.3                                                                                                                                                                                                | Maximum ISA and Local Bus Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

|           | 2.2            | ROM-BI                                                                                                                                                                                               | OS Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|           | 2.3            |                                                                                                                                                                                                      | OS Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|           | 2.4            |                                                                                                                                                                                                      | Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

|           | 2.5            |                                                                                                                                                                                                      | emory Controller Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                        |

|           |                | 2.5.1                                                                                                                                                                                                | ROM Chip-Select Command Gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

|           |                | 2.5.2                                                                                                                                                                                                | Wait States and Command Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

|           |                | 2.5.3                                                                                                                                                                                                | High-Speed Clock ROM Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                        |

|           |                | 2.5.4                                                                                                                                                                                                | ROM Chip-Select Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

|           |                | 2.5.5                                                                                                                                                                                                | DOS Chip-Select Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

|           |                | 2.5.6                                                                                                                                                                                                | Self-Refresh DRAMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                        |

|           |                | 2.5.7                                                                                                                                                                                                | 80-ns DRAM Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                        |

|           |                | 2.0                                                                                                                                                                                                  | oo no 210 an eappoint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                        |

| Chapter 4 | PC/A           | AT PERIP                                                                                                                                                                                             | PHERAL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                        |

|           | 3.1            | Bus Initi                                                                                                                                                                                            | alization Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-2                                                                                                                                    |

|           |                | 3.1.1                                                                                                                                                                                                | Bus Initialization Enable Register (Port 3D4h, Index 12h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 3-2                                                                                                                                  |

|           |                | 3.1.2                                                                                                                                                                                                | Bus Initialization Register (Port 3D4h, Index 19h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 3-2                                                                                                                                  |

|           |                | 3.1.3                                                                                                                                                                                                | Parallel Port Address Select Register (Port 3D4h, Index 20h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                        |

|           | 3.2            | PC/AT-C                                                                                                                                                                                              | Compatible Port Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|           |                |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                        |

|           |                | 3.2.1                                                                                                                                                                                                | Interrupt Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-3                                                                                                                                    |

|           |                | 3.2.1<br>3.2.2                                                                                                                                                                                       | Interrupt Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

|           |                | 3.2.2                                                                                                                                                                                                | Programmable Interval Timer Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-4                                                                                                                                    |

|           |                | _                                                                                                                                                                                                    | Programmable Interval Timer Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-4<br>3-5                                                                                                                             |

|           |                | 3.2.2<br>3.2.3<br>3.2.4                                                                                                                                                                              | Programmable Interval Timer Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-4<br>3-5<br>3-7                                                                                                                      |

|           |                | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5                                                                                                                                                                     | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-4<br>3-5<br>3-7<br>3-8                                                                                                               |

|           |                | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6                                                                                                                                                            | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-4<br>3-5<br>3-7<br>3-8                                                                                                               |

|           | 3.3            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7                                                                                                                                                   | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11                                                                                                     |

|           | 3.3            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella                                                                                                                                       | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers.  Parallel Port Interface Registers  UART Registers  Real-Time Clock  neous PC/AT-Compatible Port Registers                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-20                                                                                           |

|           | 3.3            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1                                                                                                                              | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  neous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)                                                                                                                                                                                                                                                                                                                                                                                               | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20                                                                                 |

|           | 3.3            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2                                                                                                                     | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  neous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)                                                                                                                                                                                                                                                                                                                                                                  | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-20                                                                       |

|           | 3.3            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3                                                                                                            | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  neous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)                                                                                                                                                                                                                                                                                                                      | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-20<br>. 3-21                                                             |

|           | 3.3            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                                                                                                   | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  Ineous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)                                                                                                                                                                                                                                                                                | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-20<br>. 3-21<br>. 3-21                                                   |

|           | 3.3            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3                                                                                                            | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  neous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)                                                                                                                                                                                                                                                                                                                      | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-20<br>. 3-21<br>. 3-21                                                   |

| Chapter 5 |                | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5                                                                                          | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  Ineous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)                                                                                                                                                                                                                                                                                | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-20<br>. 3-21<br>. 3-21                                                   |

| Chapter 5 |                | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5                                                                                          | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  Ineous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h).  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview                                                                                                                                                                                                                | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-20<br>. 3-21<br>. 3-21                                                   |

| Chapter 5 | CON            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>IFIGURA<br>Configu<br>4.1.1                                                           | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers.  Parallel Port Interface Registers  UART Registers  Real-Time Clock  neous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h).  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview  Port Registers                                                                                                                                                                                                | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-20<br>. 3-21<br>. 3-21                                                   |

| Chapter 5 | CON            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>IFIGURA<br>Configu<br>4.1.1<br>4.1.2                                                  | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  neous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview  Port Registers  Index Registers                                                                                                                                                                                 | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-20<br>. 3-20<br>. 3-21<br>. 3-21<br>4-2<br>4-2                                               |

| Chapter 5 | CON            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>IFIGURA<br>Configu<br>4.1.1<br>4.1.2<br>4.1.3                                         | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  Ineous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview  Port Registers  Index Registers  Configuring the ÉlanSC310 Microcontroller                                                                                                                                     | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-20<br>. 3-21<br>. 3-21<br>4-2<br>4-2<br>4-4                              |

| Chapter 5 | CON            | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>IFIGURA<br>Configu<br>4.1.1<br>4.1.2<br>4.1.3                                         | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers.  Parallel Port Interface Registers  UART Registers  Real-Time Clock  Ineous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview  Port Registers  Index Registers  Configuring the ÉlanSC310 Microcontroller  ration Port Registers                                                                                                             | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-20<br>. 3-20<br>. 3-21<br>. 3-21<br>4-2<br>4-2<br>4-4<br>. 4-11                              |

| Chapter 5 | <b>CON</b> 4.1 | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>IFIGURA<br>Configu<br>4.1.1<br>4.1.2<br>4.1.3                                         | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  neous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview  Port Registers  Index Registers  Configuring the ÉlanSC310 Microcontroller  ration Port Registers  Configuration Address Register (Port 022h)                                                                   | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-21<br>. 3-21<br>4-2<br>4-2<br>4-4<br>4-11                                |

| Chapter 5 | <b>CON</b> 4.1 | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>IFIGURA<br>Configu<br>4.1.1<br>4.1.2<br>4.1.3<br>Configu                              | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers.  Parallel Port Interface Registers  UART Registers  Real-Time Clock  Ineous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview  Port Registers  Index Registers  Configuring the ÉlanSC310 Microcontroller  ration Port Registers                                                                                                             | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-21<br>. 3-21<br>4-2<br>4-2<br>4-4<br>4-11                                |

| Chapter 5 | <b>CON</b> 4.1 | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>IFIGURA<br>Configu<br>4.1.1<br>4.1.2<br>4.1.3<br>Configu<br>4.2.1<br>4.2.2            | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  neous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview  Port Registers  Index Registers  Configuring the ÉlanSC310 Microcontroller  ration Port Registers  Configuration Address Register (Port 022h)                                                                   | 3-4<br>3-5<br>3-7<br>3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-21<br>. 3-21<br>4-2<br>4-2<br>4-1<br>. 4-11<br>. 4-11                    |

| Chapter 5 | <b>CON</b> 4.1 | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>IFIGURA<br>Configu<br>4.1.1<br>4.1.2<br>4.1.3<br>Configu<br>4.2.1<br>4.2.2            | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  Ineous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview  Port Registers  Index Registers  Configuring the ÉlanSC310 Microcontroller  ration Port Registers  Configuration Address Register (Port 022h)  Configuration Data Register (Port 023h)                         | . 3-4<br>. 3-5<br>. 3-7<br>. 3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-21<br>. 3-21<br>. 3-21<br>4-2<br>4-2<br>4-11<br>. 4-11<br>. 4-11 |

| Chapter 5 | <b>CON</b> 4.1 | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>Miscella<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>IFIGURA<br>Configu<br>4.1.1<br>4.1.2<br>4.1.3<br>Configu<br>4.2.1<br>4.2.2<br>Configu | Programmable Interval Timer Registers  DMA Controller Registers  DMA Page Registers  Parallel Port Interface Registers  UART Registers  Real-Time Clock  Ineous PC/AT-Compatible Port Registers  XT Keyboard Data Register (Port 060h)  Port B Register (Port 061h)  NMI/RTC Index Address Register (Port 070h)  RTC Index Data Register (Port 071h)  Port 92 (Port 092h)  TION REGISTERS  ration Register Overview  Port Registers  Index Registers  Configuring the ÉlanSC310 Microcontroller  ration Port Registers  Configuration Address Register (Port 022h)  Configuration Data Register (Port 023h)  ration Index Registers | . 3-4<br>. 3-5<br>. 3-7<br>. 3-8<br>. 3-11<br>. 3-16<br>. 3-20<br>. 3-21<br>. 3-21<br>. 3-21<br>4-2<br>4-2<br>4-11<br>. 4-11<br>. 4-11 |

| 4.3.4  | Reserved Registers (Indexes 0A-0Eh)                |        |

|--------|----------------------------------------------------|--------|

| 4.3.5  | Reserved Register (Index 0Fh)                      | . 4-12 |

| 4.3.6  | Reserved Registers (Indexes 10–39h)                | . 4-12 |

| 4.3.7  | I/O Timeout Register (Index 40h)                   | . 4-12 |

| 4.3.8  | SMI Enable Register (Index 41h)                    | . 4-13 |

| 4.3.9  | SMI I/O Status Register (Index 42h)                | . 4-14 |

| 4.3.10 | SMI Status Register (Index 43h)                    | . 4-14 |

| 4.3.11 | Miscellaneous 4 Register (Index 44h)               | . 4-15 |

| 4.3.12 | PIO Address Register (Index 45h)                   | . 4-15 |

| 4.3.13 | PIO Timer Register (Index 46h)                     |        |

| 4.3.14 | Drive Timer Register (Index 47h)                   |        |

| 4.3.15 | Control A Register (Index 48h)                     |        |

| 4.3.16 | Reserved Registers (Indexes 49–4Fh)                |        |

| 4.3.17 | MMS Memory Wait State 2 Register (Index 50h)       |        |

| 4.3.18 | ROM Configuration 2 Register (Index 51h)           |        |

| 4.3.19 | Reserved Registers (Indexes 52–5Fh)                |        |

| 4.3.20 | Command Delay Register (Index 60h)                 |        |

| 4.3.21 | I/O Wait State Register (Index 61h)                |        |

| 4.3.22 | MMS Memory Wait State 1 Register (Index 62h)       |        |

| 4.3.23 | Wait State Control Register (Index 63h)            |        |

| 4.3.24 | Version Register (Index 64h)                       |        |

| 4.3.25 | ROM Configuration 1 Register (Index 65h)           |        |

| 4.3.26 | Memory Configuration 1 Register (Index 66h)        |        |

| 4.3.27 | MMSA Address Extension 1 Register (Index 67h)      |        |

| -      | <b>5</b>                                           |        |

| 4.3.28 | Shadow RAM Enable 1 Register (Index 68h)           |        |

| 4.3.29 | Shadow RAM Enable 2 Register (Index 69h)           |        |

| 4.3.30 | Reserved Register (Index 6Ah)                      |        |

| 4.3.31 | Miscellaneous 2 Register (Index 6Bh)               |        |

| 4.3.32 | MMS Address Extension 1 Register (Index 6Ch)       |        |

| 4.3.33 | MMS Address Register (Index 6Dh)                   |        |

| 4.3.34 | MMS Address Extension 2 Register (Index 6Eh)       |        |

| 4.3.35 | Miscellaneous 1 Register (Index 6Fh)               |        |

| 4.3.36 | Miscellaneous 6 Register (Index 70h)               |        |

| 4.3.37 | MMSA Device 1 Register (Index 71h)                 |        |

| 4.3.38 | MMSA Device 2 Register (Index 72h)                 |        |

| 4.3.39 | MMSB Device Register (Index 73h)                   |        |

| 4.3.40 | MMSB Control Register (Index 74h)                  |        |

| 4.3.41 | Activity Mask 1 Register (Index 75h)               |        |

| 4.3.42 | Activity Mask 2 Register (Index 76h)               |        |

| 4.3.43 | Control B Register (Index 77h)                     |        |

| 4.3.44 | Reserved Registers (Indexes 78–7Fh)                |        |

| 4.3.45 | Power Control 1 Register (Index 80h)               | . 4-42 |

| 4.3.46 | Power Control 2 Register (Index 81h)               |        |

| 4.3.47 | NMI/SMI Enable Register (Index 82h)                | . 4-43 |

| 4.3.48 | High-Speed to Low-Speed Timer Register (Index 83h) | . 4-44 |

| 4.3.49 | Low-Speed to Doze Timer Register (Index 84h)       | . 4-44 |

| 4.3.50 | Doze to Sleep Timer Register (Index 85h)           | . 4-44 |

| 4.3.51 | Sleep to Suspend Timer Register (Index 86h)        |        |

| 4.3.52 | Suspend to Off Timer Register (Index 87h)          |        |

| 4.3.53 | Software Mode Control Register (Index 88h)         |        |

| 4.3.54 | General-Purpose I/O 0 Register (Index 89h)         |        |

| 4.3.55 | Reserved Registers (Indexes 8A-8Bh)                |        |

| 4.3.56 | I/O Activity Address 0 Register (Index 8Ch)        |        |

| 4.3.57 | I/O Activity Address 1 Register (Index 8Dh)        |        |

| 4.3.58 | Reserved Register (Index 8Eh)                      |        |

| 4.3.59 | Clock Control Register (Index 8Fh)                 |        |

| 4.3.60 | Reserved Register (Index 90h)                      |        |

| 4.3.61 | General-Purpose I/O Control Register (Index 91h)   |        |

|        |                                                    |        |

|            | 4.3.62      | UART Clock Enable Register (Index 92h)                    | . 4-49 |

|------------|-------------|-----------------------------------------------------------|--------|

|            | 4.3.63      | Reserved Register (Index 93h)                             |        |

|            | 4.3.64      | General-Purpose I/O 2 Register (Index 94h)                | . 4-49 |

|            | 4.3.65      | General-Purpose I/O 3 Register (Index 95h)                | . 4-49 |

|            | 4.3.66      | Reserved Registers (Indexes 96–99h)                       | . 4-49 |

|            | 4.3.67      | Memory Write Activity Lower Boundary Register (Index 9Ah) | . 4-50 |

|            | 4.3.68      | Memory Write Activity Upper Boundary Register (Index 9Bh) | . 4-50 |

|            | 4.3.69      | General-Purpose I/O 1 Register (Index 9Ch)                | . 4-51 |

|            | 4.3.70      | Reserved Register (Index 9Dh)                             | . 4-51 |

|            | 4.3.71      | Auto Low-Speed Control Register (Index 9Fh)               |        |

|            | 4.3.72      | Activity Status 1 Register (Index A0h)                    |        |

|            | 4.3.73      | Activity Status 2 Register (Index A1h)                    |        |

|            | 4.3.74      | PMU Status 1 Register (Index A2h)                         |        |

|            | 4.3.75      | CPU Status 0 Register (Index A3h)                         |        |

|            | 4.3.76      | CPU Status 1 Register (Index A4h)                         |        |

|            | 4.3.77      | NMI/SMI Control Register (Index A5h)                      |        |

|            | 4.3.78      | Reserved Register (Index A6h)                             |        |

|            | 4.3.79      | PMU Control 1 Register (Index A7h)                        |        |

|            | 4.3.80      | Reserved Register (Index A8h)                             |        |

|            | 4.3.81      | SMI MMS Upper Page Register (Index A9h)                   |        |

|            | 4.3.82      | SMI MMS Page Register (Index AAh)                         |        |

|            | 4.3.83      | Power Control 3 Register (Index ABh)                      |        |

|            | 4.3.84      | Power Control 4 Register (Index ACh)                      |        |

|            | 4.3.85      | PMU Control 3 Register (Index ADh)                        |        |

|            | 4.3.86      | Reserved Register (Index AEh)                             |        |

|            | 4.3.87      | PMU Control 2 Register (Index AFh)                        |        |

|            | 4.3.88      | Function Enable 1 Register (Index B0h)                    |        |

|            | 4.3.89      | Function Enable 2 Register (Index B1h)                    |        |

|            | 4.3.90      | PIRQ Configuration Register (Index B2h)                   |        |

|            | 4.3.91      | Miscellaneous 5 Register (Index B3h)                      |        |

|            | 4.3.92      | Function Enable 3 Register (Index B4h)                    |        |

|            | 4.3.93      | Reserved Registers (Indexes B5h-B7h)                      |        |

|            | 4.3.94      | ROM Configuration 3 Register (Index B8h)                  |        |

|            | 4.3.95      | Memory Configuration 2 Register (Index B9h)               |        |

|            | 4.3.96      | Miscellaneous 3 Register (Index BAh)                      | . 4-70 |

| Appendix A | CONFIGURAT  | TION INDEX                                                |        |

|            | REGISTER RI | EFERENCE                                                  | A-1    |

| Appendix B | XT-KEYBOAR  | D INTERFACE                                               | B-1    |

|            |             |                                                           |        |

**INDEX**

# **LIST OF FIGURES**

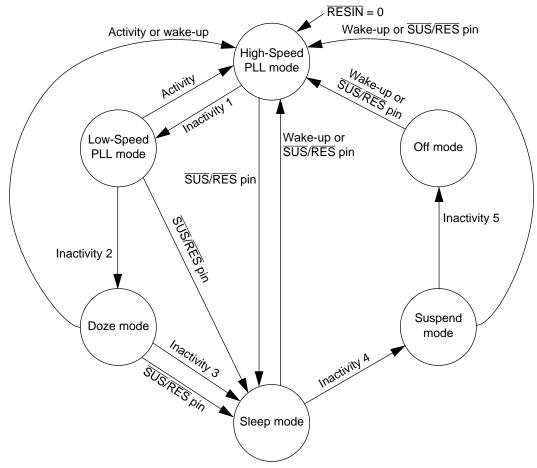

| Figure 1-1 | PMU Operating-Mode Transitions               | 1-4  |

|------------|----------------------------------------------|------|

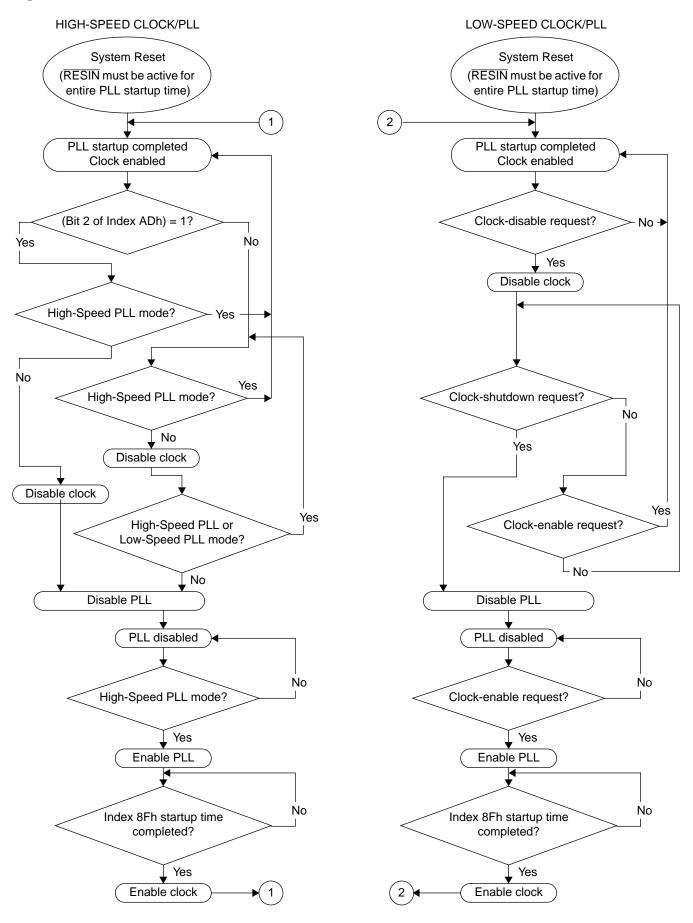

| Figure 1-2 | PLL Control Flowchart                        | 1-18 |

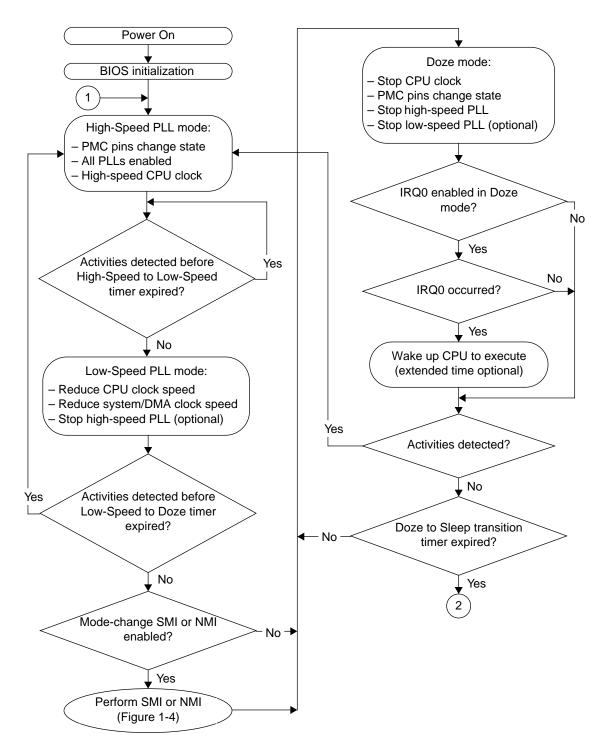

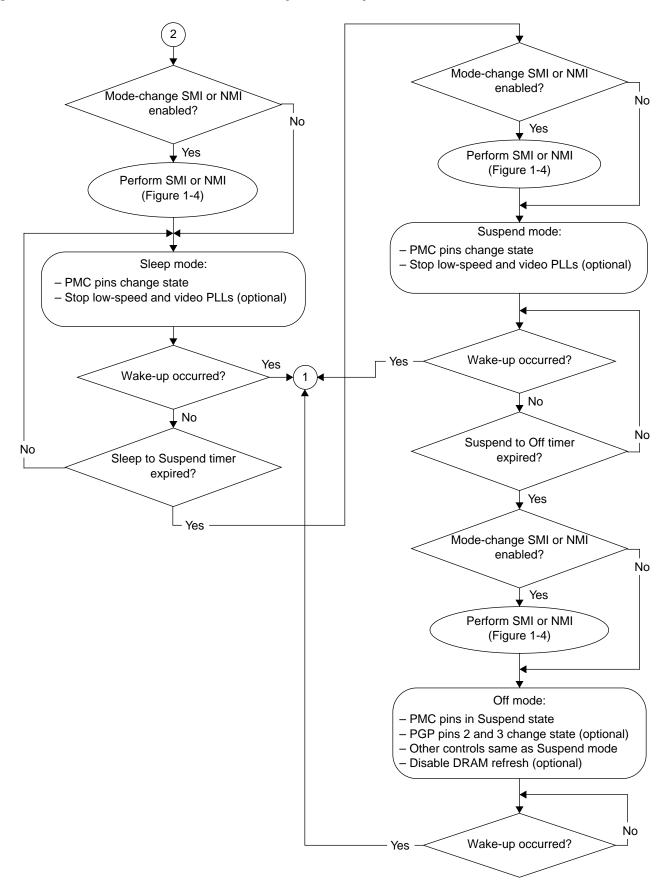

| Figure 1-3 | State Transition Flowchart                   | 1-20 |

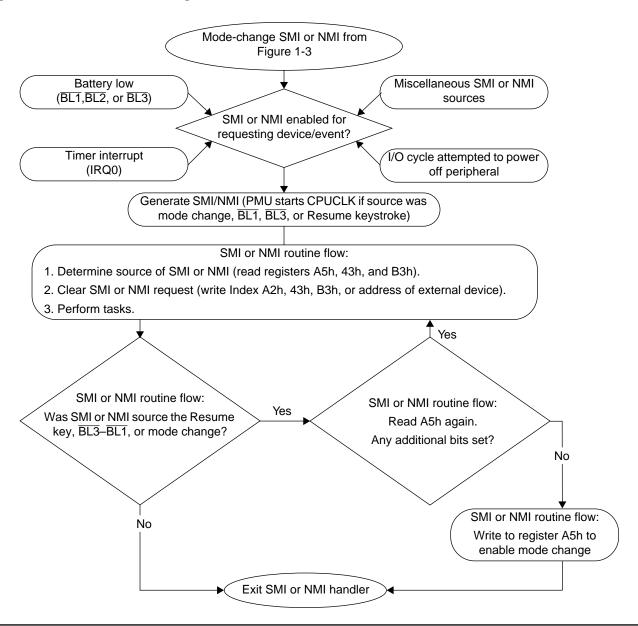

| Figure 1-4 | SMI Processing Flowchart                     | 1-26 |

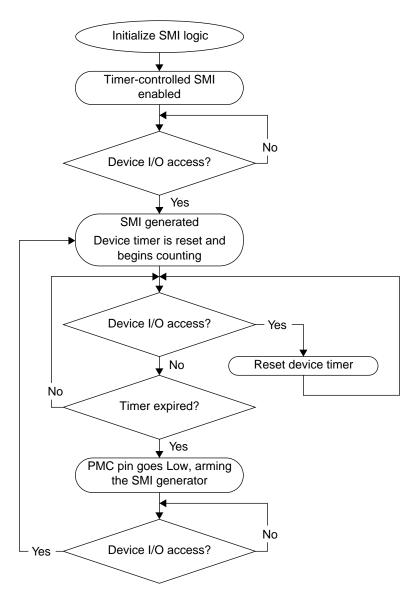

| Figure 1-5 | SMI Device-Powerdown Flowchart               | 1-30 |

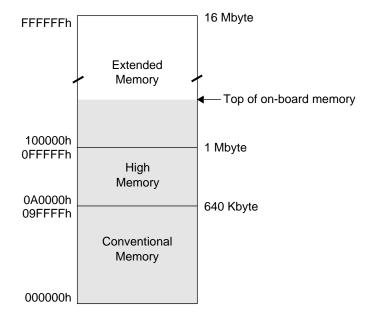

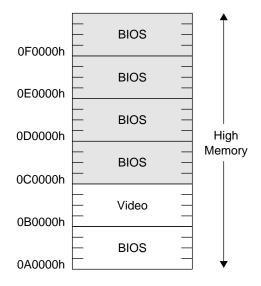

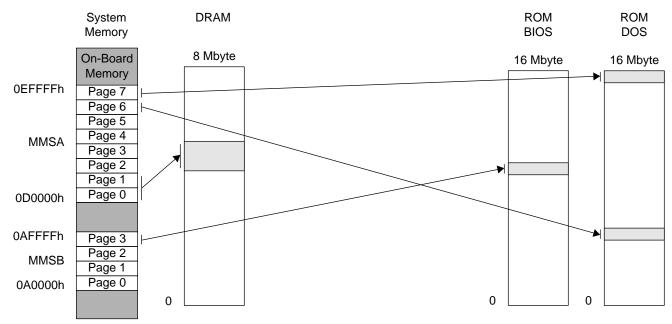

| Figure 2-1 | Typical AT Address Space                     |      |

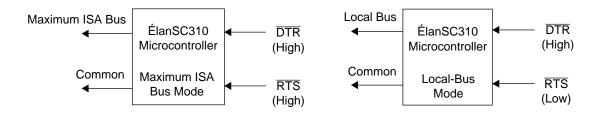

| Figure 2-2 | ÉlanSC310 Microcontroller Bus Configurations |      |

| Figure 2-3 | High Memory                                  |      |

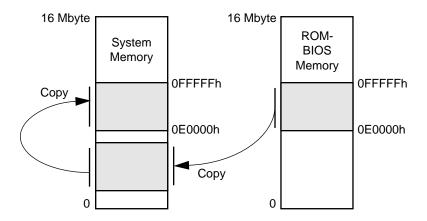

| Figure 2-4 | Copying ROM Contents                         |      |

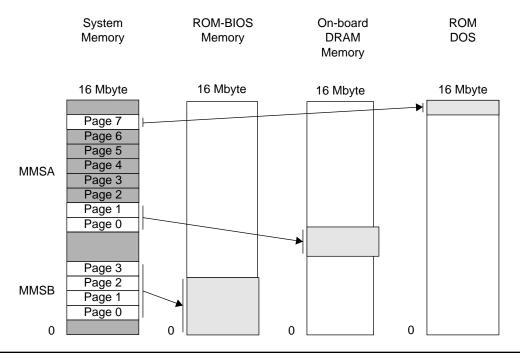

| Figure 2-5 | Memory Mapping System                        | 2-9  |

| Figure 2-6 | MMSA and MMSB                                | 2-10 |

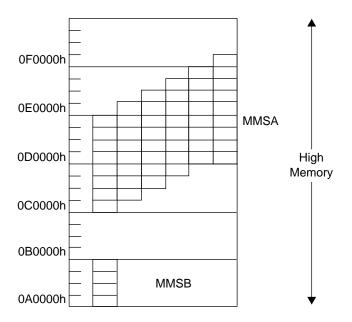

| Figure 2-7 | MMS Mapping Example                          |      |

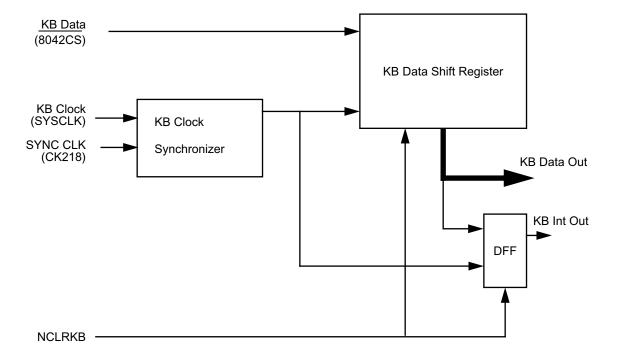

| Figure B-1 | XT Keyboard Block Diagram                    | B-1  |

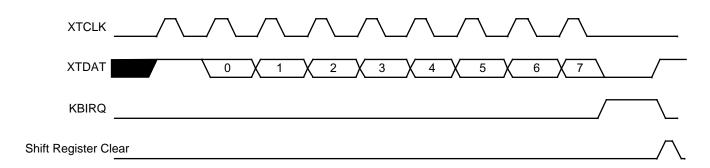

| Figure B-2 | XT Keyboard Timing Diagram                   | B-3  |

# **LIST OF TABLES**

| Table 1-1  | PMU Clock Speeds                                               | 1-6  |  |  |  |  |

|------------|----------------------------------------------------------------|------|--|--|--|--|

| Table 1-2  | Inactivity States and Transition Intervals                     |      |  |  |  |  |

| Table 1-3  | Power-Management Setup                                         |      |  |  |  |  |

| Table 1-4  | Power-Management Control Pin Settings                          |      |  |  |  |  |

| Table 1-5  | PIO Timeout Settings                                           |      |  |  |  |  |

| Table 1-6  | SMI-Generation Settings for PIO Accesses                       |      |  |  |  |  |

| Table 1-7  | MC Pin Functionality                                           |      |  |  |  |  |

| Table 1-8  | Vake-Up Signal Descriptions                                    |      |  |  |  |  |

| Table 1-9  | Registers that Enable SMI Sources                              |      |  |  |  |  |

| Table 1-10 | Battery-Level Management Functionality                         | 1-32 |  |  |  |  |

| Table 2-1  | Memory Initialization Example                                  |      |  |  |  |  |

| Table 2-2  | Refresh Initialization Example                                 | 2-3  |  |  |  |  |

| Table 2-3  | Memory-Speed Initialization Example                            |      |  |  |  |  |

| Table 2-4  | 33-MHz Wait States                                             |      |  |  |  |  |

| Table 2-5  | Bus Configuration                                              | 2-5  |  |  |  |  |