# Élan™SC400 Microcontroller

# Register Set Reference Manual Including Changes for the ÉlanSC410 Microcontroller

This document amends the *Élan™SC400 Microcontroller Register Set Reference Manual*, order #21032A, including additional information for the ÉlanSC410 microcontroller. It consists of three parts:

- "Documentation Defects and Corrections" lists documentation defects found in the original publication.

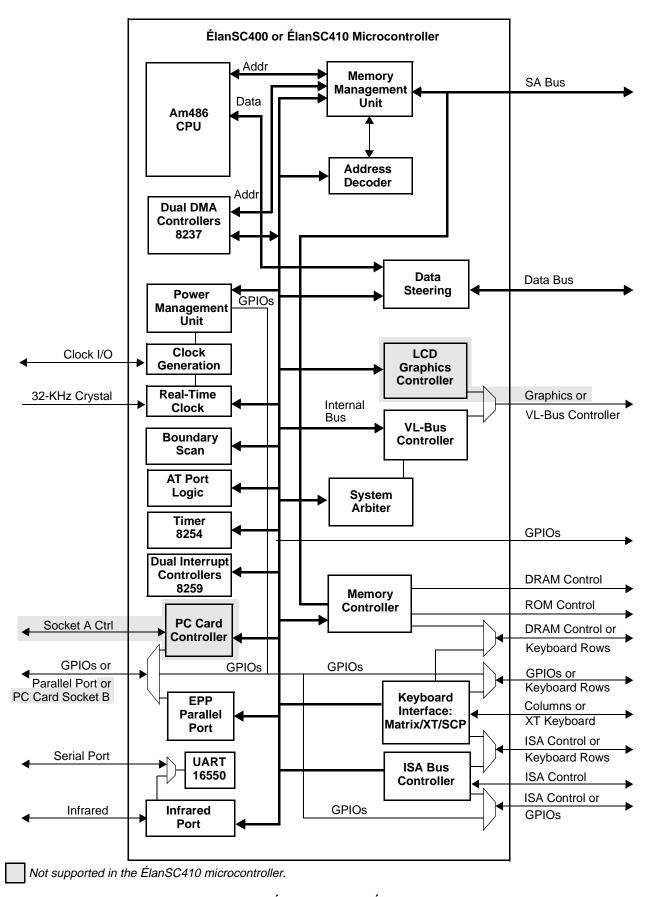

- "Changes for the ÉlanSC410 Microcontroller" on page 25 gives an overview of differences between the ÉlanSC400 microcontroller and the ÉlanSC410 microcontroller, and lists all the registers and bits not supported on the ÉlanSC410 microcontroller.

- The Index beginning on page 35 includes all of the registers listed in this document, with index offsets listed separately by subsystem.

## DOCUMENTATION DEFECTS AND CORRECTIONS

Table 1 lists defects that have been found in the Élan™SC400 Microcontroller Register Set Reference Manual, order #21032A. Defects are listed in page order. Each entry lists the following:

- page number

- item to be corrected

- original text

- corrected text

- comments explaining the change

Table entries that correct text in a diagram do not contain the entire diagram. If a default value is changed,

the original and changed default values are shown for the whole register. If other text is changed, the entry describes the affected part of the diagram and lists the original and changed text.

Each item description includes the register name, so changes affecting a particular register can be found by consulting the index in this document.

Unchanged portions of a paragraph are replaced by an ellipsis (...) in entries where this might make the change easier to find. The whole paragraph is included if it is useful for understanding why the change was made.

Table 1. Corrections to the Élan™SC400 Microcontroller Register Set Reference Manual

| Page       | Item                                                                                            | Original Text                                                                                                                    | Change To                                                                                                                                                                                                                             | Comment                                                              |

|------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Title Page |                                                                                                 | Élan™SC400 Microcontroller<br>Register Set Reference Manual                                                                      | Élan™SC400 and ÉlanSC410<br>Microcontrollers Register Set<br>Reference Manual                                                                                                                                                         | Add ÉlanSC410 microcontroller to book title.                         |

| Chapt      | er 2: PC/AT-Compatible                                                                          | Direct-Mapped Registers                                                                                                          |                                                                                                                                                                                                                                       |                                                                      |

| 2-36       | Programmable Interval<br>Timer #1 Channel 0<br>Count Register, Address<br>0040h; last paragraph | When set up for either BCD or 16-bit binary count operation, the maximum count for Channel 0 is achieved by writing the internal | When set up for either BCD or 16-bit binary count operation, the maximum count for Channel 0 is achieved by writing the internal counting element associated with this register to 0. See direct-mapped register 43h for more detail. | for all three<br>pages. Notation<br>"0000h/d" is<br>misleading. Zero |

| 2-37       | Programmable Interval<br>Timer #1 Channel 1<br>Count Register, Address<br>0041h; last paragraph | this register to 0000h/d. See direct-                                                                                            |                                                                                                                                                                                                                                       |                                                                      |

| 2-38       | Programmable Interval<br>Timer #1 Channel 2<br>Count Register, Address<br>0042h; last paragraph |                                                                                                                                  |                                                                                                                                                                                                                                       |                                                                      |

Table 1. Corrections to the Élan™SC400 Microcontroller Register Set Reference Manual (Continued)

| Page | Item                                                                                              | Original Text                                                                                                                                                                                                                   | Change To                                                                                                                                                                                                                                                                                  | Comment                                                                                                              |

|------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 2-49 | PC/AT Keyboard<br>Mouse Interface Status<br>Register, Address<br>0064h; bit 5 description         | When CSC index C0h[0] is set, this bit is a PC/2 mouse-compatible mouse output buffer full flay                                                                                                                                 | When CSC index C0h[0] is set, this bit is a PS/2 mouse-compatible mouse output buffer full flag                                                                                                                                                                                            | Two corrections: "PS/2 mouse" and "flag."                                                                            |

| 2-52 | RTC/CMOS RAM<br>Index Register,<br>Address 0070h;<br>diagram (bit 7 column)                       | Reserved<br>-                                                                                                                                                                                                                   | NMI_GATE<br>0<br>W                                                                                                                                                                                                                                                                         | The NMI_GATE function has not moved to CSC index 9Dh[2] in                                                           |

|      | RTC/CMOS RAM<br>Index Register,<br>Address 0070h; bit 7<br>description                            | 7 Reserved  During read/modify/ write operations, software must preserve this bit.                                                                                                                                              | 7 NMI_GATE Master NMI Mask  1 = NMI events are gated off from reaching the core  0 = NMI events will propagate to the CPU core                                                                                                                                                             | the ÉlanSC400<br>or ÉlanSC410<br>microcontrollers.                                                                   |

|      | RTC/CMOS RAM<br>Index Register,<br>Address 0070h;<br>Programming Notes                            | Programming Notes Bit 7 of this register is the master NMI gate control in a typical PC/AT Compatible system. For various reason, this bit has been made to reside at CSC index 9Dh[2] (entire paragraph)                       | Programming Notes                                                                                                                                                                                                                                                                          |                                                                                                                      |

| 2-92 | Master Software<br>DRQ(n) Request<br>Register, Address<br>00D2h; default bit<br>values in diagram | 0000000                                                                                                                                                                                                                         | xxxxxxx                                                                                                                                                                                                                                                                                    | "x" = non-<br>deterministic.                                                                                         |

|      | Master Software<br>DRQ(n) Request<br>Register, Address<br>00D2h; bits 1–0<br>description          | 0 0 = Mask/unmask DMA Channel 4 mask per the REQDMA bit 0 1 = Mask/unmask DMA Channel 5 mask per the REQDMA bit 1 0 = Mask/unmask DMA Channel 6 mask per the REQDMA bit 1 1 = Mask/unmask DMA Channel 7 mask per the REQDMA bit | 0 0 = Set/Reset DMA Channel 4 internal DMA request per the REQDMA bit  0 1 = Set/Reset DMA Channel 5 internal DMA request per the REQDMA bit  1 0 = Set/Reset DMA Channel 6 internal DMA request per the REQDMA bit  1 1 = Set/Reset DMA Channel 7 internal DMA request per the REQDMA bit | This field selects<br>the DMA<br>request channel<br>to assert or<br>deassert,<br>depending on<br>the state of bit 2. |

| 2-93 | Master DMA Mask<br>Register Channels 4–7,<br>Address 00D4h; default<br>bit values in diagram      | 0000000                                                                                                                                                                                                                         | xxxxxxx                                                                                                                                                                                                                                                                                    | "x" = non-<br>deterministic.                                                                                         |

| 2-94 | Master DMA Mode<br>Register Channels 4–7,<br>Address 00D6h; default<br>bit values in diagram      | 0000000                                                                                                                                                                                                                         | xxxxxxx                                                                                                                                                                                                                                                                                    | "x" = non-<br>deterministic.                                                                                         |

| 2-95 | Master DMA Clear Byte<br>Pointer Register,<br>Address 00D8h; default<br>bit values in diagram     | 0000000                                                                                                                                                                                                                         | xxxxxxx                                                                                                                                                                                                                                                                                    | "x" = non-<br>deterministic.                                                                                         |

Table 1. Corrections to the Élan™SC400 Microcontroller Register Set Reference Manual (Continued)

| Page           | Item                                                                                              | Original Text                   | Change To                                                                                                                                           | Comment                                                          |

|----------------|---------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 2-96           | Master DMA Controller<br>Reset Register,<br>Address 00DAh; default<br>bit values in diagram       | 0000000                         | xxxxxxx                                                                                                                                             | "x" = non-<br>deterministic.                                     |

| 2-97           | Master DMA Controller<br>Temporary Register,<br>Address 00DAh; default<br>bit values in diagram   | 0000000                         | xxxxxxx                                                                                                                                             | "x" = non-<br>deterministic.                                     |

| 2-98           | Master DMA Reset<br>Mask Register, Address<br>00DCh; default bit<br>values in diagram             | 0000000                         | xxxxxxx                                                                                                                                             | "x" = non-<br>deterministic.                                     |

| 2-103<br>2-104 |                                                                                                   |                                 | ?????xxx                                                                                                                                            | "x" = non-<br>deterministic.<br>"?" = depends<br>on input state. |

|                | Parallel Port 2 Status<br>Register, Address<br>0279h; Programming<br>Notes                        | Programming Notes (entire note) | Programming Notes On power-up, the parallel port defaults to PC/AT-Compatible mode. Upon switching to EPP mode the bit defaults change to ?????xx0b | Clarify behavior.                                                |

| 2-105          | Parallel Port 2 Status<br>Register (EPP Mode),<br>Address 0279h; default<br>bit values in diagram |                                 | ?????xx0                                                                                                                                            | "x" = non-<br>deterministic.<br>"?" = depends<br>on input state. |

|                | Parallel Port 2 Status<br>Register (EPP Mode),<br>Address 0279h;<br>Programming Notes             | Programming Notes               | Programming Notes On power-up, the parallel port defaults to PC/AT-Compatible mode. Upon switching to EPP mode the bit defaults change to ?????xx0b | Clarify behavior.                                                |

Table 1. Corrections to the Élan™SC400 Microcontroller Register Set Reference Manual (Continued)

| Page  | Item                                                                                     | Original Text                                                                                                                                                            | Change To                                                                                                                                                                                                                                                                                                                       | Comment                                         |

|-------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 2-111 | COM2 Baud Clock<br>Divisor Latch LSB,<br>Address 02F8h; default<br>bit values in diagram | 0000000                                                                                                                                                                  | 0000001                                                                                                                                                                                                                                                                                                                         | Divisor must be nonzero.                        |

|       | COM2 Baud Clock<br>Divisor Latch LSB,<br>Address 02F8h;<br>Programming Notes             | Programming Notes                                                                                                                                                        | Programming Notes In order to determine the UART baud rate that will result from a particular setting of the baud rate divisor latch,                                                                                                                                                                                           | notes on both pages.                            |

| 2-112 | COM2 Baud Clock<br>Divisor Latch MSB,<br>Address 02F9h;<br>Programming Notes             |                                                                                                                                                                          | the 16x baud clock is divided by 16 to give a normalized baud rate. Because the standard 16x baud clock runs at 1.8432 MHz, the "normalized" baud rate is 115200. This rate is then divided by the value of the 16-bit baud clock divisor latch register. It is invalid to program a baud rate divisor of 0.                    |                                                 |

|       |                                                                                          |                                                                                                                                                                          | The baud rate divisor latch, being a 16-bit value, provides for up to 64k–1 different baud rates (0 is not a valid baud rate). However, only a few of the available rates are ever used in common practice. See the following table for the commonly used baud rates along with the baud rate divisor required to achieve them: |                                                 |

|       |                                                                                          |                                                                                                                                                                          | Baud Divisor Latch Value                                                                                                                                                                                                                                                                                                        |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 110 0417h                                                                                                                                                                                                                                                                                                                       |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 150 0300h                                                                                                                                                                                                                                                                                                                       |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 300 0180h                                                                                                                                                                                                                                                                                                                       |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 600 00C0h                                                                                                                                                                                                                                                                                                                       |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 1200 0060h                                                                                                                                                                                                                                                                                                                      |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 2400 0030h                                                                                                                                                                                                                                                                                                                      |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 4800 0018h                                                                                                                                                                                                                                                                                                                      |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 9600 000Ch                                                                                                                                                                                                                                                                                                                      |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 19200 0006h                                                                                                                                                                                                                                                                                                                     |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 38400 0003h                                                                                                                                                                                                                                                                                                                     |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 57600 0002h                                                                                                                                                                                                                                                                                                                     |                                                 |

|       |                                                                                          |                                                                                                                                                                          | 115200 0001h                                                                                                                                                                                                                                                                                                                    |                                                 |

| 2-114 | COM2 Interrupt ID<br>Register, Address<br>02FAh; bits 7–6<br>description                 | <ul> <li>0 0 = No significance</li> <li>0 1 = No significance</li> <li>1 0 = 16450-compatible mode is enabled</li> <li>1 1 = 16550-compatible mode is enabled</li> </ul> | <ul> <li>0 0 = 16450-Compatible mode is enabled (default)</li> <li>0 1 = No significance</li> <li>1 0 = No significance</li> <li>1 1 = 16550-Compatible mode is enabled</li> </ul>                                                                                                                                              | Default of 0 0 indicates 16450-Compatible mode. |

| 2-121 | COM2 Modem Status<br>Register, Address<br>02FEh; default bit<br>values in diagram        | x x x x 0 0 0 0                                                                                                                                                          | ????0000                                                                                                                                                                                                                                                                                                                        | "?" = depends on input state                    |

Table 1. Corrections to the Élan™SC400 Microcontroller Register Set Reference Manual (Continued)

| Page           | Item                                                                                              | Original Text     | Change To                                                                                                                                           | Comment                                                          |

|----------------|---------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 2-124<br>2-125 | Parallel Port 1 Status<br>Register, Address<br>0379h; default bit<br>values in diagram            |                   | ?????xxx                                                                                                                                            | "x" = non-<br>deterministic.<br>"?" = depends<br>on input state. |

|                | Parallel Port 1 Status                                                                            | Programming Notes | Programming Notes                                                                                                                                   | Clarify behavior.                                                |

|                | Register, Address<br>0379h; Programming<br>Notes                                                  | (entire note)     | On power-up, the parallel port defaults to PC/AT-Compatible mode. Upon switching to EPP mode the bit defaults change to ?????xx0b                   |                                                                  |

| 2-126          | Parallel Port 1 Status<br>Register (EPP Mode),<br>Address 0379h; default<br>bit values in diagram |                   | ?????xx0                                                                                                                                            | "x" = non-<br>deterministic.<br>"?" = depends<br>on input state. |

|                | Parallel Port 1 Status<br>Register (EPP Mode),<br>Address 0379h;<br>Programming Notes             | Programming Notes | Programming Notes On power-up, the parallel port defaults to PC/AT-Compatible mode. Upon switching to EPP mode the bit defaults change to ?????xx0b | Clarify behavior.                                                |

Table 1. Corrections to the Élan™SC400 Microcontroller Register Set Reference Manual (Continued)

| Page  | Item                                                                                     | Original Text                                                                                                                                                    | Change To                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                    | Comment                                         |

|-------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 2-144 | COM1 Baud Clock<br>Divisor Latch LSB,<br>Address 03F8h; default<br>bit values in diagram | 0000000                                                                                                                                                          | 0000000                                                                                                                                                                                                                         | ) 1                                                                                                                                                                                                                                                                                                                                                                                                                | Divisor must be nonzero                         |

|       | COM1 Baud Clock<br>Divisor Latch LSB,<br>Address 03F8h;<br>Programming Notes             | Programming Notes                                                                                                                                                | rate that will setting of the                                                                                                                                                                                                   | etermine the UART baud<br>result from a particular<br>baud rate divisor latch,                                                                                                                                                                                                                                                                                                                                     | Add text to programming notes on both pages.    |

| 2-145 | COM1 Baud Clock<br>Divisor Latch MSB,<br>Address 03F9h;<br>Programming Notes             |                                                                                                                                                                  | give a norma<br>the standard<br>1.8432 MHz<br>rate is 11520<br>divided by th<br>clock divisor<br>to program a<br>The baud ra<br>16-bit value,<br>different bau<br>baud rate). H<br>available rat<br>common pra<br>table for the | d clock is divided by 16 to alized baud rate. Because 16x baud clock runs at the "normalized" baud 20. This rate is then e value of the 16-bit baud latch register. It is invalid a baud rate divisor of 0. the divisor latch, being a provides for up to 64k–1 and rates (0 is not a valid dowever, only a few of the es are ever used in actice. See the following commonly used baud with the baud rate divisor |                                                 |

|       |                                                                                          |                                                                                                                                                                  |                                                                                                                                                                                                                                 | achieve them:                                                                                                                                                                                                                                                                                                                                                                                                      |                                                 |

|       |                                                                                          |                                                                                                                                                                  | <u>Baud</u>                                                                                                                                                                                                                     | <b>Divisor Latch Value</b>                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 110                                                                                                                                                                                                                             | 0417h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 150                                                                                                                                                                                                                             | 0300h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 300                                                                                                                                                                                                                             | 0180h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 600                                                                                                                                                                                                                             | 00C0h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 1200                                                                                                                                                                                                                            | 0060h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 2400                                                                                                                                                                                                                            | 0030h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 4800                                                                                                                                                                                                                            | 0018h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 9600                                                                                                                                                                                                                            | 000Ch                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 19200                                                                                                                                                                                                                           | 0006h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 38400                                                                                                                                                                                                                           | 0003h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 57600                                                                                                                                                                                                                           | 0002h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

|       |                                                                                          |                                                                                                                                                                  | 115200                                                                                                                                                                                                                          | 0001h                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| 2-147 | COM1 Interrupt ID<br>Register, Address<br>03FAh; default value<br>for bit 0 in diagram   | <ul> <li>0 0 = No significance</li> <li>0 1 = No significance</li> <li>1 0 = 16450-compatible mode is enabled</li> <li>1 1 = 16550-compatible mode is</li> </ul> | enable<br>0 1 = No sig<br>1 0 = No sig                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                    | Default of 0 0 indicates 16450-Compatible mode. |

|       |                                                                                          | enabled                                                                                                                                                          | enable                                                                                                                                                                                                                          | •                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                 |

| 2-150 | COM1 Modem Control<br>Register, Address<br>03FCh; bit 3<br>description                   | Enable COM2 Interrupts                                                                                                                                           | Enable CO                                                                                                                                                                                                                       | M1 Interrupts                                                                                                                                                                                                                                                                                                                                                                                                      | Correction.                                     |

| 2-153 | COM1 Modem Status<br>Register, Address<br>03FEh; default bit<br>values in diagram        | x x x x 0 0 0 0                                                                                                                                                  | ????000                                                                                                                                                                                                                         | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                | "?" = depends on input state.                   |

Table 1. Corrections to the Élan™SC400 Microcontroller Register Set Reference Manual (Continued)

| Page  | Item                                                                                                             | Original Text                                                                                                                                                                                                                                   | Change To                                                                                                                                                                                                                                                                                                                                                                                                                  | Comment                                                                                         |

|-------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Chapt | er 3: Chip Setup and Co                                                                                          | ontrol (CSC) Indexed Registers                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                 |

| 3-15  | DRAM Control<br>Register, Index 04h;<br>Programming Notes                                                        | Programming Notes                                                                                                                                                                                                                               | Programming Notes The CAS precharge delay (controlled by TCP, bit 3) always has at least one added state (t) during CPU write-back and copy-back cycles. This is required due to the amount of time it takes for CPU data to be valid during subsequent cycles of a burst. Furthermore, if the DRAM width for the bank receiving the write- back or copy-back is 16 bits, the added wait state occurs only between DWORDs. | Add note text.                                                                                  |

| 3-16  | DRAM Refresh Control<br>Register, Index 05h;<br>bits 1–0 description                                             | When the 32-KHz clock is used<br>Thus, selecting the divide by 1 option<br>results in a refresh interval of<br>15.6 ms. For the divide by 2, 4, and 8<br>selections, the refresh intervals are<br>31.2 ms, 62.5 ms, and 125 ms<br>respectively. | When the 32-KHz clock is used Thus, selecting the divide by 1 option results in a refresh interval of 15.6 $\mu$ s. For the divide by 2, 4, and 8 selections, the refresh intervals are 31.2 $\mu$ s, 62.5 $\mu$ s, and 125 $\mu$ s respectively.                                                                                                                                                                          | Change all times to microseconds (μs).                                                          |

| 3-20  | Non-Cacheable<br>Window 0 Address/<br>Attributes/SMM<br>Register, Index 11h;<br>default bit values in<br>diagram | 0000000                                                                                                                                                                                                                                         | x000000                                                                                                                                                                                                                                                                                                                                                                                                                    | "x" = non-<br>deterministic.                                                                    |

| 3-23  | Cache and VL<br>Miscellaneous<br>Register, Index 14h;<br>bit 4 VL_RESET<br>description                           | Vesa Local Bus Reset 0 = VL_RESET deasserted 1 = VL_RESET asserted                                                                                                                                                                              | Vesa Local Bus Reset  0 = VL_RST signal deasserted  1 = VL_RST signal asserted                                                                                                                                                                                                                                                                                                                                             | Vesa local bus reset signal name is VL_RST.                                                     |

| 3-26  | Linear ROMCS0/<br>Shadow Register,<br>Index 21h; default bit<br>values in diagram                                | x000000                                                                                                                                                                                                                                         | 000000                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit 7 default is zero.  Note: Bit 6 and bits 4–1 are reserved in the ÉlanSC410 microcontroller. |

| 3-31  | ROMCS0 Configuration<br>Register B, Index 24h;<br>bits 4–3 description                                           | 00 = 0 wait states                                                                                                                                                                                                                              | 00 = Reserved—Not Valid                                                                                                                                                                                                                                                                                                                                                                                                    | Zero wait states not supported for Fast ROM.                                                    |

|       | ROMCS0 Configuration<br>Register B, Index 24h;<br>bits 2–0 description                                           | 000 = 0 wait states                                                                                                                                                                                                                             | 000 = Reserved—Not Valid                                                                                                                                                                                                                                                                                                                                                                                                   | Zero wait states not supported for Fast ROM.                                                    |

| 3-33  | ROMCS1 Configuration<br>Register A, Index 25h;<br>bits 2–1 description                                           | These two bits can be read back to determine the ROMCS1 data bus width which is set via pin strapping options, and latched at power-on reset.                                                                                                   | These two bits can be read back to determine the ROMCS1 data bus width.                                                                                                                                                                                                                                                                                                                                                    | Delete reference to pin strapping (which applies to ROMCS0 only).                               |

Table 1. Corrections to the Élan™SC400 Microcontroller Register Set Reference Manual (Continued)

| Page | Item                                                                   | Original Text                                                                                                                                 | Change To                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Comment                                                                                  |

|------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 3-34 | ROMCS1 Configuration<br>Register B, Index 26h;<br>bits 4–3 description | 00 = 0 wait states                                                                                                                            | 00 = Reserved—Not Valid                                                                                                                                                                                                                                                                                                                                                                                                                                          | Zero wait states not supported for Fast ROM.                                             |

|      | ROMCS1 Configuration<br>Register B, Index 26h;<br>bits 2–0 description | 000 = 0 wait states                                                                                                                           | 000 = Reserved—Not Valid                                                                                                                                                                                                                                                                                                                                                                                                                                         | Zero wait states not supported for Fast ROM.                                             |

| 3-36 | ROMCS2 Configuration<br>Register A, Index 27h;<br>bits 2–1 description | These two bits can be read back to determine the ROMCS2 data bus width which is set via pin strapping options, and latched at power-on reset. | These two bits can be read back to determine the ROMCS2 data bus width.                                                                                                                                                                                                                                                                                                                                                                                          | Delete reference<br>to pin strapping<br>(which applies to<br>ROMCSO only).               |

| 3-37 | ROMCS2 Configuration<br>Register B, Index 28h;<br>bits 4–3 description | 00 = 0 wait states                                                                                                                            | 00 = Reserved—Not Valid                                                                                                                                                                                                                                                                                                                                                                                                                                          | Zero wait states<br>not supported<br>for Fast ROM.                                       |

|      | ROMCS2 Configuration<br>Register B, Index 28h;<br>bits 2–0 description | 000 = 0 wait states                                                                                                                           | 000 = Reserved—Not Valid                                                                                                                                                                                                                                                                                                                                                                                                                                         | Zero wait states not supported for Fast ROM.                                             |

| 3-44 | Pin Mux Register A,<br>Index 38h; diagram, (bit<br>5 column)           | Reserved<br>0<br>R/W                                                                                                                          | Reserved<br>x                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Correction.                                                                              |

|      | Pin Mux Register A,<br>Index 38h; bit 5<br>description                 | Reserved                                                                                                                                      | Reserved During read/modify/write operations, software must preserve this bit.                                                                                                                                                                                                                                                                                                                                                                                   | Correct omission.                                                                        |

|      | Pin Mux Register A,<br>Index 38h; bits 2–1<br>descriptions             | Select GPIO or ISA PIRQx 0 = 1 = ISA signal is available                                                                                      | Select GPIO or PIRQx<br>0 =<br>1 = PIRQx signal                                                                                                                                                                                                                                                                                                                                                                                                                  | "ISA PIRQ" is<br>misleading. The<br>PIRQ pins can<br>be assigned to<br>other interrupts. |

|      | Pin Mux Register A,<br>Index 38h;<br>Programming Notes                 | Programming Notes                                                                                                                             | Programming Notes Bit 0 of this register must be set in order to use most ISA I/O peripherals. This is because it enables the AEN signal which, although listed in the DMA signal group, is generated by the DMA controller for consumption by all other ISA I/O devices which are not part of the current DMA transfer. These I/O devices should ignore I/O cycles on the bus if AEN is active because it means that fly-by DMA is occurring, not an I/O cycle. | Clarify. Bit 0 is<br>not just for ISA<br>DMA devices.                                    |

Table 1. Corrections to the Élan™SC400 Microcontroller Register Set Reference Manual (Continued)

| Page | Item                                                                                      | Original Text                                                                                                                                                                                                                                                                                                                                                                                                                 | Change To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Comment                                                                                                                                 |

|------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 3-53 | PMU Present and Last<br>Mode Register, Index<br>41h; bit 6 description                    | Set this bit to immediately time out the current mode timer. This bit does not need to be cleared and is not read back. Software should not invoke this feature for at least 15 microseconds after a wake-up from Suspend mode. Software can read the last mode from bits 5–3 of this register and delay 15 microseconds if the last mode was Suspend mode before setting this bit.                                           | Set this bit to force an immediate time-out of the current mode timer, causing the PMU to drop to the next lower speed. This bit does not need to be cleared and is not read back. This function is designed for debugging power management software.  Software should not invoke this feature for at least one 32-KHz clock cycle (30.5 µs) after a wake-up from Suspend mode. Software can read the last mode from bits 5–3 of this register and delay 30.5 µs if the last mode was Suspend mode before setting this bit. | Expand description. Increase delay. Forced time-out might be missed (bit not latched) if used too soon after wake-up from Suspend mode. |

| 3-57 | Wake-Up Pause/High-<br>Speed Clock Timers<br>Register, Index 45h;<br>bits 2–0 description | Timer value to count down after a wake up is sensed and the PLLs are started up (if necessary) and the GPIO_CSx signals are switched to High-Speed (or Low-Speed) mode levels (for those GPIO_CSx signals that are programmed to change based on PMU mode) to allow the power supplies to stabilize before the ÉlanSC400 microcontroller starts driving its outputs or using its inputs. Read returns the last value written. | Selects the required delay from the time a wake-up is sensed and the PLLs are started up to allow the power supplies to stabilize before the microcontroller begins driving its outputs or using its inputs. Read returns the last value written.                                                                                                                                                                                                                                                                           | Rewrite. Remove reference to programmed GPIO_CSx signals. All chip functions are delayed.                                               |