# **AMD-645**<sup>™</sup>

# Peripheral Bus Controller

**Data Sheet**

#### **Preliminary Information**

#### © 1997 Advanced Micro Devices, Inc. All rights reserved.

Advanced Micro Devices, Inc. ("AMD") reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied warranty of merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or systems without AMD's written approval. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products except as provided in AMD's Terms and Conditions of Sale for such product.

#### **Trademarks**

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

AMD-640, AMD-645, K86, AMD-K5, and AMD-K6 are trademarks of Advanced Micro Devices, Inc.

MMX is a trademark of the Intel Corporation.

Microsoft and Windows are registered trademarks, and Windows NT is a trademark of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## **Contents**

| 1 | Features  |         |                                     | 1-1           |

|---|-----------|---------|-------------------------------------|---------------|

|   |           | 1.1     | Enhanced IDE Controller             | . 1-1         |

|   |           | 1.2     | Universal Serial Bus Controller     | . 1-2         |

|   |           | 1.3     | Plug-N-Play Support                 | . 1-2         |

|   |           | 1.4     | Sophisticated Power Management      | . 1-2         |

|   |           | 1.5     | PC97-Compliant PCI-to-ISA Bridge    | <b>. 1-</b> 3 |

| 2 | Overview  | 1       |                                     | 2-1           |

|   |           | 2.1     | PCI-to-ISA Bridge                   | . 2-1         |

|   |           |         | 2.1.1 PCI Bus Master Mode           |               |

|   |           | 2.2     | ISA Controller                      | <b>. 2-</b> 3 |

|   |           | 2.3     | EIDE Controller                     | . 2-5         |

|   |           | 2.4     | Universal Serial Bus                | . 2-6         |

|   |           | 2.5     | Power Management                    | . 2-7         |

| 3 | Ordering  | Inforn  | nation                              | 3-1           |

| 4 | Signal De | scripti | ons                                 | 4-1           |

|   |           | 4.1     | PCI Bus Interface                   | . 4-1         |

|   |           | 4.2     | ISA Bus Interface                   | . 4-4         |

|   |           | 4.3     | Ultra DMA-33 Enhanced IDE Interface | <b>4-1</b> 0  |

|   |           | 4.4     | XD Bus Interface                    | <b>4-1</b> 3  |

|   |           | 4.5     | Plug-N-Play Support                 | <b>4-1</b> 4  |

|   |           | 4.6     | Universal Serial Bus Interface      | <b>4-1</b> 5  |

|             | 4.7        | Power Management                                                                                                                                                                                                                         | 4-15                                      |

|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|             | 4.8        | Power and Ground                                                                                                                                                                                                                         | 4-16                                      |

|             | 4.9        | Internal Real-Time Clock                                                                                                                                                                                                                 | 4-16                                      |

|             | 4.10       | Keyboard Interface                                                                                                                                                                                                                       | 4-17                                      |

|             | 4.11       | CPU Interface                                                                                                                                                                                                                            | 4-18                                      |

|             | 4.12       |                                                                                                                                                                                                                                          |                                           |

|             | 10         |                                                                                                                                                                                                                                          |                                           |

| 5 Functiona | ii Oper    | rations                                                                                                                                                                                                                                  | 5-1                                       |

|             | <b>5.1</b> | PCI Bus-Initiated Accesses                                                                                                                                                                                                               | 5-1                                       |

|             |            | 5.1.1 Overview          5.1.2 Bus Cycle Decoder                                                                                                                                                                                          |                                           |

|             | 5.2        | PCI Bus Commands                                                                                                                                                                                                                         | 5-2                                       |

|             |            | 5.2.1 Interrupt Acknowledge 5.2.2 Special Bus Cycles 5.2.3 I/O Read/Write 5.2.4 Memory Read/Write 5.2.5 Configuration Read/Write 5.2.6 Memory Read Multiple 5.2.7 Dual Address Line 5.2.8 Memory Read Line 5.2.9 Memory Write Invalidate | 5-3<br>5-3<br>5-5<br>5-16<br>5-16<br>5-16 |

|             | 5.3        | PCI Bus Features                                                                                                                                                                                                                         | 5-17                                      |

|             |            | 5.3.1 Back-to-Back Cycles                                                                                                                                                                                                                | 5-17                                      |

|             | <b>5.4</b> | ISA Bus-Initiated Cycles                                                                                                                                                                                                                 | 5-18                                      |

|             |            | 5.4.1 DMA-Initiated Cycles                                                                                                                                                                                                               |                                           |

|             | 5.5        | PCI Bus Arbitration                                                                                                                                                                                                                      | <b>5-2</b> 3                              |

|             | 5.6        | I/O and Memory Mapping                                                                                                                                                                                                                   | 5-23                                      |

|             |            | 5.6.1 I/O Mapping                                                                                                                                                                                                                        | 5-25                                      |

*iv* Table of Contents

| 5.7         | Clock Generation5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <b>5.</b> 8 | Direct Memory Access5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|             | 5.8.1       DMA Controllers       5-29         5.8.2       DMA Controller Registers       5-29         5.8.3       Middle Address Bit Latches       5-31         5.8.4       Page Registers       5-32         5.8.5       DMA Address Generation       5-32         5.8.6       Type F DMA       5-36         5.8.7       DMA Channel Mapping Registers       5-36         5.8.8       Ready Control Logic       5-37         5.8.9       External Cascading       5-38 |  |  |  |  |  |  |

| 5.9         | Distributed DMA Support5-39                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 5.10        | Ultra DMA Support5-39                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|             | 5.10.1 Ultra DMA Read Burst Command5-415.10.2 Ultra DMA Write Burst Command5-425.10.3 Slave DMA Channel5-465.10.4 DMA Control Registers5-475.10.5 DMA Software Commands5-485.10.6 DMA Addressing5-495.10.7 PCI Slave DMA Configuration Registers5-50                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 5.11        | ISA Bus Refresh Cycle Types5-51                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 5.12        | Fast IDE/EIDE Interface5-52                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | 5.12.1 IDE Drive Registers       5-52         5.12.2 PCI Cycles       5-53         5.12.3 DMA Bus Mastering       5-54         5.12.4 IDE Channel Arbitration       5-56         5.12.5 IDE Configuration Registers       5-57                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 5.13        | Power Management Support5-58                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|             | 5.13.1 Power Management Subsystem5-585.13.2 Power Plane Management5-595.13.3 Power Management Events5-615.13.4 Legacy Management Timers5-645.13.5 System Primary and Secondary Events5-655.13.6 Peripheral Events5-66                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

Table of Contents v

| 6 | Initializat | ion | ·                                                                                                                                        | 6-1                         |

|---|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|   |             | 6.1 | Legacy I/O Registers                                                                                                                     | 6-1                         |

|   |             | 6.2 | PCI Function 0 Registers—PCI-to-ISA Bridge                                                                                               | 6-5                         |

|   |             | 6.3 | PCI Function 1 Registers—IDE Control                                                                                                     | 6-8                         |

|   |             | 6.4 | PCI Function 2 Registers—USB Controller6                                                                                                 | <b>6-1</b> 0                |

|   |             | 6.5 | PCI Function 3 Registers—Power Management6                                                                                               | 5-12                        |

|   |             |     | 6.5.1 Power Management Configuration Space Registers 6 6.5.2 Power Management I/O Space Registers                                        |                             |

| 7 | Registers   |     |                                                                                                                                          | 7-1                         |

|   |             | 7.1 | PCI Mechanism #1                                                                                                                         | 7-1                         |

|   |             | 7.2 | Legacy I/O Registers                                                                                                                     | 7-2                         |

|   |             |     | 7.2.1 Keyboard Controller Registers                                                                                                      | 7-8<br>7-10<br>7-10<br>7-12 |

|   |             | 7.3 | Function 0 Registers (PCI-ISA Bridge)                                                                                                    | <b>'-15</b>                 |

|   |             |     | 7.3.1 Function 0 PCI Configuration Space Header77.3.2 ISA Bus Control77.3.3 Plug-N-Play Control Registers77.3.4 Distributed DMA Control7 | 7-17<br>7-24                |

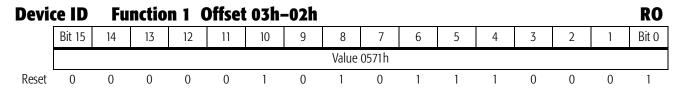

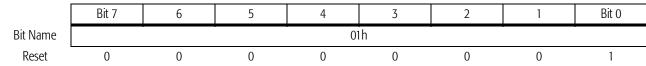

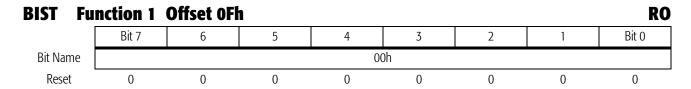

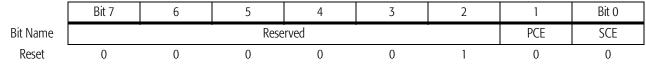

|   |             | 7.4 | Function 1 Registers (Enhanced IDE Controller)7                                                                                          | <b>7-2</b> 9                |

|   |             |     | 7.4.1 Function 1 PCI Configuration Space Header                                                                                          | 7-36                        |

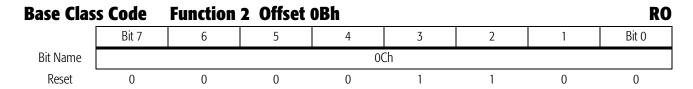

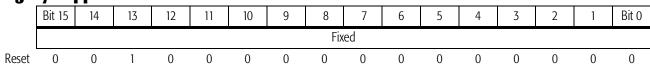

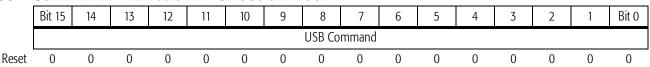

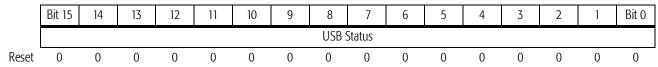

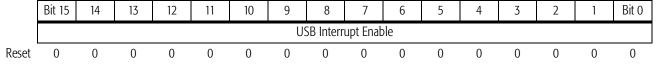

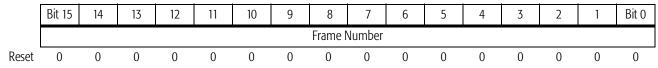

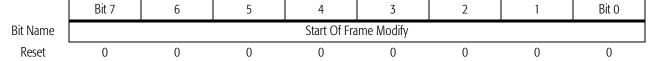

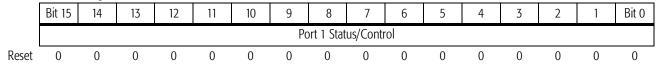

|   |             | 7.5 | Function 2 Registers (USB Controller)                                                                                                    | <sup>7</sup> -44            |

|   |             |     | 7.5.1 Function 2 PCI Configuration Space Header                                                                                          | 7-48                        |

vi Table of Contents

| AMD-645 Per | ipheral B | Bus Controll | ler Data Sheet |

|-------------|-----------|--------------|----------------|

|-------------|-----------|--------------|----------------|

|    | 7.6             | Function 3 Registers (Power Management)7-5                         | 1  |

|----|-----------------|--------------------------------------------------------------------|----|

|    |                 | <ul> <li>7.6.1 Function 3 PCI Configuration Space Header</li></ul> | 54 |

| 8  | Electrical Data | 8-                                                                 | -1 |

|    | 8.1             | Absolute Ratings8-                                                 | -1 |

|    | 8.2             | Operating Ranges8                                                  | -2 |

|    | 8.3             | DC Characteristics8                                                | -3 |

|    | 8.4             | Power Dissipation8                                                 | -4 |

| 9  | Switching Chara | ecteristics 9-                                                     | ·1 |

|    | 9.1             | PCLK Switching Characteristics9                                    | -2 |

|    | 9.2             | Valid Delay, Float, Setup, and Hold Timings9                       | -6 |

|    | 9.3             | PCI Interface Timing9                                              | -7 |

|    | 9.4             | ISA Interface Timing9                                              | -8 |

|    | 9.5             | DMA Interface Timing9-1                                            | 8  |

|    | 9.6             | X-Bus Interface Timing9-2                                          | 24 |

|    | 9.7             | EIDE Interface9-2                                                  | 26 |

|    | 9.8             | Ultra DMA-33 IDE Bus Interface Timing9-3                           | 0  |

| 10 | IBIS Models     | 10-                                                                | ·1 |

|    | 10.1            | I/O Buffer Model10-                                                | -2 |

|    | 10.2            | I/O Model Application Note10-                                      | -3 |

|    | 10.3            | I/O Buffer AC and DC Characteristics10-                            | -3 |

|    | 10.4            | References                                                         | -3 |

Table of Contents vii

21095B/0-June 1997

| AMD-645    | Peripheral   | Rus | Controller | Data Sh  | eet |

|------------|--------------|-----|------------|----------|-----|

| עדט שווווו | i Cilbiiciai | Dus | COITG OHCE | Duta Jii | CCL |

| 11 | Pin Designations |                       | 11-1   |

|----|------------------|-----------------------|--------|

|    | 11.1             | Pin Designation Table | . 11-1 |

|    | 11.2             | Pin Diagram           | . 11-3 |

| 12 | Package Specific | ations                | 12-1   |

*viii* Table of Contents

## **List of Figures**

| Diame 1.1    | AMD CAO Chinast Crustom Blook Diagnom            | 1 1   |

|--------------|--------------------------------------------------|-------|

| Figure 1-1.  | AMD 645 Parish and Res Controller Block Diagram  |       |

| Figure 2-1.  | AMD-645 Peripheral Bus Controller Block Diagram  |       |

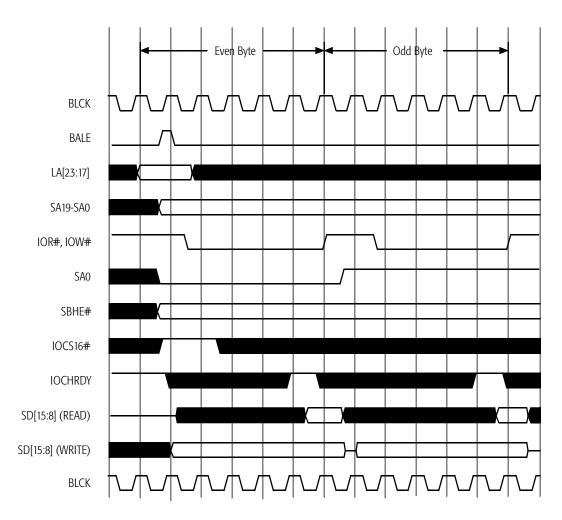

| Figure 5-1.  | I/O Access                                       |       |

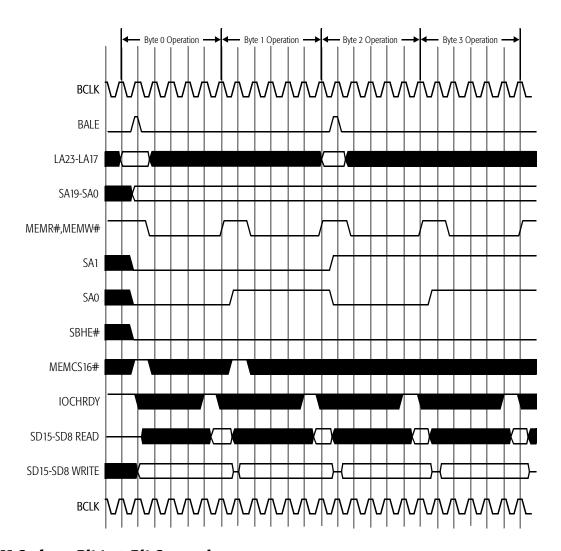

| Figure 5-2.  | I/O Cycle 16-Bit to 8-Bit Conversion             |       |

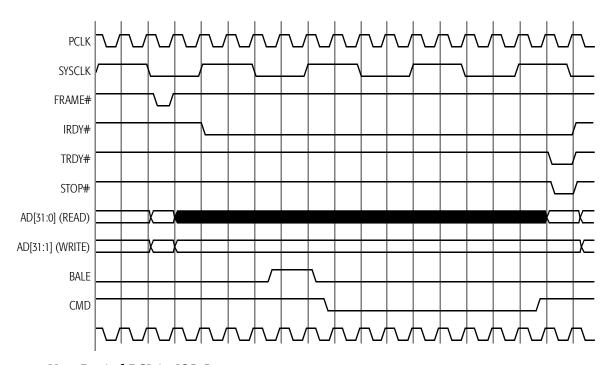

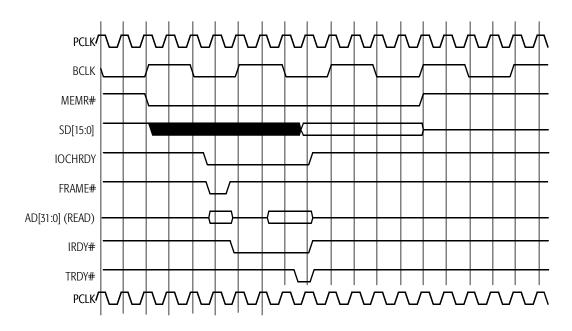

| Figure 5-3.  | Non-Posted PCI-to-ISA Access                     |       |

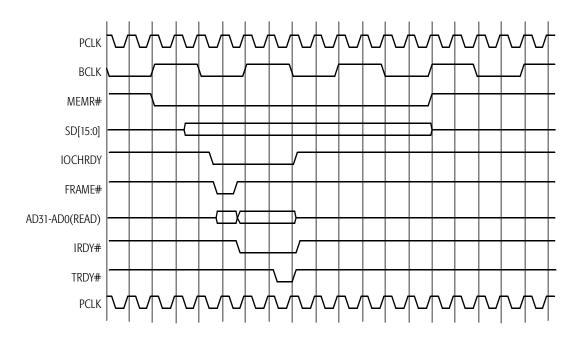

| Figure 5-4.  | Posted PCI-to-Memory Write                       |       |

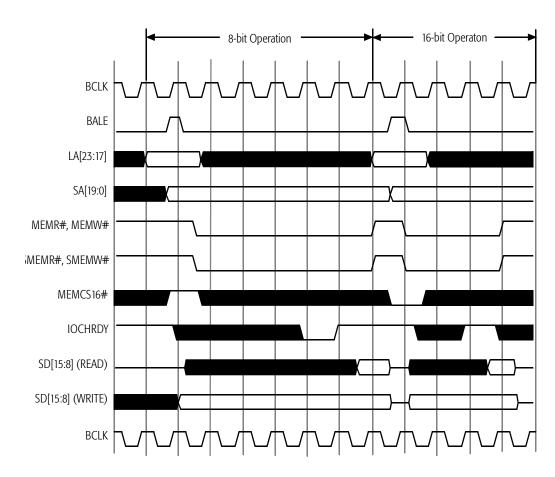

| Figure 5-5.  | ISA Bus Memory Access Cycle                      |       |

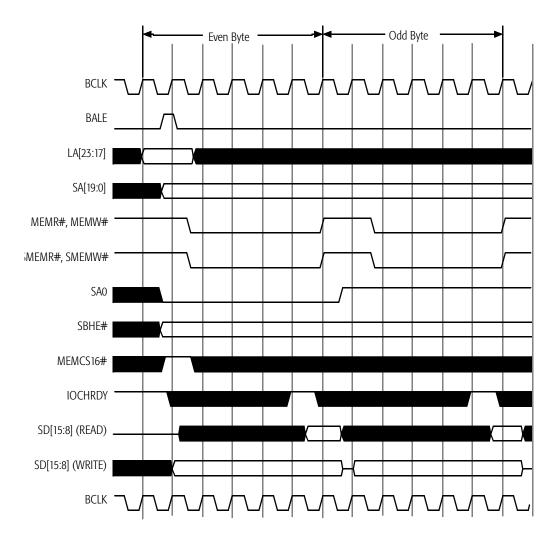

| Figure 5-6.  | ISA Bus Memory Cycle: 16-Bit to 8-Bit Conversion |       |

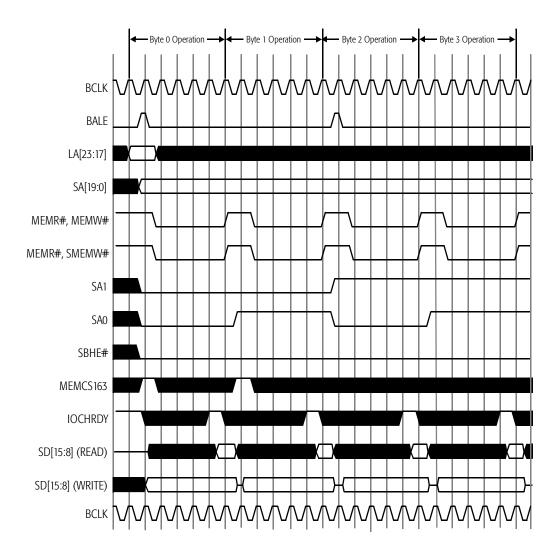

| Figure 5-7.  | Memory Cycle 32-Bit to 8-Bit Conversion          |       |

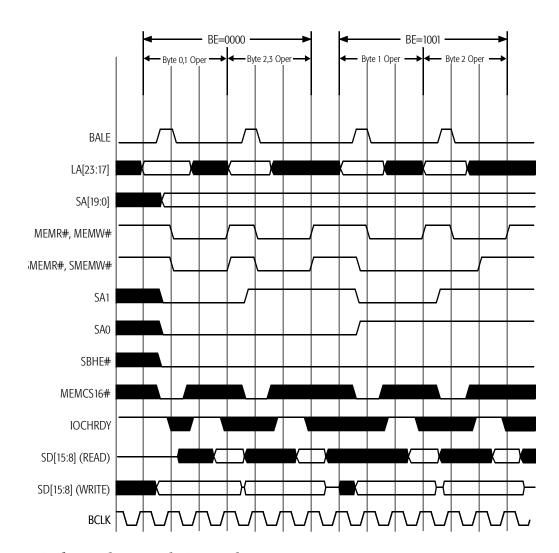

| Figure 5-8.  | Memory Cycle 32-Bit to 16-Bit Conversion         |       |

| Figure 5-9.  | ROM Access                                       |       |

| Figure 5-10. | ROM Cycle 32-Bit to 8-Bit Conversion             |       |

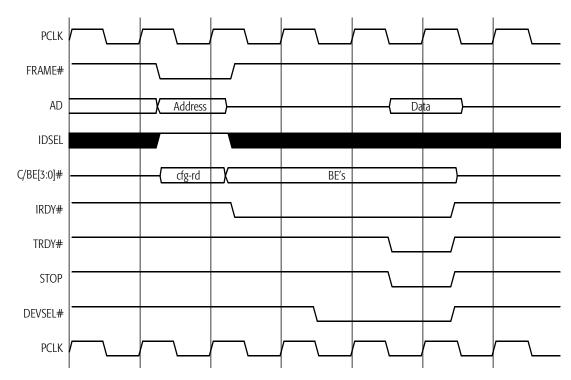

| Figure 5-11. | Configuration Read Cycle                         |       |

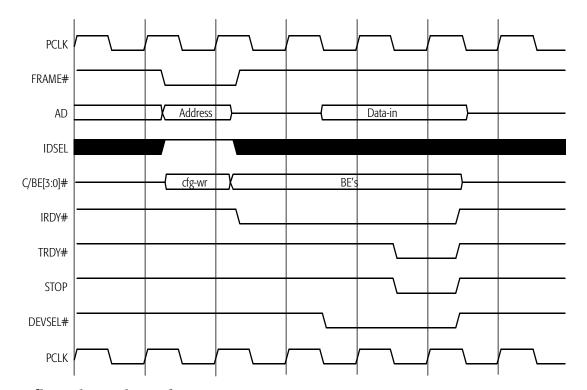

| Figure 5-12. | Configuration Write Cycle                        |       |

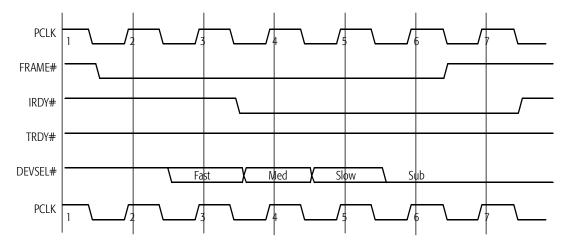

| Figure 5-13. | Subtractive Decode Timing                        |       |

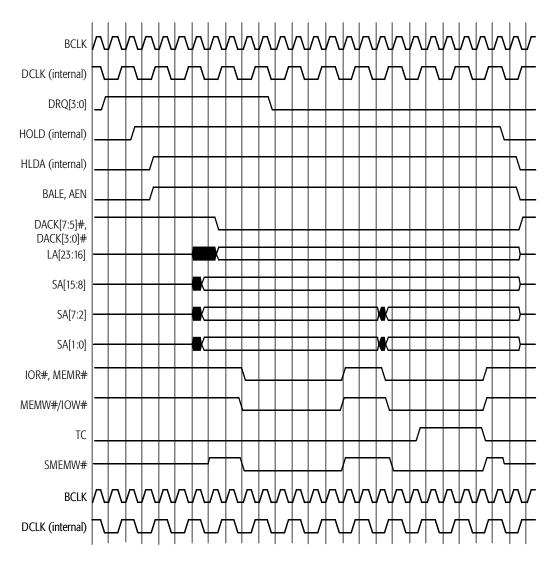

| Figure 5-14. | DMA Transfer Cycle                               |       |

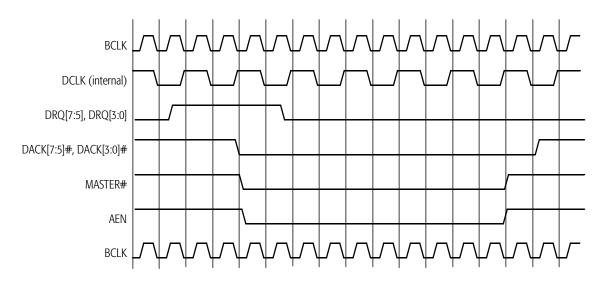

| Figure 5-15. | ISA Bus Master Arbitration Timing                |       |

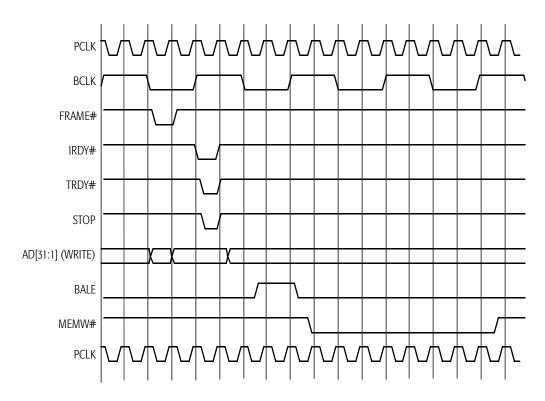

| Figure 5-16. | ISA Bus Master-to-PCI Memory (Memory Read)       |       |

| Figure 5-17. | ISA Bus Master-to-PCI Memory (Memory Write)      |       |

| Figure 5-18. | Type F DMA Timing                                |       |

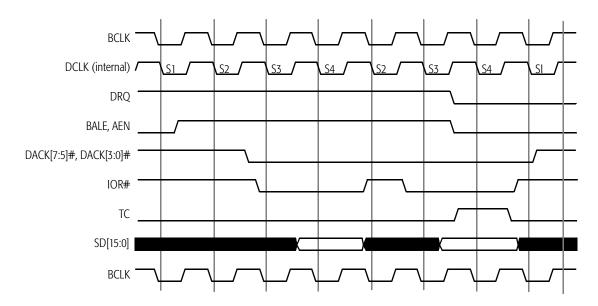

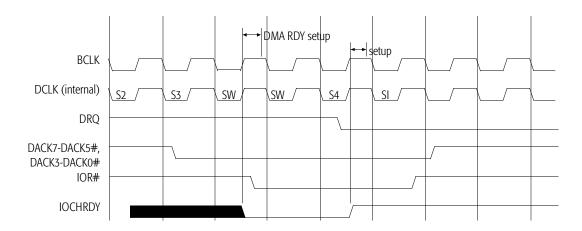

| Figure 5-19. | DMA Ready Timing                                 | 5-38  |

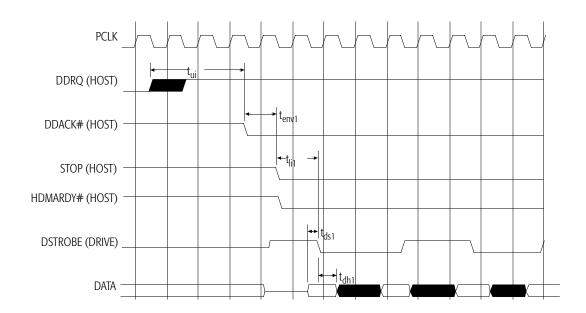

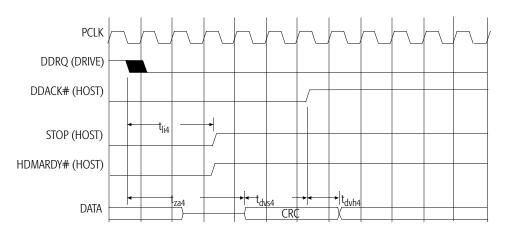

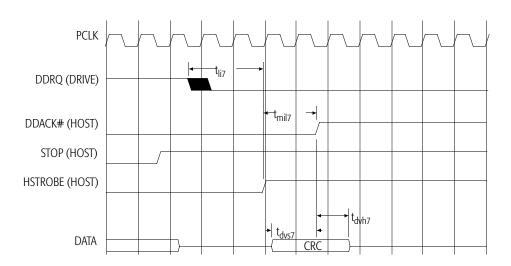

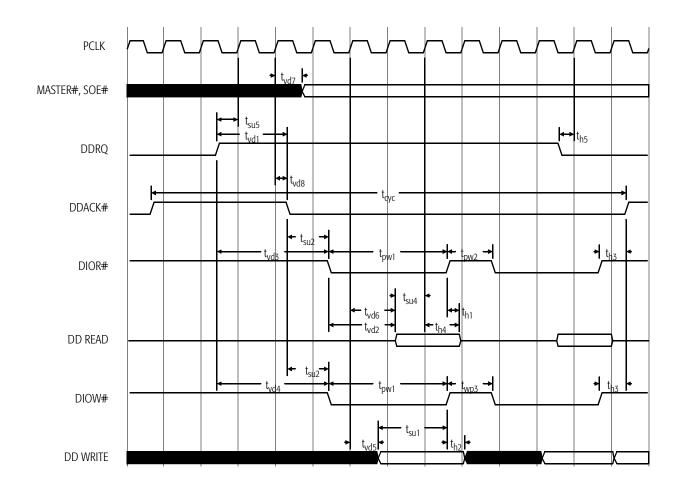

| Figure 5-20. | Ultra DMA-33 IDE Read Burst                      | 5-41  |

| Figure 5-21. | Pausing a DMA Burst                              | 5-42  |

| Figure 5-22. | Drive Terminating a DMA Read Burst               | 5-42  |

| Figure 5-23. | Host Terminating DMA Burst During Read Command   | 5-43  |

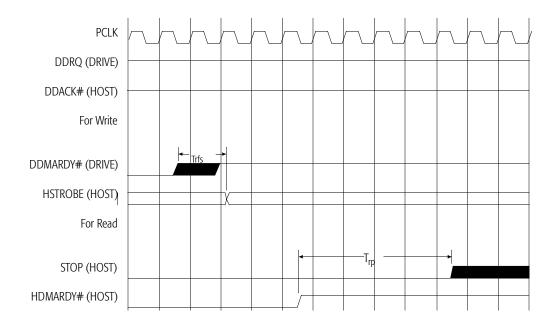

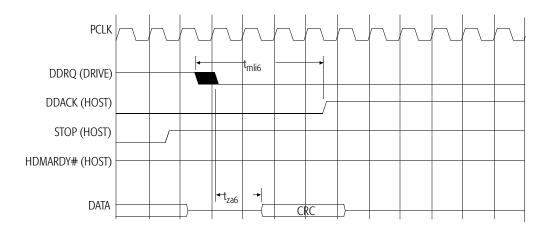

| Figure 5-24. | Ultra DMA-33 IDE Write Burst                     | 5-44  |

| Figure 5-25. | Drive Terminating DMA Burst During Write Command | 5-45  |

| Figure 5-26. | Host Terminating DMA Burst During Write Command  | 5-45  |

| Figure 5-27. | PIO Cycle                                        | 5-57  |

| Figure 5-28. | IDE Multiword DMA Cycle                          | 5-58  |

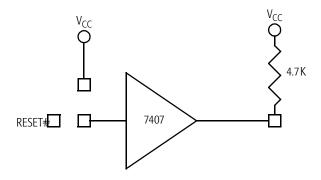

| Figure 7-1.  | Strap Option Circuit                             | 7-27  |

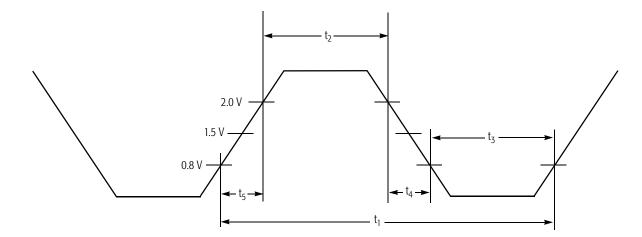

| Figure 9-1.  | PCLK Waveform                                    | . 9-3 |

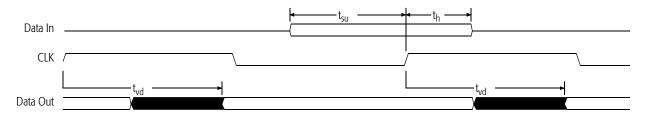

| Figure 9-2.  | Setup, Hold, and Valid Delay Timing Diagram      | . 9-6 |

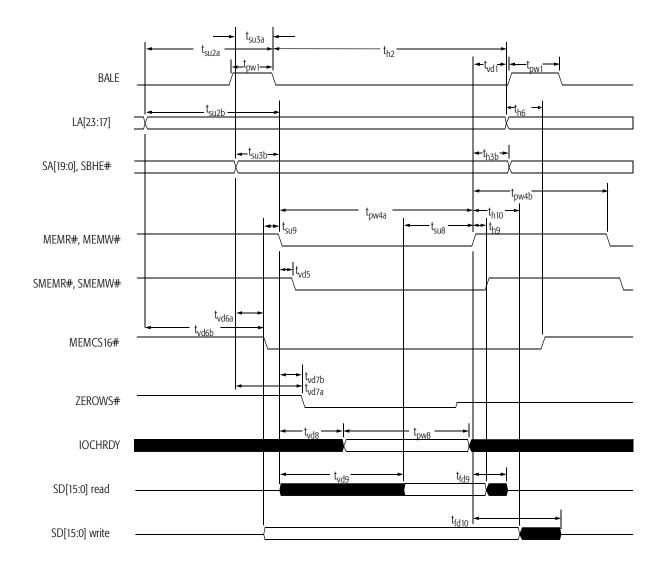

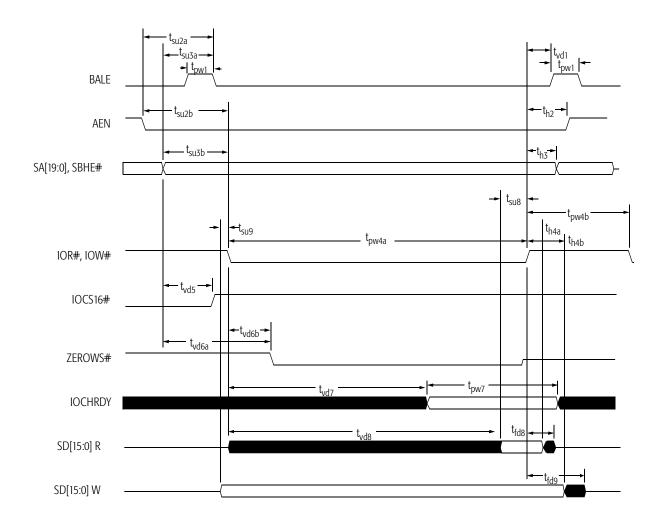

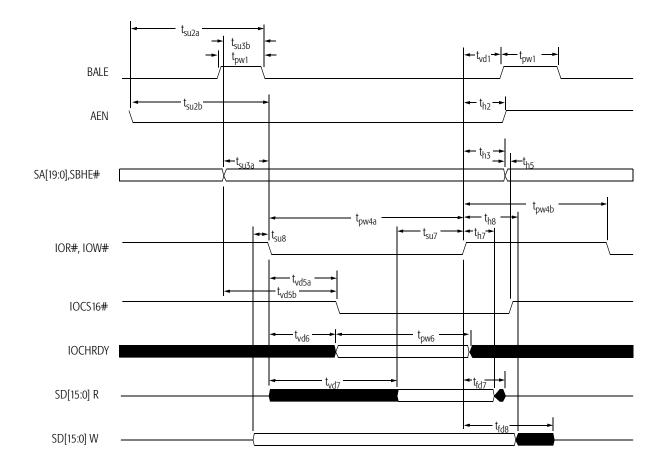

| Figure 9-3.  | ISA Master Interface Timing                      | . 9-9 |

| Figure 9-4.  | ISA 8-Bit Slave Interface Timing                 | 9-11  |

| Figure 9-5.  | ISA 16-Bit Slave Interface Timing                |       |

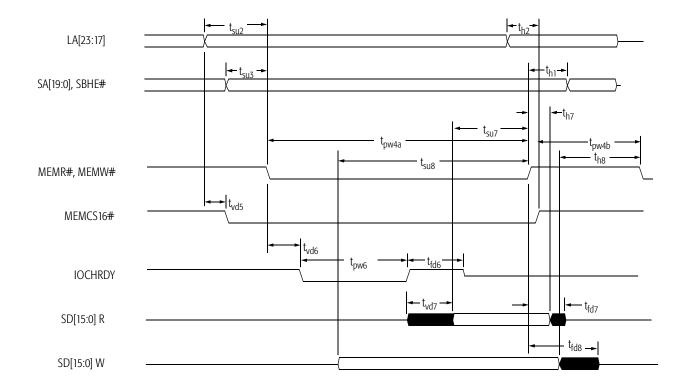

| Figure 9-6.  | ISA Master-to-PCI Access Timing                  |       |

| Figure 9-7.  | Other ISA Master Timing                          |       |

List of Figures ix

### **Preliminary Information**

## AMD-645 Peripheral Bus Controller Data Sheet

21095B/0-June 1997

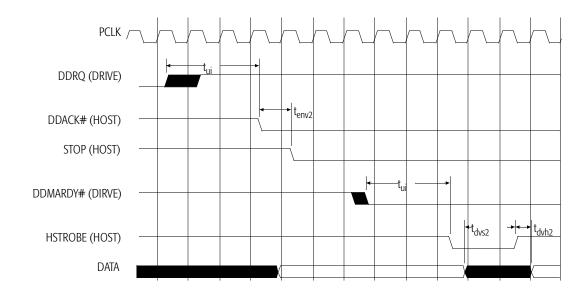

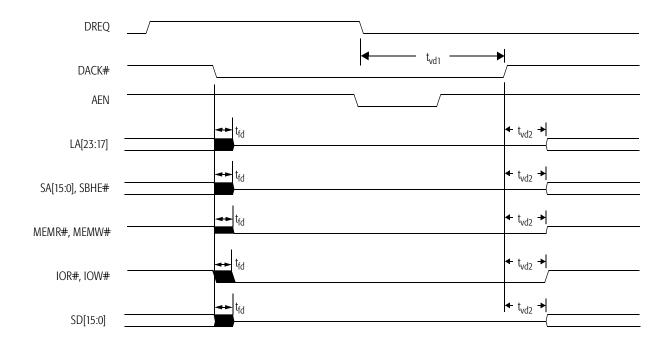

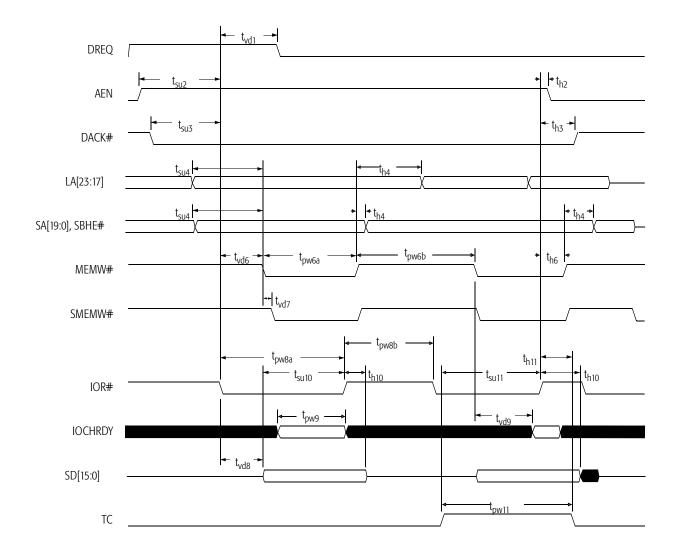

| Figure 9-8.  | DMA Read Cycle Timing 9-19                          |

|--------------|-----------------------------------------------------|

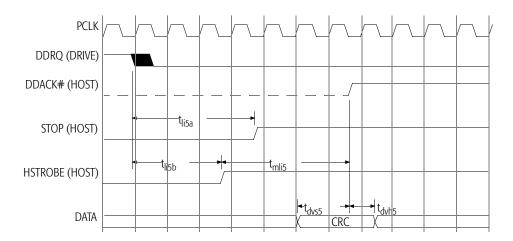

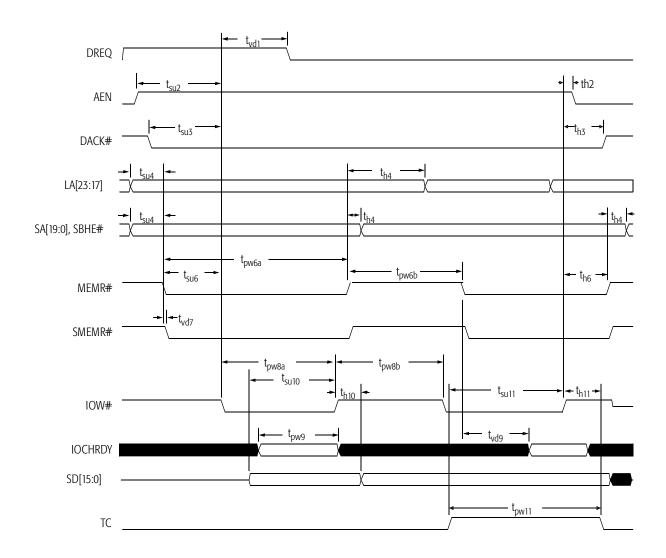

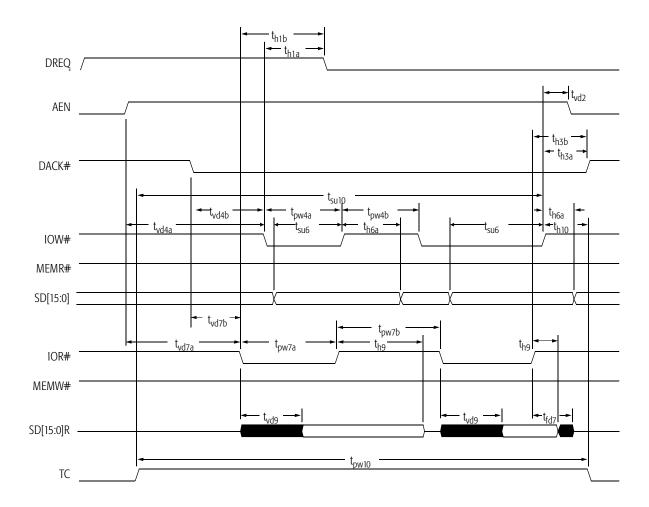

| Figure 9-9.  | DMA Write Cycle Timing 9-21                         |

| Figure 9-10. | Type F DMA Interface Timing 9-23                    |

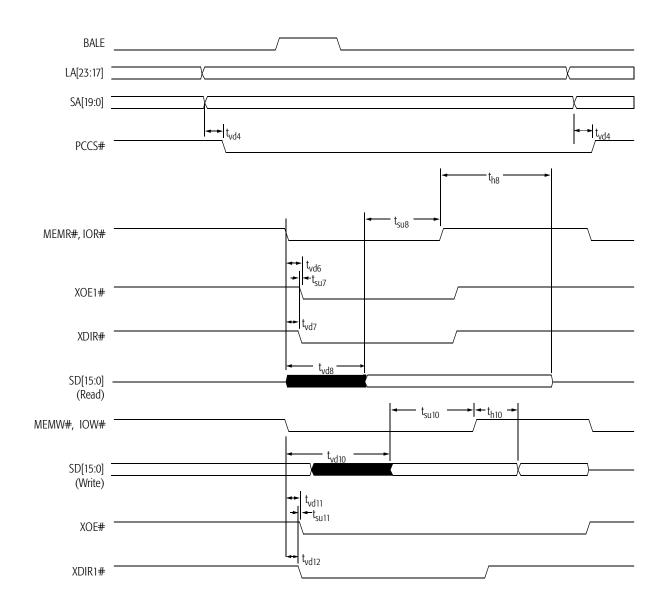

| Figure 9-11. | X-Bus Interface Timing 9-25                         |

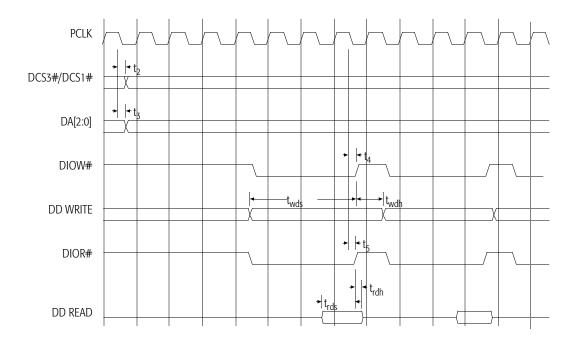

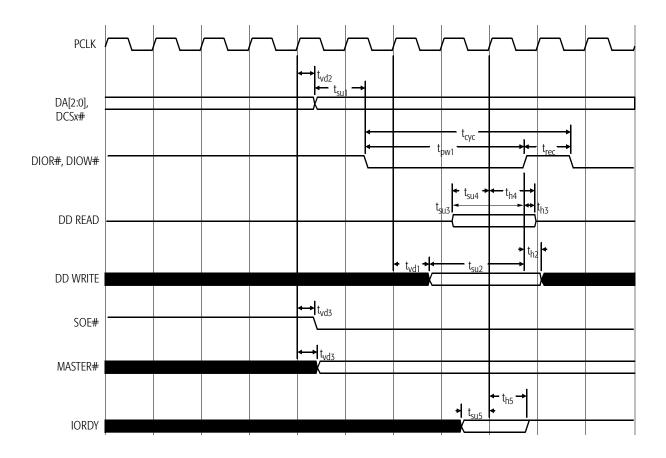

| Figure 9-12. | EIDE PIO 9-27                                       |

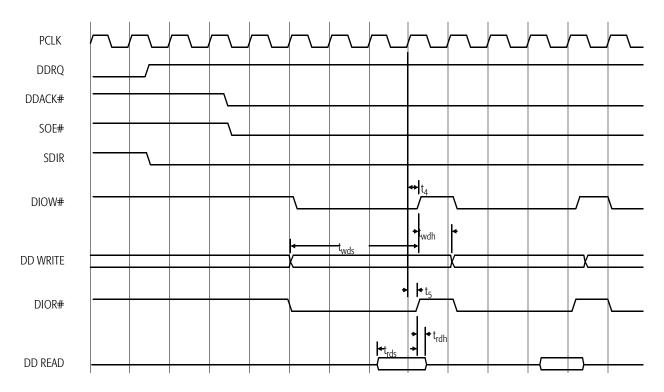

| Figure 9-13. | EIDE DMA                                            |

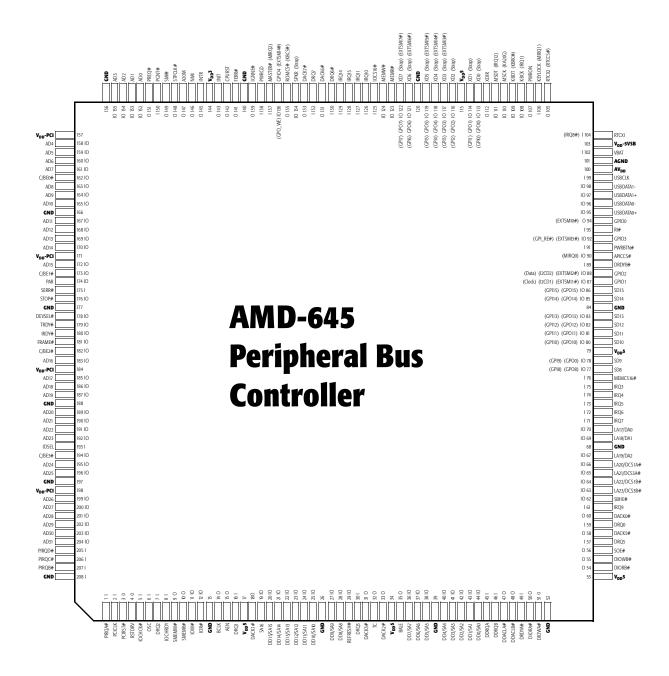

| Figure 11-1. | AMD-645 Peripheral Bus Controller Pin Diagram 11-4  |

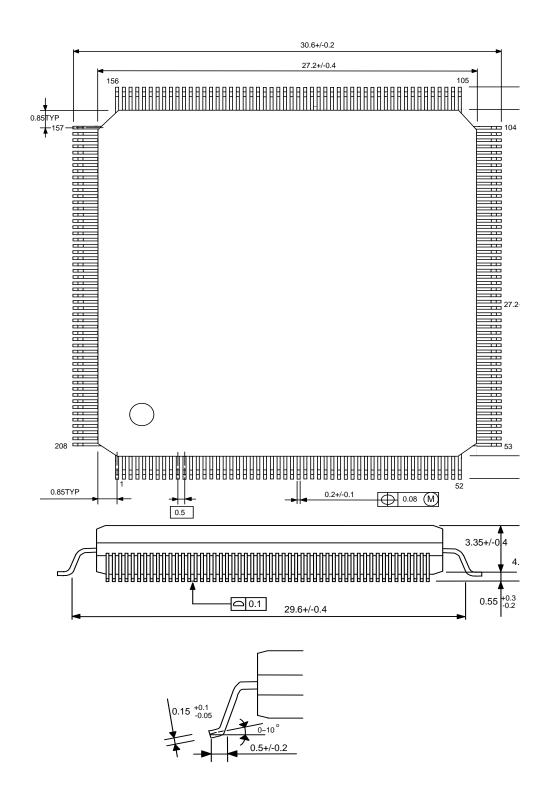

| Figure 12-1. | 208-Pin Plastic Quad Flat Pack Outline Drawing 12-2 |

x List of Figures

## **List of Tables**

| Table 3-1.  | Valid Combinations                                    | . 3-1 |

|-------------|-------------------------------------------------------|-------|

| Table 4-1.  | Connecting PIRQ Lines to PCI INT Lines                |       |

| Table 5-1.  | PCI Bus Command Encoding and Types                    |       |

| Table 5-2.  | ISA Byte and Word Accesses                            | 5-14  |

| Table 5-3.  | I/O Fixed Address Mapping                             |       |

| Table 5-4.  | Memory Address Mapping                                | 5-25  |

| Table 5-5.  | ROM Decode Control Register                           |       |

| Table 5-6.  | ISA Bus Clock Select Bit Programming                  | 5-28  |

| Table 5-7.  | Ports 00h–0Fh Master DMA Controller                   | 5-30  |

| Table 5-8.  | Ports 80h–8Fh DMA Page Register Access                | 5-32  |

| Table 5-9.  | DMA Addressing for ISA Bus Accesses (DMA/Slot Bus)    | 5-34  |

| Table 5-10. | DMA Addressing for ISA Bus Accesses (DMA/PCI AD Bus)  | 5-35  |

| Table 5-11. | Type F DMA Control                                    | 5-36  |

|             | Ultra DMA Interface Signals                           |       |

| Table 5-13. | Programming Model for Single Slave DMA Channel        | 5-46  |

|             | DMA Registers                                         |       |

| Table 5-15. | IDE Register Map                                      | 5-52  |

|             | PCI Cycles                                            |       |

| Table 5-17. | SCI/SMI/Resume Control for PM Events                  | 5-63  |

| Table 5-18. | Suspend Resume Events and Conditions                  | 5-63  |

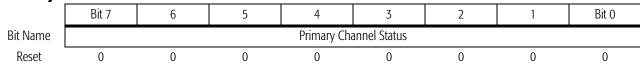

| Table 5-19. | PRI_ACT_STS and PRI_ACT_EN Register Bits              | 5-65  |

| Table 6-1.  | Master DMA Controller Registers                       |       |

| Table 6-2.  | Master Interrupt Controller Registers                 | . 6-2 |

| Table 6-3.  | Timer/Counter Registers                               | . 6-2 |

| Table 6-4.  | Keyboard Controller Registers                         | . 6-2 |

| Table 6-5.  | CMOS/RTC/NNI Registers                                |       |

| Table 6-6.  | DMA Page Registers                                    |       |

| Table 6-7.  | System Control Registers                              |       |

| Table 6-8.  | Slave Interrupt Controller Registers                  |       |

| Table 6-9.  | Slave DMA Controller Registers                        |       |

|             | Configuration Space PCI-to-ISA Header Registers       |       |

|             | ISA Bus Control Registers                             |       |

|             | Plug-n-Play Control Registers                         |       |

|             | Distributed DMA                                       |       |

|             | Configuration Space IDE Header Registers              |       |

|             | Configuration Space IDE Registers                     |       |

|             | IDE Controller I/O Registers                          |       |

|             | Configuration Space USB Header Registers              |       |

|             | Configuration Space USB Registers                     |       |

|             | USB Controller I/O Registers                          |       |

|             | Configuration Space Power Management Header Registers |       |

|             | Configuration Space Power Management Registers        |       |

| Table 6-22. | Basic Power Management Control/Status Registers       | 6-13  |

List of Tables xi

| 1 able 6-23. | Processor Power Management Registers                 | 6-14  |

|--------------|------------------------------------------------------|-------|

| Table 6-24.  | General Purpose Power Management Registers           | 6-14  |

|              | Generic Power Management Registers                   |       |

| Table 6-26.  | General Purpose I/O                                  |       |

| Table 7-1.   | Keyboard Controller Command Codes                    | . 7-4 |

| Table 7-2.   | Traditional Port Pin Definition                      |       |

| Table 7-3.   | Ports 00h–0Fh Master DMA Controller                  | . 7-8 |

| Table 7-4.   | Ports C0h-DFh Slave DMA Controller                   | . 7-9 |

| Table 7-5.   | Ports 80h–8Fh DMA Page Registers                     | . 7-9 |

| Table 7-6.   | Ports 20h-21h Master Interrupt Controller Registers  | 7-10  |

| Table 7-7.   | Ports A0h-A1h Slave Interrupt Controller Registers   | 7-10  |

| Table 7-8.   | Ports 40h–43h Timer/Counter Registers                | 7-12  |

| Table 7-9.   | CMOS Register Summary                                | 7-13  |

| Table 7-10.  | Compatibility Mode vs. Native PCI Mode               | 7-31  |

| Table 7-11.  | FIFO Distribution                                    |       |

| Table 8-1.   | Absolute Maximum Ratings                             | . 8-1 |

| Table 8-2.   | Absolute Ratings                                     |       |

| Table 8-3.   | Operating Ranges                                     | . 8-2 |

| Table 8-4.   | DC Characteristics                                   | . 8-3 |

| Table 8-5.   | Typical and Maximum Power Dissipation                | . 8-4 |

| Table 9-1.   | CLK Switching Characteristics for 33-MHz PCI Bus     | . 9-3 |

| Table 9-2.   | USBCLK Switching Characteristics for 12-MHz USB Bus  | . 9-4 |

| Table 9-3.   | USBCLK Switching Characteristics for 1.5-MHz USB Bus | . 9-4 |

| Table 9-4.   | BCLK Switching Characteristics for 8-MHz Bus         | . 9-5 |

| Table 9-5.   | OSC Switching Characteristics for 14.3182-MHz Bus    | . 9-5 |

| Table 9-6.   | PCI Interface Timing                                 | . 9-7 |

| Table 9-7.   | ISA Master Interface Timing                          | . 9-8 |

| Table 9-8.   | ISA 8-Bit Slave Interface Timing                     | 9-10  |

| Table 9-9.   | ISA 16-Bit Slave Interface Timing                    | 9-12  |

| Table 9-10.  | ISA Master-to-PCI Access Timing                      | 9-14  |

|              | Other ISA Master Timing                              |       |

| Table 9-12.  | DMA Read Cycle Timing                                | 9-18  |

| Table 9-13.  | DMA Write Cycle Timing                               | 9-20  |

| Table 9-14.  | Type F DMA Interface Timing                          | 9-22  |

| Table 9-15.  | X-BUS Interface Timing                               | 9-24  |

| Table 9-16.  | EIDE PIO                                             | 9-26  |

|              | EIDE DMA                                             |       |

| Table 9-18.  | UltraDMA-33 IDE Bus Interface Timing                 | 9-30  |

| Table 11-1   | Functional Grouping                                  | 11-1  |

xii List of Tables

## 1 Features

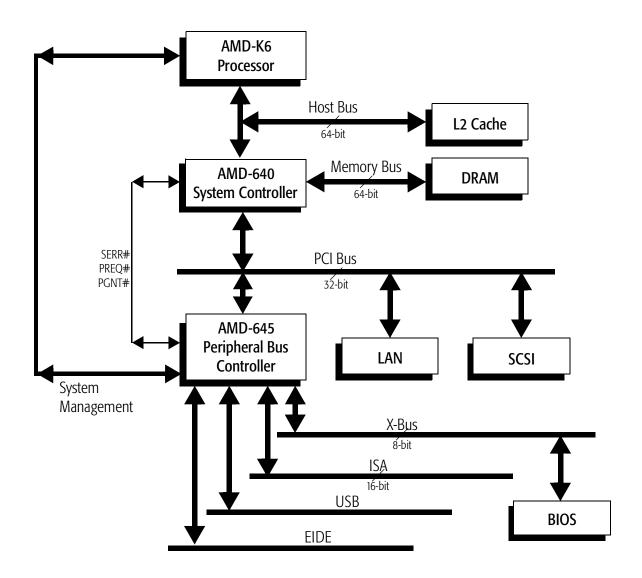

The AMD-640<sup>TM</sup> chipset is a highly integrated system solution designed to deliver superior performance for the AMD-K5<sup>TM</sup> processor, AMD-K6<sup>TM</sup> MMX<sup>TM</sup> enhanced processor, and other Socket 7-compatible processors. The AMD-640 chipset consists of the AMD-640 system controller in a 328-pin BGA package and the AMD-645<sup>TM</sup> peripheral bus controller in a 208-pin PQFP package. The AMD-645 peripheral bus controller features an integrated ISA bus controller, enhanced master mode PCI IDE controller with ultra DMA-33 support, USB controller, keyboard/mouse controller, and real-time clock.

This document describes the features and operation of the AMD-645 peripheral bus controller. For a description of the AMD-640 system controller, see the *AMD-640 System Controller Data Sheet*, order# 21090. Key features of the AMD-645 peripheral bus controller are provided in this section.

### 1.1 Enhanced IDE Controller

- Enhanced master mode PCI IDE controller with Ultra DMA-33 support

- Dual channel master mode PCI supporting four enhanced IDE devices

- Transfer rate up to 33 Mbytes per second to cover PIO mode 4 and multi-word DMA mode 2 drivers, and Ultra DMA-33/ATA-33 interface

- Sixteen levels (doublewords) of prefetch and write buffers

- Interlaced commands between the two channels

- Bus master programming interface for SFF-8038i, rev. 1.0 and Microsoft<sup>®</sup> Windows<sup>®</sup> 95 compliance

- Full scatter-gather capability

- Supports ATAPI-compliant devices

- Supports PCI native and ATA compatibility modes

- Complete software driver support

Features 1-1

## 1.2 Universal Serial Bus Controller

- USB v. 1.0 and Intel Universal HCI v. 1.1-compatible

- Eighteen-level (doubleword) data FIFOs

- Root hub and two function ports with built-in physical layer transceivers

## 1.3 Plug-N-Play Support

- PCI interrupts steerable to any interrupt channel

- Microsoft Windows 95 and Plug-N-Play BIOS compliant

## 1.4 Sophisticated Power Management

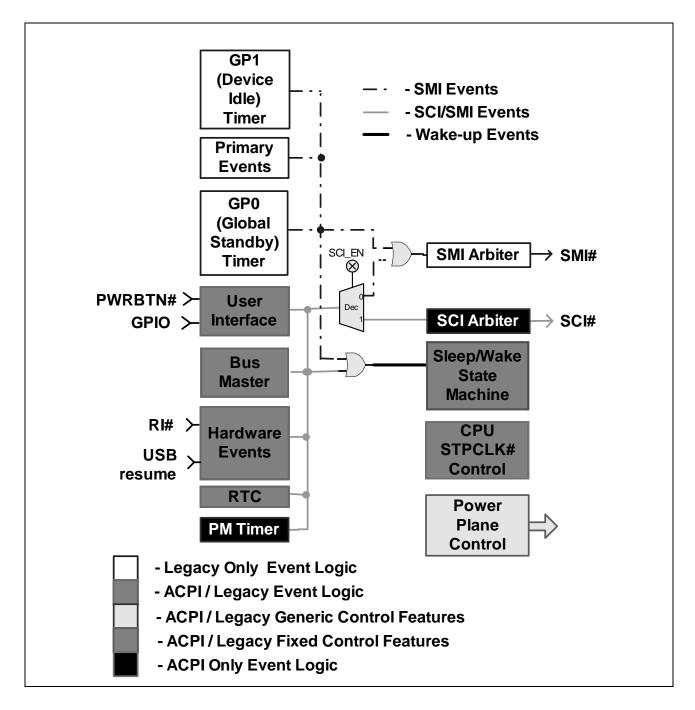

- Supports both ACPI (Advanced Configuration and Power Interface) and legacy (APM) power management

- ACPI v.0.9 Compliant

- APM v.1.2 Compliant

- Supports soft-off and power-on suspend with hardware automatic wakeup

- One idle timer, one peripheral timer, and one general purpose timer, plus 24- or 32-bit APCI-compliant timer

- Dedicated input pin for external modem ring indicator for system wakeup

- Normal, doze, sleep, suspend, and conserve modes

- System event monitoring with two event classes

- Five multipurpose I/O pins plus support for up to 16 general purpose input ports and 16 output ports

- Primary and secondary interrupt differentiation for individual channels

- Clock throttling control

- Multiple internal and external SMI# sources for flexible power management

1-2 Features

## 1.5 PC97-Compliant PCI-to-ISA Bridge

- Dual cascaded AT-compatible 8259 interrupt controllers

- AT-compatible 8255 programmable interval timer

- Dual AT-compatible 8237 DMA controllers

- Distributed DMA support for ISA legacy DMA across the PCI bus

- Integrated keyboard controller with PS/2 mouse support

- Integrated real-time clock with extended 256-byte CMOS RAM

- PCI v. 2.1-compliant interface

- Eight double-word line buffer between PCI and ISA bus

- Supports type F DMA transfers

- Fast reset and gate A20 operation

- Edge-triggered or level-sensitive interrupts

- Flash, 2-Mbyte EPROM, and combined BIOS support

- Programmable ISA bus clock

- Supports external IOAPIC interface with symmetrical multiprocessor configurations

Features 1-3

Figure 1-1. AMD-640 Chipset System Block Diagram

**1-4** Features

## 2 Overview

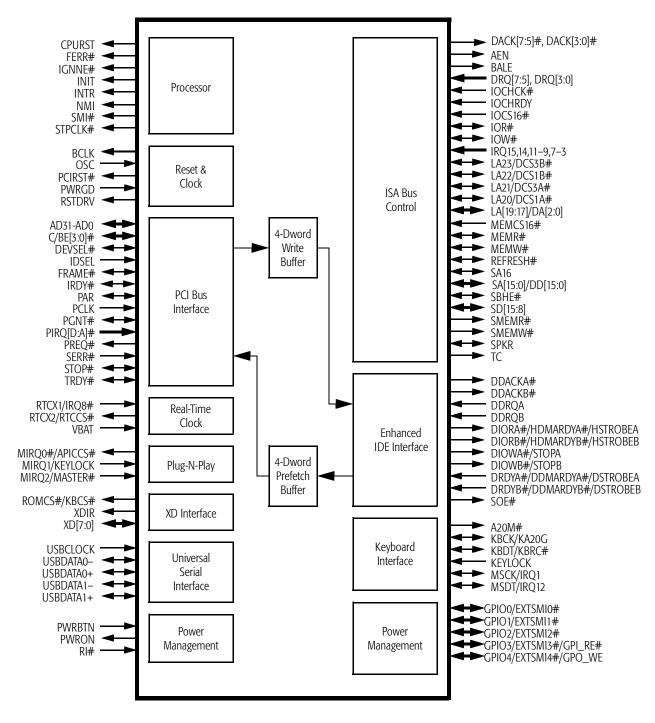

The AMD-645 peripheral bus controller is responsible for converting between PCI and ISA bus cycles. The AMD-645 peripheral bus controller PCI-to-ISA bridge contains eight double-word line buffers and supports Type F DMA transfers and delay transactions to streamline PCI bus operation and comply with PCI Specification version 2.1.

The AMD-645 peripheral bus controller also integrates many AT-compatible and system control functions, including a keyboard controller with PS/2 mouse support, real-time clock with extended 256-byte CMOS RAM, master mode EIDE controller with full scatter and gather capability, and a USB interface with root hub and two function ports with built-in physical layer transceiver.

## 2.1 PCI-to-ISA Bridge

The AMD-645 peripheral bus controller offers both a PCI-compatible bus interface and an ISA-compatible interface. These interfaces, which are fully compliant with the PCI 2.1 specification, control PCI/ISA bus communication. Two main blocks, the PCI bus master and slave blocks, make up the PCI interface control.

To become PCI bus master, the AMD-645 peripheral bus controller must arbitrate for control of the bus with the AMD-640 system controller. Once bus ownership has been granted, the AMD-645 peripheral bus controller assumes PCI bus master responsibility. The AMD-645 peripheral bus controller is in slave mode whenever it does not own the PCI bus.

Overview 2-1

21095B/0-June 1997

#### 2.1.1 PCI Bus Master Mode

The AMD-645 peripheral bus controller arbitrates for bus ownership when an ISA bus resource requests a DMA-controlled transfer between memory and an I/O device, or when an ISA bus master requests bus ownership for data transfers. In both DMA and ISA master mode, the data transfer takes place either between two ISA bus resources or between an ISA and a PCI bus resource.

To determine the destination of the bus master request, the AMD-645 peripheral bus controller can sample an active DEVSEL# input, which indicates that a particular target on the PCI bus is responding to the current request. The destination can also be determined by a positive decoding of the master-driven address.

A third alternative for determining the destination is subtractive decode. If the destination is not identified by either positive address decoding or an active DEVSEL# input, the AMD-645 peripheral bus controller assumes the access is occurring only between two ISA bus resources.

The AMD-645 peripheral bus controller PCI interface translates all non-positive decoded ISA master requests to the PCI bus. In situations in which the request is forwarded to the PCI bus, the AMD-645 peripheral bus controller ensures ISA and PCI bus synchronization by controlling the ISA-based IOCHRDY signal. If an active DEVSEL# response is not received within the specified time, the AMD-645 peripheral bus controller master interface assumes the requested cycle was between ISA resources and executes a PCI master abort cycle. In the event the DEVSEL# signal is sampled active within the specified time, the AMD-645 peripheral bus controller master interface executes a data transfer between the ISA and PCI buses.

#### 2.1.2 PCI Bus Slave Mode

The AMD-645 peripheral bus controller stays in PCI slave mode when it does not own the bus. The slave interface responds to any request from a PCI resource by asserting DEVSEL# if it has positively decoded the current address as a destination for either the ISA bus or for on-chip I/O.

2-2 Overview

When the current address is not positively decoded, the AMD-645 peripheral bus controller target interface is deselected by an active DEVSEL# input driven by another PCI resource.

If no active DEVSEL# signal is received within a specified time, the AMD-645 peripheral bus controller acts as the subtractive decode resource by claiming all otherwise unclaimed PCI bus requests and directing the request to the ISA bus.

To ensure correct data synchronization between the two buses on PCI-to-ISA write cycles, the ISA command sequence begins only after the current PCI master has indicated valid data on the bus by asserting IRDY#.

The AMD-645 peripheral bus controller responds to requests destined for the ISA bus or on-chip I/O by executing a single data transfer and signalling a target disconnect. If the AMD-645 peripheral bus controller samples an active DEVSEL# input within a specified time, it is de-selected, allowing the transfer to take place between the two PCI resources.

The AMD-645 peripheral bus controller is capable of posting PCI-to-ISA memory write cycles. When posting is enabled, the PCI request is acknowledged immediately and the write data is latched to allow the ISA cycle to proceed independently from the PCI transaction.

### 2.2 ISA Controller

The integrated ISA system address latches and control logic allow the AMD-645 peripheral bus controller user to design an extremely cost-effective system. In addition, the AMD-645 peripheral bus controller contains the decode logic to select an external keyboard controller. This keyboard controller can be programmed for attachment on either the XD or SD bus.

The AMD-645 peripheral bus controller controls accesses to 8-bit BIOS ROM and to 8-bit or 16-bit ISA bus ROM. The BIOS ROM must be 8 bits and is accessed via an external XD bus. All other ROM is accessed as either 8-bit or 16-bit ROM residing

Overview 2-3

on the ISA SD bus, either on-board or off-board via the slots. Accesses in the C0000h-CFFFFh and E0000h-EFFFFh ranges are optionally definable as on-board system ROM or off-board memory via the ROM relocation register. A special mode is supported for erasing and programming flash memories in areas where such devices are used as the BIOS ROMs.

The 82C37A-compatible DMA controllers control data transfers between an I/O channel and on-board or off-board memory. The DMA controllers can transfer data over a 24-bit (16- Mbyte) address range. Internal latches latch the middle address bits output by the 8237A megacells. A memory mapper generates the upper address bits.

As specified by the industry standard, distributed DMA offers support for seven DMA channels. The distributed DMA logic remaps I/O cycles from the distributed I/O target locations to the applicable DMA controller. When this remapping is enabled, accesses to the legacy DMA I/O addresses are disabled and ISA cycles are generated instead. DMA requests from the ISA bus that address PCI memory cause PCI master requests and cycles to be generated by the AMD-645 peripheral bus controller.

The AMD-645 peripheral bus controller generates synchronous ISA bus timing and synchronous IDE interface timing from the 33-MHz PCI bus clock.

The AMD-645 peripheral bus controller performs all the data steering functions between the ISA bus and the PCI bus. PCI bus data accesses that are wider than those supported by the targeted ISA bus device are automatically split into two, three, or four ISA cycles. When PCI bus reads are split into several ISA bus reads, the data returned by the ISA devices is assembled by latches before being returned to the PCI bus. The AMD-645 peripheral bus controller also performs low-to-high and high-to-low byte swaps on the 16-bit SD bus.

As a PCI slave, the AMD-645 peripheral bus controller is capable of expanding PCI accesses with non-contiguous byte enables into the appropriate discrete ISA cycles.

The AMD-645 peripheral bus controller functions are programmable via a set of internal device-specific

2-4 Overview

configuration registers. The state of various interface pins on reset is used to determine the default configuration.

### 2.3 EIDE Controller

The AMD-645 peripheral bus controller's enhanced IDE interface provides a variety of features to optimize system performance. A 16-doubleword write FIFO and look-ahead read buffer supports 32-bit PCI data transfers. The IDE-PCI interface operates at PCI speed and allows concurrent IDE and PCI operations to maximize system performance.

Logically, the IDE drive interface can be viewed as being composed of six controller blocks.

## **CPU Command Processor**

The CPU command processor receives input commands from the CPU, FIFO full/FIFO empty signals from the write-FIFO, and read-ahead full signals from the read-ahead buffer.

#### I/O Processor

The I/O processor is the IDE control signal block, containing all of the IDE bus control logic. It receives inputs from the IDE bus, command processor, and write FIFO. The I/O processor issues the IOR#/IOW# signals to the IDE bus, based on programmed address setup time, IOR#/IOW# precharge time, and IOR#/IOW# active duration. It also translates 16-bit cycles to two 8-bit cycles when necessary.

#### **Write Buffer**

The write buffer takes 32-bit CPU data and converts it to the proper 16-bit or 8-bit data format.

#### Read-Ahead/Posted-Write FIFO

This block functions as a read-ahead buffer during read accesses from I/O address 1F0h. During writes, this block stores 16-bit data in the 16-doubleword FIFO and passes control to the I/O processor or DMA state machine. Its direction is determined by commands and register programming.

#### **IDE Arbiter**

The arbiter arbitrates between IDE channels and multiplexes the IDE data bus, IDE address, and IDE chip selects.

#### **DMA State Machine**

The DMA bus mastering state machine controls IOW# and IOR# pulses for each IDE channel during DMA accesses.

Overview 2-5

The AMD-645 peripheral bus controller's enhanced IDE controller provides a data path and control interface to standard IDE drives. The block is fully compatible with the ANSI ATA specifications for IDE hard disk operation. The bus mastering IDE interface supports transfer rates up to and beyond mode 4-programmed I/O and mode 2 DMA. Two channels are supported with the ability to connect to both with no external logic. Data is transferred over a shared 16-bit IDE data bus.

The AMD-645 peripheral bus controller contains two IDE interfaces. Channel 0 is the primary interface, with target I/O addresses at 1F0h–1F7h and 3F6h. Its IRQ pin is mapped to IRQ14. Channel 1 is the secondary IDE interface, with target I/O addresses at 170h–177h and 376h. Its IRQ pin is mapped to IRQ15. Unless otherwise noted, discussions in this document referring to channel 0 resources apply equally to the respective channel 1 resources.

The master mode registers for both channels are contained in a single I/O block located at the I/O address specified by the contents of the Bus Master Control Registers Base Address register located at Function 1, offset 23h–20h. The first 8 bytes of the 16-byte block are associated with channel 0, and the second 8 bytes with channel 1. Independent configuration registers exist in PCI configuration space for each channel.

### 2.4 Universal Serial Bus

The AMD-645 peripheral bus controller USB host controller interface is fully compatible with both the USB specification v.1.0 and the Intel Universal HCI specification v.1.1. There are two sets of software-accessible registers, the PCI configuration registers and the USB I/O registers.

The interface supports eighteen levels (doublewords) of data FIFOs, and a root hub and two function ports with built-in physical layer transceivers. The USB controller allows hot Plug-N-Play and isochronous peripherals to be inserted into the system with universal driver support.

2-6 Overview

In addition, the AMD-645 peripheral bus controller offers legacy (X-bus) keyboard and PS/2 mouse support.

## 2.5 Power Management

The AMD-645 peripheral bus controller supports Advanced Configuration and Power Interface (ACPI) as well as legacy Advanced Power Management (APM). It complies with both ACPI specification v.0.9 and APM specification v.1.2. In addition, AMD-645 peripheral bus controller power management is compatible with PC97 and OnNow.

The real-time clock with 256-byte extended CMOS includes a data alarm and other enhancements for compatibility with the ACPI standard. Two types of sleep states are provided, soft-off and power-on suspend, along with hardware automatic wake-up. Additional power management features includes event monitoring, CPU clock throttling, hardware and software-based event handling, general purpose IO, and external SMI.

Overview 2-7

Figure 2-1. AMD-645 Peripheral Bus Controller Block Diagram

2-8 Overview

## **3 Ordering Information**

AMD standard products are available in several packages and operating ranges. The order number (valid combination) is formed by a combination of the elements below.

Table 3-1. Valid Combinations

| OPN     | Package Type | Operating Voltage | Case Temperature |

|---------|--------------|-------------------|------------------|

| AMD-645 | 208-pin PQFP | 4.75 V-5.25 V     | 70°C             |

#### Notes:

Valid combinations are configurations that are or will be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

Ordering Information 3-1

21095B/0-June 1997

**3-2** Ordering Information

## 4 Signal Descriptions

### 4.1 PCI Bus Interface

### AD[31:0] PCI Address/Data Bus Bidirectional

AD[31:0] are the standard PCI address and data lines. They contain a physical address during the first clock of a PCI transaction, and data during subsequent clocks. The address is driven when FRAME# is asserted, and data is driven or received in subsequent cycles.

When the AMD-645 peripheral bus controller is PCI master, these lines are outputs during the address and write data phases of a transaction, and inputs during the read data phase.

When the AMD-645 peripheral bus controller is PCI slave, these lines are inputs during the address and write data phases of a transaction, and outputs during the read data phase.

#### C3/BE[3:0]# PCI Command/Byte Enable Bidirectional

During the first clock of a PCI transaction, when FRAME# is asserted, these lines contain the PCI bus command (C[3:0]). On subsequent clocks, these lines contain PCI byte enables (BE[3:0]#) corresponding to supplied or requested data.

BE[3:0]# are outputs when the AMD-645 peripheral bus controller is the PCI bus master. They are inputs when it is the slave.

#### **DEVSEL#** PCI Bus Device Select Bidirectional

When the AMD-645 peripheral bus controller is PCI bus master, DEVSEL# is an input that determines whether a slave has responded to the current address. If DEVSEL# is sampled inactive in the fourth PCLK cycle after FRAME# is asserted, the AMD-645 peripheral bus controller aborts the PCI bus cycle.

Signal Descriptions 4-1

When the AMD-645 peripheral bus controller is not PCI bus master it defaults to target mode, and DEVSEL# is an output indicating that it claims a PCI transaction through either positive or subtractive decoding. In a positive decode, the AMD-645 peripheral bus controller asserts DEVSEL# one PCLK cycle after FRAME# is sampled active and holds it low through the end of the transaction. In a subtractive decode, DEVSEL# is driven low three PCLK cycles after FRAME# is asserted. Positive and negative decoding are explained in Section 5.1 on page 5-1.

#### FRAME# PCI Bus Cycle Frame Bidirectional

The assertion of FRAME# indicates the address phase of a PCI transfer, while its negation indicates that one more data transfer is desired by the cycle initiator. While FRAME# is asserted, data transactions can continue. When FRAME# is deasserted, data transactions are in the final phase.

When the AMD-645 peripheral bus controller is PCI bus master, FRAME# is driven active for one clock cycle to start the current bus cycle. When the AMD-645 peripheral bus controller is the slave, FRAME# is an input indicating the beginning and duration of the current bus cycle.

#### IDSEL PCI Initialization Device Select Input

IDSEL is used as a chip select during configuration read and write cycles.

#### IRDY# PCI Bus Initiator Ready Bidirectional

IRDY# is asserted by a PCI initiator from the first clock cycle after FRAME# to the last clock of the transaction to indicate it is ready for data transfer.

When the AMD-645 peripheral bus controller is PCI master, IRDY# is an output that indicates the ability of the chip to complete the current data phase of the transaction. When the AMD-645 peripheral bus controller is PCI slave, a read cycle cannot end and the write cycle cannot start until the IRDY# input is sampled active.

**4-2** Signal Descriptions

#### **PAR** *PCI Bus Parity Bidirectional*

This signal provides even parity for AD[31:0] and C/BE[3:0]#. When the AMD-645 peripheral bus controller is PCI bus master, it drives PAR one PCLK after the address and write data phases.

When the AMD-645 peripheral bus controller is PCI slave, it samples the PAR input one clock after a read is completed.

#### PCIRST# PCI Reset Output

PCIRST# is an active low reset signal for the PCI bus. The AMD-645 peripheral bus controller can assert reset during power-up. A PCI reset can be forced during normal operation by setting configuration register Function 0, offset 47h, bit 0.

#### PCLK PCI Bus Clock Input

PCLK provides timing for all transactions on the PCI bus. It runs at half the CPU frequency, up to 33 MHz. PCLK can also be divided down to generate the ISA bus clock.

#### PGNT# PCI Grant Input

The AMD-640 system controller drives PGNT# to grant PCI bus access to the AMD-645 peripheral bus controller.

#### PIRQ[D:A]# PCI Interrupt Requests Input

These pins are typically connected to the PCI bus INT lines as shown in Table 4-1.

Table 4-1. Connecting PIRQ Lines to PCI INT Lines

|            | PIRQA# | PIRQB# | PIRQC# | PIRQD# |

|------------|--------|--------|--------|--------|

| PCI Slot 1 | INTA#  | INTB#  | INTC#  | INTD#  |

| PCI Slot 2 | INTB#  | INTC#  | INTD#  | INTA#  |

| PCI Slot 3 | INTC#  | INTD#  | INTA#  | INTB#  |

| PCI Slot 4 | INTD#  | INTA#  | INTB#  | INTC#  |

#### PREQ# PCI Request Output

The AMD-645 peripheral bus controller asserts PREQ# to request control of the PCI bus.

Signal Descriptions 4-3

21095B/0-June 1997

#### SERR# System Error Input

Any PCI device that detects a system error condition can alert the system by asserting SERR# for one PCI clock. The AMD-645 peripheral bus controller can be programmed to generate an NMI to the CPU if it samples SERR# active.

#### **STOP#** Stop Bidirectional

A PCI target asserts STOP# to request that the master stop the current transaction. When the AMD-645 peripheral bus controller is PCI master, STOP# is an input that causes the AMD-645 peripheral bus controller to terminate the transfer and abort or retry it depending on the state of DEVSEL# and TRDY#.

When the AMD-645 peripheral bus controller is PCI slave, it asserts STOP# and TRDY# simultaneously to indicate a target disconnect following the data transfer or burst. It does not assert STOP# if the transfer is a single, non-bursted transfer.

#### **TRDY#** PCI Target Ready Bidirectional

A PCI target asserts TRDY# when it is ready for data transfer. When the AMD-645 peripheral bus controller is the PCI master, TRDY# is an input that indicates the ability of the target device to complete the data phase of the transaction. Once a PCI bus transaction is initiated, the AMD-645 peripheral bus controller inserts wait cycles until TRDY# is sampled active.

As the PCI slave, the AMD-645 peripheral bus controller asserts TRDY# to indicate it has sampled the data from the PCI address/data bus during a write phase, or presented valid data on the bus during a read phase.

## 4.2 ISA Bus Interface

#### **AEN** Address Enable Output

AEN is asserted during DMA transfer cycles to the I/O resources on the bus to prevent I/O slaves from misinterpreting DMA cycles as valid I/O cycles. It is asserted only when the DMA controller is the bus owner.

**4-4** Signal Descriptions

**BALE** Bus Address Latch Enable Output

BALE is asserted for a bus clock at the beginning of any bus cycle initiated by a PCI master. It is asserted by the AMD-645 peripheral bus controller to indicate that the address signal lines (SA[19:0], LA[23:17], and SBHE#) are valid.

BCLK Bus Clock Output

BCLK is the ISA bus clock.

DACK[7:5]#, DMA Acknowledge Output

CACK[3:0]#

These lines indicate that the corresponding request for DMA service has been accomplished.

DRQ[7:5], DMA Request Input

DRQ[3:0]

These asynchronous DMA request lines are used by external devices to request services from the AMD-645 peripheral bus controller DMA controller. DRQ[3:0] are used for transfers between 8-bit I/O adapters and system memory. DRQ[7:5] are used for transfers between 16-bit I/O adapters and system memory. DRQ4 is not available externally.

IOCHCK# I/O Channel Check Input

IOCHCK# is asserted by a device or memory on the ISA bus to indicate that a parity error or other uncorrectable error has occurred.

If I/O checking is enabled, the AMD-645 peripheral bus controller generates an NMI to the processor when it samples IOCHCK# asserted.

IOCHRDY I/O Channel Ready Input

Devices on the ISA bus negate IOCHRDY to indicate that additional time is required to complete the cycle. The cycle can be generated by the CPU, DMA controllers, or refresh controller. The AMD-645 peripheral bus controller responds by inserting wait states to add more time to the cycle.

The default number of wait states for cycles initiated by the CPU is as follows:

■ 8-bit peripherals 4 wait states

■ 16-bit peripherals 1 wait state

Signal Descriptions 4-5

#### ■ ROM cycles 3 wait states

One DMA wait state is inserted as the default for all DMA cycles. Any peripheral that cannot present read data or strobe in write data in this amount of time must assert IOCHRDY to extend these cycles.

The AMD-645 peripheral bus controller always drives IOCHRDY low in either DMA or Master Mode to allow for PCI bus latency.

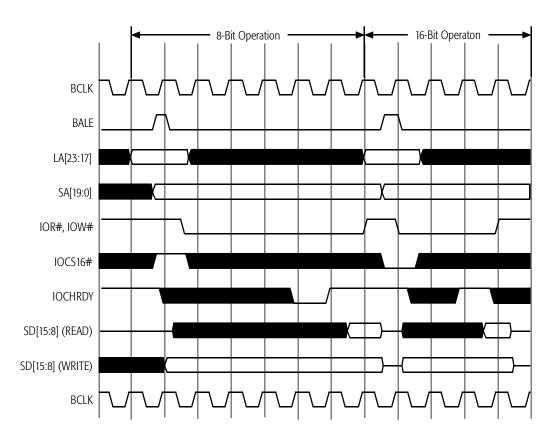

#### IOCS16# 16-Bit I/O Chip Select Input

IOCS16# is driven by I/O devices on the ISA bus to indicate that they support 16-bit I/O bus cycles.

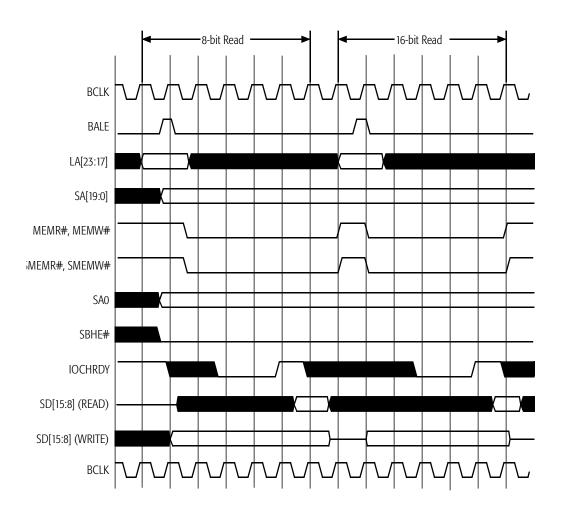

The AMD-645 peripheral bus controller samples IOCS16# to determine when a CPU access requires a 16-bit to 8-bit conversion. It also performs a conversion if it requests a 16-bit I/O cycle and samples IOCS16# high. In a conversion, the AMD-645 peripheral bus controller inserts a command delay of one bus cycle and the cycle becomes four wait states long. If IOCS16# is sampled low, the AMD-645 peripheral bus controller performs an I/O access in one wait state, inserting one command delay.

#### IOR# I/O Read Bidirectional

IOR# is the command to an ISA I/O slave device indicating the slave can drive data onto the ISA data bus.

IOR# is an input when the AMD-645 peripheral bus controller is bus master and an output at all other times. When the AMD-645 peripheral bus controller is a PCI slave, IOR is driven by the internal ISA bus controller.

During DMA transfers, IOR# is driven by the DMA controller. It is inactive during a refresh cycle.

#### IOW# I/O Write Bidirectional

IOW# is the command to an ISA I/O slave device indicating the slave can latch data from the ISA data bus.

**4-6** Signal Descriptions

IOW# is an input when the AMD-645 peripheral bus controller is bus master and an output at all other times. When the AMD-645 peripheral bus controller is a PCI slave, IOW# is driven by the internal ISA bus controller.

During DMA transfers, IOW# is driven by the DMA controller. It is inactive during a refresh cycle.

IRQ15, IRQ14, IRQ11:9], IRQ[7:3]

#### Interrupt Request

#### Input

The IRQ signals provide both system board components and ISA bus I/O devices with a mechanism for asynchronously interrupting the CPU.

LA23/DCS3B#, LA22/DCS1B#, LA21/DCS3A#, LA20/DCS1A#, LA[19:17]/ DA[2:0]

#### Multifunctional Pins

#### **Bidirectional**

ISA Bus Cycles—Unlatched Address

The LA[23:17] address lines are bidirectional and allow accesses to physical memory on the ISA bus up to 16 Mbytes.

PCI IDE Cycles—Chip Select

DCS1A#, DCS3A#, DCS1B# and DCS3B# are for the ATA command register block and correspond directly to CS1FX#, CSF3X#, CS17X#, and CS37X# on the primary IDE connector, respectively.

#### **PCI IDE Cycles**—*Disk Address*

DA[2:0] are used to indicate which byte in either the ATA command or control block is being accessed.

The value driven on the LA bus is the address stored in the AD address register during PCI-initiated cycles and the refresh counter during non-ISA bus master refresh cycles. The LA pins are outputs when MASTER# is high and are inputs when it is low.

#### MASTER#/MIRQ2

#### Multifunctional Pin

#### Input

ISA Master Cycle Indicator

An external bus master device asserts MASTER# to indicate that it has control of the bus.

Plug and Play Interrupt Request 2

MIRQ2 is a steerable interrupt request for on-board devices.

Signal Descriptions 4-7

21095B/0-June 1997

#### MEMCS16# 16-Bit Memory Chip Select Input

ISA 16-bit slave memory devices drive this line low to indicate support for 16-bit memory bus cycles. This line is sampled to determine when a 16-bit to 8-bit conversion is needed for CPU accesses. Conversion is performed when the AMD-645 peripheral bus controller requests a 16-bit memory cycle and MEMCS16# is sampled high. A command delay of one clock cycle is inserted and the cycle becomes four wait states long. If MEMCS16# is sampled low, a memory access is performed in one wait state with no command delays inserted.

MEMCS16# is ignored for DMA and refresh cycles.

#### MEMR# Memory Read Bidirectional

MEMR# is the command to a memory slave that permits it to drive data onto the ISA data bus. This signal is an input when an external bus master is in control and an output at all other times.

#### MEMW# Memory Write Bidirectional

MEMW# is the command to a memory slave that permits it to latch data from the ISA data bus. This signal is an input when an external bus master is in control and an output at all other times.

#### REFRESH# Refresh Bidirectional

As an output, REFRESH# indicates a refresh cycle is in progress. It is asserted by the AMD-645 peripheral bus controller whenever a refresh cycle is initiated. As an input, REFRESH# is driven by 16-bit ISA bus masters to indicate a refresh cycle.

#### RSTDRV Reset Drive Output

RSTDRV is the reset signal to the ISA bus. It is generated from the received RST signal and is synchronized to PCLK, though it is used for the ISA bus.

## SA[15:0]/ System Address Bus/IDE Data Bus Bidirectional DD[15:0]

These pins serve as the address bus in ISA operation and the data bus in IDE operation.

**4-8** Signal Descriptions

**SA16** System Address Bus **Bidirectional**

This signal is ISA address bit 16.

System Byte High Enable SBHE# **Bidirectional**

> When asserted, SBHE# indicates that a byte is being transferred on the upper byte of the ISA data bus (SD[15:8]).

SBHE# is negated during refresh cycles.

**SD[15:8]/ GPI[15:8] GPO[15:8]**  Multifunctional Pins **Bidirectional**

SD[15:8] provide the high order data path for devices residing on the ISA bus. The low order ISA path, SD[7:0], is multiplexed

with XD[7:0] (see page 4-13).

General-Purpose Inputs

If the GPIO3 CFG bit is cleared (Function 3, offset 40h, bit 6), these pins function as GPI[15:8] and pin 92 serves as read

enable GPI RE#.

ISA System Data

*General-Purpose Outputs*

If the GPIO4 CFG bit is cleared (Function 3, offset 40h, bit 7), these pins function as GPO[15:8] and pin 92 serves as write

enable GPI\_WE.

SMEMR# Standard Memory Read Output

SMEMR# is the command that permits a slave to drive data

residing below the 1 MByte region onto the ISA data bus.

SMEMW# Standard Memory Write **Output**

> SMEMW# is the command that permits a slave to latch data residing below the 1 MByte region from the ISA data bus.

TC Terminal Count Output

> The AMD-645 peripheral bus controller asserts TC to DMA slaves to indicate that one of the DMA channels has

transferred all data.

**Bidirectional** SPKR/ Multifunction Pin

**Power-Up Strap** Speaker Drive

After reset, this pin functions as the SPKR signal, which is the

output of counter 2.

Signal Descriptions 4-9

21095B/0-June 1997

Power-Up Strapping

At reset, if this pin is strapped low, the IDE I/O base is fixed. If the pin is strapped high, the IDE I/O base is flexible.

## 4.3 Ultra DMA-33 Enhanced IDE Interface

**Note:** The IDE address, data, and drive select pins are multiplexed with the ISA bus LA and SA pins and are described in Section 4.2.

#### **DDACKA#** Disk DMA Acknowledge A Output s

DDACKA# is the primary IDE channel DMA acknowledge. The AMD-645 peripheral bus controller responds to DDRQA either to acknowledge that data has been accepted or to inform that data is available.

#### **DDACKB#** Disk DMA Acknowledge B Output

DDACKB# is the secondary IDE channel DMA acknowledge. The AMD-645 peripheral bus controller responds to DDRQB either to acknowledge that data has been accepted or to inform that data is available.

#### **DDRQA** Device DMA Request A Input

DDRQA is the primary IDE channel DMA request. A device asserts DDRQA when it is ready to read or write DMA data.

#### **DDRQB** Device DMA Request B Input

DDRQB is the secondary IDE channel DMA request. A device asserts DDRQB when it is ready to read or write DMA data.

#### DIORA#/ HDMARDYA#/ HSTROBEA#

#### Multifunction Pin

#### **Output**

#### **EIDE Mode**—Device I/O Ready A

DIORA# is the primary IDE channel drive write strobe. The falling edge of DIORA# enables the transfer of data from a register or data port of the drive onto the IDE data bus, DD[15:0]. The rising edge of DIORA# latches the data.

#### **Ultra DMA Mode**—Host DMA Ready

HDMARDYA# functions as the primary channel input flow control. The host can assert HDMARDYA# to pause input data transfers.

**4-10** Signal Descriptions

#### Ultra DMA Mode—Host Strobe A

HSTROBEA functions as the primary channel output strobe. The host can stop HSTROBEA to pause output data transfers.

Output

### DIORB#/ HDMARDYB#/ HSTROBEB

#### Multifunction Pin

### **EIDE Mode**—Device I/O Ready B

DIORB# is the secondary IDE channel drive write strobe. The falling edge of DIORB# enables the transfer of data from a register or data port of the drive onto the IDE data bus, DD[15:0]. The rising edge of DIORB# latches the data.

#### Ultra DMA Mode—Host DMA Ready B

HDMARDYB# functions as the secondary channel input flow control. The host can assert HDMARDYB# to pause input data transfers.

#### Ultra DMA Mode—Host Strobe B

HSTROBEB functions as the secondary channel output strobe. The host can stop HSTROBEB to pause output data transfers.

### DIOWA#/ STOPA

#### **Multifunction Pin**

#### Output

#### **EIDE Mode**—Device I/O Write A

DIOWA# is the primary IDE channel drive read strobe. The rising edge of DIOWA# clocks data from the IDE data bus (DD[15:0]) into either a register or the data port of the drive.

#### Ultra DMA Mode—Stop A

STOPA halts data transfer in the primary channel. The host asserts STOPA before an Ultra DMA burst is initiated and negates STOPA before an Ultra DMA burst is transferred. The host asserts STOPA during or after data transfer in Ultra DMA mode to signal the termination of the burst.

### DIOWB#/ STOPB

#### Disk I/O Write B

#### **Output**

#### **EIDE Mode**—Device I/O Write B

DIOWB# is the secondary IDE channel drive write strobe. The rising edge of DIOWA# clocks data from the IDE data bus (DD[15:0]) into either a register or the data port of the drive.

Signal Descriptions 4-11

21095B/0-June 1997

#### **Ultra DMA Mode**—Stop B

STOPB halts data transfer in the secondary channel. The host asserts STOPB before an Ultra DMA burst is initiated and negates STOPB before an Ultra DMA burst is transferred. The host asserts STOPB during or after data transfer in Ultra DMA mode to signal the termination of the burst.

### DRDYA#/ DDMARDYA#/ DSTROBEA

#### Multifunction Pin

#### Input

### **EIDE Mode**—Device Ready A

DRDYA# is the primary channel device ready indicator. A device negates DRDYA# to extend the AMD-645 peripheral bus controller read or write cycle when it is not ready to respond to a data transfer request. When DRDYA# is negated, it is in a high impedance state.

#### Ultra DMA Mode—Device DMA Ready A

DDMARDYA# is the primary channel output flow control. A device can assert DDMARDYA# to pause output transfers.

#### Ultra DMA Mode—Device Strobe A

DSTROBEA is the primary channel input data strobe. A device can stop DSTROBEA to pause input data transfers.

### DRDYB#/ DDMARDYB#/ DSTROBEB

#### Multifunction Pin

#### Input

#### **EIDE Mode**—Device Ready B

DRDYB# is the secondary channel device ready indicator. A device negates DRDYB# to extend the AMD-645 peripheral bus controller read or write cycle when it is not ready to respond to a data transfer request. When DRDYB# is negated, it is in a high impedance state.

#### **Ultra DMA Mode**—Device DMA Ready B

DDMARDYB# is the primary channel output flow control. A device can assert DDMARDYB# to pause output transfers.

#### Ultra DMA Mode—Device Strobe B

DSTROBEB is the primary channel input data strobe. A device can stop DSTROBEB to pause input data transfers.

**4-12** Signal Descriptions

#### SOE#

#### System Address Transceiver Output Enable Output

SOE# controls the output enables of the 74F245 transceivers that interface the IDE data bus (DD[15:0]) to the system address bus (SA[15:0]). MASTER# drives the transceiver direction control with DD[15:0] connected to the "A" side of the transceivers and SA[15:0] connected to the "B" side.

# 4.4 XD Bus Interface

#### ROMCS#/KBCS#

#### Multifunctional Pin

#### **Output**

ROM Chip Select

In ISA memory cycles, ROMCS# is the chip select to the ROM BIOS.

Keyboard Chip Select

In ISA I/O cycles, KBCS# is the chip select to the external keyboard controller.

XD[7:0]/ SD[7:0]/ EXTSMI[7:3]/ GPI[7:0]/ GPO[7:0]/

**Power-Up Straps**

#### **Multifunction Pins**

#### **Bidirectional**

XD[7:0]

Connection to external X-bus devices such as BIOS ROM.

SD[7:0]

Low order data path for devices residing on the ISA bus. These signals are multiplexed with XD[7:0] through a 74F245 transceiver. Refer to the description of the XDIR pin on page 4-14

*EXTSMI*[7:3]

External SCI/SMI ports.

*GPI*[7:0]

General-purpose inputs if configuration register Function 3, offSet 40h, bit 6 is cleared.

GPO[7:0]

General-purpose outputs if configuration register Function 3, offset 40h, bit 7 is cleared.

Signal Descriptions 4-13

21095B/0-June 1997

Power-Up Straps

Pins XD[7:0] are used as strap options during power-up (see configuration register Function 0, offset 5Ah on page 7-27). Strapping low disables and strapping high enables the following functions:

• XD[7:4] RP[16:13] for internal KBC

• XD2 internal RTC

• XD1 internal PS/2 Mouse

• XDO internal KBC

**XDIR** X-Bus Data Direction Output

XDIR is tied directly to the direction control of the 74F245 transceiver that buffers the X-bus data and ISA-bus data. SD[7:0] connect to the "A" side of the transceiver and XD[7:0] connect to the "B" side. The output enable of the transceiver should be grounded. A high signal on SDIR indicates that SD[7:0] drives XD[7:0].

# 4.5 Plug-N-Play Support

The AMD-645 peripheral bus controller provides three interrupt request pins to support Plug-n-Play functions from non-PnP devices. These asynchronous interrupt requests are mappable to any of the interrupt channels. Each pin has an alternate function which is selected in configuration register Function 0, offset 59h (see page 7-26).

MIRQ2/MASTER# Multifunction Pin Input

**Plug-n-Play**—Interrupt Request 2

**ISA**—*Master Cycle Indicator* (see page 4-7)

MIRQ1/KEYLOCK Multifunction Pin Input

Plug-n-Play—Interrupt Request 1

**KEYLOCK**—Keyboard Lock Input

MIRQO#/APICCS# Multifunction Pin Input

Plug-n-Play—Interrupt Request 0

4-14 Signal Descriptions

**APICCS**#—*APIC Chip Select*

This signal is provided for external IO APIC devices in symmetric multiprocessor implementations.

# 4.6 Universal Serial Bus Interface

USBCLKUniversal Serial Bus ClockInputUSBDATA0+USB Port 0 Data +BidirectionalUSBDATA0-USB Port 0 Data -BidirectionalUSBDATA1+USB Port 1 Data +BidirectionalUSBDATA1-USB Port 1 Data -Bidirectional

# 4.7 Power Management

PWRBTN# Power Button Input

Referenced to  $V_{DD}$ -5VSB.

PWRGD Power Good Input

PWRGD is connected to the POWERGOOD signal on the power

supply.

**PWRON** Power Supply Control Output

Powered by  $V_{DD}$ -5VSB.

RI# Ring Indicator Input

This signal can be connected to external modem circuitry to allow the system to be reactivated by a received phone call.

Input referenced to  $V_{\mbox{\scriptsize DD}}\mbox{-5VSB}.$

Signal Descriptions 4-15

21095B/0-June 1997

# 4.8 Power and Ground

**AGND** USB Differential Output Ground Power

**A<sub>VDD</sub>** USB Differential Output Power Source

V<sub>nn</sub>3 Power Supply for the CPU I/O VoltagePower

This pin should be connected to the same voltage as the CPU

I/O circuitry.

**V<sub>DD</sub>** Power Supply of 4.75 V to 5.25 V Power

This supply is turned on only when the mechanical switch on the power supply is turned on and the PWRON signal is

conditioned high.

**V<sub>DD</sub>-5SB** Power Supply Power

V<sub>DD</sub>-5SB is always available unless the mechanical switch of the power supply is turned off. If the "soft-off" state is not

implemented, then this pin can be connected to  $V_{DD}$ .

**V<sub>DD</sub>-PCI** *PCI Voltage, 3.3 V or 5 V Power*

**GND** Ground Power

# 4.9 Internal Real-Time Clock

**OSC** Oscillator Input

OSC is a 14.31818-MHz clock used by the internal timers and

the ACPI timer.

RTCX1/IRQ8# Multifunctional Pin Input

RTCX1

When the internal RTC is enabled, this signal is the

RTC crystal or oscillator input (32.768 KHz.)

IRO8#

When the internal RTC is disabled, IRQ8# is an input from an

external keyboard controller.

**4-16** Signal Descriptions

RTCX2/RTCCS# Multifunctional Pin Output

RTCX2

When the internal RTC is enabled, this signal is the RTC crystal or oscillator output (32.768 KHz.)

RTCCS

When the internal RTC is disabled, this signal is the External

RTC chip select.

**VBAT** RTC Battery Input

This signal is the battery input for internal RTC.

# 4.10 Keyboard Interface

A20M# A20 Mask Output

The AMD-645 peripheral bus controller A20M# is a direct

connection to A20M# on the CPU.

**KBCK/KA20G** *Multifunctional Pin Bidirectional*

Keyboard Clock

When the internal keyboard controller is enabled, KBCK is the

clock to the keyboard interface.

Keyboard Gate A20

When the internal keyboard controller is disabled, KA20G is

the Gate A20 output from the external keyboard controller.

**KBDT/KBRC#** *Multifunctional Pin Bidirectional*

Keyboard Data

When the internal keyboard controller is enabled, KBDT is the

data line to the keyboard interface.

Keyboard Reset

When the internal keyboard controller is disabled, KBRC# is a

reset input from the external keyboard controller.

**KEYLOCK** Keyboard Lock Input

KEYLOCK is the keyboard lock signal for the internal