# Power Management Features of X86 Microprocessors

Authors: Jack R. Smith and Sebastian

Ventrone

# Application Note

#### Introduction

This paper describes techniques to control power consumption in X86-based computers. The IBM 486 series, Intel® 486 series and Intel Pentium<sup>TM</sup> series microprocessors are studied, and their power management features are compared.

Each processor studied has the ability to manage power in one or more ways. The processors are similar in this respect, but there are vast differences in the ways they perform this task. IBM announced a new feature on 486DX2/DX4 to reduce these differences.

## **Background on Power Management**

X86 power management allows the microprocessor to regulate the amount of electrical power consumed by the system. Using power management, the microprocessor can control its own power as well as the power consumed by system logic, memory and peripheral devices. Power management is important to customers for the following reasons: 1) it reduces the cost of operating office systems, 2) it extends battery life in portable systems and 3) it conforms to applicable international energy standards.

The original Thinkpad portable computer contained an Intel 386SX microprocessor. In 1986, IBM developed a Thinkpad based on the IBM 386SLC processor that has an on-chip cache and a faster clock. However, a major drawback of the original 386SLC design was its power consumption. The original 386SLC consumed more power than the Intel 386SX. Several engineering discussions were held to solve this problem, and it was determined that power could be significantly reduced by implementing an efficient shutdown procedure.

The new shutdown procedure became known as the IBM power management architecture, and is implemented in current versions of the IBM 386SLC, 486SLC2 and Blue Lightning processors. The core of the new architecture is a new mode of operation (System Management Mode) which is accessed through a chip input (PWI# or SMI#). When the input is asserted, the processor finishes the current instruction, saves the state of the CPU to memory and enters System Management Mode. If the processor is using an on-chip write-back cache, it must be flushed before removing power from the processor. When power is returned, the processor restores the state of the CPU and resumes processing in the mode it was in prior to receiving the PWI interrupt. In addition to System Management Mode, IBM added to the 386SLC a low power halt

Page 1 of 12 October 12, 1995 Fax #40012

function and a dynamic frequency shift protocol. Low power halt allows the processor to turn off its internal clocks during the halt state to achieve minimum standby power. Dynamic frequency shift allows the system to reduce the external clock frequency at certain times, which reduces power consumption.

An X86 microprocessor can manage power in the following ways:

- 1. System Management Mode

- 2. Low Power Halt

- 3. Adjustable Core Clock Multiplier

- 4. Dynamic Frequency Shift

- 5. Additional Features

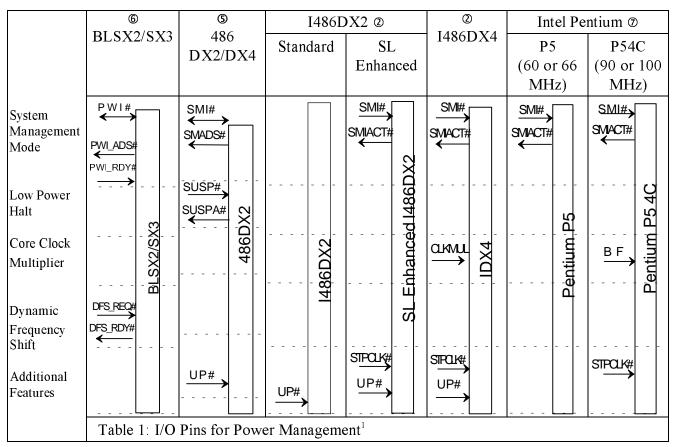

The first feature controls system power, and the other features control the processor only. Table 1 (on the following page) shows the power management pins on each processor.

# System Management Mode

System Management Mode (SMM) is an X86 operating environment which allows the processor to manage power through software which runs transparent to the operating system and applications programs. SMM mode is intended for use only by system firmware, not by applications.

Many things can be done in SMM mode. An idle processor can be put into a low power state or shutdown, as described earlier. This is an ideal application for portable PCs, where closing the lid can trigger an SMM interrupt to prepare for shutdown. The concept can be extended to desktop systems, where the processor can be powered down if it has been idle for some time.

SMM mode can also manage I/O devices. Devices can be powered down when not in use, and powered up when they are needed. When instructions are directed to an offline device, SMM software suspends activity to this device, powers up the device and reissues the instruction stream.

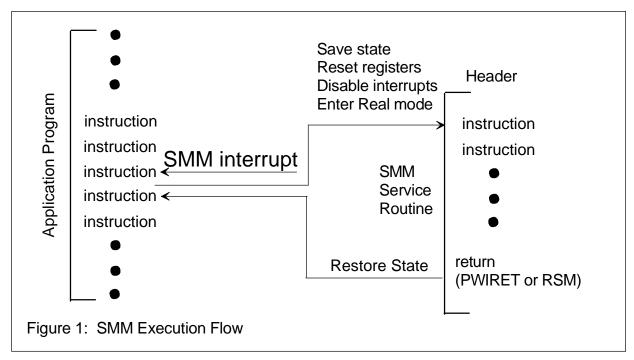

SMM mode is entered through a dedicated hardware interrupt and uses a separate memory space (SMRAM) which holds the CPU state and interrupt service routine. When an SMM interrupt occurs, the processor finishes the current instruction and then saves the CPU state to the header area in SMRAM. It resets some architected registers, disables INTR and NMI interrupts, enters Real addressing mode and begins executing the service routine. The locations of the header and service routine are specified by each processor.

The service routine is developed by the system designer and installed in SMRAM at boot up. The last instruction in the routine causes the processor to exit the routine, refresh the CPU state from SMRAM and resume executing in the mode it was in prior to receiving the SMM

Numbers in the heading of this and the following tables designate entries in the References Section at the end of this document.

interrupt. For the IBM 486SX2 and 486SX3 processors, the PWIRET instruction performs this function. All other processors studied use the RSM instruction to exit SMM mode. Figure 1 illustrates the transition to and from SMM mode.

Below is a technique to put the CPU into a low power state:

- 1. Flush the cache (if using Intel CPU or early revisions of IBM 486DX2/DX4. Intel CPUs may cache accesses to SMM memory, so the cache must be flushed upon SMM entry and exit. Rev. 4.1 and earlier of IBM 486DX2/DX4 does not snoop the bus during halt.)

- 2 Enter SMM mode

- 3. SMM routine enables INTR or NMI, then executes HLT to enter low power state

- 4. Stop external clock to processor

When the processor is needed, start the external clock, interrupt the halt state, and exit SMM.

Below is a technique to shutdown the CPU:

- 1. Flush the cache (if write-back)

- 2. Enter SMM mode

- 3. SMM routine copies header (CPU state) to another memory location and sets an SMM indicator bit in memory.

- 4. Disconnect power to CPU

After power is returned, the CPU resets. BIOS reads the SMM indicator bit from memory, determines that the CPU was in SMM mode before shutdown and gives an SMM interrupt. The CPU enters SMM mode. The SMM routine reads the original CPU state from the other memory location, puts it into the header in SMRAM and exits SMM mode. SMM provides a faster but more risky means of shutting down the CPU than the traditional method. SMM is controlled by processor microcode and runs independent of the operating system. The traditional

method uses standard interrupt protocol (assert INTR pin, execute power management routine, return via IRET instruction) and relies on the operating system to ensure proper operation. The traditional method is used today. The SMM method will be used in future systems.

All of the processors listed in Table 1 above, except the standard version of the Intel 486DX2/DX4, implement SMM mode. All come with SMM enabled at power up, except IBM 486DX2/DX4 which must configure SMM before it can be used. All processors listed in Table 1 offer a hardware interrupt. The IBM processors also offer a software interrupt.

The hardware interrupt on IBM 486SX2 and 486SX3 is PWI#, and all other processors listed in Table 1 use SMI#. The pin is bidirectional on IBM processors and unidirectional on Intel processors. On IBM processors, the system drives the pin to enter SMM mode and then the CPU drives the pin when it is in SMM mode. Intel processors do this differently. For Intel processors SMI# as an input only, and SMIACT# is an output asserted when SMM mode is active. Since Intel processors have separate interrupt and acknowledge pins, they can process nested SMM interrupts.

Another pinout difference between IBM and Intel processors is memory address strobes. IBM processors have two address strobes (ADS# for normal accesses, PWI\_ADS# or SMADS# for SMM accesses). Intel processors have one address strobe (ADS#), and the SMIACT# signal differentiates normal accesses from SMM accesses.

Page 4 of 12 October 12, 1995 Fax #40012

All processors listed in Table 1, except Intel Pentium P5, support I/O instruction restart during SMM. This function is enabled through a configuration register (IBM SX2 and SX3) or bits in the SMM header (IBM 486DX2/DX4, Intel DX4, Intel Pentium P54C).

Table 2 (on the following page) lists the SMM features on each processor.

For some time, the pinout differences made SMM incompatible from processor to processor. Recently, IBM announced a new feature to clear this up. On the 3.3 volt version of the Blue Lightning 486DX2/DX4, the SMM hardware interface can be made functionally compatible with Intel SL Enhanced 486DX2/DX4 by setting a configuration bit. If bit 3 in configuration register CCR3 is set, IBM's SMI# pin is compatible with Intel's SMI# pin and the SMADS# pin is compatible with Intel's SMIACT# pin. If this bit is reset, the chip operates as it did before. The software interrupt is not available when CCR3(3) is set.

Page 5 of 12 October 12, 1995 Fax #40012

|                                  | © DI CV2/CV2                                   | <b>0.40</b><br>IBM                                                                           | I486DX2 <b>②</b> |                                                                  | <b>②</b><br>I486DX4                                                 | Intel Pentium ⑦                                                  |                                                                  |  |  |

|----------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|--|--|

|                                  | BLSX2/SX3                                      | 486DX2/DX4                                                                                   | Std.             | SL Enhanced                                                      | 1480DX4                                                             | P5(60 or 66MHz)                                                  | P54C (90 or<br>100MHz)                                           |  |  |

| Entry                            | HW: Assert PWI# 12cycles SW: PWIBP instruction | HW: Assert SMI# 2 cycles SW: SMINT instruction                                               |                  | Assert SMI#<br>1 cycle                                           | Assert SMI# 1<br>cycle                                              | Assert SMI# 1<br>cycle                                           | Assert SMI# 1 cycle                                              |  |  |

| Exit                             | PWIRET<br>instruction<br>or RESET              | RSM instruction                                                                              |                  | RSM instruction or RESET                                         | RSM<br>instruction<br>or RESET                                      | RSM instruction<br>RESETor INIT                                  | RSM instruction<br>RESET or INIT                                 |  |  |

| Enable                           | Always<br>Enabled                              | HW:<br>CCR1(1)=1<br>CCR1(2)=0<br>SMAR(3:0)>0<br>SW:<br>CCR1(1)=1<br>CCR1(2)=1<br>SMAR(3:0)>0 |                  | Always enabled                                                   | Always<br>enabled                                                   | Always enabled                                                   | Always enabled                                                   |  |  |

| Header<br>Location               | 00060000h-<br>0006014Ch                        | Defined by SMAR                                                                              |                  | 0003 FE00h -<br>0003 FFFFh<br>(relocatable)                      | 0003FE00h -<br>0003FFFFh<br>(relocatable)                           | 0003FE00h -<br>0003FFFFh<br>(relocatable)                        | 0003FE00h -<br>0003FFFFh<br>(relocatable)                        |  |  |

| Service<br>Routine<br>Location   | Bootstrap<br>address at<br>FFFFFFF0h           | Defined by SMAR                                                                              |                  | 00038000h<br>(relocatable)                                       | 00038000h<br>(relocatable)                                          | 00038000h<br>(relocatable)                                       | 00038000h<br>(relocatable)                                       |  |  |

|                                  | T                                              | D                                                                                            | uring S          | System Managemer                                                 | nt Mode (SMM)                                                       |                                                                  |                                                                  |  |  |

| INTR                             | Disabled                                       | Disabled.<br>Enabled by<br>STI instruction                                                   |                  | Disabled.<br>Enabled by<br>STI<br>instruction                    | Disabled.<br>Enabled by<br>STI<br>instruction                       | Disabled.<br>Enabled by<br>STI<br>instruction                    | Disabled.<br>Enabled by<br>STI<br>instruction                    |  |  |

| NMI                              | Disabled                                       | Disabled, 1 event latched. Enabled by CCR3(1).                                               |                  | Disabled, 1<br>event latched.<br>Enabled by IRET<br>instruction. | Disabled, 1<br>event latched.<br>Enabled by<br>IRET<br>instruction. | Disabled, 1<br>event latched.<br>Enabled by IRET<br>instruction. | Disabled, 1<br>event latched.<br>Enabled by IRET<br>instruction. |  |  |

|                                  |                                                |                                                                                              |                  |                                                                  |                                                                     |                                                                  |                                                                  |  |  |

| SMM<br>Interrupt                 | NO, PWI# is output during SMM mode.            | NO, SMI# is output during SMM mode.                                                          |                  | 1 event latched.                                                 | 1 event<br>latched.                                                 | 1 event latched.                                                 | 1 event latched.                                                 |  |  |

| HALT                             | YES, if IF=1<br>or MSR1000<br>[5]=1            | YES                                                                                          |                  | YES, if INTR or<br>NMI enabled.                                  | YES, if INTR or NMI enabled.                                        | YES, if INTR or<br>NMI enabled.                                  | YES, if INTR or<br>NMI enabled.                                  |  |  |

| Warm<br>Reset                    | None                                           | NO                                                                                           |                  | NO                                                               | NO                                                                  | INIT                                                             | INIT                                                             |  |  |

| A20M#                            | Recognized                                     | Ignored                                                                                      |                  | Recognized                                                       | Recognized                                                          | Recognized                                                       | Recognized                                                       |  |  |

| Access<br>to<br>System<br>Memory | Cached                                         | Cached                                                                                       |                  | Cached                                                           | Cached                                                              | Cached                                                           | Cached                                                           |  |  |

| Access<br>to<br>SMM<br>Memory    | Not cached                                     | Not cached                                                                                   |                  | Cached, unless<br>KEN# =1 during<br>access                       | Cached, unless<br>KEN# =1<br>during access                          | Cached, unless<br>KEN# =1 during<br>access                       | Cached, unless<br>KEN# =1 during<br>access                       |  |  |

| Table 2: System Management Mode  |                                                |                                                                                              |                  |                                                                  |                                                                     |                                                                  |                                                                  |  |  |

#### Low Power Halt

All of the processors listed in Table 3, except the standard version of Intel 486DX2/DX4 and the Intel Pentium P5, offer a low power halt function. This is accessed through the HLT instruction. The IBM 486DX2/DX4 also offers hardware entry through the SUSP# pin. The IBM processors must enable this function before it can be used, and Intel processors always have this function enabled. The IBM processors stop the internal clocks during low power halt. The external clock on the Intel Pentium P54C cannot be stopped the during this state, it must return to normal state before stopping the external clock.

|       | <b>6</b>                    | 6 0 0 0 5 148<br>BLSX2/SX3 IBM 486DX2/DX4                         |      | 486DX2 <b>②</b>                          | <b>@</b><br>I486DX4                      | Intel Pentium ②     |                                     |

|-------|-----------------------------|-------------------------------------------------------------------|------|------------------------------------------|------------------------------------------|---------------------|-------------------------------------|

|       | DL3A2/3A3                   | IDM 480DAZ/DA4                                                    | Std. | SL Enhanced                              | 1400DA4                                  | P5(60 or<br>66 MHz) | P54C (90 or<br>100MHz)              |

| Entry | HLT instruction             | HW: SUSP#<br>SW: HLT<br>instruction                               |      | HLT instruction                          | HLT instruction                          |                     | HLT instruction                     |

|       | RESET, PWI#,<br>INTR or NMI | HW: RESET or<br>deassert SUSP#<br>SW: RESET, SMI#,<br>INTR or NMI |      | RESET,<br>SRESET,<br>SMI#,INTR or<br>NMI | RESET,<br>SRESET,<br>SMI#,INTR or<br>NMI |                     | RESET, INIT,<br>SMI#,INTR or<br>NMI |

Always

enabled

ON

Always

enabled

ON

Always enabled

ON

Table 3 summarizes the low power halt feature.

# Adjustable Core Clock Multiplier

MSR1000[13]=1 | HW: CCR2[7]=1

OFF

SW: CCR2[3]=1

Enable

Internal

Clocks

OFF

Table 3: Low Power Halt

This feature allows the speed of the CPU core clock to be adjusted with respect to the external bus clock. It is available on the IBM 486SX2, IBM 486SX3, Intel DX4 and 100MHz version of the Intel Pentium P54C. The other processors in Table 4 operate the core at a fixed ratio (2x for 486DX2 & 3x for 486DX4 CPUs, 1x for Intel Pentium P5, 1.5x for 90MHz Intel Pentium P54C).

The IBM 486SX2 and 486SX3 are capable of running the core at 1x, or 2x. The 486SX3 can also run the core at 3x. The default is 1x, and it is controlled by writing a configuration register after RESET. The Intel DX4 operates the core at 2x or 3x. The default is 3x, and it is controlled by tying the CLKMUL pin at RESET. The 100MHz version of the Intel Pentium P54C operates the core at 1.5x or 2x, with a maximum internal frequency of 100MHz. It is controlled by tieing the BF pin at RESET.

Table 4 shows the core clock multiplier for each processor.

Page 7 of 12 October 12, 1995 Fax #40012

|          | © IBM <b>①④⑤</b> I486DX2 <b>②</b>                                       |        | X2 ②   | <b>2</b> | Intel Pentium ⑦ |                                                                                                                                         |                 |                                                    |

|----------|-------------------------------------------------------------------------|--------|--------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------|

|          | BL3A2/3A3                                                               | 486DX2 | 486DX4 | Standard | SL<br>Enhanced  | 1486DX4                                                                                                                                 | P5(60 or 66MHz) | P54C (90 or<br>100MHz)                             |

| Multiple | 1X, 2X or 3x.<br>Default is 1X. Write<br>MSR1002[26:24]<br>after RESET. | 2X     | 3X     | 2X       | 2X              | 2X, 2 5X or 3X. Default is 3X. Tie CLKMUL at RESET  2X: CLKMUL=V <sub>ss</sub> 2.5X: CLKMUL=BREQ 3X: CLKMUL=V <sub>cc</sub> or floating | 1X              | 1.5X or 2X.<br>Default is 1.5X.<br>Tie BF at RESET |

| Table 4: | Core Clock Multipli                                                     | er     |        |          |                 |                                                                                                                                         |                 |                                                    |

# **Dynamic Frequency Shift**

This feature is available on all IBM processors, Intel SL Enhanced 486DX2, Intel DX4 and Intel Pentium P54C. It allows the system to vary the frequency of the external clock after power up. The IBM 486SX2 and 486SX3 activate this feature through the DFS\_REQ# pin or a configuration bit. The IBM 486DX2/DX4 always has this feature ready for use, and Intel processors activate this through the STPCLK# pin.

Table 5 shows how to use dynamic frequency shift on each processor.

|         | <b>6</b>                                                                                                                                                       | 0.00                                         |     | I486DX2 ②                                             | <b>②</b>                                           | Intel Pentium ⑦    |                                                       |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----|-------------------------------------------------------|----------------------------------------------------|--------------------|-------------------------------------------------------|--|

|         | BLSX2/SX3                                                                                                                                                      | BL486DX2<br>/DX4                             | Std | SL Enhanced                                           | 1486DX4                                            | P5(60 or<br>66MHz) | P54C (90 or 100<br>MHz)                               |  |

|         | HW: Assert DFS_REQ#,<br>wait for DFS_RDY#, then<br>change frequency of CLK2.<br>SW: Set MSR1002[27] wait<br>for MSR1002[28], then<br>change frequency of CLK2. | Change<br>frequency<br>of clock any<br>time. |     | Assert STPCLK#<br>then change<br>frequency of<br>CLK. | Assert STPCLK#<br>then change<br>frequency of CLK. |                    | Assert STPCLK#<br>then change<br>frequency of<br>CLK. |  |

| Enable  | HW:MSR1000[10]=1<br>MSR1000[29]=1<br>SW: Always enabled                                                                                                        | Always<br>enabled                            |     | Always enabled                                        | Always enabled                                     |                    | Always enabled                                        |  |

| Table 5 | Dynamic Frequency Shift                                                                                                                                        |                                              |     |                                                       |                                                    |                    |                                                       |  |

### **Additional Features**

Table 6 shows some additional power management features. The primary one is the ability to stop the external clock. Stop clock is available on all processors except the standard version of Intel 486DX2/DX4 and Intel's Pentium P5. It is accessed through the HLT instruction on IBM processors and the STPCLK# pin on Intel processors. The IBM 486DX2/DX4 can also stop clocks using the SUSP# pin.

Page 8 of 12 October 12, 1995 Fax #40012

|                                   | 6                    | 0.45                     | I486DΣ       | K2 <b>②</b>                                                                                                          | 2                                                                                                                       | Intel Pentium ⑦    |                     |  |

|-----------------------------------|----------------------|--------------------------|--------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|--|

|                                   | BLSX2/SX3            | IBM<br>486DX2/DX4        | Standard     | SL<br>Enhanced                                                                                                       | I486DX4                                                                                                                 | P5(60 or<br>66MHz) | P54C (90 or 100MHz) |  |

| Stop External<br>Clock            | Yes<br>(HLT)         | Yes<br>(HLT or<br>SUSP#) | No           | Yes<br>(STPCLK#)                                                                                                     | Yes<br>(STPCLK#)                                                                                                        | No                 | Yes<br>(STPCLK#)    |  |

| Tri-state Outputs<br>& Power Down | No                   | Yes<br>(UP#)             | Yes<br>(UP#) | Yes<br>(UP#)                                                                                                         | Yes<br>(UP#)                                                                                                            | No                 | No                  |  |

| Cache Low Power                   | Yes<br>(MSR1004[28]) | No                       | No           | No                                                                                                                   | No                                                                                                                      | No                 | No                  |  |

| FPU powers down when idle         | No                   | Yes                      | No           | No                                                                                                                   | No                                                                                                                      | No                 | No                  |  |

| CPU powers down<br>when idle      | No                   | No                       | No           | Yes.<br>CPU<br>reduces core<br>clock to 1X<br>when idle<br>and waiting<br>for read data<br>from<br>memory or<br>I/O. | Yes.<br>CPU<br>reduces<br>core clock<br>to 1X when<br>idle and<br>waiting for<br>read data<br>from<br>memory or<br>I/O. | No                 | No                  |  |

| Power Supply                      | 3.0V - 4.2V          | 3.3 V or 5.0 V           | 5.0 V        | 3.3 V or<br>5.0 V                                                                                                    | 3.45 V                                                                                                                  | 5.0V               | 3.3 V               |  |

| Table 6: Addition                 | al Features          | 1                        | 1            | II.                                                                                                                  | 1                                                                                                                       | I.                 | 1                   |  |

# **Power Saving Comparison**

Tables 7 and 8 give numeric values for power dissipation in the normal and low power states. Most notable in the low power state is the Intel Pentium P54C, which consumes much more power than any other processor in Table 8 when the external clock is running.

Page 9 of 12 October 12, 1995 Fax #40012

|                        | 6                                                   | 045               | I486D                                              | X2 <b>②</b>                                        | 2                                                   | Intel Penti                                                         | um ⑦                                               |

|------------------------|-----------------------------------------------------|-------------------|----------------------------------------------------|----------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|

|                        | BLSX2/SX3                                           | IBM<br>486DX2/DX4 | Standard                                           | SL Enhanced                                        | I486DX4                                             | P5(60 or 66MHz)                                                     | P54C (90 or<br>100MHz)                             |

| V <sub>cc</sub> =3.3 V |                                                     |                   |                                                    | I <sub>cc</sub> =0.46A (1)<br>P=1.52W<br>(f=50MHz) |                                                     |                                                                     | I <sub>cc</sub> =1.86A<br>P=6.15W<br>(f=90MHz)     |

|                        |                                                     |                   |                                                    |                                                    |                                                     |                                                                     | I <sub>cc</sub> =1.18A (1)<br>P=3.9W<br>(f=100MHz) |

| $V_{cc} = 3.45 V$      |                                                     |                   |                                                    |                                                    | I <sub>cc</sub> =0.83A (1)<br>P=2.85W<br>(f=75MHz)  |                                                                     |                                                    |

|                        |                                                     |                   |                                                    |                                                    | I <sub>cc</sub> =1.17A (2)<br>P=4.04W<br>(f=100MHz) |                                                                     |                                                    |

| V <sub>cc</sub> =3.6V  | I <sub>cc</sub> =0.73A<br>P=2.63W<br>(f=75MHz SX3)  |                   |                                                    |                                                    |                                                     |                                                                     |                                                    |

| V <sub>cc</sub> =4.2V  | I <sub>cc</sub> =1.16A<br>P=4.87W<br>(f=100MHz SX3) |                   |                                                    |                                                    |                                                     |                                                                     |                                                    |

| V <sub>cc</sub> =5.0V  |                                                     |                   | I <sub>cc</sub> =0.78A (1)<br>P=3.88W<br>(f=50MHz) | I <sub>cc</sub> =0.98A (1)<br>P=4.88W<br>(f=66MHz) |                                                     | I <sub>cc</sub> =2.37-2.60A<br>(1)<br>P=11.85-13.0W<br>(f=60-66MHz) |                                                    |

|                        |                                                     |                   | I <sub>cc</sub> =1.03A<br>P=5.13W<br>(f=66MHz)     |                                                    |                                                     | (1-00-00IVII IZ)                                                    |                                                    |

| Note: "f"              | indicates internal or                               | peration frequen  | cy.                                                |                                                    |                                                     |                                                                     |                                                    |

| Table 7:               | CPU Power Dissipa                                   | tion Under Norr   | nal Conditions                                     |                                                    |                                                     |                                                                     |                                                    |

Values in table 7 are the BAPCo 93 ratings in all cases except:

- (1) value listed in Intel databook

- (2) DOS edit prompt with menu pulled down.

|                                | 6                                                                                        | 000                                                         | I486D              | X2 ②                                                          | 2                                                               | Intel Pentium ⑦          |                                                                 |  |  |

|--------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------|---------------------------------------------------------------|-----------------------------------------------------------------|--------------------------|-----------------------------------------------------------------|--|--|

|                                | BLSX2/SX3                                                                                | IBM<br>486DX2/DX4                                           | Standard           | SL Enhanced                                                   | I486DX4                                                         | P5(60 or<br>66MHz)       | P54C (90 or<br>100MHz)                                          |  |  |

| Enter<br>Low<br>Power<br>State | HLT when<br>MSR1000[13]=<br>1                                                            | HLT when<br>CCR2[3]=1 or<br>SUSP# when<br>CCR2[7]=1         | No low power state | STPCLK#                                                       | STPCLK#                                                         | No low<br>power<br>state | STPCLK#                                                         |  |  |

|                                |                                                                                          |                                                             | External           | Clock On                                                      |                                                                 |                          |                                                                 |  |  |

| V <sub>cc</sub> =3.3 V         |                                                                                          | I <sub>cc</sub> =9-16 mA<br>P=30-53 mW<br>(f=33-80<br>MHz)  |                    | I <sub>cc</sub> =20-23 mA<br>P=66-76 mW<br>(f=40-50 MHz)      |                                                                 |                          | I <sub>cc</sub> =424-470 mA<br>P=1400-1550 mW<br>(f=90-100 MHz) |  |  |

| V <sub>cc</sub> =3.45V         |                                                                                          |                                                             |                    |                                                               | I <sub>cc</sub> =75-100 mA<br>P=259-345 mW<br>(f=75-100<br>MHz) |                          |                                                                 |  |  |

| V <sub>cc</sub> =3.6V          | I <sub>cc</sub> =30 mA<br>P=108 mW<br>(f=75 MHz)                                         |                                                             |                    |                                                               |                                                                 |                          |                                                                 |  |  |

| $V_{cc}=5.0V$                  |                                                                                          | I <sub>cc</sub> =13-18 mA<br>P=63-90 mW<br>(f=33-80<br>MHz) |                    | I <sub>cc</sub> =35-45 mA<br>P=175-225<br>mW<br>(f=50-66 MHz) |                                                                 |                          |                                                                 |  |  |

|                                |                                                                                          |                                                             | External           | Clock Off                                                     |                                                                 |                          |                                                                 |  |  |

| $V_{cc}=3.3 V$                 |                                                                                          | I <sub>cc</sub> =450 μA<br>P=1.5 mW                         |                    | I <sub>cc</sub> =100 μA<br>P=0.33 mA                          |                                                                 |                          | I <sub>cc</sub> =90 μA<br>P=0.3 mW                              |  |  |

| V <sub>cc</sub> =3.45 V        |                                                                                          |                                                             |                    |                                                               | I <sub>cc</sub> =1 mA<br>P=3.45 mW                              |                          |                                                                 |  |  |

| V <sub>cc</sub> =3.6V          | I <sub>cc</sub> =4 mA<br>P=15 mW                                                         |                                                             |                    |                                                               |                                                                 |                          |                                                                 |  |  |

| $V_{cc}=5.0V$                  |                                                                                          | I <sub>cc</sub> =450 μA<br>P=2.3 mW                         |                    | I <sub>cc</sub> =200 μA<br>P=1 mW                             |                                                                 |                          |                                                                 |  |  |

| Note "f" in databooks          | Note: "f" indicates internal operation frequency.  databooks.  Information obtained from |                                                             |                    |                                                               |                                                                 |                          |                                                                 |  |  |

| Table 8                        | CPU Power Dissip                                                                         | ation in Low Pov                                            | wer State          |                                                               |                                                                 |                          |                                                                 |  |  |

## Conclusion

This paper described five power saving features available on X86 processors. It explained how to use each feature and discussed advantages and disadvantages of certain processors. When selecting a processor for a system, the designer should consider the benefits of power management and decide which features are needed. For more information, please consult the references listed below.

#### **References:**

- 1. IBM 486 DX2 Addendum to the IBM Blue Lightning 486 DX2 Databook, August 11, 1995

- 2. Intel 486 Microprocessor Family Databook, 1994

- 3. Enhanced Am486<sup>TM</sup> Microprocessor Family Datasheet, May, 1995

- 4. IBM 486 DX4 Addendum to the IBM Blue Lightning 486 DX2 Databook, September 12, 1995

- 5. IBM Blue Lightning 486 DX2 Databook, 1994

- 6. IBM Blue Lightning Microprocessor Datasheet, February 7, 1994

- 7. Pentium<sup>™</sup> Family User's Manual, 1994

IBM Corporation 1995. All rights reserved.

IBM and the IBM logo are registered trademarks of International Business Machines Corporation. IBM Microelectronics is a trademark of the IBM Corp.

All other product and company names are trademarks/registered trademarks of their respective holders. 1995 IBM Corp.

This document may contain preliminary information and is subject to change by IBM without notice. IBM makes no representations or warranties that the use of the information or applications herein shall be free of third party intellectual property claims and assumes no responsibility or liability from any use of the information contained herein. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties.

The products described in this document are not intended for use in implantation or other direct life support applications where malfunction may result in physical harm or injury to persons.

NO WARRANTIES OF ANY KIND, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE ARE OFFERED IN THIS DOCUMENT.

All performance data contained in this publication was obtained in a specific environment, and is presented as an illustration. The results obtained in other operating environments may vary.

Page 12 of 12 October 12, 1995 Fax #40012