## IBM 6x86 MICROPROCESSOR

**Appendix**

Sixth-Generation Superscalar Superpipelined x86-Compatible CPU

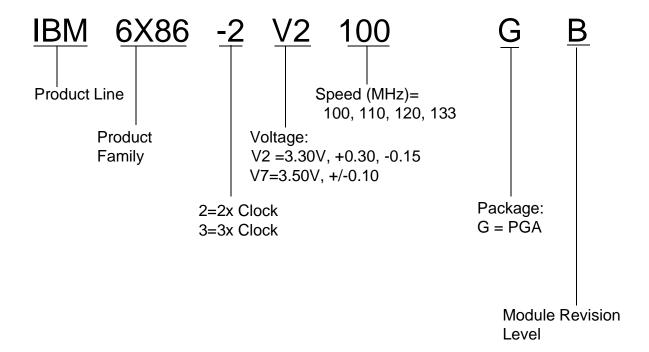

## Ordering Information for Module Revision Level "B" Only

Table A-1. 6x86 Device to P-Rating Conversion

| 6x86 Freque | ncy (MHz) |          |

|-------------|-----------|----------|

| BUS         | CORE      | P-Rating |

| 50          | 100       | P120+    |

| 55          | 110       | P133+    |

| 60          | 120       | P150+    |

| 66          | 133       | P166+    |

| 75          | 150       | P200+    |

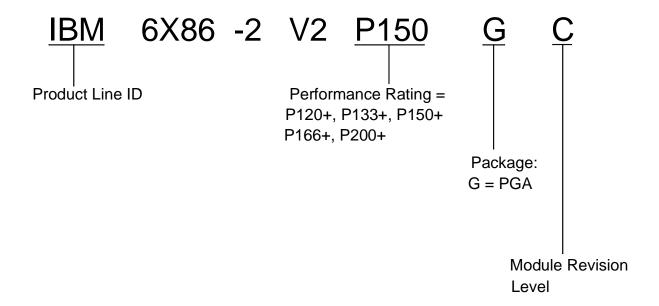

## Ordering Information for Module Revision Level "C" and Later

Table A-2. 6x86 Device to P-Rating Conversion

| 6x86 Frequency (MHz) |      |          |

|----------------------|------|----------|

| BUS                  | CORE | P-Rating |

| 50                   | 100  | P120+    |

| 55                   | 110  | P133+    |

| 60                   | 120  | P150+    |

| 66                   | 133  | P166+    |

| 75                   | 150  | P200+    |

For more information concerning the IBM 6x86 Microprocessor, please visit our website: http://www.chips.ibm.com/products/x86/index.html or call 1-800-IBM-3333.

Index **INDEX** "1+4" Burst Read Cycle **CCR5** Bit Definitions 3-35 2 - 303-7 **Clock Control Clock Count for CPU Instructions** 6-13 **AC** Characteristics 4-5 **Clock Count for FPU Instructions** 6-29 **Configuration Control Registers** 2-23 Address Bus 3-9 **Control Registers** 2-13 Address Region Registers (ARRx) 2-31 Address Space 2-40 D -----**Architecture Overview** 1-1 3-10 Data Bus **Data Bypassing** 1 - 10**Data Forwarding** 1-7 **Back-Off Timing** 3-49 4-4 DC Characteristics **Branch Control** 1-11 2-37 **Debug Registers** Burst Cycle Address Sequence 3-34 Descriptors 2-16 **Burst Write Cycles** 3-37 **Descriptor Table Registers Bus Arbitration** 3-16 and Descriptors 2-15 **Bus Arbitration** 3-46 **Device Identification Registers** 2-36 **Bus Cycle Definition** 3-11 DIRx 2-36 3-12 Bus Cycle Types 3-29 Bus Cycles, Non-pipelined Bus Hold, Signal States During 3-17 **Electrical Specifications** 4-1 3-1 **Bus Interface Error Codes** 2-62 Bus Interface Unit 1-16 **EWBE# Timing** 3-45 **Bus State Definition** 3-26 **Exceptions** 2-56 Exceptions in Real Mode 2-61 Cache Coherency Signals 3-18 F -----Cache Control 3-14 Flags Register 2-9 Cache Control Timing 3-43 Floating Point Unit 1-15 Cache Disable 2-34 FPU Error Interface 3-19 3-50 Cache Inquiry Cycles **FPU Operations** 2-75 Cache Units 1-12 **Functional Blocks** 1-1 2-52 Caches, Memory 3-25 **Functional Timing CCR0** Bit Definitions 2-25 **CCR1** Bit Definitions 2-26 **CCR2** Bit Definitions 2-27 Gates and Protection 2-73 **CCR3** Bit Definitions 2-28 **CCR4** Bit Definitions 2-29

| Т | <br>A 27 |

|---|----------|

|   | 150.0    |

| I                                 | <del></del> | 0 ————                             |      |

|-----------------------------------|-------------|------------------------------------|------|

| I/O Address Space                 | 2-41        | Offset Mechanism                   | 2-42 |

| Initialization and Protected Mode | 2-73        | Out-of-order Processing            | 1-4  |

| Initialization of the CPU         | 2-1         | P                                  |      |

| Instruction Fields, General       | 6-2         |                                    | ~ .  |

| Instruction Line Cache            | 1-13        | Package, Mechanical Drawing        | 5-4  |

| Instruction Pointer Register      | 2-9         | Paging Mechanisms (Detail)         | 2-45 |

| Instruction Set Overview          | 2-3         | Paging Mechanisms (Introduction)   | 1-14 |

| Instruction Set Encodings         |             | Paging - Traditional Mechanism     | 2-45 |

| and Summary                       |             | Paging - Variable-Size Paging      |      |

| Instruction Set Summary           | 6-1         | Mechanism                          | 2-51 |

| Instruction Set Tables            |             | Pin Diagram, 296-Pin SPGA Package  |      |

| Assumptions                       | 6-12        | Pin List, Sorted by Pin Number     | 5-2  |

| Integer Unit                      | 1-2         | Pin List, Sorted by Signal Name    | 5-3  |

| Interrupt Acknowledge Cycles      | 3-41        | Pipeline Stages                    | 1-3  |

| Interrupt and Exception           |             | Pipelined Bus Cycles               | 3-38 |

| Priorities                        | 2-59        | Power and Ground Connections       | 4-1  |

| Interrupt Control                 | 3-13        | Power Management Interface         | 3-22 |

| Interrupt Vectors                 | 2-57        | Power Management Interface Timing  | 3-61 |

| Interrupts and Exceptions         | 2-55        | Privilege Level, Requested         | 2-8  |

| J                                 |             | Privilege Levels                   | 2-71 |

| J                                 |             | Programming Interface              | 2-1  |

| JTAG Interface                    | 3-24        | Protected Mode Address Calculation | 2-44 |

| L                                 |             | Protection, Segment and Page       | 2-71 |

| I D A #                           | 2.25        | Pull-Up and Pull-Down Resistors    | 4-1  |

| LBA#                              | 2-35        | R                                  |      |

| Lines, within the Cache           | 2-53        | DAW D 1                            | 1.0  |

| Lock Prefix                       | 2-3         | RAW Dependency Example             | 1-8  |

| M                                 |             | Recommended Operating Conditions   |      |

| Maximum Ratings, Absolute         | 4-2         | Region Control Registers (RCRx)    | 2-33 |

| Memory Addressing                 | 2-43        | Register Renaming                  | 1-4  |

| Memory Addressing Methods         | 2-41        | Register Sets                      | 2-4  |

| Memory Management Unit            | 1-14        | Registers, Control                 | 2-13 |

| MESI States, Unified Cache        | 2-52        | Registers, General Purpose         | 2-4  |

| Mode State Diagram                | 2-70        | Registers, 6x86 Configuration      | 2-23 |

| <b>G</b>                          | 2 70        | Registers, System Set              | 2-11 |

| N                                 |             | Requested Privilege Level          | 2-8  |

| NC and Reserved Pins              | 4-1         | Reset Control                      | 3-7  |

| Non-pipelined Bus Cycles          | 3-29        | RESET Timing                       | 3-25 |

Index

| S                                  | _    |

|------------------------------------|------|

| Scatter/Gather Buffer Interface    | 3-19 |

| Scatter/Gather Buffer              |      |

| Interface Timing                   | 3-56 |

| Sectors, Cache                     | 2-53 |

| Segment Registers                  | 2-7  |

| Selector Mechanism                 | 2-44 |

| Selectors                          | 2-7  |

| Shutdown and Halt                  | 2-69 |

| Signal Description Table           | 3-2  |

| Signal Groupings                   | 3-1  |

| SMI# Interrupt Timing              | 3-42 |

| System Management Mode (SMM)       | 2-63 |

| SMM Instructions                   | 2-67 |

| SMM Memory Space                   | 2-68 |

| SMM Memory Space Header            | 2-65 |

| SMM Operation                      | 2-64 |

| Stop Grant (Special Bus Cycle)     | 3-12 |

| Stop Grant and SUSP#               | 3-22 |

| Speculative Execution              | 1-12 |

| Suspend Mode, HALT Initiated       | 3-62 |

| Suspend Mode, Signal States During | 3-23 |

| System Management Mode             | 2-63 |

| T                                  |      |

| Task Register                      | 2-20 |

| Test Registers                     | 2-39 |

| Testing of the Unified Cache       | 2-53 |

| Thermal Characteristics Timing, Functional Translation Lookaside Buffer Translation Lookaside Buffer Testing | 5-6<br>3-25<br>2-45<br>2-47 |

|--------------------------------------------------------------------------------------------------------------|-----------------------------|

| U                                                                                                            | _                           |

| Unified Cache                                                                                                | 1-12                        |

| Unified Cache Testing                                                                                        | 2-53                        |

| V                                                                                                            | _                           |

| Variable-Size Paging                                                                                         |                             |

| Mechanism                                                                                                    | 1-14                        |

| Variable-Size Paging                                                                                         |                             |

| Mechanism                                                                                                    | 2-51                        |

| Virtual 8086 Mode                                                                                            | 2-74                        |

| W                                                                                                            | -                           |

| WAR Dependency Example                                                                                       | 1-5                         |

| WAW Dependency Example                                                                                       | 1-6                         |

| Weak Locking                                                                                                 | 2-34                        |

| Weak Write Ordering                                                                                          | 2-34                        |

| Write Gathering                                                                                              | 2-35                        |

| Write Through                                                                                                | 2-35                        |