# PROCESSOR Data Sheet

This is **Version 1.0** of the IDT WinChip 2 Processor data sheet.

The latest versions of this data sheet may be obtained from www.winchip.com

#### © 1998 Integrated Device Technology, Inc. All Rights Reserved

Integrated Device Technology, Inc. reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to any implied warranty of merchantability or fitness for a particular purpose. No license, express or implied, to any intellectual property rights is granted by this document.

Centaur Technology, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. Centaur Technology, Inc. disclaims responsibility for any consequences resulting from the use of the information included herein.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as components in life support or other medical devices or systems (hereinafter life support devices) unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices are devices which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. This policy covers any component of a life support device or system whose failure to perform can cause the failure of the life support device or system, or to affect its safety or effectiveness.

WinChip, WinChip 2, WinChip C6, and CentaurHauls are trademarks of Integrated Device Technology Corporation.

AMD, AMD K6, and AMD K6-2 are trademarks of Advanced Micro Devices, Inc. Microsoft and Windows are registered trademarks of Microsoft Corporation.

Intel and MMX are trademarks of the Intel Corporation. Pentium is a registered trademark of the Intel Corporation.

Cyrix is a registered trademark and Cyrix 6X86MX is a trademark of the Cyrix Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

IDT WINCHIP 2™ PROCESSOR DATA SHEET

# **REVISION HISTORY**

| DATE    | VERSION | REVISION        |

|---------|---------|-----------------|

| 10/1998 | 1.0     | Initial release |

# **CONTENTS**

| RI | EVISION F      | ISTORY                                   | III  |

|----|----------------|------------------------------------------|------|

| C  | ONTENTS        |                                          | IV   |

| 1  | INTROD         | JCTION                                   | 1-1  |

|    | 1.1            | Basic Features                           | 1-1  |

|    |                | Processor Versions                       |      |

|    |                | Competitive Comparisons                  |      |

|    |                | Compatibility                            |      |

|    |                | Data Sheet Assumptions                   |      |

| 2  | WINCHIE        | 2 ARCHITECTURE                           | 2-1  |

|    | 2.1            | Introduction                             | 2-1  |

|    |                | Key Concepts                             |      |

|    |                | Component Summary                        |      |

|    |                | 3.1 General Architecture                 |      |

|    | 2.             | 3.2 I-Cache                              |      |

|    | <del>-</del> - | 3.3 Translator Unit                      |      |

|    |                | 3.4 Branch Prediction Unit               |      |

|    |                | 3.5 Execution Unit                       |      |

|    |                | 3.6 D-Cache                              |      |

|    |                | 3.7 X86 Fetch Unit                       |      |

|    |                | 3.8 FP Unit                              |      |

|    |                | 3.9 MMX Units                            |      |

|    |                | 3.11 Bus Unit                            |      |

| 3  | PROGR <i>A</i> | MMING INTERFACE                          | 3-1  |

|    | 3.1            | General                                  | 3-1  |

|    |                | Additional Functions                     |      |

|    |                | Machine-Specific Functions               |      |

|    |                | 3.1 General                              |      |

|    | _              | 3.2 Standard CPUID Instruction Functions |      |

|    | 3.             | 3.3 Extended CPUID Instruction Functions |      |

|    | 3.             | 3.4 Processor Identification             |      |

|    | 3.             | 3.5 EDX Value After Reset                | 3-10 |

|    | 3.             | 3.6 CR4                                  |      |

|    | 3.             | 3.7 Machine-Specific Registers           | 3-12 |

| 3.4 Omitted Functions                                                                                                                                                                                                                                                                                        | 3-12                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 3.4.1 Pentium Appendix H Enhancements                                                                                                                                                                                                                                                                        |                                      |

| 3.4.2 Other Functions                                                                                                                                                                                                                                                                                        | 3-13                                 |

| 4 HARDWARE INTERFACE                                                                                                                                                                                                                                                                                         | 4-1                                  |

| 4.1 Bus Interface                                                                                                                                                                                                                                                                                            | 4-1                                  |

| 4.1.1 Differences                                                                                                                                                                                                                                                                                            | 4-1                                  |

| 4.1.2 Clarifications                                                                                                                                                                                                                                                                                         |                                      |

| 4.1.3 Omissions                                                                                                                                                                                                                                                                                              |                                      |

| 4.2 Signal Summary                                                                                                                                                                                                                                                                                           |                                      |

| 4.3 Power Management                                                                                                                                                                                                                                                                                         |                                      |

| 4.3.1 Static Power Management                                                                                                                                                                                                                                                                                |                                      |

| 4.3.2 Dynamic Power Management                                                                                                                                                                                                                                                                               |                                      |

| 4.4 Test & Debug4.4.1 Machine Check                                                                                                                                                                                                                                                                          |                                      |

| 4.4.1 Machine Check4.4.2 BIST                                                                                                                                                                                                                                                                                |                                      |

| 4.4.3 Internal Error Detection                                                                                                                                                                                                                                                                               |                                      |

| 4.4.4 JTAG                                                                                                                                                                                                                                                                                                   |                                      |

| 4.4.5 Debug Port                                                                                                                                                                                                                                                                                             |                                      |

| 5 ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                                                  | 5-1                                  |

|                                                                                                                                                                                                                                                                                                              |                                      |

| 5.1 AC Timing Tables for 100-MHz Bus                                                                                                                                                                                                                                                                         | 5-1                                  |

| 3                                                                                                                                                                                                                                                                                                            |                                      |

| 5.2 AC Timing Tables for 83-MHz Bus                                                                                                                                                                                                                                                                          | 5-5                                  |

| <ul><li>5.2 AC Timing Tables for 83-MHz Bus</li><li>5.3 AC Timing Tables for 75-MHz Bus</li></ul>                                                                                                                                                                                                            | 5-5<br>5-9                           |

| <ul><li>5.2 AC Timing Tables for 83-MHz Bus</li><li>5.3 AC Timing Tables for 75-MHz Bus</li><li>5.4 AC Timing Tables for 66-MHz Bus</li></ul>                                                                                                                                                                | 5-5<br>5-9<br>5-13                   |

| 5.2 AC Timing Tables for 83-MHz Bus                                                                                                                                                                                                                                                                          | 5-5<br>5-9<br>5-13                   |

| 5.2 AC Timing Tables for 83-MHz Bus                                                                                                                                                                                                                                                                          | 5-5<br>5-9<br>5-13<br>5-17           |

| <ul> <li>5.2 AC Timing Tables for 83-MHz Bus</li> <li>5.3 AC Timing Tables for 75-MHz Bus</li> <li>5.4 AC Timing Tables for 66-MHz Bus</li> <li>5.5 AC Timing Tables for 60-MHz Bus</li> <li>5.6 DC Specifications</li> </ul>                                                                                | 5-5<br>5-9<br>5-13<br>5-17<br>5-21   |

| <ul> <li>5.2 AC Timing Tables for 83-MHz Bus</li></ul>                                                                                                                                                                                                                                                       | 5-55-95-135-215-215-215-21           |

| <ul> <li>5.2 AC Timing Tables for 83-MHz Bus</li> <li>5.3 AC Timing Tables for 75-MHz Bus</li> <li>5.4 AC Timing Tables for 66-MHz Bus</li> <li>5.5 AC Timing Tables for 60-MHz Bus</li> <li>5.6 DC Specifications</li> <li>5.6.1 Recommended Operating Conditions</li> <li>5.6.2 Maximum Ratings</li> </ul> | 5-55-95-135-215-215-215-21           |

| <ul> <li>5.2 AC Timing Tables for 83-MHz Bus</li></ul>                                                                                                                                                                                                                                                       | 5-55-95-175-215-215-225-23           |

| 5.2 AC Timing Tables for 83-MHz Bus                                                                                                                                                                                                                                                                          | 5-55-95-175-215-215-225-23           |

| 5.2 AC Timing Tables for 83-MHz Bus                                                                                                                                                                                                                                                                          | 5-55-95-135-175-215-215-236-1        |

| 5.2 AC Timing Tables for 83-MHz Bus                                                                                                                                                                                                                                                                          | 5-55-95-135-175-215-215-225-236-1    |

| 5.2 AC Timing Tables for 83-MHz Bus                                                                                                                                                                                                                                                                          | 5-55-95-135-175-215-215-225-236-16-6 |

| 5.2 AC Timing Tables for 83-MHz Bus                                                                                                                                                                                                                                                                          | 5-55-95-135-175-215-215-236-16-16-6  |

| 5.2 AC Timing Tables for 83-MHz Bus                                                                                                                                                                                                                                                                          | 5-55-95-135-175-215-215-226-16-67-1  |

# September 1998

| 7.5 Recommended Thermal Solutions                    | 7-4  |

|------------------------------------------------------|------|

| 7.6 Contacts                                         | 7-5  |

| APPENDIX A. MACHINE SPECIFIC REGISTERS               | A-1  |

| A.1 General                                          | A-1  |

| A.2 Category 1 MSRs                                  | A-4  |

| 02h: TR1 (Pentium Processor Parity Reversal Register | ,    |

| 0Eh: TR12 (Pentium Processor Feature Control)        |      |

| 10h: TSC (Time Stamp Counter)                        |      |

| 11h: CESR (Control & Event Select Register)          |      |

| 12h-13h: CTR0 & CTR1 (Event Counters 0 & 1)          |      |

| 107h: FCR (Feature Control Register)                 |      |

| 109h: FCR3 (Feature Control Register 3)              |      |

| 10Ah: FCR4 (Feature Control Register 4)              |      |

| A.3 Memory Configuration Registers                   | A-12 |

| General                                              |      |

| Memory Configuration Registers                       | A-13 |

| MCR Control Register                                 | A-15 |

| APPENDIX B. COMPATIBILITY                            | B-1  |

| B.1 Introduction                                     | B-1  |

| B.2 Bus Compatibility                                | B-2  |

| B.3 Integer instruction Compatibility                | B-4  |

| B.4 Floating-Point Compatibility                     |      |

|                                                      |      |

#### 1 INTRODUCTION

The IDT WinChip  $2^{\text{TM}}$  processor, designed by Centaur Technology Inc., is a plug-compatible alternative to the Intel® Pentium® processor with MMX<sup>TM</sup> technology (also known informally as the P55C processor). In addition to the Intel Pentium family, the IDT WinChip 2 processor also directly competes with other Socket 7-compatible processors such as the AMD K6- $2^{\text{TM}}$ , the AMD K6- $2^{\text{TM}}$ , and the Cyrix® 6x86MX<sup>TM</sup> processors.

The IDT WinChip 2 processor family is based on a unique Centaur-developed design approach and is manufactured with the IDT 0.35 and 0.25-micron CMOS technologies as well as IBM 0.25-micron technology. These technologies provide high-performance, low-cost, and low-power solutions to the desktop and mobile personal computer market.

When considered individually, the function, performance, and cost of the IDT WinChip 2 processor family are all very competitive. When considered as a whole, the IDT WinChip 2 processor family offers a breakthrough level of *value*.

#### 1.1 BASIC FEATURES

The IDT WinChip 2 processor family comprises several versions. All family versions share the following common features:

- Plug-compatible with the Intel Pentium processorbus, electrical interface, and physical package (Socket 7).

- Software-compatible with Intel Pentium processors and the thousands of X86 software applications

- Software-compatible with Intel MMX technology

- Two large (32-KB each) on-chip caches.

- Two large TLBs (128 entries each).

- Sophisticated branch prediction mechanism.

- Two MMX units with superscalar execution.

- Bus speeds up to 100 MHz (Super7<sup>TM</sup> bus).

- Low cost due to a very small die (58 mm² in IDT 0.25-micron technology) and use of low-cost technology.

# Notable Features

#### 1.2 PROCESSOR VERSIONS

The IDT WinChip 2 processor is suitable for both desktop and mobile applications. These basic versions are offered in several internal speed ranges and several different voltage settings.

# WinChip 2

- 3DNow!TM instructions. These new instructions compatible with the 3DNow! instructions included in the AMD K6-2 processor. These instructions provide significant performance improvements for 3D geometry and lighting calculations.

- 3DNow! instructions are directly utilized by Microsoft's Direct3D version 6 as well as by many games.

# The IDT WinChip 2 processor is initially available in several speed grades:

225 MHz (75-MHz bus),

240 MHz (60-MHz bus)

250 MHz (83-MHz bus)

266 MHz (66-MHz bus)

300 MHz (75 & 100 MHz bus)

Future versions of the WinChip 2 processor will provide other speed grades and bus speed combinations. In particular, the 100 MHz bus will be supported at 233, 250 and 266 MHz.

# Speed Versions

# Voltage **Versions**

IDT WinChip 2 processors initially support one of two voltage ranges:

3.52V (3.45V3.6V)

3.3V (3.135V<del>3</del>.6V)

Future versions of the WinChip 2 processor will support lower core voltages.

#### 1.3 COMPETITIVE COMPARISONS

The following tables summarize the major features of the IDT WinChip 2 processor and its primary competitors. The competitive information is as specified in the competitive processor's data sheets and is accurate only as of the time this datasheet was written. The features are those that characterize the primary capabilities of an x86 processor. Additional specifics on the WinChip 2 processor design are found in Chapter 2.

The major themes of this summary are:

- The IDT WinChip 2 processor has equivalent or better cache and TLB capabilities. These are critical to system performance for modern PC operating systems and applications. (See Table 1-1)

- The IDT WinChip 2 processor has a generally simpler internal architecture than its competitors. However, the IDT WinChip 2 selectively implements advanced features like superscalar execution and branch prediction. This design approach results in a good performance with a small die size (See Table 1-2)

- The IDT WinChip 2 processor has a much smaller die size for more basic technology. This small size benefits the user by facilitating low price (See Table 1-3)

Table 1-1. Cache and TLB Characteristics.

| MA IOD EE      | MAJOR FEATURES |           | INTEL   | AMD     | CYRIX                     |

|----------------|----------------|-----------|---------|---------|---------------------------|

| MAJOR FEATURES |                | WINCHIP 2 | P55     | K6      | 6x86MX                    |

| I-Cache        | Size           | 32 KB     | 16 KB   | 32 KB   | 256                       |

|                | Data Ways      | 2         | 4       | 2       | assoc                     |

| D-Cache        | Size           | 32 KB     | 16 KB   | 32 KB   | 64 KB unified I & D cache |

|                | Data Ways      | 4         | 4       | 2       | 4                         |

| TLB            | Size (I / D)   | 128 / 128 | 32 / 64 | 64 /128 | 16                        |

|                | Ways           | 8         | assoc   | ?       | direct                    |

|                | L2 TLB         | N         | N       | N       | 64 x 6                    |

| Page Dir Cache |                | 8 entries | N       | N       | N                         |

Table 1-2. Microarchitecture Characteristics.

| MAJOR FEATURES        |        | WINCHIP 2           | INTEL<br>P55        | AMD<br>K6            | CYRIX<br>6x86MX      |

|-----------------------|--------|---------------------|---------------------|----------------------|----------------------|

| <b>Decode</b> General |        | 1 Inst<br>In-order  | 2 Insts<br>In-order | 3 Insts<br>In-order  | 2 Insts<br>In-order  |

|                       | MMX/3D | 2 Insts<br>In-order |                     |                      |                      |

| Issue & Execute       | ,      | Single<br>In-order  | 2 Insts<br>In-order | 3 insts<br>Out-order | 2 Insts<br>Out-order |

|                       | MMX/3D | 2 Insts<br>In-order |                     |                      |                      |

| Branch Prediction     | on     | Υ                   | Y                   | Υ                    | Υ                    |

| Call/Return Stac      | :k     | 8 entries           | Y                   | 16 entries           | N                    |

Table 1-3. Technology & Die Size

| MAJOR FEATURES          |  | WINCHIP 2         | INTEL<br>P55 | AMD<br>K6-2        | CYRIX<br>6x86MX |

|-------------------------|--|-------------------|--------------|--------------------|-----------------|

| <b>Technology</b> Metal |  | 0.35μ /<br>0.28μ  | 0.25μ        | 0.25μ              | 0.25μ           |

| Poly                    |  | 0.26μ             |              |                    |                 |

|                         |  | 5LM               | 4LM          | 5LM+LI             | 4LM             |

| Die Size                |  | 58 mm²<br>(0.28μ) | 98 mm²       | 81 mm <sup>2</sup> | 88 mm²          |

#### 1.4 COMPATIBILITY

The IDT WinChip 2 processor is compatible with the Intel Pentium processor with MMX technology.

An IDT WinChip 2 processor can plug into existing Pentium processor-based desktop and portable system boards and can operate without requiring changes to the system hardware. In some cases, a special BIOS may be needed (due to possible use by the BIOS of Pentium processor-unique machine specific registers). Currently, BIOS support for the IDT WinChip 2 processor is available from Award, AMI, Phoenix, and SystemSoft.

The IDT WinChip 2 processor does not provide Pentium-compatible dual processing (neither do the mobile Pentium processor, the AMD K6 and AMD K6-2 processors, nor the Cyrix 6x86MX processor).

Note that *all* processors developed for use in PCs (\$86" processors) have some differences in low-level functions. (These include differences between the various Intel processors and between Intel processors and the equivalent Cyrix and the AMD processors.) The IDT WinChip 2 processor has similar differences.

Centaur has performed extensive testing of hundreds of PC boards, peripherals, software applications, and operating systems to confirm the IDT WinChip 2 processor's compatibility.

Indicative of this compatibility, the IDT WinChip 2 processor has XXCAL Inc. Platinum Certification (their highest compatibility rating) and will soon obtain Windows 98 and Windows NT certification.

#### 1.5 DATA SHEET ASSUMPTIONS

The IDT WinChip 2 processor specifications are directly based upon the Pentium processor's external specifications as defined by: (1) publicly available Intel publications, and (2) by the actual behavior (derived from testing) of the Pentium processor. This data sheet book provides only minimal descriptions of these Pentium-compatible functions. The major emphasis in this document is to describe differences from the explicit and implicit (behavioral) Pentium specifications.

The intent of these specifications is to make it easy for a board designer, system designer, or BIOS developer to utilize the IDT WinChip 2 processor in place of the Pentium processor or the Pentium processor with MMX technology. (This, of course, makes it trivially easy for the end-user to be able to exploit the advantages of the IDT WinChip 2 processor.) We assume that the reader is a potential direct user of the IDT WinChip 2 processor and is thus familiar with the specifications of the Pentium processor.

Table 1-4 lists some relevant documents that define the reference x86 architecture.

Table 1-4. x86 Architecture Specification Documents

| DOCUMENT TITLE                                         | INTEL<br>ORDER# | VERSION |

|--------------------------------------------------------|-----------------|---------|

| Intel Architecture Software Developer's Manual, Vol. 1 | 243190          | 001     |

| Intel Architecture Software Developer's Manual, Vol. 2 | 243191          | 001     |

| Intel Architecture Software Developer's Manual, Vol. 3 | 243192          | 001     |

| Pentium Processor Family Developer's Manual            | 241428          | 005     |

| Pentium Processor with MMX Technology                  | 243185          | 004     |

| Pentium Processor Specification Update                 | 242480          | 027     |

#### 2 WINCHIP 2 ARCHITECTURE

## 2.1 INTRODUCTION

The IDT WinChip 2 processor is externally (bus and software) compatible with the Intel Pentium processor with MMX Technology. However, the internal architecture and design of the IDT WinChip 2 processor is very different from that of the Pentium processor and other contemporary x86 processors such as the AMD K6 and Cyrix 6x86MX processors. The IDT WinChip 2 processor uses a unique design approach that provides significant benefits to the end-user.

This design approach provides high performance at low cost and low power using a unique architecture that includes large onchip caches and is extensively optimized for the target PC environment. The resulting IDT WinChip 2 processor is smaller (die size is only 58 mm² in 0.25 $\mu$  geometry technology) than any other x86 processor yet has comparable performance to the most recent processors.

Philosophically, the IDT WinChip 2 processor's internal design is a return to the same basic concepts of RISC design that allowed microprocessor performance breakthroughs in the 1980's. Recently, however, contemporary x86 processors have followed a different path using very complex internal designs employing advanced architecture concepts such as superscalar execution, out-of-order instruction execution, reorder buffers, non-blocking caches, and so forth (these terms are all found in the datasheets of competitive products).

Unfortunately, while these advanced technical concepts make for good technical reading, the real bottom-line benefit that they provide to the end-user has been limited; especially when considering the resultant large chip sizes (resulting in high costs) and high power consumption. No such advanced technical hocus-pocus is to be found on an IDT WinChip 2 processor it merely offers good compatibility with good performance, low cost, and low power consumption.

#### 2.2 KEY CONCEPTS

The key concepts underlying the IDT WinChip 2 processor design are:

- Simple instructions (load, store, branch, ALU) dominate instruction execution time. This is the basic RISC design concept, which is also true in the x86 architecture: over 90% of instructions executed come from these basic categories. Of course, "simple" x86 instructions are more complex than corresponding RISC architecture instructions.

- The IDT WinChip 2 processor optimizes the performance of these types of basic x86 instructions while minimizing the hardware provided for other little-used x86 functions. The little-used instructions are primarily implemented in microcode with minimal hardware support.

- Memory performance is the limiting CPI performance factor. Due to the high ratio of internal clock speed versus the relatively limited PC processor-bus speed, off-chip memoryaccess performance is the primary factor in processor CPI performance (as opposed to internal instruction execution performance).

- The IDT WinChip 2 processor addresses this phenomenon by providing very large on-chip caches and TLBs that run at the high internal processor clock frequency. In addition, sophisticated TLB and cache management algorithms are included to further reduce bus activity.

- Optimize the design for the target user environment. The IDT WinChip 2 processor implements very specific and detailed design tradeoffs to provide high performance with low cost. Minimal hardware is provided for functions that are not heavily used or that are not critical to performance in the target environments (low-end desktop and mobile systems). These design optimizations are based on extensive and detailed analysis of the actual behavior of Windows operating systems and applications

- *Small is beautiful*. The IDT WinChip 2 processor is highly optimized for small physical size and few logic transistors. In addition to the obvious cost benefits, this small size provides secondary benefits of low power consumption and improved reliability.

#### 2.3 COMPONENT SUMMARY

#### 2.3.1 General Architecture

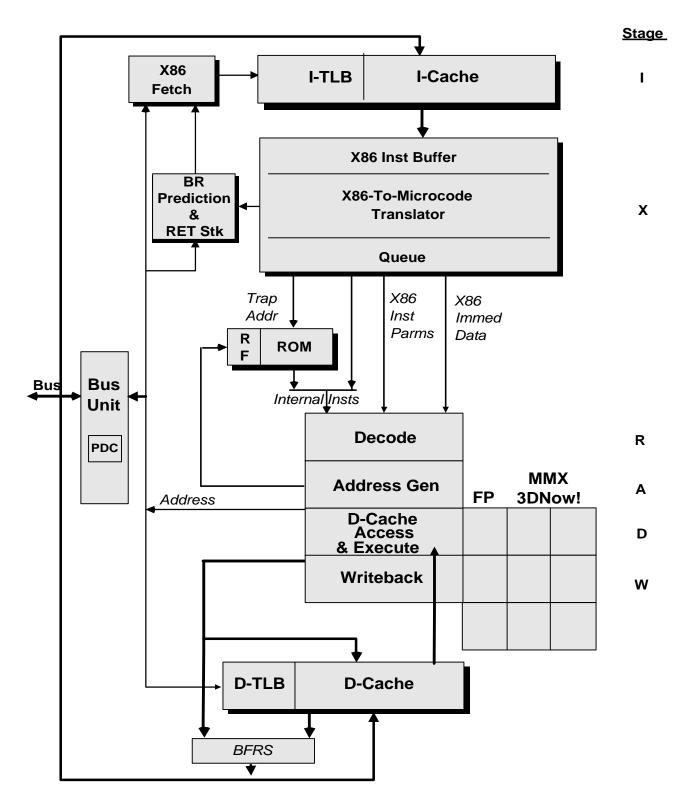

Figure 2-1 illustrates the basic components of the IDT WinChip 2 processor.

Fundamentally, the IDT WinChip 2 processor's internal design is a classic five-stage integer pipeline execution core with an additional instruction translation stage to translate x86 instructions coming from the fetch stage into the internal microinstruction format.

Fetching and translating x86 instructions is asynchronous to the internal execution pipeline. Integer and floating-point instructions are issued and executed one at a time in program order. MMX and 3DNow! instructions can be paired and issued and executed two at a time. All instructions are executed and retired in order. Cache and TLB misses stall the pipeline until the data is available for the requesting instruction.

In spite of this basic micro-architecture, the IDT WinChip 2 processor achieves high performance through several mechanisms:

- Good CPI on highly used instructions. The IDT WinChip 2 processor implements specific design features to reduce the number of cycles for heavily used instructions —including complex functions such as protect-mode segment-register loads and string instructions.

- Very large and fast on-chip caches and TLBs. These reduce the bus wait component of system performance, which can be equal to the processor-running component.

- Lots of fine-tuning and low-level optimizations. This includes such items as fast unaligned data access and fewer pipeline interlocks than the Pentium processor.

- Issue and execution pairing on instructions that benefit significantly from dual execution. This feature, like all others, is highly tuned for x86 application code.

Figure 2-1. IDT WinChip 2 Processor Data Flow

#### 2.3.2 I-Cache

The I-cache contains 32 KB organized as two-way set associative with 32-byte lines. An LRU replacement algorithm is used. The associated I-TLB contains 128 entries organized as 8-way set associative with a 7-bit pseudo-LRU replacement algorithm. This large cache and TLB has a one-clock access time and operates at the high clock frequencies of the IDT WinChip 2 processor.

The I-TLB utilizes an 8-entry unified page directory cache that significantly reduces the TLB miss penalty. In addition, the I-cache control logic includes several innovative features that minimize cache invalidates and unnecessary bus fetches.

As opposed to many other contemporary x86 processors, the data in the I-cache is exactly what came from the bus; that is, there are no hidden pre-decode bits. This facilitates the provision of large cache capacity in a small physical size.

The I-cache is dynamically turned off when not used to reduce power requirements.

#### 2.3.3 Translator Unit

The I-cache or bus unit delivers up to 16 bytes per clock to an x86 instruction buffer in the translator unit. The translator converts x86 instructions to internal instruction and data forms. Assuming that the instruction is in the x86 instruction buffer at the start of the cycle, the translator translates an entire x86 instruction in one clock. Instruction prefixes other than 0F require an additional translator cycle for each prefix. However, due to the asynchronous fetch and fookahead capability of the translator, these extra cycles for prefixes rarely result in a bubble in the execution pipeline.

The translator can also translate two MMX or two 3DNow! instructions each clock. The "pairing" rules for allowed combinations are similar to those for MMX on the Pentium processor and for 3DNow! on the AMD K6-2 processor.

The output of the translator is: (1) the internal micro-instruction stream to perform the x86 instruction function, (2) the immediate data fields from the x86 instruction, and (3) various x86 state information used to control execution (for example, operand size). The internal instruction stream for an x86 instruction can consist of micro-instructions directly generated by the translator, or micro-instructions from the on-chip ROM (microcode), or both. For performance-sensitive instructions, there is no delay due to access of micro-code from ROM.

The microcode ROM capacity is larger than most x86 microcode ROMs to allow more unimportant (relative to performance) functions to be performed in microcode (versus in hardware), to allow extensive self-test microcode, and to allow extensive built-in debugging aids (for processor design debug).

Instruction fetch and translator operation is made asynchronous from micro-instruction execution via a three-entry translated-instruction queue between the translator and the execution unit. Each entry contains up to three internal instructions for the corresponding x86 instruction. Most performance-critical x86 instructions can be represented by these three generated instructions. This queue allows the translator to fook-ahead"and continue translating x86 instructions even though the execution unit is stalled or is busy with a microcode sequence. The translator can also overlap generation of multiple internal instructions with translating prefixes on the subsequent instruction.

#### 2.3.4 Branch Prediction Unit

The IDT WinChip 2 has two advanced branch prediction mechanisms. These predict the branch target address and whether the branch is to be taken during the translator stage (X).

The branch target address for displacement branches is directly calculated while the branch instruction is the X- stage. The target address is fetched from the I-cache during the next cycle. This direct calculation of the target address eliminates the need for a large branch target buffer (BTB) such as found in the Pentium processor.

The prediction of the direction of conditional branches is performed by a state-of-the-art mechanism. A 12-bit global branch history is combined with the branch address to index a dynamically updated branch history table (BHT) with 4K entries. The BHT entry predicts whether the conditional branch direction will agree with a default direction guess by the translator. The translator guess is 70% accurate leading to an overall BHT prediction accuracy of over 90%.

In addition, x86 Return instructions are accurately predicted by an 8-entry Return-address stack.

#### 2.3.5 Execution Unit

Internal micro-instructions are executed in a tightly coupled four-stage pipeline that is very similar in structure to a basic RISC pipeline:

- **Decode stage (R)**: Micro-instructions are decoded, integer register files are accessed, resource dependencies evaluated, and so forth.

- **Addressing stage (A)**: Memory addresses are calculated and sent to the cache units. The IDT WinChip 2 processor is capable of calculating most x86 instruction address forms in one clock; a few forms containing two registers or a shifted index register require two clocks.

Branches (x86 and microcode) are also resolved in the A-stage. A fast forwarding mechanism allows the EFLAGS result of the instruction in front of a conditional branch (in the D-stage) to resolve conditional branches in the A-stage. Resolving branches in the A-stage means that a mispredicted, or not predicted, branch causes only a three clock stall.

■ **The Execute stage (D):** Integer ALU operations or load accesses to the D-cache are performed. All basic register-register ALU functions take one clock except multiply and divide. Load-ALU and Load-ALU-store sequences require only two clocks; the ALU operation and the store are combined.

During this stage the floating-point, MMX and 3DNow! execution units access their registers. These execution units hang off'the end of the main execution unit so that load-ALU operations for these units can be pipelined in one clock.

■ **Write-back stage (W)**: The results of operations are committed to the registers and store data is written to the D-cache or external write buffers.

Although the pipeline structure is similar to non-x86 processors, the micro-instructions and associated execution units are highly tuned to the x86 architecture. The micro-instructions closely resemble the corresponding x86 instructions. Examples of specialized hardware features supporting the x86 architecture are: hardware handling of the x86 condition codes, segment descriptor decode and manipulation instructions, hardware to automatically save the x86 floating-point environment, and so forth.

#### 2.3.6 D-Cache

The D-cache is very similar to the I-cache (except for set-associativity): 32 KB organized as four-way set associative with 32-byte lines. A 3-bit pseudo-LRU replacement algorithm is used. The associated D-TLB contains 128 entries organized as 8-way set associative with a 7-bit pseudo-LRU replacement algorithm. This large cache has a one-clock access time and is designed to operate at the high clock frequencies of the IDT WinChip 2 processor. The D-TLB shares the 8-entry unified page directory cache which reduces the TLB miss penalty. The D-cache is dynamically turned off when not used to reduce power requirements.

#### 2.3.7 X86 Fetch Unit

The x86 instruction fetch unit manages fetching instructions and I-TLB entries from the bus and delivering instructions from the I-cache. It implements a "smart" instruction prefetch mechanism to minimize wasted bus cycles.

#### 2.3.8 FP Unit

In addition to the integer execution unit, the IDT WinChip 2 processor has a separate 80-bit floating-point execution unit that can execute x86 floating-point instructions in parallel with integer instructions.

The floating-point unit is designed to maximize clock frequency and to minimize chip size while providing good floating-point performance for typical desktop use. The unit is fully pipelined and can start a floating-point add or multiply each clock.

The IDT WinChip 2 processor issues only one instruction per clock into the main instruction pipeline. However, once a hardwired floating point instruction (load, store, add, multiply, divide, square root, etc.) reaches the FP unit, following integer instructions can execute in parallel with the floating-point instruction. Certain little-used and complex floating point instructions (sin, atan, etc.) use the integer instruction pipeline and thus cannot be overlapped with integer execution.

The floating-point unit is dynamically turned off when not used to reduce power requirements.

#### 2.3.9 MMX Units

The IDT WinChip 2 processor contains two separate execution units for the MMX-compatible instructions. Up to two MMX instructions are issued and executed each clock (using the same pairing rules as for the Pentium processor).

Each MMX unit contains an adder and logic functions. One MMX unit has a multiplier-adder and the other has a shifter/packer. The multiplier(-adder) is fully pipelined and can start one MMX multiply[-add] instruction (which consists of up to four separate multiplies) every clock. The MMX units share hardware with the 3DNow! units such that in any clock only two MMX or 3DNow! instructions can be executed.

Architecturally, the MMX registers are the same as the floatingpoint registers. However, there are actually two different register files (one in the FP-unit and one in the MMX units) that are kept synchronized by hardware.

The MMX unit is dynamically turned off when not used to reduce power requirements.

#### 2.3.10 3DNow! Units

The IDT WinChip 2 processor contains two separate execution units for the new 3DNow! instructions. These instructions are compatible with the AMD K6-2 processor 3DNow! instructions and provide performance assists for graphics transformations via new SIMD single-precision floating-point capabilities. Up to two 3DNow! instructions are issued and executed each clock. Each instruction operates on two single precision floating-point numbers.

One 3DNow! unit has two single-precision floating-point multipliers. The other unit has two single-precision floating-point adders. Other functions such as conversions, reciprocal, and reciprocal square root are provided by the appropriate unit.

The multiplier and adder are fully pipelined and can start one 3DNow! multiply instruction (which consists of two separate multiplies) and one 3DNow! add instruction (which consists of two separate adds) every clock.

#### 2.3.11 Bus Unit

The IDT WinChip 2 processor bus unit provides an external bus interface compatible with the Pentium processor. In addition to the expected bus control functions, the bus unit implements a eight-entry page-directory cache to reduce the impact of TLB misses. Four 64-bit write buffers allow internal execution to proceed overlapped with waiting for external stores to complete.

The IDT WinChip 2 processor bus unit contains many special features designed to reduce bus traffic and cache disruption. Examples include store byte-combining function (optional), cache cast-out snarfing, "mart lock" management mechanisms, weak-read ordering (optional), and so forth. The optional features are controlled by memory range registers that allow different address-space regions to have different characteristics.

The IDT WinChip 2 supports bus speeds of 60, 66, 75 and 100 MHz. The 100 MHz bus is compatible with the AMD Super7 bus architecture. The initial version of the IDT WinChip 2 supports only integer ratios of the bus frequency as core frequencies. A subsequent version will support fractional ratios.

#### 3 PROGRAMMING INTERFACE

#### 3.1 GENERAL

In general, the IDT WinChip 2 processor is compatible with both the bus and software-visible architecture of the Intel Pentium processor with MMX technology. That is, a program that executes on a Pentium processor should generally execute on an IDT WinChip 2 processor and produce the same results (with the exceptions as noted in this datasheet).

The IDT WinChip 2 processor's Pentium-compatible functions include:

- All basic X86 instructions, registers, and functions

- All floating-point (numeric processor) instructions, registers and functions

- All new Pentium processor instructions and registers (CMPXCHG8B, RDMSR, WRMSR, RDTSC, CPUID, RSM, MOV CR4)

- All basic operating modes: real mode, protect mode, virtual-8086 mode

- System Management Interrupt (SMI) and the associated System Management Mode (SMM)

- All interrupt and exception functions

- All debug functions (including the new I/O breakpoint function)

- All input/output functions

- All tasking functions (TSS, task switch, etc.)

- Processor initialization behavior

The IDT WinChip 2 processor, in addition to the MMX instructions, also includes instructions to boost the performance of 3D graphics compatible with the AMD-3D Technology.

However, there are some differences between the IDT WinChip 2 processor and the Pentium processor. These differences fall into four groups:

- Additional IDT WinChip 2 processor functions. Examples are memory range registers that allow different attributes for each range. These additional functions are provided through Machine Specific Registers such that compatibility is not affected.

- **Implementation-specific differences**. Examples are cache and TLB testing features, and performance monitoring features that expose the internal implementation features. These types of functions are incompatible among *all* different x86 implementations.including the Intel486, the Pentium, and the Pentium Pro processors.

- Omitted functions. Some Pentium processor functions are not provided on the IDT WinChip 2 processor because they arent used or arent needed in the targeted PC systems. Examples are some specific bus functions such as functional redundancy checking and performance monitoring.

- These types of differences are similar to those among various versions of the Pentium processor (for example, the mobile Pentium processor also omits the same bus functions as omitted by the IDT WinChip 2 processor), and among the AMD-K6 and Cyrix 6x86MX processors.

- WinChip 2 processor functions are different from the Pentium because the results are (1) documented in the Intel documentation as *undefined*, and (2) known to be different for different x86 implementations (in particular, different among the Intel i486, the Pentium, and the Pentium Pro processors). That is, compatibility with the Pentium processor for these functions is clearly not needed for software compatibility (or they wouldn't be different across different implementations). Where the Pentium and Pentium Pro processor results differ, the IDT WinChip 2 processor often provides the Pentium Pro result.

This chapter summarizes the first three types of differences: additional functions, implementation-specific functions, and omitted functions. *Appendix A* contains more details on machine-specific functions. *Appendix B* contains details on low-level differences.

In some areas, we also include comparative information about the Pentium Pro, AMD-K6, and Cyrix 6x86MX processors. This information is taken from the data sheets of these products and has not been verified by Centaur Technology. Our Pentium processor information, however, is based on detailed testing.

#### 3.2 ADDITIONAL FUNCTIONS

The IDT WinChip 2 processor provides some memory range management functions. These are similar in concept, but different in specifics, to memory range registers in the Pentium Pro, AMD-K6, and Cyrix 6x86MX processors (all of which are different from each other). These functions are provided via Machine Specific Registers. Appendix A provides specifics on the IDT WinChip 2 Machine Specific Registers. Note that there are differences in the specifics of memory range management between the IDT WinChip 2 and it's predecessor, the IDT WinChip C6. The IDT WinChip 2 processor supports extended CPUID functions, as defined by AMD. The IDT WinChip 2 3D processor also includes instructions to boost the performance of 3D graphics compatible with the AMD-3D Technology

#### 3.3 MACHINE-SPECIFIC FUNCTIONS

#### 3.3.1 General

All x86 processor implementations provide a variety of *machine-specific functions*. Examples are cache and TLB testing features, and performance monitoring features that expose the internal implementation features. These types of functions are different and incompatible among all different x86 implementations—including the Intel i486, the Pentium, and the Pentium Pro processors, and between these processors and competitive processors from Cyrix and AMD. The Intel documentation clearly identifies these types of functions as machine-specific and warns of possible changes in new implementations.

This section describes the IDT WinChip 2 processor machine-specific functions that are most likely used by software and compares them to related processors where applicable. *Appendix A* describes the IDT WinChip 2 processor machine-specific registers (*MSRs*).

This section covers those features of Pentium-compatible processors that are used to commonly identify and control processor features. All Pentium-compatible processors have the same mechanisms, but the bit-specific data values often differ.

#### 3.3.2 Standard CPUID Instruction Functions

The CPUID instruction is available on all contemporary x86 processors. The CPUID instruction has two standard functions requested via the EAX register. The first function returns a vendor identification string in registers EBX, ECX and EDX. The second CPUID function returns an assortment of bits in EAX and EDX that identify the chip version and describe the specific features available.

The EAX:EBX:ECX:EDX return values of the CPUID instruction executed with EAX == 0 are:

Table 3-1

| REGISTER[BITS] –<br>MEANING                                | WINCHIP 2          | P54                | P55                | K6                 | М2                 |

|------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| EAX<br>(highest EAX input<br>value understood<br>by CPUID) | 1                  | 1                  | 1                  | 1                  | 1                  |

| EBX:EDX:ECX<br>(vendor ID string)                          | "Centaur<br>Hauls" | "Genuine<br>Intel" | "Genuine<br>Intel" | "Authentic<br>AMD" | "Cyrix<br>Instead" |

The EAX return values of the CPUID instruction executed with EAX == 1 are:

Table 3-2

| EAX BITS - MEANING | WINCHIP 2                                                      | P54 | P55 | <b>K</b> 6 | M2 |

|--------------------|----------------------------------------------------------------|-----|-----|------------|----|

| 3:0 - Stepping ID  |                                                                |     |     |            |    |

| 7:4 - Model ID     | Same as the return value in EDX after Reset (see next section) |     |     |            |    |

| 11:8 - Family ID   |                                                                |     |     |            |    |

| 13:12 - Type ID    |                                                                |     |     |            |    |

The EDX return values of the CPUID instruction with EAX == 1 are:

Table 3-3

| EAX BITS - MEANING                       | WINCHIP 2 | P54 | P55 | K6 | М2 | NOTES |

|------------------------------------------|-----------|-----|-----|----|----|-------|

| 0 - FP present                           | 1         | 1   | 1   | 1  | 1  |       |

| 1 - VM86 Extensions (VME)                | 0         | 1   | 1   | 1  | 0  | 1     |

| 2 - Debugging Extensions                 | 1         | 1   | 1   | 1  | 1  |       |

| 3 - Page Size Extensions (4MB)           | 0         | 1   | 1   | 1  | 0  | 1     |

| 4 - Time Stamp Counter (TSC) supported   | 1         | 1   | 1   | 1  | 1  | 2     |

| 5 - Model Specific Registers<br>present  | 1         | 1   | 1   | 1  | 1  | 3     |

| 6 - PAE supported (P6 Function)          | 0         | 0   | 0   | 0  | 0  | 4     |

| 7 - Machine Check Exception              | 1/0       | 1   | 1   | 1  | 0  | 5     |

| 8 - CMPXCHG8B instruction                | 0/1       | 1   | 1   | 1  | 1  | 6     |

| 9 - APIC supported                       | 0         | 1   | 1   | 0  | 0  | 7     |

| 10:11 -Reserved                          |           |     |     |    |    |       |

| 12- Memory Range Registers               | 0         | 0   | 0   | 0  | 0  | 8     |

| 13 - PTE Global Bit supported            | 0         | 0   | 0   | 0  | 1  | 4     |

| 14- Machine Check Architecture supported | 0         | 0   | 0   | 0  | 0  | 4     |

| 15- Conditional Move supported           | 0         | 0   | 0   | 0  | 1  | 4     |

| 16:22 - Reserved                         |           |     |     |    |    |       |

| 23 - MMX supported                       | 1/0       | 0   | 1   | 1  | 1  | 9     |

| 24:31 - Reserved                         |           |     |     |    |    |       |

#### **Notes On CPUID Feature Flags**

General: an x/y entry means that the default setting of this bit is x but the bit (and the underlying function) can be set to y using the FCR MSR.

- 1. These 'Appendix H''functions are not provided on the IDT WinChip 2 processor since they are not used by the target operating systems. They are also not provided on the Cyrix 6x86MX processor.

- 2. The IDT WinChip 2 processor implementation varies slightly from that of the Pentium processor in a way that should have no practical impact.

- 3. Every system has different MSRsaddresses and contents.

- 4. This is a function introduced with the Pentium Pro processor and is generally not provided on Pentium-compatible processors.

- 5. The Machine Check exception is defined by Intel documentation as machine-specific. The IDT WinChip 2 processor's Machine Check has slightly different specifics than the Pentium processor's Machine Check function. The Machine Check support can be enabled or disabled by a bit in the FCR MSR. The CPUID bit reports the current setting of this enable control.

- 6. The Pentium processor-compatible CMPXCHG8B instruction is provided and always enabled. However, the default for the corresponding CPUID function bit is 0 (due to a bug found in Windows NT). This default can be changed via a bit in the FCR MSR.

- 7. This is an Intel-specific multiprocessing function. None of the other Pentium-compatible processors provide this function since it has no utility in the target system environment.

- 8. The IDT WinChip 2 and Cyrix 6x86MX processors have memory range registers, but the specifics are not compatible with the P6 MRRs. The Pentium processor has no memory range registers.

9. The IDT WinChip 2 processor's MMX-technology compatible instruction support can be enabled or disabled by a bit in the FCR. The CPUID bit reports the current setting of this enable control.

#### 3.3.3 Extended CPUID Instruction Functions

The IDT WinChip 2 processor supports extended CPUID functions similar to those provided by the AMD-K6 and Cyrix GXm. These functions provide additional information about the IDT WinChip 2.

Extended CPUID functions are requested by executing CPUID with EAX set to any value in the range 0x80000000 through 0x80000005.

The IDT WinChip 2 CPUID instruction aliases EAX values in the range 0xC0000000 through 0xC0000005 to the extended functions in the range 0x80000000 through 0x80000005 (there is no guarantee that this will be true in future processors. The following table summarizes the extended CPUID functions.

| EAX           | TITLE                     | ОИТРИТ                                 |  |  |  |

|---------------|---------------------------|----------------------------------------|--|--|--|

| 80000000      | Largest Extended Function | EAX=8000005                            |  |  |  |

|               | Input Value               | EBX,ECX,EDX=Reserved                   |  |  |  |

| 80000001      | Processor Signature and   | EAX=Processor Signature                |  |  |  |

| Feature Flags |                           | EBX,ECX=Reserved                       |  |  |  |

|               |                           | EDX=Extended Feature Flags             |  |  |  |

| 80000002      | Processor Name String     | EAX,EBX,ECX,EDX                        |  |  |  |

| 80000003      | Processor Name String     | EAX,EBX,ECX,EDX                        |  |  |  |

| 8000004       | Processor Name String     | EAX,EBX,ECX,EDX                        |  |  |  |

| 80000005      | TLB and Cache Information | EAX = Reserved                         |  |  |  |

|               |                           | EBX = TLB Information                  |  |  |  |

|               |                           | ECX = L1 Data Cache Information        |  |  |  |

|               |                           | EDX = L1 Instruction Cache Information |  |  |  |

# Largest Extended Function Input Value (EAX==0x80000000)

Returns 0x80000005 in EAX, the largest extended function input value.

### **Processor Signature and Feature Flags (EAX==0x80000001)**

Returns processor version information in EAX, this value is identical to the value of EDX after RESET.

Returns feature flags in EDX, this value is identical to the value in EDX after CPUID standard function 1, with the exception of bit 31:

EDX[31]=0 3DNow! instructions not supported.

EDX[31]=1 3DNow! instructions supported.

Note that if FCR[20]=0 then AMD-3D instructions are not supported and EDX[31] will be 0.

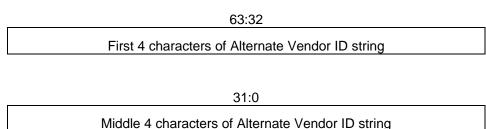

#### Processor Name String (EAX==0x80000002-0x80000004)

Returns the name of the processor, suitable for BIOS to display on the screen (ASCII). The string can be up to 48 characters in length. If the string is shorter, the rightmost characters are padded with zero. The leftmost characters go in EAX, then EBX, ECX, and EDX. The leftmost character goes in least significant byte (little endian).

For example, the string IDT WinChip 2-3D would be returned by extended function EAX=0x80000002 as follows:

EAX = 0x20544449

EBX = 0x436E6957

ECX = 0x20706968

EDX = 0x44332D32

Since the string is exactly 16 bytes, the extended functions EAX=0x80000003 and EAX=0x80000004 return zero in EAX, EBX, ECX, and EDX.

Note that if FCR[20] is 0' then AMD-3D instructions are not supported and extended function EAX=0x80000002 returns *IDT WinChip 2*".

# Cache Information (EAX == 0x80000005)

Returns information about the implementation of the TLBs and caches.

| REGISTER   | DESCRIPTION                      | VALUE |

|------------|----------------------------------|-------|

| EAX        | Reserved                         |       |

| EBX        | TLB Information                  |       |

| EBX[31:24] | D-TLB associativity              | 8     |

| EBX[23:16] | D-TLB # entries                  | 128   |

| EBX[15: 8] | I-TLB associativity              | 8     |

| EBX[ 7: 0] | I-TLB # entries                  | 128   |

| ECX        | L1 Data Cache Information        |       |

| ECX[31:24] | Size (Kbytes)                    | 32    |

| ECX[23:16] | Associativity                    | 4     |

| ECX[15: 8] | Lines per Tag                    | 1     |

| ECX[ 7: 0] | Line Size (bytes)                | 32    |

| EDX        | L1 Instruction Cache Information |       |

| EDX[31:24] | Size (Kbytes)                    | 32    |

| EDX[23:16] | Associativity                    | 2     |

| EDX[15: 8] | Lines per Tag                    | 1     |

| EDX[ 7: 0] | Line Size (bytes)                | 32    |

#### 3.3.4 Processor Identification

The IDT WinChip 2 processor provides several machine-specific features. Some of these features are compatible with those provided by P55 and are identified by the standard CPUID function EAX=1.

Other machine-specific features described in this datasheet have no P55 equivalent. These features are controlled by IDT WinChip 2 MSRs. Some of these features are not backward-compatible with the predecessor IDT WinChip C6.

System software must not assume that all future processors in the IDT WinChip family will implement all of the same machine-specific features or even that these features will be implemented in a backward-compatible manner. In order to determine if the processor supports particular machine-specific features, system software should follow the following procedure. Identify the processor as a member of the IDT WinChip family by checking for a Vendor Identification String of CentaurHauls" using CPUID with EAX=0. Once this has been verified, system software must determine the processor version in order to properly configure the machine-specific registers. In particular some of the control fields of the memory configuration registers were redefined for the IDT WinChip 2.

There are two ways of distinguishing between the IDT WinChip 2 and its predecessor, the IDT WinChip C6.

If system software is only concerned with programming the memory configuration registers, then it can read the MCR\_CTRL register and inspect the Trait Mode Key field (MCR\_CTRL[19:17]). In the IDT WinChip 2 and later versions of the processor family the Trait Mode Key must be written to the Trait Mode control field (MCR\_CTRL[8:6]) in order to activate the memory configuration registers.

In general system software can determine the processor version by comparing the Family and Model Identification fields returned by the CPUID standard function EAX=1.

If the processor version is not recognized then system software must not attempt to activate any machine-specific feature.

The following table indicates how to interpret the results of both methods.

| FAMILY | MODEL | TRAIT MODE KEY<br>MCR_CTRL[19:17] | PROCESSOR VERSION                          |

|--------|-------|-----------------------------------|--------------------------------------------|

| 5      | 4     | 0                                 | IDT WinChip C6, use appropriate datasheet. |

| 5      | 8     | 1                                 | IDT WinChip 2, use this datasheet          |

#### 3.3.5 EDX Value After Reset.

As for other x86 processors, after reset the EDX register holds a component identification number as follows:

|     | 31:14    | 13:12   | 11:8      | 7:4      | 3:0         |

|-----|----------|---------|-----------|----------|-------------|

| EDX | Reserved | Type ID | Family ID | Model ID | Stepping ID |

|     | 18       | 2       | 4         | 4        | 4           |

The specific values for the various *IDT WinChip C6* processor types are:

|--|

IDT WINCHIP 2™ PROCESSOR DATA SHEET

| WinChip C6 | 0 | 5 | 4 | Varies |

|------------|---|---|---|--------|

| WinChip 2  | 0 | 5 | 8 | Varies |

For comparison, following are the values for other X86 processors:

| PROCESSOR    | TYPE ID | FAMILY ID | MODEL ID | STEPPING ID |

|--------------|---------|-----------|----------|-------------|

| P54C         | 0       | 5         | 2        | Varies      |

| P55          | 0       | 5         | 4        | Varies      |

| Cyrix 6x86MX | 0       | 6         | 0        | Varies      |

| AMD-K6       | 0       | 6         | 6-9      | Varies      |

## 3.3.6 CR4

Control register 4 (CR4) is a new feature of the Pentium processor that controls some of its advanced features. The *IDT WinChip 2* processor provides a CR4 with the following specifics:

| CR4 BITS - MEANING                            | WIN<br>CHIP<br>2 | P54 | P55 | <i>K</i> 6 | М2  | NOTES |

|-----------------------------------------------|------------------|-----|-----|------------|-----|-------|

| 0: VME: Enables VME<br>feature                | 0                | 0/1 | 0/1 | 0/1        | 0   | 1     |

| 1: PVI: Enables PVI feature                   | 0                | 0/1 | 0/1 | 0/1        | 0   | 1     |

| 2: TSD: Makes RDTSC inst privileged           | 0/1              | 0/1 | 0/1 | 0/1        | 0/1 |       |

| 3: DE: Enables I/O<br>breakpoints             | 0/1              | 0/1 | 0/1 | 0/1        | 0/1 |       |

| 4: PSE: Enables 4-MB pages                    | 0                | 0/1 | 0/1 | 0/1        | 0   | 1     |

| 5: PAE: Enables addr<br>extensions            | r                | r   | r   | r          | r   | 2     |

| 6: MCE: Enables<br>machine check<br>exception | 0/1              | 0/1 | 0/1 | 0/1        | 0   | 3     |

| 7: PGE: Enables global page feature           | r                | r   | r   | r          | 0/1 | 2     |

| 8: PCE: Enables RDPMC<br>for all levels       | 0/1              | r   | 0/1 | r          | 0/1 |       |

| 31:9 - reserved                               | r                | r   | r   | r          | r   |       |

#### **Notes On CR4**

General: a 0/1"means that the default setting of this bit is 0 but the bit can be set to (1). A 0"means that the bit is always 0; it cannot be set. An fi"means that this bit is reserved. It appears as a 0 when read, and a GP exception is signaled if an attempt is made to write a 1 to this bit.

- 1. The IDT WinChip 2 processor does not provide this 'Appendix H' function and this CR4 bit cannot be set. However, no GP exception occurs if an attempt is made to set this bit. The Cyrix 6x86MX processor also does not provide this function.

- 2. This is a Pentium-Pro processor function that is typically not provided on P55-compatible processor.

- 3. The IDT WinChip *2* processor Machine Check has slightly different specifics than the P54C Machine Check function

## 3.3.7 Machine-Specific Registers

The IDT WinChip 2 processor implements the Pentium family concept of Machine Specific Registers (MSRs). RDMSR and WRMSR instructions are provided and the CPUID instruction identifies that the IDT WinChip 2 processor supports MSRs. However, the IDT WinChip 2 processor MSRs are different from the Pentium and Pentium Pro processors (which are different from each other, and from the Cyrix 6x86MX and AMD-K6 processors).

In general, the MSRs have no usefulness to application or operating system software and are not used. (This is to be expected since the MSRs are different on each processor). *Appendix A* contains a detailed description of the *IDT WinChip 2* processor's MSRs.

#### 3.4 OMITTED FUNCTIONS

This section summarizes those functions that are included in some Pentium processor versions, but are not in the IDT WinChip 2 processor.

# 3.4.1 Pentium Appendix H Enhancements

The infamous *Appendix H* functions are those Pentium functions that are documented in Appendix H (Advanced Functions) of Volume 3 of the Pentium Processor Family Developer's Manual.

Unfortunately, Appendix H is only available to those with the appropriate non-disclosure agreements in place. However, most of these functions are now publicly documented in the Pentium Pro processor documentation.

The Appendix H features are identified as optional in future are specifically identified as being supported or not by the CPUID instruction.

Due to the limited utility of these advanced functions (they are complex operating system functions), there are few programs that utilize these features. In particular, these functions are either not used at all, or are conditionally used if present, by Microsoft desktop operating systems.

The IDT WinChip 2 processor does not provide the following Appendix H functions.

## Virtual Memory Enhancements (4-MB Pages).

These Pentium processor enhancements provide the ability to optionally define 4-MB virtual memory pages in addition to the usual 4-KB page size. A bit in the feature identification return from the CPUID instruction indicates whether this feature is present or not. This enhancement is not provided on the IDT WinChip 2 processor since it is not used by the target operating systems: Windows 95 and Windows 98. Note that this function is also not provided on the Cyrix 6x86MX processor.

# Virtual-8086 Mode Enhancements (VME)

These Pentium processor enhancements provide potential performance improvements to mode-switching operations while operating in VM86 mode. A bit in the feature identification return from the CPUID instruction indicates whether this feature is present or not. This enhancement is not provided on the IDT WinChip 2 processor since it is not used by the target Microsoft operating systems. Note that this function is also not provided on the Cyrix 6x86MX processor.

### 3.4.2 Other Functions

The IDT WinChip 2 processor also omits the software interface to the Intel-proprietary symmetric multiprocessing support: *APIC.* This bus function is omitted since the target market for the IDT WinChip 2 processor is portables and typical desktop systems (which do not support APIC multiprocessing).

IDT WINCHIP 2 ™ PROCESSOR DATA SHEET

A bit in the feature identification return from the CPUID instruction indicates whether this feature is present or not. This enhancement is not provided on the IDT WinChip 2 processor (as it is not on the mobile Pentium processor and on the AMD-K6 and Cyrix 6x86MX processors).

## 4 HARDWARE INTERFACE

### 4.1 BUS INTERFACE

The IDT WinChip 2 processor bus interface is compatible with the Pentium processor and the Pentium processor with MMX technology. This behavior is specified in *Pentium Processor* Family Developer's Manual.

The majority of the pins within the bus interface are involved with the physical memory and I/O interface. These pins and this interface perform the same functions as in the Pentium processor. The remaining pins are power and ground pins, test and debug support pins and various ancillary control functions. Most of these pins are identical to the Pentium processor. Others are associated with functions that behave slightly differently from the Pentium processor on the IDT WinChip 2 processor. Still others behave differently among the various versions of the Pentium processor, and thus require clarification on the IDT WinChip 2 processor. Lastly there are several Pentium processor functions which are completely omitted on the IDT WinChip 2.

### 4.1.1 Differences

The areas where the IDT WinChip 2 processor differs from the Pentium processor are not anticipated to cause operational compatibility issues. These differences are:

- Bus Frequency Control

- Machine Check Exceptions on BUSCHK# and PEN#

- Drive Strengths

- Probe Mode / JTAG / TAP Port (see *Test and Debug Section*)

## **Bus Frequency Control**

Like other Socket 7 processors, the IDT WinChip 2 processor derives its internal clock frequency by multiplying the external bus clock based on the levels of the BF pins at the deassertion of RESET. Unlike other Socket 7 processors, the IDT WinChip 2 does not support fractional bus frequency multiples. Otherwise the supported integer bus frequency multiples are compatible with the multiples supported by the AMD K6. Supported clock ratios are shown in Table 4-1. The IDT WinChip 2 pulls up all three of the BF pins so that the default is 4x multiplier.

K6 CLOCK BF2 BF1 BF0 **IDT WINCHIP 2 CLOCK RATIO RATIO** 1 0 0 5/2xreserved 1 0 1 3x 3x 1 1 0 2x 2x 1 1 reserved 7/2x 0 0 0 reserved 9/2x0 0 1 5x 5x

Table 4-1. Bus Frequency Ratios

1

1

## Machine Check Exceptions on BUSCHK# & PEN#

0

1

As in the Pentium processor, the BUSCHK# interrupt causes a Machine Check exception or is ignored based on CR4.MCE. The difference is that the semantics of Machine Check exception are slightly different on a IDT WinChip 2 processor from a Pentium processor (a IDT WinChip 2 processor doesn't save and report the bus address and cycle data). See section 4.4 for further description of Machine Check.

4x

reserved

4x

11/2x

# **Drive Strength**

0

0

Desktop Pentium processors have three driver strengths that can be selected at Reset for certain pins (for example ADS#). The driver strength is selected by the BRDYC# and BUSCHK# pins when sampled at RESET deassertion

The IDT WinChip 2 processor has only two driver strengths:

Table 4-2. Drive Strengths

| BUSCHK# | BRDYC# | IDT WINCHIP 2 DRIVER | P54C DRIVER |

|---------|--------|----------------------|-------------|

| 0       | 0      | Medium               | Strong      |

| 0       | 1      | Medium               | Medium      |

| 1       | 0      | Typical              | Typical     |

| 1       | 1      | Typical              | Typical     |

Only ADS#, A[20:3], HITM# and W/R# are configurable. All other drivers are typical strength. The AC characteristics of both drive strengths are described in Chapter 5, Electrical Specifications.

## 4.1.2 Clarifications

## **Power Supply Voltage**

The IDT WinChip 2 processor operates with a unified power plane. Depending on the version, the processor requires either 3.3 Volts or 3.52 Volts at its VCC inputs.

The IDT WinChip 2 package is compatible with Socket 7, in that the VCC2DET# pin is internally no-connected. Flexible socket 7 motherboards can use the fact that VCC2DET# is not internally connected to force the motherboard core and pad regulators to produce the same voltage.

#### **5V Tolerance**

Like the P55, the IDT WinChip 2 processor's CLK input is not 5 Volt tolerant. It should be driven by a 3.3 Volt device.

### 4.1.3 Omissions

# **Advanced Peripheral Interrupt Controller (APIC)**

The APIC is not supported by the IDT WinChip 2. The APIC pins (PICCLK, PICD0, and PICD1) are classified as reserved, and should not be connected on the motherboard.

(The APIC is also not supported in the mobile Pentium processor, the Cyrix 6x86MX and AMD-K6 processors.)

#### **Dual Processor Interface**