**AP-483**

# APPLICATION NOTE

# Application Examples Using the 8XC196MC/MD Microcontroller

MASANORI DOI GARY HARRIS EMBEDDED CONTROL

August 1993

Order Number: 272282-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

\*Third-party brands and names are the property of their respective owners.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

# **Table of Contents**

| CONTENTS                                                 | PAGE |

|----------------------------------------------------------|------|

| 1.0 UNDERSTANDING THE 8XC196MC/MD INTERRUPTS AND PTS     | 2    |

| 1.1 Interrupt Processing                                 | 2    |

| 1.1.1 Interrupt Controller                               | 2    |

| 1.1.2 Peripheral Transaction Server (PTS)                | 2    |

| 1.2 Interrupt Latency                                    | 4    |

| 1.2.1 Calculating Latency                                | 5    |

| 1.2.2 Standard Interrupt Latency                         | 5    |

| 1.2.3 PTS Interrupt Latency                              | 5    |

| 1.3 Interrupt Priorities                                 | 6    |

| 1.3.1 Modifying Interrupt Priorities                     | 7    |

| 1.4 End-of-PTS Interrupts                                | 7    |

| 1.5 Special Interrupts                                   |      |

| 1.5.1 Unimplemented Opcode                               |      |

| 1.5.2 Software Trap                                      | 8    |

| 1.5.3 NMI                                                |      |

| 1.6 EPA Interrupts                                       |      |

| 1.6.1 Using the PTS to Service the EPA                   |      |

| 1.7 Programming the Interrupts                           |      |

| 1.7.1 Selecting Either PTS or Standard Interrupt Service |      |

| 1.7.2 Enabling PTS Interrupts                            |      |

| 1.7.3 Enabling Standard Interrupts                       |      |

| 1.7.4 Interrupt Mask Registers                           |      |

| 1.7.5 Interrupt Pending Registers                        |      |

| 1.7.6 The Peripheral Interrupt (PI)                      |      |

| 1.7.6.1 WG Interrupt                                     |      |

| 1.7.6.2 COMP5 Interrupt                                  |      |

| 1.7.7 The EXTINT Interrupt                               |      |

| 1.7.8 The TOVF Interrupt                                 |      |

| 1.8 Configuring the PTS                                  |      |

| 1.8.1 Setting Up PTS Control Blocks                      |      |

| 1.8.1.1 PTSCOUNT Register                                |      |

| 1.8.1.2 PTSCON Register                                  |      |

| 1.8.2 Single Transfer Mode                               |      |

| 1.8.2.1 Single Transfer Mode Example                     |      |

| 1.8.3 Block Transfer Mode                                |      |

| 1.8.3.1 Block Transfer Mode Example                      | 17   |

| CONTENTS                                                  | PAGE |

|-----------------------------------------------------------|------|

| 1.8.4 A/D Scan Mode                                       | 17   |

| 1.8.4.1 PTS Cycles in A/D Scan Mode                       | 18   |

| 1.8.4.2 A/D Scan Mode Example 1                           | 18   |

| 1.8.4.3 A/D Scan Mode Example 2                           | 19   |

| 1.8.5 Serial I/O Modes                                    | 19   |

| 1.8.5.1 PTSCOUNT Register                                 |      |

| 1.8.5.2 PTSCON Register                                   | 20   |

| 1.8.5.3 EPAREG Register                                   | 21   |

| 1.8.5.4 BAUD Register                                     |      |

| 1.8.5.5 PTSVEC1 Register                                  | 21   |

| 1.8.5.6 PORTREG Register                                  |      |

| 1.8.5.7 PORTMASK Register                                 | 22   |

| 1.8.5.8 PTSCON1 Register                                  |      |

| 1.8.5.9 DATA Register                                     |      |

| 1.8.5.10 SAMPTIME Register                                |      |

| 1.8.6 PTS Asynchronous SIO Receive Mode                   | 23   |

| 1.8.6.1 PTS Asynchronous SIO Transmit Mode                |      |

| 1.8.6.2 PTS Synchronous SIO Receive Mode                  |      |

| 1.8.7 PTS Synchronous SIO Transmit Mode                   | 25   |

| 2.0 SYNCHRONOUS SERIAL DATA TRANSMISSION PROGRAM EXAMPLE  | 26   |

| 2.1 Introduction                                          | 26   |

| 2.1.1 End-of-PTS Interrupt                                | 26   |

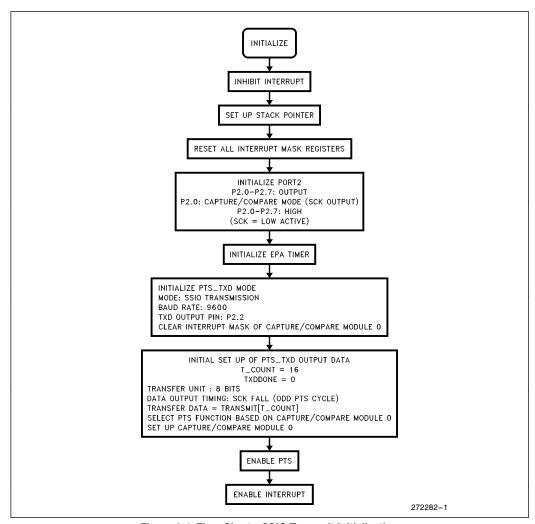

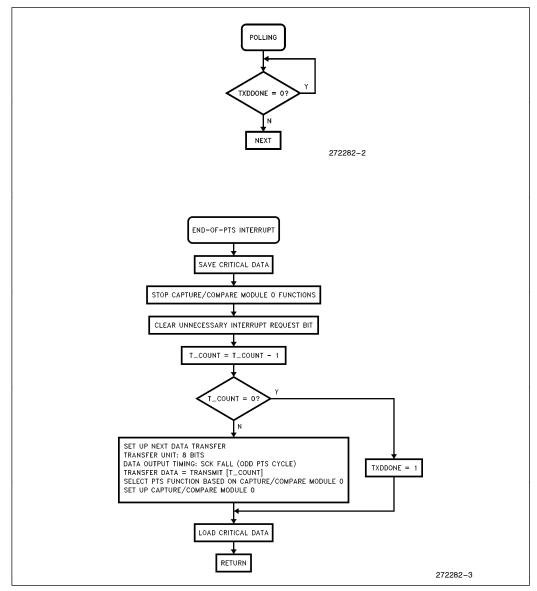

| 2.2 Detailed Program Description                          | 26   |

| 2.2.1 Constant Declarations (Lines 1-46)                  |      |

| 2.2.2 Interrupt Vectors and CCB (Lines 47–66)             | 26   |

| 2.2.3 Main Program (Lines 67–135)                         | 26   |

| 2.2.4 End-of-PTS Interrupt Routine                        | 27   |

| 2.3 Top 5 Issues of Using the PTS/SSIO Transmit Mode      |      |

| 2.4 Program Example                                       | 28   |

| 3.0 SYNCHRONOUS SERIAL DATA RECEPTION PROGRAM EXAMPLE     | 33   |

| 3.1 Introduction                                          | 33   |

| 3.1.1 End-of-PTS Interrupt                                | 34   |

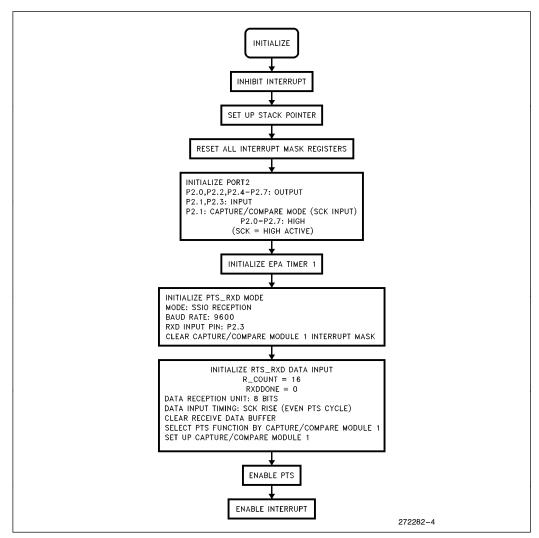

| 3.2 Detailed Program Description                          | 34   |

| 3.2.1 Constant Declarations (Lines 1–42)                  | 34   |

| 3.2.2 Interrupt Vectors and CCB (Lines 43–66)             | 34   |

| 3.2.3 Main Program (Lines 67–135)                         | 34   |

| 3.2.4 End-of-PTS Interrupt Routine                        | 35   |

| 3.3 Top 5 Issues of Using the PTS/SSIO Receive Mode       | 35   |

| 3.4 Program Example                                       | 36   |

| 4.0 ASYNCHRONOUS SERIAL DATA TRANSMISSION PROGRAM EXAMPLE | 41   |

| 4.1 Introduction                                          | 41   |

| CONTENTS                                                           | PAGE |

|--------------------------------------------------------------------|------|

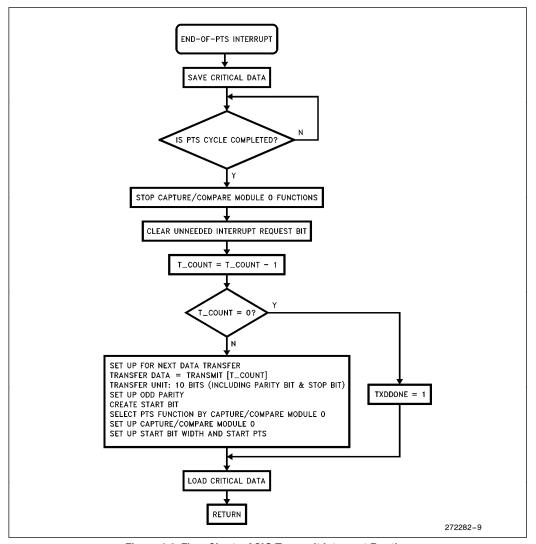

| 4.1.1 End-of-PTS Interrupt                                         | 41   |

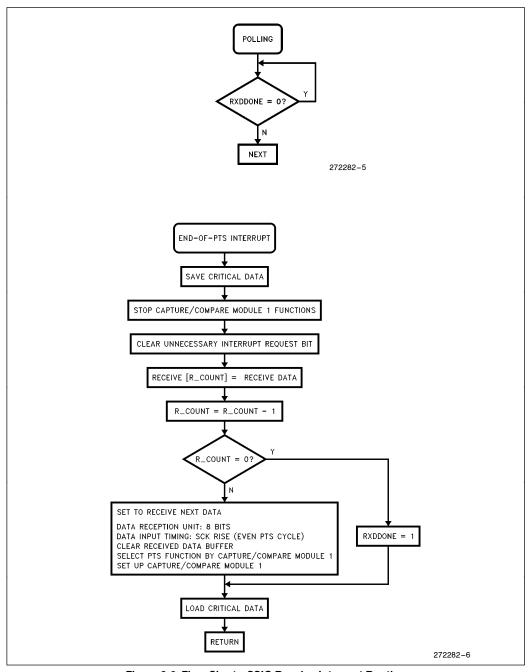

| 4.2 Detailed Program Description                                   | 41   |

| 4.2.1 Constant Declarations (Lines 1-42)                           | 41   |

| 4.2.2 Interrupt Vectors and CCB (Lines 43-66)                      | 41   |

| 4.2.3 Main Program (Lines 67–135)                                  | 42   |

| 4.2.4 End-of-PTS Interrupt Routine                                 | 42   |

| 4.3 Top 5 Issues of Using the PTS/SIO Transmit Mode                | 43   |

| 4.4 Program Example                                                | 44   |

| 5.0 ASYNCHRONOUS SERIAL DATA RECEPTION PROGRAM SAMPLE              | 49   |

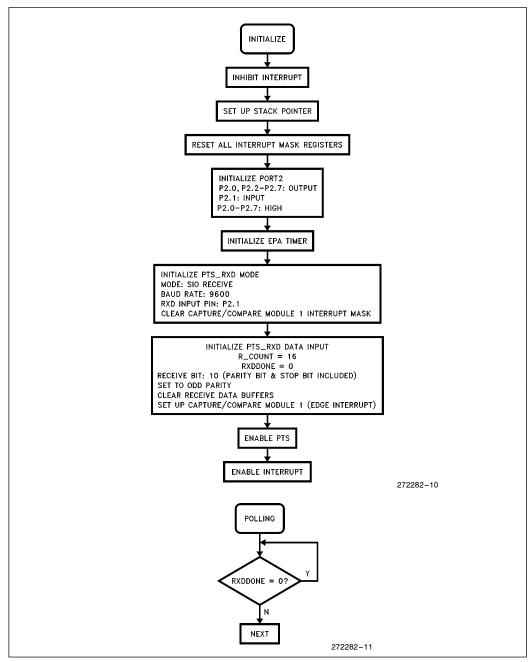

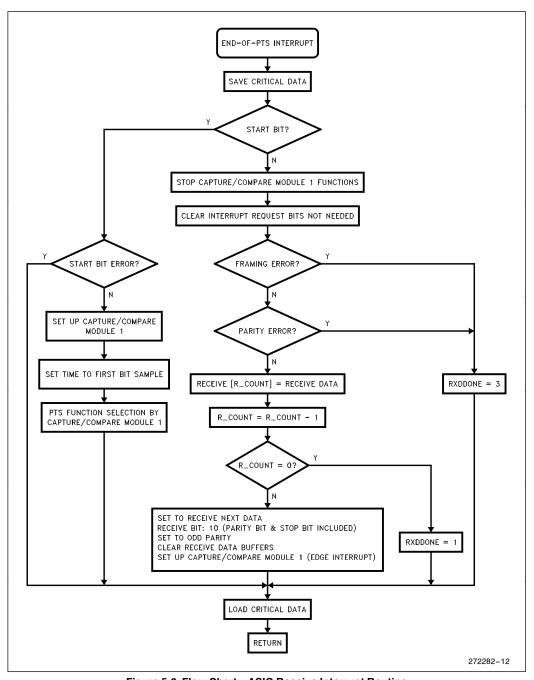

| 5.1 Introduction                                                   | 49   |

| 5.1.1 End-of-PTS Interrupt                                         |      |

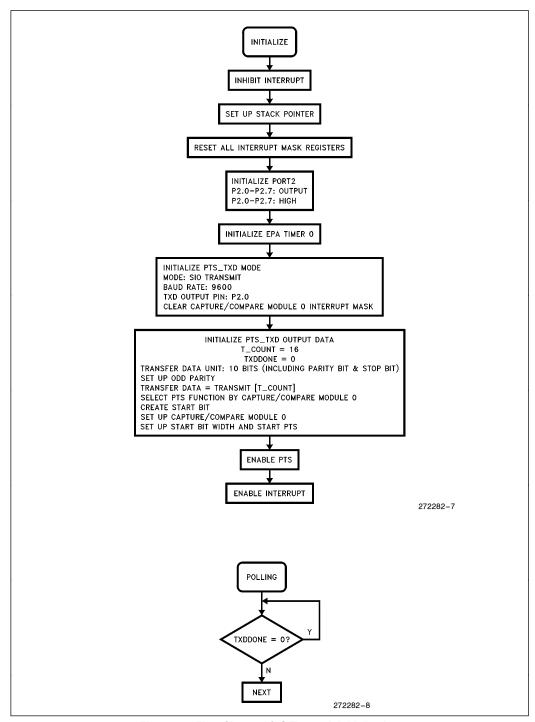

| 5.2 Detailed Program Description                                   | 50   |

| 5.2.1 Constant Declarations (Lines 1-42)                           | 50   |

| 5.2.2 Interrupt Vectors and CCB (Lines 43-66)                      | 50   |

| 5.2.3 Main Program (Lines 67-135)                                  | 50   |

| 5.2.4 End-of-PTS Interrupt Routine (Lines 133–176)                 | 51   |

| 5.3 Top 5 Issues of Using the PTS/SIO Receive Mode                 | 51   |

| 5.4 Program Example                                                | 52   |

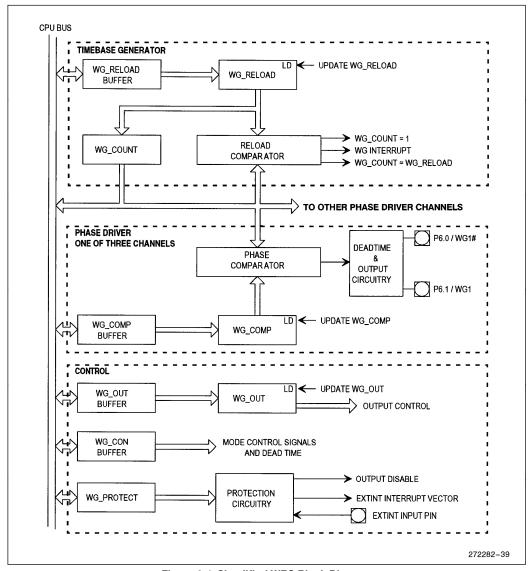

| 6.0 UNDERSTANDING THE WAVEFORM GENERATOR                           | 58   |

| 6.1 Introduction                                                   | 58   |

| 6.2 Buffering                                                      |      |

| 6.3 The Timebase Generator                                         | 60   |

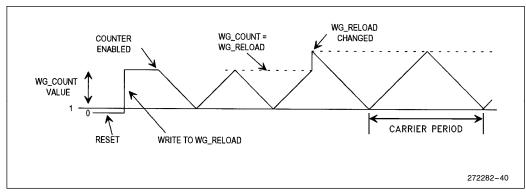

| 6.3.1 Center Aligned Mode WG_COUNT Operation (Modes 0 and 1)       | 60   |

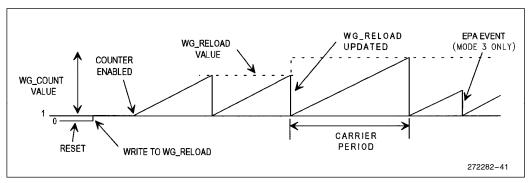

| 6.3.2 Edge Aligned Mode WG_COUNT Operation (Modes 2 and 3) $\dots$ | 60   |

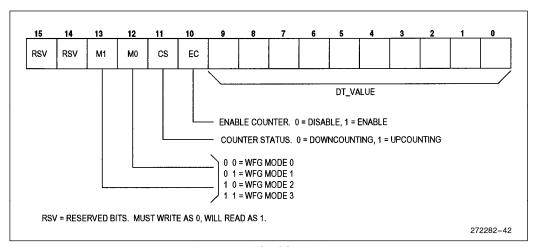

| 6.4 The WFG Control Register (WG_CON)                              | 61   |

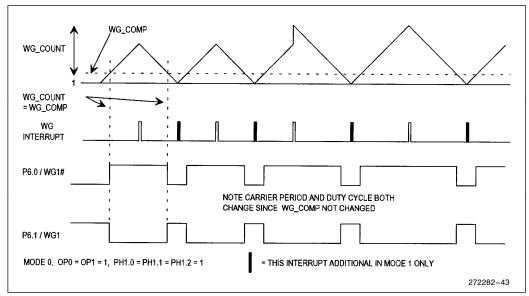

| 6.5 Center Aligned PWM Modes (Modes 0 and 1)                       | 61   |

| 6.5.1 Power-Up Initialization                                      | 61   |

| 6.5.2 WFG Output Operation                                         | 62   |

| 6.5.3 Differences between Mode 0 and Mode 1                        | 62   |

| 6.5.4 Formulas for Carrier Period and Duty Cycle                   | 62   |

| 6.6 Edge Aligned PWM Modes (Modes 2 and 3)                         |      |

| 6.6.1 Power-Up Initialization                                      | 63   |

| 6.6.2 WFG Output Operation                                         | 63   |

| 6.6.3 Differences between Modes 2 and 3                            | 64   |

| 6.6.4 Formulas for Carrier Frequency and Duty Cycle                | 64   |

| 6.7 Interrupt Generation                                           | 64   |

| 6.7.1 The WG Interrupt                                             | 64   |

| 6.7.1.1 WG Interrupt Generation                                    | 65   |

| 6.7.2 The EXTINT Interrupt                                         | 65   |

| CONTENTS                                                         | PAGE |

|------------------------------------------------------------------|------|

| 6.8 Dead-Time Generator                                          | 66   |

| 6.8.1 Dead-Time Generator Operation                              | 66   |

| 6.8.2 Dead-Time Calculation                                      | 67   |

| 6.8.3 Effect of Dead-Time on PWM Duty Cycle                      | 67   |

| 6.9 Output Control Circuitry                                     | 67   |

| 6.9.1 PH Control Bits                                            |      |

| 6.9.2 Enabling and Disabling the WFG Outputs                     |      |

| 6.9.3 Output Polarity                                            |      |

| 6.9.4 Output Schematic                                           |      |

| 6.10 Protection Circuitry                                        |      |

| 6.10.1 Protection Circuitry Operation                            |      |

| 6.11 Software Example                                            | 72   |

| 7.0 3-PHASE INDUCTION MOTOR CONTROL PROGRAM SAMPLE               | 76   |

| 7.1 Introduction                                                 | 76   |

| 7.1.1 Sine Look-Up Table                                         | 77   |

| 7.1.2 Frequency-to-Voltage Look-Up Table                         | 78   |

| 7.1.3 Output Waveforms                                           | 79   |

| 7.2 Detailed Program Description                                 | 80   |

| 7.2.1 Constant Declarations (Lines 1–42)                         | 80   |

| 7.2.2 Interrupt Vectors and CCB (Lines 43-57)                    | 80   |

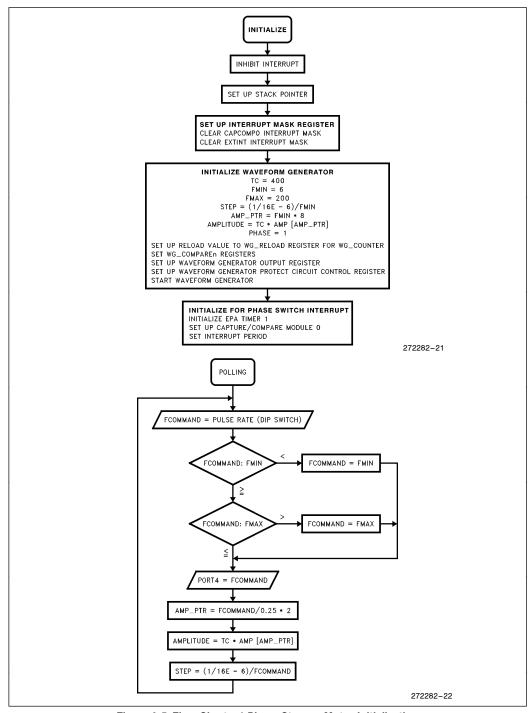

| 7.2.3 Main Program (Lines 58-93)                                 | 80   |

| 7.2.4 Polling Routine (Lines 94–126)                             | 80   |

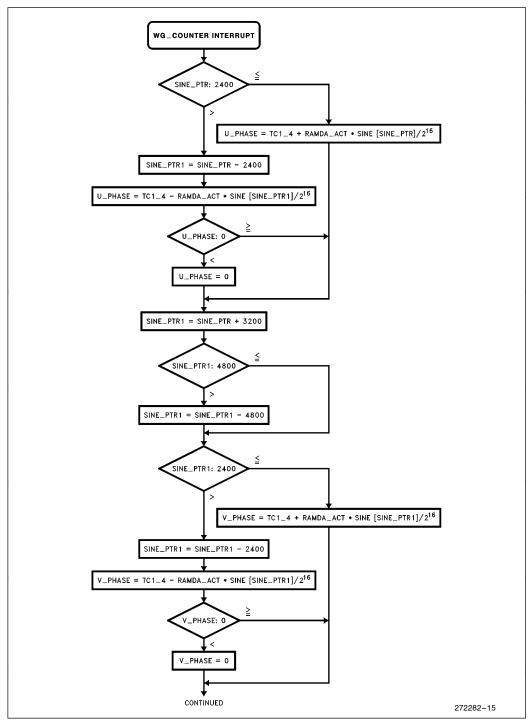

| 7.2.5 WG Interrupt Routine (Lines 127–211)                       | 81   |

| 7.2.6 EXTINT Interrupt Routine (Lines 212–223)                   | 81   |

| 7.2.7 Sine Look-Up Table (Lines 224–1429)                        | 81   |

| 7.2.8 RAMDA Look-Up Table (Lines 1430–2235)                      | 81   |

| 7.3 Top 5 Issues for the 3-Phase Induction Motor Control Example |      |

| 7.4 Program Example                                              | 82   |

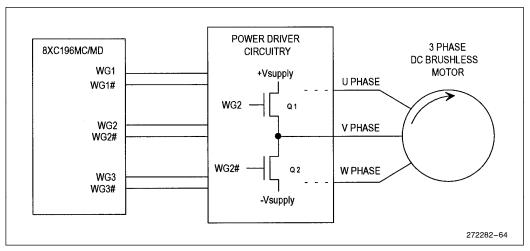

| 8.0 3-PHASE DC BRUSHLESS MOTOR CONTROL PROGRAM SAMPLE            | 90   |

| 8.1 Introduction                                                 |      |

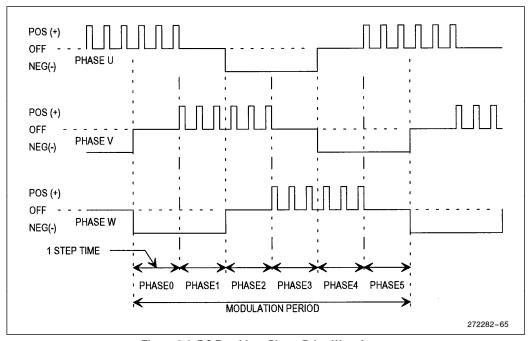

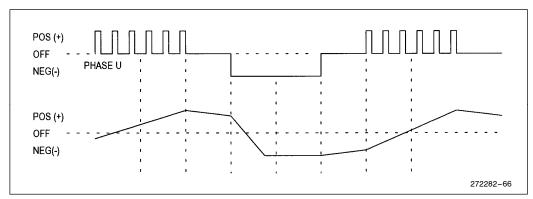

| 8.1.1 Drive Waveforms                                            | 91   |

| 8.1.2 Frequency-to-Voltage Look-Up Table                         | 92   |

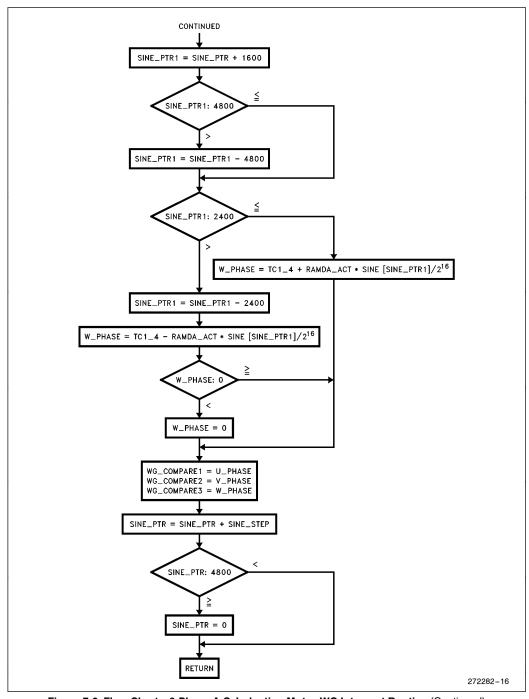

| 8.2 Detailed Program Description                                 | 93   |

| 8.2.1 Constant Declarations (Lines 1–27)                         |      |

| 8.2.2 Interrupt Vectors and CCB (Lines 28–48)                    |      |

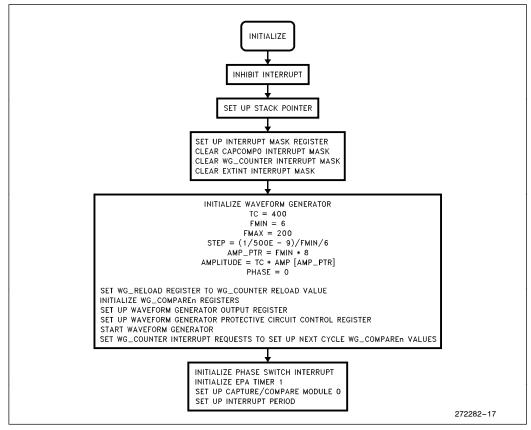

| 8.2.3 Main Program Initialization (Lines 49–97)                  | 93   |

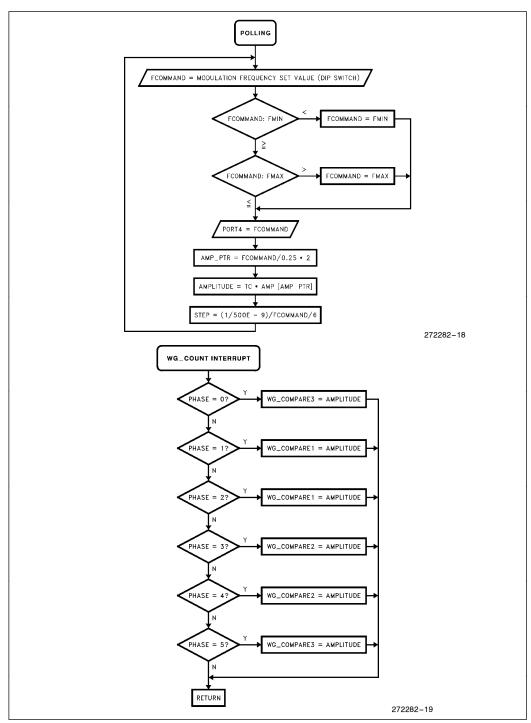

| 8.2.4 Polling Routine (Lines 98–134)                             | 94   |

| 8.2.5 WG Interrupt Routine (Lines 135–173)                       |      |

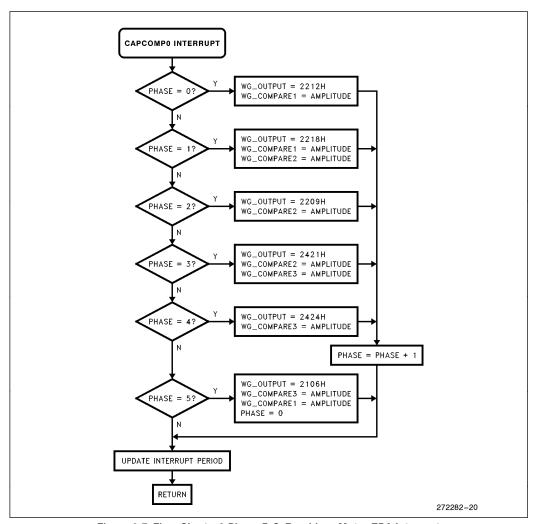

| 8.2.6 CAPCOMP0 Interrupt Routine (Lines 174–225)                 | 94   |

| 8.2.7 EXTINT Interrupt Routine (Lines 226–237)                   | 95   |

| 8.2.8 Amplitude Look-Up Table (Lines 244–1044)                   | 95   |

| CONTENTS                                                       | PAGE |

|----------------------------------------------------------------|------|

| 8.3 Top 4 Issues for the DC Brushless Motor Control Example    | 95   |

| 8.4 Program Example                                            | 96   |

| 9.0 QUADRIPHASE STEPPING MOTOR CONTROL PROGRAM SAMPLE          | 104  |

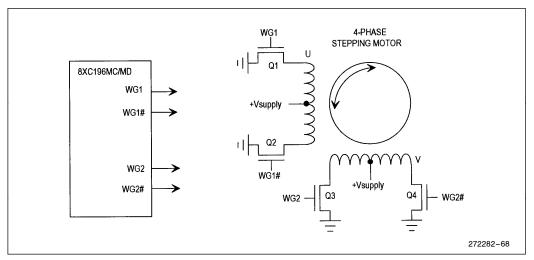

| 9.1 Introduction                                               | 104  |

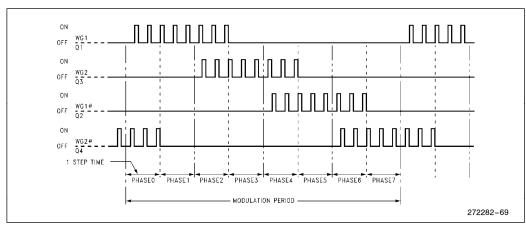

| 9.1.1 Drive Waveforms                                          | 104  |

| 9.2 Detailed Program Description                               | 107  |

| 9.2.1 Constant Declarations (Lines 1-29)                       | 107  |

| 9.2.2 Interrupt Vectors and CCB (Lines 29-49)                  | 107  |

| 9.2.3 Main Program Initialization (Lines 50–95)                | 107  |

| 9.2.4 Polling Routine (Lines 96–134)                           | 107  |

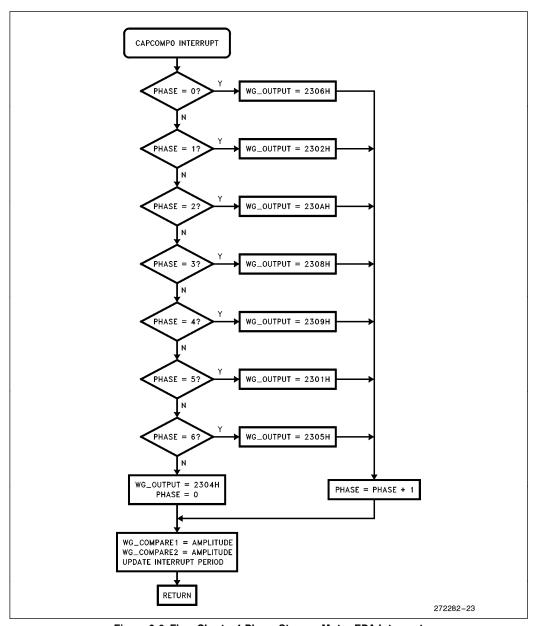

| 9.2.5 CAPCOMP0 Interrupt Routine (Lines 131–186)               | 108  |

| 9.2.6 EXTINT Interrupt Routine (Lines 187–198)                 | 108  |

| 9.2.7 Amplitude Look-Up Table (Lines 199-1005)                 | 108  |

| 9.3 Top 3 Issues for the 4-Phase Stepper Motor Control Example | 108  |

| 9.4 Program Example                                            | 109  |

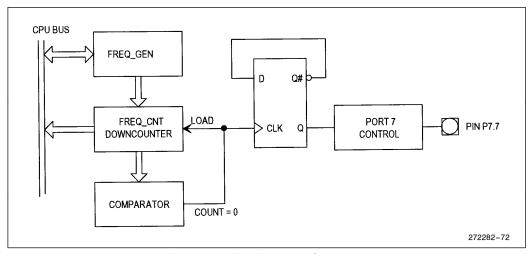

| 10.0 THE FREQUENCY GENERATOR (MD ONLY)                         | 115  |

| 10.1 Introduction                                              | 115  |

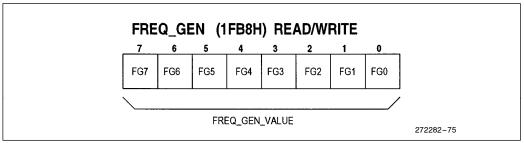

| 10.2 Using the Frequency Generator                             | 116  |

| 10.3 Program to Transmit Data via Frequency Generator          | 118  |

| 10.3.1 Constant and Variable Declarations (Lines 1-81)         | 118  |

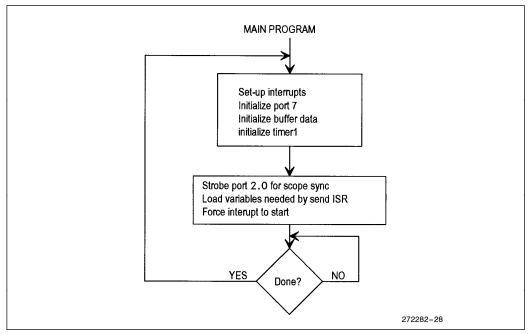

| 10.3.2 Main Program (Lines 82-132)                             | 118  |

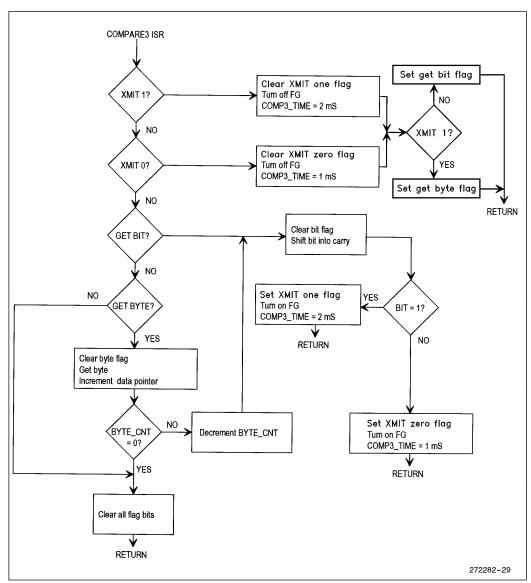

| 10.3.3 Compare3 Interrupt Routine                              | 118  |

| 10.4 Program Example                                           | 119  |

**CONTENTS** PAGE

## List of Figures

| Figure 1-1  | Flow Diagram for PTS and Standard Interrupts | . 3 |

|-------------|----------------------------------------------|-----|

| Figure 1-2  | Standard Interrupt Response Time             | . 5 |

| Figure 1-3  | PTS Interrupt Response Time                  | . 6 |

| Figure 1-4  | PTSSEL Register                              | 10  |

| Figure 1-5  | INT_MASK and INT_MASK1 Registers             | 11  |

| Figure 1-6  | INT_PEND and INT_PEND1 Registers             | 11  |

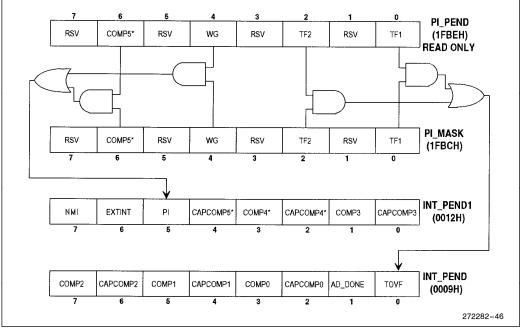

| Figure 1-7  | PI Interrupt Sharing                         | 12  |

| Figure 1-8  | PTS Control Blocks                           | 14  |

| Figure 1-9  | PTSCON Register                              | 15  |

| Figure 1-10 | PTS SIO Control Blocks                       | 20  |

| Figure 1-11 | PTSCON Register in SIO Modes                 | 20  |

| Figure 1-12 | PTSCON1 in Asynchronous Mode                 | 22  |

| Figure 1-13 | PTSCON1 in Synchronous Mode                  | 23  |

| Figure 1-14 | Asynchronous SIO Receive Mode Timing         | 24  |

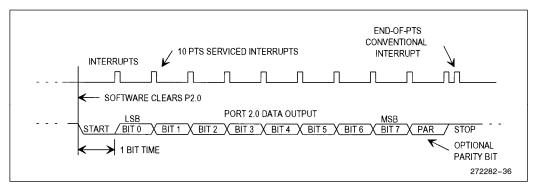

| Figure 1-15 | Asynchronous SIO Transmit Mode Timing        | 24  |

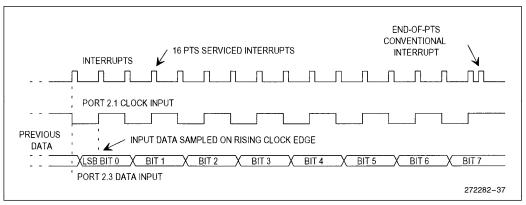

| Figure 1-16 | Synchronous SIO Receive Mode Timing          | 25  |

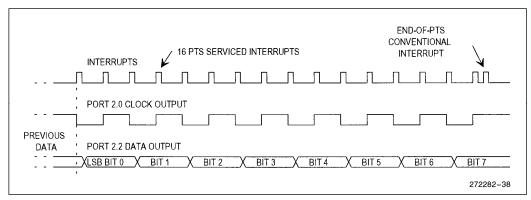

| Figure 1-17 | Synchronous SIO Transmit Mode Timing         | 25  |

| Figure 2-1  | Flow Chart—SSIO Transmit Initialization      | 32  |

| Figure 2-2  | Flow Chart—SSIO Transmit Interrupt Routine   | 33  |

| Figure 3-1  | Flow Chart—SSIO Receive Initialization       | 39  |

| Figure 3-2  | Flow Chart—SSIO Receive Interrupt Routine    | 39  |

| Figure 4-1  | Flow Chart—ASIO Transmit Initialization      | 48  |

| Figure 4-2  | ASIO Transmit Interrupt Routine              | 49  |

| Figure 5-1  | Flow Chart—ASIO Receive Initialization       | 56  |

| Figure 5-2  | Flow Chart—ASIO Receive Interrupt Routine    | 57  |

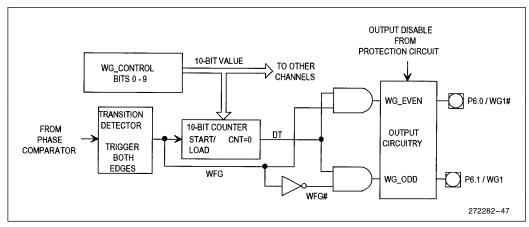

| Figure 6-1  | Simplified WFG Block Diagram                 | 58  |

| Figure 6-2  | Modes 0 and 1 Counter Operation              | 60  |

| Figure 6-3  | Modes 2 and 3 Counter Operation              | 61  |

| Figure 6-4  | WG_CON Register                              | 61  |

| Figure 6-5  | WGCOUNT during Center Aligned PWM            |     |

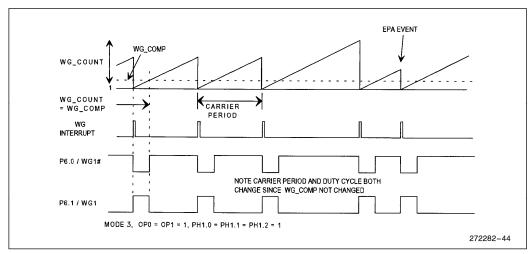

| Figure 6-6  | WG_COUNT during Edge Aligned PWM             | 63  |

| Figure 6-7  | PI Interrupt Sharing                         | 65  |

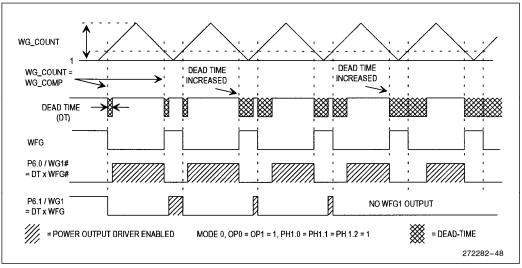

| Figure 6-8  | Dead-Time Generation                         |     |

| Figure 6-9  | Effect of Dead-Time on WFG Duty Cycle        | 67  |

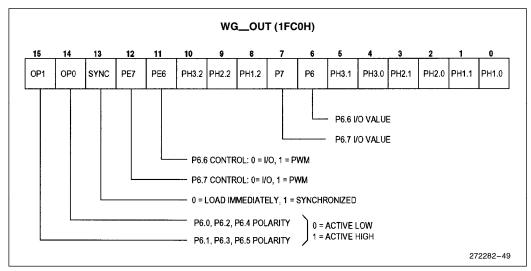

| Figure 6-10 | WG_OUT Register                              | 68  |

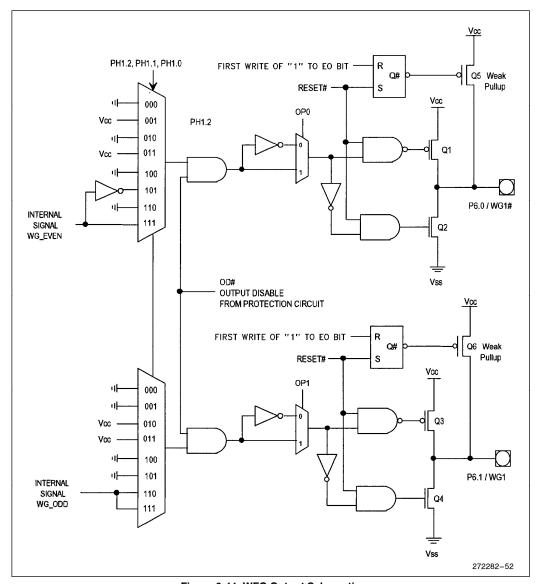

| Figure 6-11 | WFG Output Schematic                         | 70  |

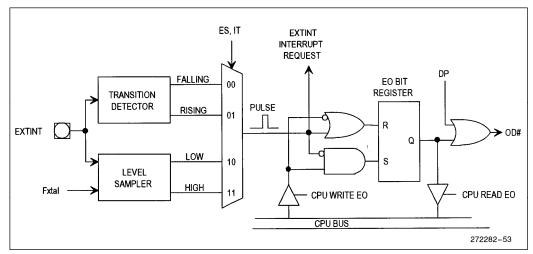

| Figure 6-12 | Protection Circuitry                         | 71  |

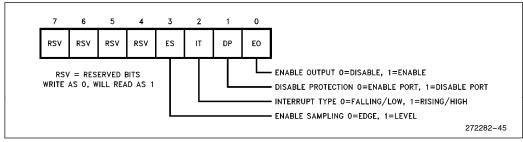

| Figure 6-13 | The WG_PROTECT Register                      | 72  |

**CONTENTS** PAGE

# List of Figures

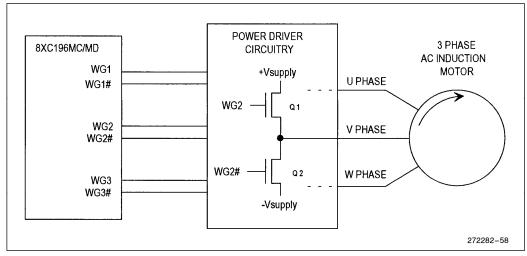

| Figure 7-1  | 3-Phase Induction Motor System                               | 77  |

|-------------|--------------------------------------------------------------|-----|

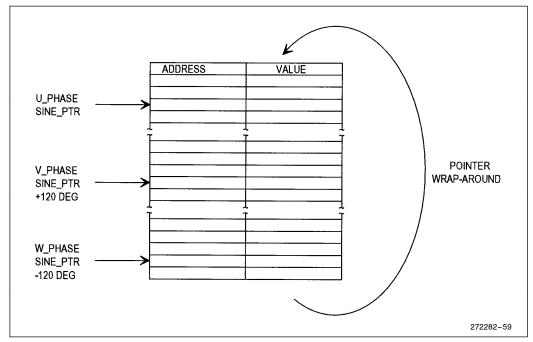

| Figure 7-2  | Sine Look-Up Table                                           | 77  |

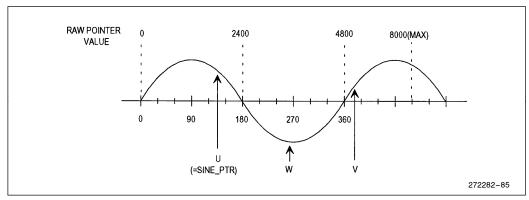

| Figure 7-3  | Raw Pointer Values                                           | 78  |

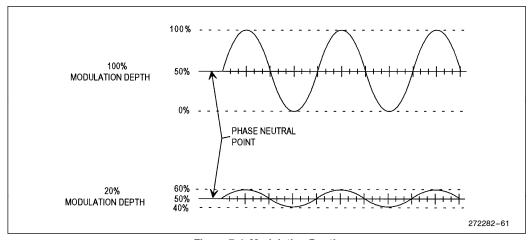

| Figure 7-4  | Modulation Depth                                             | 78  |

| Figure 7-5  | WFG Output Drive                                             | 79  |

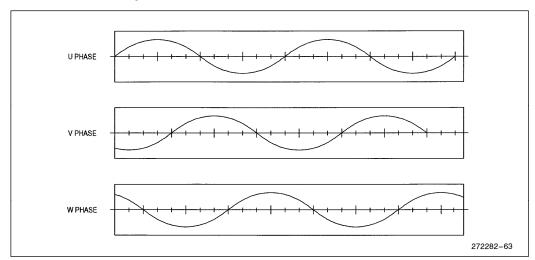

| Figure 7-6  | WFG Output Waveform after Low-Pass Filter                    | 79  |

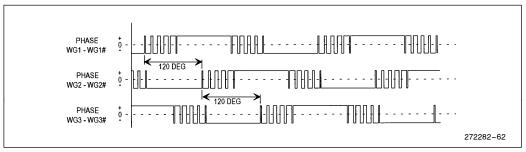

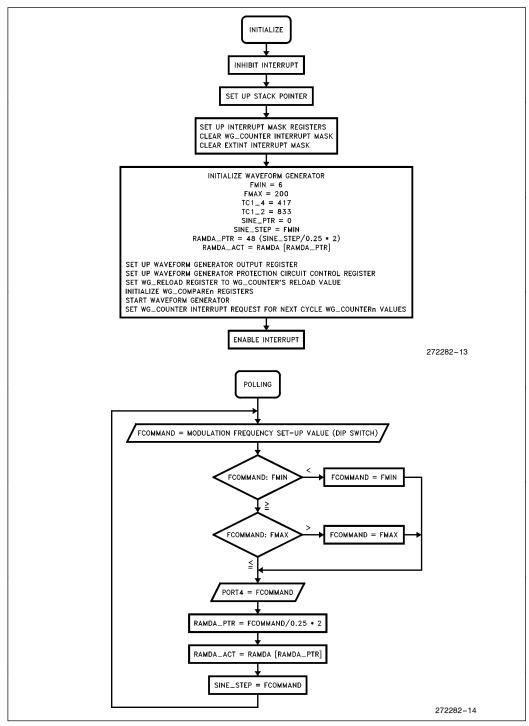

| Figure 7-7  | Flow Chart—3-Phase A.C. Induction Motor Initialization       | 87  |

| Figure 7-8  | Flow Chart—3-Phase A.C. Induction Motor WG Interrupt Routine | 88  |

| Figure 8-1  | 3-Phase DC Brushless Motor System                            | 90  |

| Figure 8-2  | DC Brushless Phase Drive Waveforms                           | 91  |

| Figure 8-3  | WFG Output Waveform after Low-Pass Filter                    | 92  |

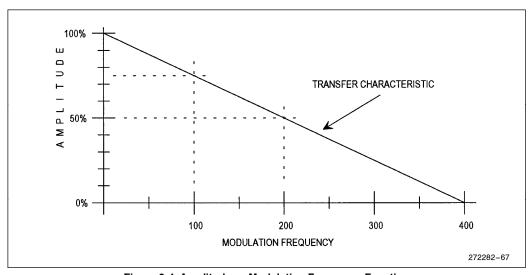

| Figure 8-4  | Amplitude vs Modulation Frequency Function                   | 92  |

| Figure 8-5  | Flow Chart—3-Phase D.C. Brushless Motor Initialization       | 101 |

| Figure 8-6  | Flow Chart—3-Phase D.C. Brushless Motor WGCOUNT Interrupt    | 102 |

| Figure 8-7  | Flow Chart—3-Phase D.C. Brushless Motor EPA Interrupt        | 103 |

| Figure 9-1  | 4-Phase Stepper Motor System                                 | 104 |

| Figure 9-2  | 4-Phase Stepper Drive Waveforms                              | 104 |

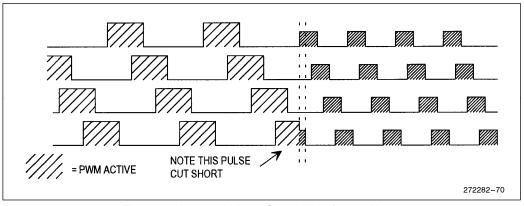

| Figure 9-3  | Average Voltage Output Waveform at Motor                     | 105 |

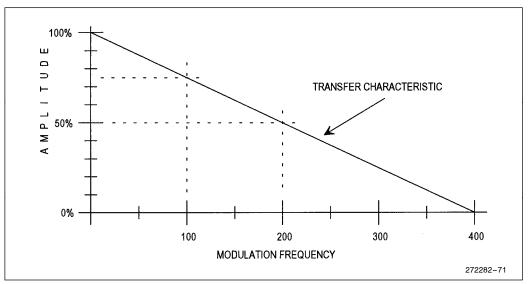

| Figure 9-4  | Amplitude vs Modulation Frequency Function                   | 106 |

| Figure 9-5  | Flow Chart—4-Phase Stepper Motor Initialization              | 113 |

| Figure 9-6  | Flow Chart—4-Phase Stepper Motor EPA Interrupt               | 114 |

| Figure 10-1 | The Frequency Generator                                      | 115 |

| Figure 10-2 | FREQ_GEN Register                                            |     |

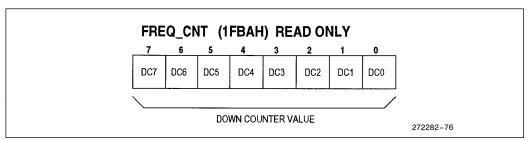

| Figure 10-3 | FREQ_CNT Register                                            | 116 |

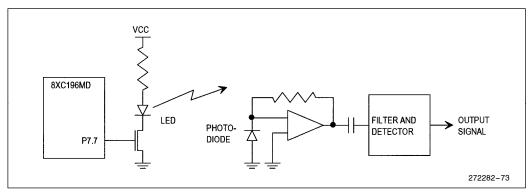

| Figure 10-4 | Infrared Remote Control Block Diagram                        | 116 |

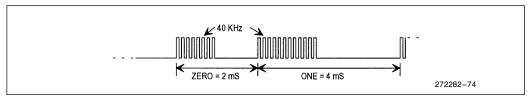

| Figure 10-5 | Encoding of Zeros and Ones                                   | 117 |

| Figure 10-6 | Flow Chart—Frequency Generator Initialization                | 123 |

| Figure 10-7 | Interrupt Routine Flow Chart                                 | 124 |

**CONTENTS** PAGE

### **List of Tables**

| lable 1-1  | Interrupt Sources                                   | 6   |

|------------|-----------------------------------------------------|-----|

| Table 1-2  | Interrupt and PTS Control and Status Registers      | 9   |

| Table 1-3  | EXTINT Mode Selection                               | 13  |

| Table 1-4  | PTS Mode Select (PTSCON Bits 5–7)                   | 14  |

| Table 1-5  | PTSCON Bits 0-4 for Single and Block Transfer Modes | 15  |

| Table 1-6  | PTSCON Bits 0-4 for A/D Scan Mode                   | 15  |

| Table 1-7  | Single Transfer Mode PTSCB                          | 16  |

| Table 1-8  | Block Transfer Mode PTSCB                           | 17  |

| Table 1-9  | A/D Scan Mode Command/Data Table                    | 17  |

| Table 1-10 | Command/Data Table (Example 1)                      | 18  |

| Table 1-11 | A/D Scan Mode PTSCB (Example 1)                     | 18  |

| Table 1-12 | Command/Data Table (Example 2)                      | 19  |

| Table 1-13 | A/D Scan Mode PTSCB (Example 2)                     | 19  |

| Table 1-14 | PTSCON Bits 0-4 for SIO Modes                       | 21  |

| Table 1-15 | PTSCON Bits 0-7 for Asynchronous SIO Mode           | 22  |

| Table 1-16 | PTSCON Bits 0-7 for Synchronous SIO Mode            | 23  |

| Table 6-1  | Conditions for Register Updates                     | 59  |

| Table 6-2  | EXTINT Mode Selection                               | 65  |

| Table 6-3  | WG Output Configuration                             | 68  |

| Table 6-4  | Protection and Output Status                        | 69  |

| Table 6-5  | Output Polarities, Modes 4-7                        | 69  |

| Table 8-1  | WFG Output Sequencing                               | 91  |

| Table 9-1  | WFG Output Sequencing                               | 105 |

#### **OVERVIEW**

This application note gives several practical software examples using the unique features of the 8XC196MC microcontroller. Each section uses one of the 8XC196MC features to perform a "typical" application. A brief explanation of the peripheral used is given, followed by detailed analysis of a software example. The program source code is listed, along with figures and flow charts.

This application note is meant to be used in conjunction with the 8XC196MC USER'S MANUAL, order number 272181.

The program examples were developed for several different hardware configurations, and may need to be modified for the end user's application.

All programs were assembled using the standard Intel ASM-96 assembler, along with the MC include file for register names. Additional include files are required to support the windowed register names and look-up tables. The program source code is available from the Intel bulletin board system:

The Intel Applications Bulletin Board System (916) 356-3600 or (916) 356-3605

1200, 2400 Bps 8 DATA BITS NO PARITY 1 STOP BIT

and

9600 Bps v.32, v.42 8 DATA BITS NO PARITY 1 STOP BIT

All 8XC196MC files are under the embedded directory.

#### 1.0 UNDERSTANDING THE 8XC196MC/MD INTERRUPTS AND PTS

A microcontroller's primary function is to provide real-time control of an instrument or device. The interrupt control circuitry within a microcontroller permits real-time events to control program flow. When an event generates an interrupt, the CPU services the interrupt before executing the next instruction. An internal peripheral, an external signal, or an instruction can request an interrupt. In the simplest case, the device receives the request, performs the service, and returns to the task that was interrupted.

#### 1.1 Interrupt Processing

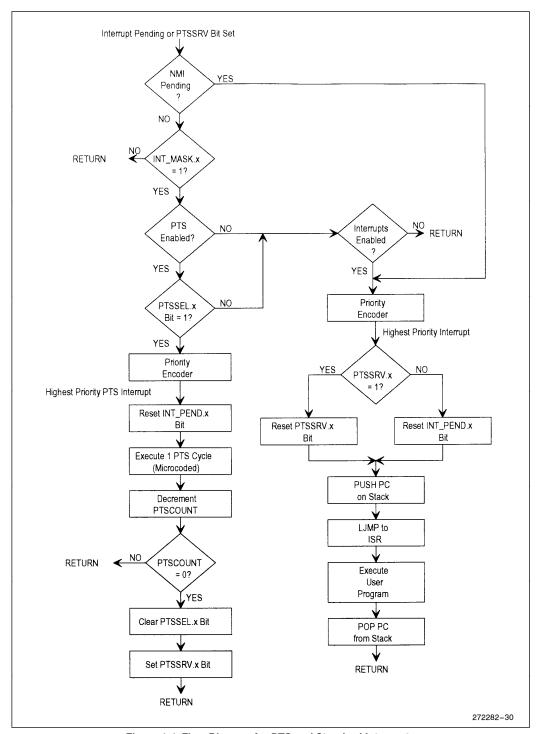

There are two options for interrupt service: software interrupt service routines via the Interrupt Controller and microcoded hardware interrupt processing via the Peripheral Transaction Server (PTS). You can select either option for each of the maskable interrupts. The nonmaskable interrupts (NMI, Software Trap, and Unimplemented Opcode) are always serviced by interrupt service routines. Figure 1-1 illustrates the interrupt processing flow.

#### 1.1.1 INTERRUPT CONTROLLER

The Interrupt Controller generates vectors to software interrupt service routines. When the hardware detects an interrupt, it generates and executes an interrupt call. This pushes the contents of the program counter onto the stack and then loads the program counter with the contents of the appropriate interrupt vector. The CPU vectors to the address of the interrupt service routine, then executes the routine. Upon completion of the interrupt service routine, the program counter is reloaded from the stack and program execution continues.

#### 1.1.2 PERIPHERAL TRANSACTION SERVER (PTS)

The Peripheral Transaction Server (PTS) is a microcoded hardware interrupt handler. It can be used in place of a standard interrupt service routine for each of the maskable interrupts. The PTS services interrupts with less overhead; it does not modify the stack or the PSW, and it allows normal instruction flow to continue. For these reasons, the PTS can service an interrupt in the time required to execute a single instruction.

Figure 1-1. Flow Diagram for PTS and Standard Interrupts

The 8XC196MC/MD PTS operates in four special microcoded modes that enable it to complete specific tasks in much less time than an equivalent interrupt service routine can. See Section 1.8 for a description of the PTS modes.

Each PTS interrupt requires a block of data called the PTS Control Block (PTSCB). The PTS vector table entries point to the PTSCB. When a PTS interrupt occurs, the Priority Encoder selects the appropriate vector and fetches the PTS Control Block (PTSCB). The PTSCB determines the mode, the number of transfers per cycle (if applicable), the total number of cycles that will execute before the PTS requires servicing, and the source and/or destination of data transfers (if applicable). Each PTS interrupt generates one PTS cycle.

#### NOTE:

The PTSCB must be located in register RAM, and must be aligned on a quad-word boundary (evenly divisible by eight).

#### 1.2 Interrupt Latency

Interrupt latency is the total delay between the time that the interrupt is generated and the time that the device begins executing the interrupt service routine or PTS cycle. A delay occurs between the time that the interrupt is generated and the time that it is acknowledged.

Acknowledgment is defined as when the CPU clears the interrupt pending bit that initiated the interrupt. If the interrupt occurs earlier than four state times before the end of the current instruction, it may not be acknowledged until after the next instruction finishes. This additional delay occurs because instructions are prefetched and prepared a few state times before they are executed. Thus, the maximum delay between interrupt generation and acknowledgment is four state times plus the execution time of the next instruction.

When a standard interrupt is acknowledged, the hardware clears the interrupt pending bit and forces a call to the address contained in the corresponding interrupt vector after completing the current instruction. The procedure that gets the vector and forces the call requires 11 state times. If the stack is in 16-bit 0 wait-state external RAM, the call requires an additional 2 state times. When a PTS interrupt is acknowledged, it immediately vectors to the PTSCB and begins executing the PTS cycle.

Execution of any of the following inhibits interrupts from being acknowledged until after the **next** instruction is executed:

- the signed prefix opcode (FE) for the two-byte, signed multiply and divide instructions

- the Unimplemented Opcode interrupt

- the Software Trap interrupt

- any PTS cycle (back-to-back PTS cycles are not possible)

- any of these eight protected instructions: DI, EI, DPTS, EPTS, POPA, POPF, PUSHA, PUSHF.

All of these increase latency because an interrupt cannot occur until after the next instruction is executed.

#### 1.2.1 CALCULATING LATENCY

The maximum latency occurs when the interrupt occurs too late for acknowledgment following the current instruction. The following worst-case calculation assumes that the current instruction is not a protected instruction. To calculate latency, add the following terms:

- Time for the current instruction to finish execution (4 state times).

- If this is a protected instruction, the instruction that follows it must also execute before the interrupt can be acknowledged. Add the execution time of the instruction that follows a protected instruction.

- Time for the next instruction to execute. (The longest instruction, NORML, takes 39 state times. See Appendix A

for instruction execution times.)

- For standard interrupts only, the response time to get the vector and force the call

- 11 state times for an internal stack or 13 for an external stack

Please note that, depending on the number of words being transferred, the BMOV instruction could take longer than 39 state times to execute. In this case, the BMOVI instruction may be a better choice.

#### 1.2.2 STANDARD INTERRUPT LATENCY

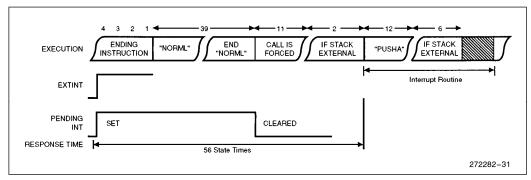

Figure 1-2 illustrates interrupt latency. The maximum latency for a standard interrupt is 56 state times (4 + 39 + 13). This delay time does not include the time needed to execute the first instruction in the interrupt service routine or the time to execute the instruction following a protected instruction.

Figure 1-2. Standard Interrupt Response Time

#### 1.2.3 PTS INTERRUPT LATENCY

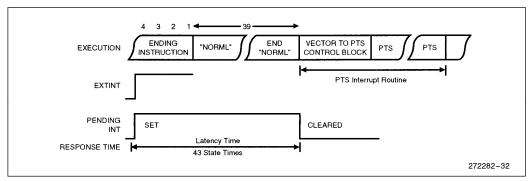

The interrupt latency for a PTS interrupt is 43 state times (4 + 39). This delay time does not include the added delay if the PTS is disabled (PSW.2 clear), if a protected instruction is being executed, or if a PTS request is already in progress.

Figure 1-3. PTS Interrupt Response Time

#### 1.3 Interrupt Priorities

Table 1-1 shows the default interrupt priorities (30 is highest and 0 is lowest). The Unimplemented Opcode and Software Trap interrupts are not prioritized; they go directly to the Interrupt Controller for servicing and thus vector immediately upon execution.

The Priority Encoder determines the priority of all other pending interrupt requests. NMI has the highest priority of all prioritized interrupts, PTS interrupts have the next highest priority, and standard interrupts have the lowest. The Priority Encoder selects the highest priority pending request for service.

| Interrupt Service         | Symbol   | Interrupt Source |        |          | PTS Service |        |          |  |

|---------------------------|----------|------------------|--------|----------|-------------|--------|----------|--|

| interrupt corvice         | - Cy2C.  | Name             | Vector | Priority | Name        | Vector | Priority |  |

| NMI                       | NMI      | INT15            | 0203EH | 30       | _           | _      | _        |  |

| EXTINT Pin                | EXTINT   | INT14            | 0203CH | 14       | PTS14       | 0205CH | 29       |  |

| Peripheral Interrupt      | PI       | INT13            | 0203AH | 13       | PTS13*      | 0205AH | 28       |  |

| Capture/Compare5**        | CAPCOMP5 | INT12            | 02038H | 12       | PTS12       | 02058H | 27       |  |

| Compare4**                | COMP4    | INT11            | 02036H | 11       | PTS11       | 02056H | 26       |  |

| Capture/Compare4**        | CAPCOMP4 | INT10            | 02034H | 10       | PTS10       | 02054H | 25       |  |

| Compare3                  | COMP3    | INT09            | 02032H | 09       | PTS09       | 02052H | 24       |  |

| Capture/Compare3          | CAPCOMP3 | INT08            | 02030H | 08       | PTS08       | 02050H | 23       |  |

| Unimplemented Opcode      | _        | _                | 02012H | _        | _           | _      | _        |  |

| Software TRAP Instruction | _        | _                | 02010H | _        | _           | _      | _        |  |

| Compare2                  | COMP2    | INT07            | 0200EH | 07       | PTS07       | 0204EH | 22       |  |

| Capture/Compare2          | CAPCOMP2 | INT06            | 0200CH | 06       | PTS06       | 0204CH | 21       |  |

| Compare1                  | COMP1    | INT05            | 0200AH | 05       | PTS05       | 0204AH | 20       |  |

| Capture/Compare1          | CAPCOMP1 | INT04            | 02008H | 04       | PTS04       | 02048H | 19       |  |

| Compare0                  | COMP0    | INT03            | 02006H | 03       | PTS93       | 02046H | 18       |  |

| Capture/Compare0          | CAPCOMP0 | INT02            | 02004H | 02       | PTS02       | 02044H | 17       |  |

| A/D Conversion Complete   | AD_DONE  | INT01            | 02002H | 01       | PTS01       | 02042H | 16       |  |

| Timer Overflow            | TOVF     | INT00            | 02000H | 00       | PTS00*      | 02040H | 15       |  |

Table 1-1. Interrupt Sources

<sup>\*</sup>This is a shared interrupt from the PI\_PEND register. Be aware that the PTS cannot determine the source of the PI interrupt

<sup>\*\*</sup>These interrupts only exist on the 8XC196MD. They are reserved on the 8XC196MC.

#### 1.3.1 MODIFYING INTERRUPT PRIORITIES

The software can modify the default priorities of maskable interrupts by controlling the interrupt mask registers (INT\_MASK, INT\_MASK1, and PI\_MASK). For example, you can specify which interrupts, if any, can interrupt an interrupt service routine. The following code shows one way to prevent all interrupts, except EXTINT (priority 14), from interrupting an EPA COMP3 interrupt service routine (priority 9).

```

COMP3_ISR:

PUSHA

: Save PSW, INT_MASK, INT_MASK1, & WSR

;(this disables all interrupts)

LDB INT_MASK1, #01000000B

;Enable EXTINT only

;Enable interrupt servicing

Service the COMP3 interrupt

POPA

;Restore PSW, INT_MASK, INT_MASK1, &

:WSR registers

RET

CSEG AT 02032H

;fill in interrupt table

DCW COMP3_ISR

END

```

Note that location 02032H in the interrupt vector table must be loaded with the value of the label COMP3\_ISR before the interrupt request occurs and that the COMP3 interrupt must be enabled for this routine to execute.

This routine, like all interrupt service routines, is handled in the following manner:

- After the hardware detects and prioritizes an interrupt request, it generates and executes an interrupt call. This

pushes the program counter onto the stack and then loads it with the contents of the vector corresponding to the

highest priority, pending, unmasked interrupt. The hardware will not allow another interrupt call until after the

first instruction of the interrupt service routine is executed.

- 2. The PUSHA instruction, which is now guaranteed to execute, saves the contents of the PSW, INT\_MASK, INT\_MASK1, and Window Select Register (WSR) onto the stack and then clears the PSW, INT\_MASK, and INT\_MASK1. In addition to the arithmetic flags, the PSW contains the global interrupt enable bit (I) and the PTS enable bit (PSE). By clearing the PSW and the interrupt mask registers, PUSHA effectively masks all maskable interrupts, disables standard interrupt servicing, and disables the PTS. Because PUSHA is a protected instruction, it also inhibits interrupt calls until after the next instruction executes.

- 3. The LDB INT\_MASK1 instruction enables those interrupts that you choose to allow to interrupt the service routine. In this example, only EXTINT can interrupt the COMP3 interrupt service routine. By enabling or disabling interrupts, the software establishes its own interrupt servicing priorities.

- The EI instruction re-enables interrupt processing and inhibits interrupt calls until after the next instruction executes.

- 5. The actual interrupt service routine executes within the priority structure established by the software.

- 6. At the end of the service routine, the POPA instruction restores the original contents of the PSW, INT\_MASK, INT\_MASK1, and WSR registers; any changes made to these registers during the interrupt service routine are overwritten. Because interrupt calls cannot occur immediately following a POPA instruction, the last instruction (RET) will execute before another interrupt call can occur.

Notice that the "preamble" and exit code for this routine does not save or restore register RAM. The interrupt service routine is assumed to allocate its own private set of registers from the lower Register File. The general-purpose Register RAM in the lower Register File makes this quite practical. In addition, the RAM in the upper Register File is available via windowing.

#### 1.4 End-of-PTS Interrupts

An end-of-PTS interrupt is a "standard" interrupt, but it is generated by a bit being set in the PTSSRV register. The Interrupt Controller processes it with an interrupt service routine that is stored in the memory location pointed to by the standard interrupt vector. When the end-of-PTS interrupt vectors to the interrupt service routine, hardware clears the PTSSRV bit.

It is important to note that the end-of PTS interrupt does not affect the conventional interrupt pending bit. The end-of-PTS interrupt is forced by the PTS microcode setting the corresponding PTSSRV bit. Thus, a conventional interrupt and an end-of-PTS interrupt can occur simultaneously, and both will be serviced.

The end-of-PTS interrupt routine typically services the PTSCB and may also process data that was collected from multiple PTS cycles. Before exiting, the interrupt service routine must set the PTSSEL bit to re-enable PTS interrupt servicing for that interrupt. Figure 1-1 shows the program flow for processing of all interrupts.

#### 1.5 Special Interrupts

The device supports three special interrupts: Unimplemented Opcode, Software Trap, and NMI. These interrupts are not affected by the interrupt enable bit (I) in the PSW (PSW.1), and they cannot be masked. All of these interrupts are serviced by the Interrupt Controller; they cannot be assigned to the PTS. Of these three, only NMI goes through the Transition Detector and Priority Encoder. The other two special interrupts go directly to the Interrupt Controller for servicing. Be aware that these interrupts are often assigned to special functions in Intel development tools.

#### 1.5.1 UNIMPLEMENTED OPCODE

If the CPU attempts to execute an unimplemented opcode, an indirect vector through location 02012H occurs. This prevents random software execution during hardware and software failures. The interrupt vector should contain the starting address of an error routine that will not further corrupt an already erroneous situation. The Unimplemented Opcode interrupt prevents other interrupts from being acknowledged until after the next instruction is executed.

#### 1.5.2 SOFTWARE TRAP

The TRAP instruction (opcode 0F7H) causes an interrupt call that is vectored through location 02010H. The TRAP instruction provides a single-instruction interrupt that is useful when debugging software or generating software interrupts. The TRAP instruction prevents other interrupts from being acknowledged until after the next instruction is executed.

#### 1.5.3 NMI

The external NMI pin generates a Nonmaskable Interrupt for implementation of critical interrupt routines. NMI has the highest priority of all the prioritized interrupts. It is passed directly from the Transition Detector to the Priority Encoder, and it vectors indirectly through location 0203EH.

A Transition Detector samples NMI during Phase 1 (CLKOUT low) and latches the interrupt when a low-to-high transition occurs. The interrupt input must be held high for at least one state time to guarantee recognition. Because the interrupts are edge-triggered, only one interrupt is generated if an input is held high.

#### NOTE

The interrupt detection logic can generate an interrupt if a momentary negative glitch occurs while the NMI pin is held high. For this reason, NMI should normally be held low when not active.

For design symmetry with the INT\_PEND1 register, an NMI mask bit exists in the INT\_MASK1 register. However, the mask bit has no function; NMI is enabled for both NMI\_MASK set and NMI\_MASK cleared. To ensure compatibility with future products, always write zero to the NMI mask bit.

#### 1.6 EPA Interrupts

Interrupts from the EPA to the core are handled in two ways. Event interrupts from all EPA modules except COMP5 are mapped directly to the core interrupt unit as separate sources. These interrupts can be serviced either by a software interrupt routine or by the PTS. The PI interrupt is a shared interrupt which includes the Compare5 (COMP5) and the Waveform Generator (WG) interrupts. Since the PTS cannot tell which interrupt source caused the PI interrupt, it should not be used if more than one of the shared interrupts is unmasked.

#### 1.6.1 USING THE PTS TO SERVICE THE EPA

The PTS can be configured to service the individual EPA interrupts. For example, you could create four PTS channels, one for each Capture module, 0–3. Set up each channel with a fixed source address (the CAPCOMx\_TIME register), an auto-incrementing destination address (somewhere in RAM), and a transfer count (n transfers). Select PTS service for each interrupt, and configure an EPA module for capture. Each time an event occurs, the time is stored in CAPCOMx\_TIME and a PTS interrupt is generated. The PTS transfers the time value from CAPCOMx\_TIME to a RAM location and decrements the transfer count. After n interrupts (PTS transfers) occur on the channel, the transfer count equals zero, and a conventional software interrupt routine is initiated. This software interrupt service routine could reinitialize the PTS channels and perhaps process the captured data arrays.

You can use a similar method to support multiple sequential output events programmed for a single pin. After one output event executes, the resulting interrupt request causes the PTS to transfer the next event time from RAM into CAPCOMx\_TIME. Since the PTS can take only a single action, it cannot change the control register. Therefore, this method can be used only when the same action is to be reinitiated at different times or when the action is a pin toggle. (See "Configuring the PTS" Section 1.8 for a complete discussion of the PTS modes.)

#### 1.7 Programming the Interrupts

Table 1-2 lists the programmable registers that affect the performance and function of the Interrupt Controller and PTS.

Table 1-2. Interrupt and PTS Control and Status Registers

| Register<br>Mnemonic  | Register<br>Name                               | Description                                                                                                                                         |

|-----------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| PI_MASK               | Peripheral<br>Interrupt<br>Mask<br>Register    | This register enables/disables the 4 shared interrupts COMP5, WG, TF2, TF1                                                                          |

| PI_PEND               | Peripheral<br>Interrupt<br>Pending<br>Register | The bits in this register are set by hardware to indicate that an interrupt is pending.                                                             |

| INT_MASK<br>INT_MASK1 | Interrupt<br>Mask<br>Registers                 | These registers enable/disable each maskable interrupt (that is, each interrupt except Unimplemented Opcode, Software Trap, and NMI.)               |

| INT_PEND<br>INT_PEND1 | Interrupt<br>Pending<br>Registers              | The bits in this register are set by hardware to indicate that an interrupt is pending.                                                             |

| PSW                   | Program<br>Status Word                         | This register contains one bit that globally enables or disables servicing of all maskable interrupts and another that enables or disables the PTS. |

| PTSSEL                | PTS<br>Select<br>Register                      | This register selects either a PTS cycle or a standard interrupt service routine for each of the fifteen maskable interrupt requests.               |

| PTSSRV                | PTS<br>Service<br>Register                     | The bits in this register are set by microcode to request an end-of-PTS interrupt.                                                                  |

#### 1.7.1 SELECTING EITHER PTS OR STANDARD INTERRUPT SERVICE

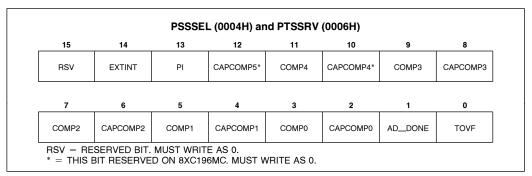

The PTS Select register (PTSSEL) selects either a PTS cycle or a standard software interrupt service routine for each of the maskable interrupt requests (see Figure 1-4). Setting a bit selects a PTS cycle; clearing a bit selects a standard interrupt service routine. Note that both the PTSSEL and PTSSRV registers share the same bit names and locations within their registers.

Figure 1-4. PTSSEL Register

#### 1.7.2 ENABLING PTS INTERRUPTS

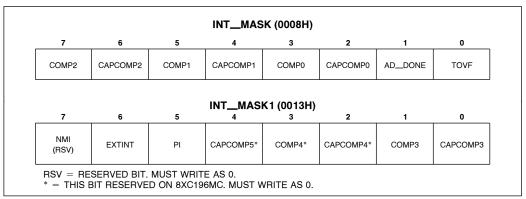

When you assign an interrupt to the PTS, you must set up a PTS control block (PTSCB) for each interrupt source. Once the control block is set up, you must enable both the PTS and the individual interrupt. The PTS enable (PSE) bit in the Program Status Word (PSW.2) globally enables or disables the PTS. The EPTS instruction sets the bit, which enables the PTS, and the DPTS instruction clears the bit, which disables the PTS. The bits in INT\_MASK and INT\_MASK1 individually enable or disable the interrupts (see Figure 1-5). These bits must be set to service the interrupt with the PTS.

The PTS does not require that global interrupt servicing be enabled. However, you must enable global interrupt servicing to handle the end-of-PTS interrupt. The global interrupt enable (I) bit in the Program Status Word (PSW.1) globally enables or disables the servicing of all maskable interrupts. The EI instruction sets the bit, which enables standard interrupt servicing, and the DI instruction clears the bit, which disables standard interrupt servicing.

#### NOTE:

PTS cycles will occur after a DI instruction, if the appropriate INT\_MASK and PTSSEL bits are set. However, the end-of-PTS interrupt will not occur.

#### 1.7.3 ENABLING STANDARD INTERRUPTS

When you assign an interrupt to a standard software service routine, you must enable both the servicing of the interrupt and the individual interrupt. The global interrupt enable (I) bit in the Program Status Word (PSW.1) globally enables or disables the servicing of all maskable interrupts. The EI instruction sets the bit, which enables interrupt servicing. The DI instruction clears the bit, which disables interrupt servicing. The bits in INT\_MASK and INT\_MASK1 individually enable or disable the interrupts (see Figure 1-5). Interrupts that occur while interrupt servicing is globally disabled (PSW.1 cleared) are held in the interrupt pending registers.

#### 1.7.4 INTERRUPT MASK REGISTERS

The interrupt mask registers, INT\_MASK and INT\_MASK1 (Figure 1-5), enable or disable (mask) individual interrupts. With the exception of the Nonmaskable Interrupt (NMI) bit (INT\_MASK1.7), setting a bit enables the corresponding interrupt source; clearing a bit disables the source. A device reset or the PUSHA instruction clears the interrupt mask registers (disabling interrupts). The PUSHF instruction clears INT\_MASK but does not clear INT\_MASK1.

Figure 1-5. INT\_MASK and INT\_MASK1 Registers

#### 1.7.5 INTERRUPT PENDING REGISTERS

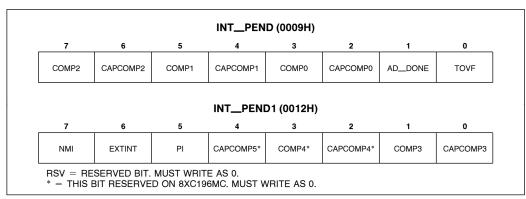

When the Transition Detector detects an interrupt, it sets the corresponding bit in the INT\_PEND or INT\_PEND1 register. This bit is set even if the individual interrupt is disabled (masked). The pending bit is cleared when the program vectors to the interrupt service routine. INT\_PEND and INT\_PEND1 can be read, to determine which interrupts are pending. They can also be modified (written), either to clear pending interrupts or to generate interrupts under software control.

Figure 1-6. INT\_PEND and INT\_PEND1 Registers

Care should be taken in writing code that modifies these registers. For example, an instruction sequence that clears a pending bit could result in an interrupt being acknowledged after the sequence begins but before the bit is actually cleared. In this case a five-state-time *partial* interrupt cycle occurs. That is, the interrupt process begins, but never jumps to the interrupt service routine. This time delay can be avoided by making the code inseparable, in the sense that an interrupt will not be acknowledged while the code is executing. The easiest way to do this is to use the logical instructions in the two- or three-operand format, as in the example:

ANDB INT\_PEND,#01111111B ; Clears the COMP2 interrupt ORB INT\_PEND,#10000000B ; Sets the COMP2 interrupt

The device does not acknowledge interrupts during execution of these "read-modify-write" instructions.

#### 1.7.6 THE PERIPHERAL INTERRUPT (PI)

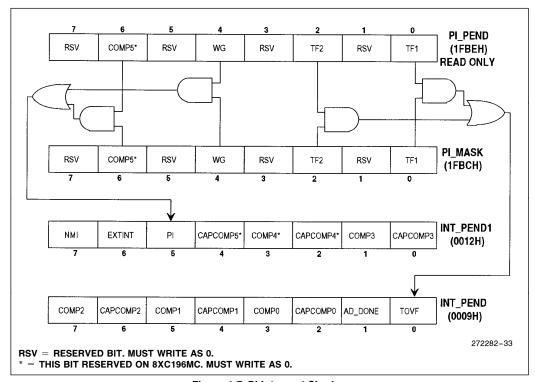

The Peripheral Interrupt (PI) is a "shared" interrupt, and signals that an interrupt has been generated by either the Compare5 (COMP5) module or the Waveform Generator (WG). When any of these sources generate an interrupt, the corresponding bit in the PI\_PEND register is set. If the bit is unmasked in the PI\_MASK register, the PI interrupt pending bit in INT\_PEND1 is set. Figure 1-7 illustrates the relationship between these registers.

Figure 1-7. PI Interrupt Sharing

The user interrupt routine can read the PI\_PEND register to determine what the source of the interrupt was. Note that reading PI\_PEND clears all bits. Therefore, the value of the register must be stored in a shadow register if more than one bit needs to be checked. Also note that the PI\_PEND bits cannot be set by writing to the PI\_PEND register. This register is read only, writes will have no effect.

It is not necessary to read (clear) PI\_PEND to re-enable the PI interrupt function. The signals that set the PI\_PEND bits will (if unmasked) always cause the PI bit to be set in INT\_PEND1.

#### 1.7.6.1 WG Interrupt

The WG interrupt is generated by the Waveform Generator reload compare function, discussed in Section 6. This interrupt is typically used to calculate and/or reload the output and compare registers in the WFG. If the WFG registers are all that need updating, the PTS can service this interrupt with a block move of data to these registers.

#### 1.7.6.2 COMP5 Interrupt

The Compare5 interrupt is also shared through the PI. This interrupt is generated by the EPA in response to an EPA compare event. See the user's manual for information on using this function.

#### 1.7.7 THE EXTINT INTERRUPT

The EXTINT interrupt is generated by the WFG protection circuitry, described in Section 6.10. Two bits in the WG\_PROTECT register (Figure 6-14), Interrupt Type (IT) and Enable Sampling (ES) control the type of external event which will cause EXTINT. EXTINT can be caused by a transition (rising or falling edge), or by a constant level (high or low). Table 1-3 shows the combinations for these bits. The EXTINT interrupt sets the EXTINT bit in the INT\_PEND1 register, and if unmasked in the INT\_MASK1 register, takes the vector located at 203CH.

| 142.0 1 01 271 1111 1110 410 0010011011 |    |                                 |  |  |  |

|-----------------------------------------|----|---------------------------------|--|--|--|

| ES                                      | IT | EXTINT Input<br>Characteristics |  |  |  |

| 0                                       | 0  | Falling Edge Triggered          |  |  |  |

| 0                                       | 1  | Rising Edge Triggered           |  |  |  |

| 1                                       | 0  | Low Level Triggered             |  |  |  |

| 1                                       | 1  | High Level Triggered            |  |  |  |

Table 1-3. EXTINT Mode Selection

The transition modes are selected by clearing the ES bit. To be a valid transition, the signal must remain asserted for a minimum period of 2  $T_{osc}$  ( $T_{osc} = 2/F_{XTAL}$ ). The IT bit controls whether a rising edge (IT = 1) or falling edge (IT = 0) causes the interrupt.

The level modes are selected by setting the ES bit. To be a valid level, the signal must remain asserted for a minimum period of 24  $T_{\rm osc}$ . When the signal is asserted, sample circuitry monitors the input level 3 times during a 24  $T_{\rm osc}$  period. The signal must be asserted for each of the samples before it is recognized as valid. If the signal is valid, the EXTINT interrupt is generated. The IT bit controls whether a high level (IT = 1) or low level (IT = 0) input signal causes the interrupt.

The level mode is useful in noisy environments, where a noise spike might cause an unintended interrupt. Note that the same signal which generates the EXTINT also generates the output disable signal, discussed in Section 6.10.

#### 1.7.8 THE TOVF INTERRUPT

The Timer Overflow Interrupt (TOVF) is a "shared" interrupt, and signals that an interrupt has been generated by either Timer 1 (TF1) or Timer 2 overflow/underflow (TF2). When these sources generate an interrupt, the corresponding bit in the PI\_PEND register is set. If the bit is unmasked in the PI\_MASK register, the TOVF interrupt pending bit in INT\_PEND is set. Figure 1-7 illustrates the relationship between these registers.

The user interrupt routine can read the PI\_PEND register to determine what the source of the interrupt was. Note that reading PI\_PEND clears all bits. Therefore, the value of the register must be stored in a shadow register if more than one bit needs to be checked. Also note that the PI\_PEND bits cannot be set by writing to the PI\_PEND register. This register is read only, writes will have no effect.

It is not necessary to read (clear) PI\_PEND to re-enable the TOVF interrupt function. The signals that set the PI\_PEND bits will (if unmasked) always cause the PI bit to be set in INT\_PEND1.

#### 1.8 Configuring the PTS

Each PTS interrupt requires a block of data called the PTS Control Block (PTSCB). The PTSCB determines the PTS mode, the number of PTS cycles, and the address of the source and destination of data transfers. You must set up the PTSCB for each interrupt source **before** enabling the corresponding PTS interrupts.

#### 1.8.1 SETTING UP PTS CONTROL BLOCKS

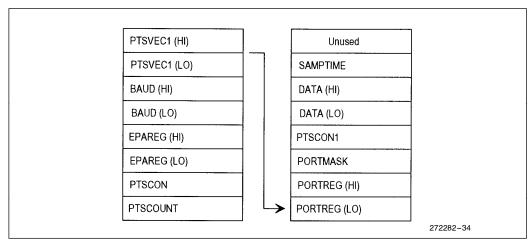

Each PTS control block (PTSCB) requires eight data bytes in register RAM. The address of the first (lowest) byte is stored in the PTS vector table in special-purpose memory (see Chapter 4). Figure 1-8 shows the PTSCB for each PTS mode. Unused PTSCB bytes can be used as RAM. The SIO mode is unique in that it links two PTSCB's together (SIO #1 and SIO #2) in order to perform its function. The PTSVEC in SIO #1 points to the base address of SIO #2.

#### NOTE:

The PTSCB must be located in register RAM, in page 00H. The location of the first byte of the PTSCB must be aligned on a quad-word boundary (an address evenly divisible by 8).

| Single<br>Transfer | Block<br>Transfer | A/D So<br>Mode |      | SIO #1       |  | SIO #2       |

|--------------------|-------------------|----------------|------|--------------|--|--------------|

| Unused             | Unused            | Unused         |      | PTSVEC1 (HI) |  | Unused       |

| Unused             | PTSBLOCK          | Unused         |      | PTSVEC1 (LO) |  | SAMPTIME     |

| PTSDST (HI)        | PTSDST (HI)       | PTSPTR2        | (HI) | BAUD (HI)    |  | DATA (HI)    |

| PTSDST (LO)        | PTSDST (LO)       | PTSPTR2        | (LO) | BAUD (LO)    |  | DATA (LO)    |

| PTSSRC (HI)        | PTSSRC (HI)       | PTSPTR1        | (HI) | EPAREG (HI)  |  | PTSCON1      |

| PTSSRC (LO)        | PTSSRC (LO)       | PTSPTR1        | (LO) | EPAREG (LO)  |  | PORTMASK     |

| PTSCON             | PTSCON            | PTSCON         |      | PTSCON       |  | PORTREG (HI) |

| PTSCOUNT           | PTSCOUNT          | PTSCOU         | NT   | PTSCOUNT     |  | PORTREG (LO) |

Figure 1-8. PTS Control Blocks

#### 1.8.1.1 PTSCOUNT Register

In Single Transfer, Block Transfer, and A/D Scan modes, the first location of each PTSCB is the PTSCOUNT register. PTSCOUNT defines the number of PTS cycles to be executed consecutively without software intervention. Since PTSCOUNT is an 8-bit value, the maximum number of cycles is 255. PTSCOUNT is decremented at the end of each PTS cycle. When PTSCOUNT reaches zero, hardware clears the corresponding PTSSEL bit and sets the PTSSRV bit, which requests the end-of-PTS interrupt.

#### 1.8.1.2 PTSCON Register

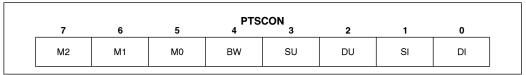

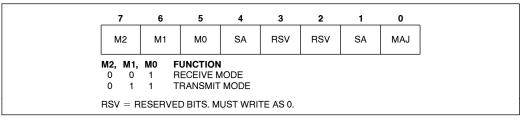

The second location of each PTSCB (except SIO #2) is the PTSCON register. The upper three bits of the PTSCON register determine the PTS mode (Table 1-4).

| Table 1 4.1 To mode delete (1 100014 Bits 0 7) |            |            |            |  |

|------------------------------------------------|------------|------------|------------|--|

| Desired PTS Mode                               | Bit 7 (M2) | Bit 6 (M1) | Bit 5 (M0) |  |

| Single Transfer                                | 1          | 0          | 0          |  |

| Block Transfer                                 | 0          | 0          | 0          |  |

| A/D Scan                                       | 1          | 1          | 0          |  |

| Serial Transmit Mode                           | 0          | 1          | 1          |  |

| Serial Receive Mode                            | 0          | 0          | 1          |  |

Table 1-4. PTS Mode Select (PTSCON Bits 5-7)

The PTS Mode determines the configuration of the remaining bits. PTSCON has one configuration for Single and Block Transfer modes and A/D Scan mode (Figure 1-9), and one for the serial I/O modes (Figure 1-11).

Figure 1-9. PTSCON Register

Table 1-5. PTSCON Bits 0-4 for Single and Block Transfer Modes

| Bit<br>Number | Bit<br>Mnemonic | Bit<br>Name                  | Description                                                                                                                                                                                                                                                          |

|---------------|-----------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | DI              | PTSDST<br>Auto-<br>Increment | Setting this bit causes the PTS destination register to increment at the end of each PTS cycle. (In Single Transfer mode, the DI and DU bits must be equal.)                                                                                                         |

| 1             | SI              | PTSSRC<br>Auto-<br>Increment | Setting this bit causes the PTS source register to increment at the end of each PTS cycle. (In Single Transfer mode, the SI and SU bits must be equal.)                                                                                                              |

| 2             | DU              | Update<br>PTSDST             | Setting this bit causes the PTSDST register to retain its final value at the end of a PTS cycle. Clearing it causes the register to revert to the value that existed at the beginning of the PTS cycle. (In Single Transfer mode, the DI and DU bits must be equal.) |

| 3             | SU              | Update<br>PTSSRC             | Setting this bit causes the PTSSRC register to retain its final value at the end of a PTS cycle. Clearing it causes the register to revert to the value that existed at the beginning of the PTS cycle. (In Single Transfer mode, the SI and SU bits must be equal.) |

| 4             | BW              | Byte/Word<br>Transfer        | Setting this bit specifies a byte transfer. Clearing it specifies a word transfer.                                                                                                                                                                                   |

Table 1-6. PTSCON Bits 0-4 for A/D Scan Mode

| Bit<br>Number | Bit<br>Mnemonic | Bit<br>Name       | Description                                                                                                                                                                                              |

|---------------|-----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | _               | _                 | Always one.                                                                                                                                                                                              |

| 1             | _               | _                 | Always one.                                                                                                                                                                                              |

| 2             | _               | _                 | Always zero.                                                                                                                                                                                             |

| 3             | SU              | Update<br>PTSPTR1 | Setting this bit causes the PTSPTR1 register to retain its final value at the end of a PTS cycle. Clearing it causes the register to revert to the value that existed at the beginning of the PTS cycle. |

| 4             | _               | _                 | Always zero.                                                                                                                                                                                             |

#### 1.8.2 SINGLE TRANSFER MODE

Single Transfer mode is typically used with the EPA, in capture mode, to move the captured time value from the SFR location to internal RAM for further processing.

In the Single Transfer mode, each PTS cycle transfers a single byte or word (selected by the BW bit in PTSCON) from one memory location to another. The PTSCOUNT register specifies the number of transfers (each transfer is one PTS cycle). The PTS moves the byte or word from the location pointed to by the source register (PTSSRC) to the location pointed to by the destination register (PTSDST).

PTSSRC and PTSDST may point to any memory location; however, they must point to an even address if word transfers are selected. Setting the auto-increment and update bits causes the PTS to increment the source (if SI and SU are set) and/or destination (if DI and DU are set) address at the end of each PTS cycle. The address increments by one if byte transfers are selected or by two if word transfers are selected. In Single Transfer mode, each pair of auto-increment and update bits (SI/SU, DI/DU) must both be either set or cleared. Programming either pair to unequal values selects an invalid mode. The source and destination can be incremented and updated independently of one another. (The SI and SU pair must be equal, and the DI and DU pair must be equal. However, the two pairs, SI/SU and DI/DU, need not be equal.)

#### 1.8.2.1 Single Transfer Mode Example

The PTSCB in Table 1.7 defines nine PTS cycles. Each cycle moves a single word from location 20H to an external memory location. The PTS transfers the first word to location 6000H. Then it increments and updates the destination address and decrements the PTSCOUNT register; it does not increment the source address. When the second cycle begins, the PTS moves a second word from location 20H to location 6002H. When PTSCOUNT equals zero, the PTS will have filled locations 6000H-600FH, and an end-of-PTS interrupt is generated.

Table 1-7. Single Transfer Mode PTSCB

| Unused                                        |

|-----------------------------------------------|

| Unused                                        |

| PTSDST (HI) = 60H                             |

| PTSDST (LO) = 00H                             |

| PTSSRC (HI) = 00H                             |

| PTSSRC (LO) = 20H                             |

| PTSCON = 85H (Mode = 100, DI & DU = 1 BW = 0) |

| PTSCOUNT = 09H                                |

#### 1.8.3 BLOCK TRANSFER MODE

In Block Transfer mode, the PTS moves a block of bytes or words (selected by the BW bit in PTSCON) from one memory location to another. The PTSBLOCK register specifies the number (from 1–32) of bytes or words in each block. The PTS moves the block of bytes or words from the location pointed to by the source register (PTSSRC) to the location pointed to by the destination register (PTSDST).

PTSSRC and PTSDST may point to any memory location; however, they must point to an even address if word transfers are selected. Setting the auto-increment bits in the PTSCON register causes the PTS to increment the source (SI set) and/or destination (DI set) address at the end of each PTS transfer. If the update bit is also set, the incremented address is saved in the PTSSRC (SU set) or PTSDST (DU set) register after each PTS cycle. Setting both the increment and update bits causes the source and/or destination address to be incremented after each cycle. The registers increment by one if byte transfers are selected or by two if word transfers are selected. The increment and update features may be selected independently (unlike in Single Transfer Mode).

In this mode, it is important to differentiate between a PTS transfer and a PTS cycle. A PTS transfer is the movement of a single byte or word from the source to the destination. A PTS cycle consists of the transfer of an entire block of bytes or words. Because a PTS cycle is uninteruptable, the Block Transfer mode can create long interrupt latency. The worst-case latency could be as high as 500 states. This worst-case latency assumes a block transfer of 32 words from one external memory location to another using an 8-bit bus with no wait states.

#### 1.8.3.1 Block Transfer Mode Example

The PTSCB in Table 1.8 defines three PTS cycles that will each transfer the bytes in memory locations 20H–24H to one of the following blocks: 6000H–6004H, 6005H–6009H, or 600AH–600EH. Each PTS cycle transfers a block of five bytes. The source and destination are incremented after each transfer, but only the destination is updated after each cycle. The first byte of each cycle is always read from location 20H.

Unused

PTSBLOCK = 05H

PTSDST (HI) = 60H

PTSDST (LO) = 00H

PTSSRC (HI) = 00H

PTSSRC (LO) = 20H

PTSCON = 17H (Mode = 000; DI, SI DU, BW = 1; SU = 0)

PTSCOUNT = 03H

Table 1-8. Block Transfer Mode PTSCB

#### 1.8.4 A/D SCAN MODE

In the A/D Scan mode, the PTS causes the A/D converter to perform multiple conversions on one or more channels and then stores the results. To use the A/D Scan mode, you must first set up a command/data table in memory (Table 1-9). The command/data table contains A/D commands that are interleaved with blank memory locations. The PTS stores the conversion results in these blank locations.

To initiate A/D Scan mode, enable the A/D Conversion Complete interrupt and assign it to the PTS, then have software start the first conversion. When the A/D finishes the first conversion and generates an A/D Conversion Complete interrupt, the PTS cycle is initiated.

During each PTS cycle, the PTS stores the results from the previous conversion and then executes the next conversion command. Since the conversion results are not stored until the next PTS cycle, the last command location should contain all zeros to prevent a final conversion from starting. Typically, the A/D commands are loaded into the table from an external ROM. Only the amount of available memory limits the table size; it can reside in internal or external RAM.

| Table 1-9. A/L | Scall Wode Col | ililialiu/Data Table |

|----------------|----------------|----------------------|

| XXX + 0AH      | A/D Result 2   |                      |

| XXX + 8H       | Unused         | A/D Command 3        |

| XXX + 6H       | A/D Result 1   |                      |

| XXX + 4H       | Unused         | A/D command 2        |

| XXX + 2H       | A/D Result 0*  |                      |

| XXX            | Unused         | A/D command 1        |

Table 1-9. A/D Scan Mode Command/Data Table

In A/D Scan mode, the PTSCOUNT specifies the total number of A/D conversion cycles. The PTSPTR1 register points to the table of conversion commands and results. Setting the UPDT bit in the PTSCON register (PTSCON.3) causes the PTSPTR1 register to retain its final value at the end of the PTS cycle. Clearing it causes the register to revert to the value that existed at the beginning of the PTS cycle. PTSPTR2 points to the AD\_RESULT register.

<sup>\*</sup>Result of the A/D conversion that initiates the PTS cycle.

#### 1.8.4.1 PTS Cycles in A/D Scan Mode

Software must start the first A/D conversion. The A/D Conversion Complete interrupt initiates the PTS cycle. The following actions occur after the PTS cycle begins:

- 1. The PTS reads the first command, stores it in a temporary location, and increments the PTSPTR1 register twice. PTSPTR1 now points to the first blank location in the command/data table (address XXX + 2).

- 2. The PTS reads the AD\_RESULT register, stores the results of the first conversion into location XXX + 2 in the command/data table, and increments the PTSPTR1 register twice. PTSPTR1 now points to XXX + 4.

- 3. The PTS loads the command from the temporary location into the AD\_COMMAND register. This starts the next A/D conversion cycle.

- 4. If UPDT (PTSCON.3) is clear, the PTSPTR1 register is reinitialized to its original value. The next cycle will use the same command and overwrite previous data. If UPDT is set, the PTS saves the new contents of PTSPTR1 and it points to the next command.

- PTSCOUNT is decremented and the CPU returns to regular program execution. When PTSCOUNT reaches zero, hardware clears the corresponding PTSSEL bit and sets the PTSSRV bit, which requests the end-of-PTS interrupt.

When the conversion started by the PTS cycle completes and the A/D generates the A/D Conversion Complete interrupt, a new PTS cycle begins. Steps 1-5 repeat.

Because the lower six bits of the AD\_RESULT register contain status information, the end-of-PTS interrupt service routine could shift the results data to the right six times to leave only the conversion results in the memory locations.

#### 1.8.4.2 A/D Scan Mode Example 1

The command/data table shown in Table 1.10 sets up a series of A/D conversions, beginning with channel 7 and ending with channel 4. Each table entry is a word (two bytes). Table 1-11 shows the corresponding PTSCB.

Software starts a conversion on Channel 7. Upon completion of the conversion, the A/D Conversion Complete interrupt initiates the first PTS cycle. Step 1 stores the Channel 6 command in a temporary location and increments PTSPTR1 to 3002H. Step 2 stores the result of the Channel 7 conversion in location 102H and increments PTSPTR1 to 3004H. Step 3 loads the Channel 6 command from the temporary location into the AD\_COMMAND register to start the next conversion. Step 4 updates PTSPTR1 (PTSPTR1 points to 3004H) and step 5 decrements PTSCOUNT to 7. The next cycle begins by storing the Channel 5 command in the temporary location. During the last cycle (PTSCOUNT = 1), the dummy command is loaded into the AD\_COMMAND register and no conversion is performed. PTSCOUNT is decremented to zero and the end-of-PTS interrupt is requested.

Table 1-10. Command/Data Table (Example 1)

| Address | Contents              |

|---------|-----------------------|

| 300EH   | AD_RESULT for ACH4    |

| 300CH   | 0000H (Dummy Command) |

| 300AH   | AD_RESULT for ACH5    |

| 3008H   | AD_COMMAND for ACH4   |

| 3006H   | AD_RESULT for ACH6    |

| 3004H   | AD_COMMAND for ACH5   |

| 3002H   | AD_RESULT for ACH7    |

| 3000H   | AD_COMMAND for ACH6   |

Table 1-11. A/D Scan Mode PTSCB (Example 1)

| Unused                              |  |

|-------------------------------------|--|

| Unused                              |  |

| PTSPTR2 (HI) = 1FH                  |  |

| PTSPTR2 (LO) = AAH                  |  |

| PTS_PTR1 (HI) = 30H                 |  |

| PTS_PTR1 (LO) = 00H                 |  |

| PTSCON = CBH (Mode = 110, UPDT = 1) |  |

| PTSCOUNT = 04H                      |  |

#### 1.8.4.3 A/D Scan Mode Example 2

Table 1-13 sets up a series of ten PTS cycles, each of which reads a single A/D channel and stores the result in a single location (3002H). The UPDT bit (PTSCON.3) is cleared so that original contents of PTSPTR1 are restored after the cycle. The command/data table is shown in Table 1-12.

Table 1-12. Command/Data Table (Example 2)

| Address | Contents            |  |  |

|---------|---------------------|--|--|

| 3002H   | ADRESULT for ACHx   |  |  |

| 3000H   | AD_COMMAND for ACHx |  |  |

Table 1-13. A/D Scan Mode PTSCB (Example 2)

| Unused                              |

|-------------------------------------|

| Unused                              |

| PTSPTR2 (HI) = 1FH                  |

| PTSPTR2 (LO) = AAH                  |

| PTSPTR1 (HI) = 30H                  |

| PTSPTR1 (LO) = 00H                  |

| PTSCON = C3H (Mode = 110, UPDT = 0) |

| PTSCOUNT = 0AH                      |

Software starts a conversion on Channel x. When the conversion is finished and the A/D Conversion Complete interrupt is generated, the first PTS cycle begins. The PTS stores the value of the AD\_RESULT register in location 3002H and then copies the conversion command from location 3000H to the AD\_COMMAND register. The CPU can process or move the conversion results data from the table before the next conversion completes and a new PTS cycle begins. When the next cycle begins, PTSPTR1 again points to 3000H. The value of the AD\_RESULT register is written to location 3002H and the command at location 3000H is re-executed.

#### 1.8.5 SERIAL I/O MODES

Since the 8XC196MC/MD has no hardware UART, the serial I/O function is implemented using special PTS modes. There are four basic serial modes of operation; several options are available within each of these modes.

The SIO mode require 2 PTSCB's to completely configure all possible options. These blocks do not need to be contiguous, but must be in register RAM and located on quad-word boundaries.

The serial modes are very versatile. The baud rate is established by an EPA channel, and up to 16 bits per character (including parity and stop bits) may be transmitted/received. In the synchronous modes, the shift clock can either be input to or output by the 8XC196MC/MD. The data and clock may be assigned to most I/O pins in port 2 or port 7. Ports 3, 4 and 5 do not support the serial I/O function.

Additional information on the PTS SIO modes can be found in the 8XC196MC User's Manual. Software examples are given in this Ap-Note, Chapters 2-5.

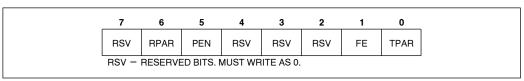

Figure 1-10. PTS SIO Control Blocks

#### 1.8.5.1 PTSCOUNT Register

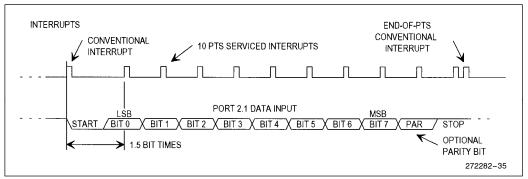

PTSCOUNT defines the number of PTS cycles to be executed consecutively without software intervention. Since PTSCOUNT is an 8-bit value, the maximum number of cycles is 256 (with setting of 0). In the SIO modes, PTSCOUNT determines how many bits will be transmitted or received. The different SIO modes have different requirements for PTSCOUNT; refer to Sections 1.8.6 and 1.8.7 for detailed information.

Like in all other PTS modes, PTSCOUNT is decremented at the end of each PTS cycle. When PTSCOUNT reaches zero, hardware clears the corresponding PTSSEL bit and sets the PTSSRV bit, which requests the end-of-PTS interrupt.