### AP-475

### APPLICATION NOTE

### Using the 8XC196NT

RICHARD N. EVANS CHRISTINE NEFFENGER APPLICATIONS ENGINEERS

January 1994

Order Number: 272315-001

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive and iCOMP trademarks has been issued to Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

### Using the 8XC196NT

| CONTENTS                                                                                 | PAGE   |

|------------------------------------------------------------------------------------------|--------|

| 1.0 INTRODUCTION                                                                         | 1      |

| 2.0 ARCHITECTURAL OVERVIEW                                                               | 1      |

| 3.0 8XC196NT NEW INSTRUCTIONS                                                            | 3      |

| 3.1 ELD/ELDB—Extended Load<br>Word/Byte                                                  | 3      |

| 3.2 EST/ESTB—Extended Store<br>Word/Byte                                                 | 4      |

| 3.3 EBR—Extended Branch                                                                  |        |

| 3.4 EBMOVI—Interruptable Extender<br>Block Move                                          | d<br>5 |

| 3.5 ECALL—Extended Subroutine<br>Call                                                    | 6      |

| 3.6 RET—24-Bit Mode Return                                                               | 6      |

| 3.7 EJMP—Extended Jump                                                                   | 6      |

| 4.0 EPORT                                                                                | 6      |

| 4.1 EPORT Gives 20-Bit External<br>Address                                               |        |

| 4.2 EPORT is Address Lines or I/O<br>Pins                                                | 6      |

| 4.3 EPORT SFRs                                                                           | 6      |

| 4.3.1 EPMODE Register                                                                    | 7      |

| 4.3.2 EPDIR Register                                                                     | 7      |

| 4.3.3 EPREG Register                                                                     |        |

| 4.3.4 EPPIN Register                                                                     | 8      |

| 4.3.5 Reset Values of EPORT<br>SFRs                                                      |        |

| 4.3.6 Accessing EPORT SFRs                                                               | 8      |

| 4.4 EPORT                                                                                | 8      |

| 5.0 MEMORY MAP                                                                           | 9      |

| 5.1 Memory Layout                                                                        |        |

| 5.2 How the EPORT Affects Memory<br>Accesses                                             |        |

| 5.2.1 The iC Compiler                                                                    | 10     |

| 5.2.2 Warning about Changing<br>Pages with EPREG when the<br>Stack is in External Memory | 10     |

| 5.3 The Different Memory Maps                                                            |        |

| 5.3.1 MODE 16                                                                            |        |

| 5.3.2 REMAP                                                                              |        |

| 5.3.3 64K Compatible Mode                                                                |        |

|                                                                                          |        |

| CONTENTS PAGE                                                                                               |

|-------------------------------------------------------------------------------------------------------------|

| 5.3.4 Example: Using the "64K<br>Compatible Mode" with<br>96 Kbytes of Data11                               |

| 5.3.5 64K Compatible Mode with<br>Page 00h Free14                                                           |

| 5.3.6 Example: Using the 64K<br>Compatible Mode with 128K of<br>External Data14                             |

| 5.3.7 24-Bit Mode with EPROM<br>Remapped15                                                                  |

| 5.3.8 Example: Using 24-Bit Mode<br>with (EP)ROM Remapped 15                                                |

| 5.3.9 24-Bit Mode 16                                                                                        |

| 5.3.10 Example: Using 24-Bit<br>Mode 16                                                                     |

| 5.4 Internal RAM 17                                                                                         |

| 5.4.1 Reading the EA Pin and<br>Redirecting Internal RAM<br>Accesses                                        |

| 5.5 Wraparound                                                                                              |

| 6.0 TIMING IMPROVEMENTS                                                                                     |

| 6.1 Signals 22                                                                                              |

| 6.2 Conditions 22                                                                                           |

| 6.3 Critical Memory Timings 22                                                                              |

| 6.4 What Can Be Done to Use Less<br>Expensive Memories and Run at<br>Maximum Speed with Zero Wait<br>States |

| 6.5 New Timing Modes 23                                                                                     |

| 6.5.1 Standard Timing (Mode 3) 24                                                                           |

| 6.5.1.1 Mode 3 Timing Specs 24                                                                              |

| 6.5.2 Standard Timing with One<br>Wait State (Mode 0)                                                       |

| 6.5.2.1 Mode 0 Timing Specs 24                                                                              |

| 6.5.3 Long READ/WRITE with<br>Advanced ALE (Mode 1)                                                         |

| 6.5.3.1 Mode 1 Timing Specs 25                                                                              |

| 6.5.4 Long READ/WRITE with<br>Advanced ALE and Early Address<br>(Mode 2)                                    |

| 6.5.4.1 Mode 2 Timing Specs 25                                                                              |

| 6.6 Given These New Timing Modes,<br>Which Memory Devices Can Be<br>Used with No Wait States?               |

### CONTENTS

| 6.7 Changes to the Bus Control |    |

|--------------------------------|----|

| Timings                        | 27 |

| 6.8 8-Bit Bus in Modes 1 and 2 | 27 |

### PAGE CONTENTS PAGE

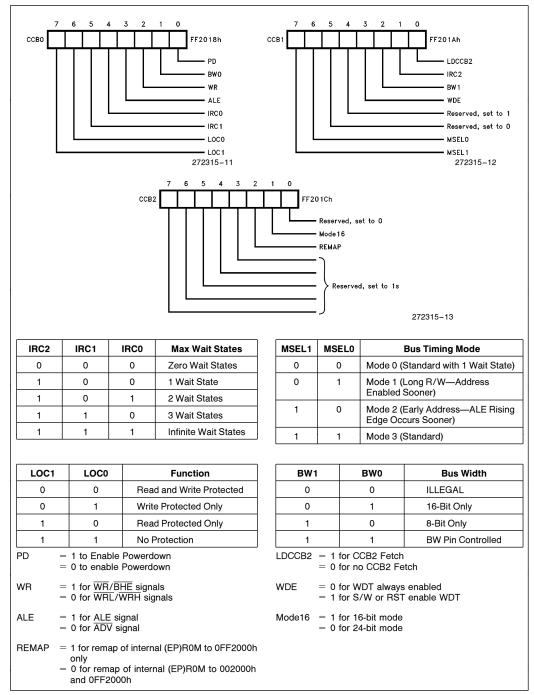

| 7.0 CHIP CONFIGURATION BYTES 33 |  |

|---------------------------------|--|

| 7.1 CCBs 33                     |  |

8.0 QUESTIONS AND ANSWERS ...... 35

#### **1.0 INTRODUCTION**

The 8XC196NT can address 1 Mbyte of linear address space which is beyond the standard MCS®-96 64 Kbyte address space. Many applications require much memory whether it be from large code sizes due to high level language compilation or from large data tables. The standard MCS-96 family member has 16 address lines which allow linear access to 64 Kbytes of address space. To accommodate a growing need for address space the 8XC196NT was designed with 20 external address lines. The 8XC196NT is an upgrade from the standard MCS-96 family member. There are many similarities and a few differences that must be noted. The same peripheral set exists on the 8XC196NT as on the 8XC196KR. The peripherals on the 8XC196NT and the 8XC196KR are more advanced than the peripherals on the 8X96BH, 8XC196KB, 8XC196KC and 8XC196KD. The instruction set is a superset of the MCS-96 family containing special extended addressing instructions. The bus controller on the 8XC196NT has

new modes which allow for slower memories to be utilized resulting in cost savings. An extended address port (EPORT) adds 4 more address lines to the external bus. The EPORT can also be used as an I/O port if the extended address lines are not needed.

#### 2.0 ARCHITECTURAL OVERVIEW

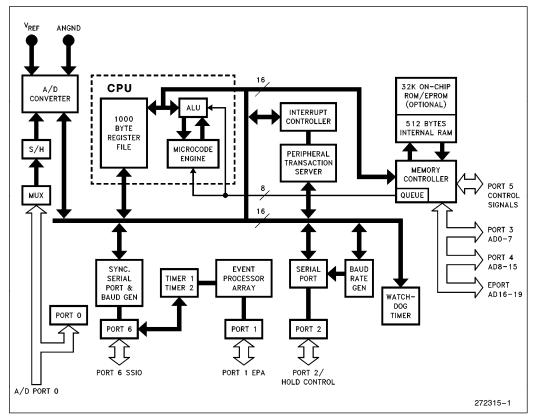

The architecture for the 8XC196NT is consistent with the previous members (see Figure 2-1). The program counter has been extended to 24 bits to accommodate the extended addressing capabilities. The ALU is tied directly to the register RAM which creates a registerregister architecture. The 8XC196NT has 1000 bytes of register RAM. Hence, one thousand accumulators (each a byte wide) are possible. This many accumulators minimizes the number of load/store operations. Notice that there are 32 Kbytes of on-chip (EP)ROM available and 512 bytes of internal RAM. The internal RAM can be used just like external RAM to execute code or hold data.

Figure 2-1. 8XC196NT Block Diagram

#### AP-475

The peripheral set on the 8XC196NT includes the following:

- Serial Port (3 asynchronous modes, 1 synchronous mode)

- SSIO (Synchronous Serial I/O Port with bi-directional clocking with two separate data and two separate clock channels)

- Slave Port

- EPA (Event Processor Array—high speed input capture and output compare) 10 channels

- PTS (Peripheral Transaction Server—microcoded interrupt service routine)

- A/D converter (4 channel 8/10 bit resolution with programmable sample and convert times)

- Two 16-bit timers Watchdog Timer

- Dedicated 15-bit Baud Rate Generator

- Extended Address Port (EPORT)

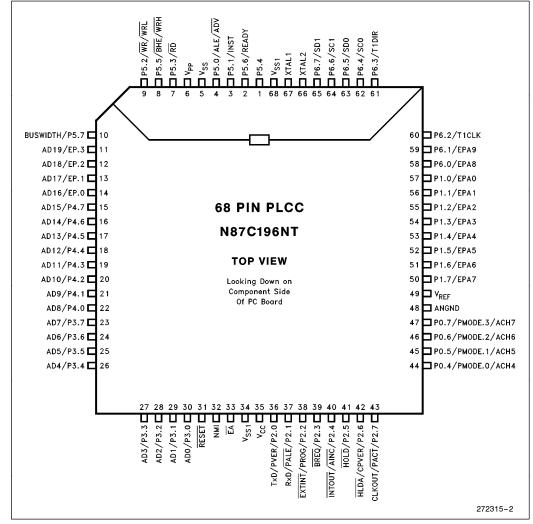

- See pin out diagram in Figure 2-2.

For more information on the peripherals consult the 8XC196NT or 8XC196KX user's guides. The next sections go into more detail on how to use the EPORT, the memory map and the bus controller improvements which allow for greater flexibility in choosing memories. Also, code examples are given where needed as well as memory interface diagrams.

Figure 2-2. 8XC196NT Pin Out Diagram

#### AP-475

#### 3.0 8XC196NT NEW INSTRUCTIONS

There are a few new instructions for accessing the 1 Mbyte address space. They are listed below and explained in detail in the following pages. When executing in 24-bit mode, instructions which push or pop the PC onto the stack will decrement or increment the stack pointer by four. These instructions include LCALL, SCALL, and RET. RET is explained in the new instruction section.

New Instructions:

EBMOVI-Interruptable Extended Block Move

EBR-Extended Branch, Indexed

ECALL-Extended Subroutine Call

EJMP-Extended Jump

ELD/ELDB—Extended Load Word/Byte, Indexed or Indirect

EST/ESTB-Extended Store Word/Byte, Indexed or Indirect

RET-24-Bit Mode Return from Subroutine

#### 3.1 ELD/ELDB—Extended Load Word/Byte

Operation:

The word/byte contents of the source—indirect, indirect auto-increment, or index addressed—are copied into the register indicated by the destination. The source is located at a 24-bit address.

Example:

rseg at 1CH

A: dsb 1

B: dsw 2

cseg at OFF2080h

ld B,#01FE6h ; load low word of B with low word of 24-bit address

ldbze B+2,#00h ; load high word of B with highest byte of 24-bit address

eldb A,[B] ; (A) <= (001FE6h), which reads EF\_PIN register</pre>

Assembly Language: DST SRC

ELD wreg, waopi

where:

wreg = a word register in the internal register file.

waopi = a word operand 24-bit indirect or indexed addressed. Even address boundary, so LSB = 0 if indirect and LSB = 1 if indirect auto-increment.

Object Code Format:

| Instruction |       |             | -> | Object code format   |

|-------------|-------|-------------|----|----------------------|

| ELD         | wreg, | -<br>[wiop] |    | [E8][wiop 0][wreg]   |

| ELD         | wreg, | [wiop]+     | -> | [E8][wiop l][wreg]   |

| ELD         | wreg, | xx[wiop]    | -> | [E9][wiop][xx][wreg] |

| ELDB        | breg, | [biop]      | -> | [EA][biop 0][breg]   |

| ELDB        | breg, | [biop]+     | -> | [EA][biop l][breg]   |

| ELDB        | breg, | xx[biop]    | -> | [EB][biop][xx][breg] |

|             |       |             |    |                      |

-> Object code format

-> [lE][biop 0][breg]

-> [1C][wiop][wreg]

EST wreg, xx[wiop] -> [1D][wiop 0][xx][wreg]

EST wreg, xx[wiop]+ -> [1D][wiop 1][xx][wreg]

ESTB breg, [biop]+ -> [lE][biop l][breg]

ESTB breg, xx[biop] -> [lF][biop][xx][breg]

#### 3.2 EST/ESTB—Extended Store Word/Byte

Operation:

The word/byte contents of the source—indirect, indirect auto-increment\*, or index addressed—are copied into the register indicated by the destination. The source is located at a 24-bit address.

Assembly Language:

SRC DST EST wreg, wiop

where:

- wreg = a word register in the internal register file

- wiop = a word operand 24-bit indirect or indexed addressed modes. Even address boundary, so LSB = 0 for indirect and LSB = 1 for indirect auto-increment.

#### Example:

| rseg at 1CH |                                                                 |

|-------------|-----------------------------------------------------------------|

| A: dsb      | 1                                                               |

| B: dsw      | 2                                                               |

| cseg at OFF | 2080h                                                           |

| 1db A,#05   | 5h ; load A with value                                          |

| 1d B,#03    | FFCh ; load low word of B with low word of extended address     |

| ldbze B+2,  | 00h ; load high word of B with highest byte of extended address |

| estb A,[B]  | ; (OOlFFCh) $\leq$ = 055h, which writes to P3_REG, a location   |

|             | ; unavailable with windowing or with 'stb' if EP_REG not        |

|             | ; set to 00h                                                    |

Object Code Format:

EST wreg, [wiop]

ESTB breg, [biop]

Instruction

#### 3.3 EBR—Extended Branch

Operation:

Assembly Language: EBR [dwreg]

where:

Execution continues at the extended address specified in the operand register.

dwreg = double word register containing 24-bit address of the branch location

Object Code Format: [E3][dwreg]

Example:

rseg at 1CH

B: dsw 2

cseg at OFF2080h

.

.

ld B,#2080h

ldbze B+2,#00h ; load B with external address for execution

ebr [B] ; load PC with 24-bit address in B (002080h)

#### 3.4 EBMOVI—Interruptable Extended Block Move

Operation:

This instruction is used to move a block of word data from one location in extended memory to another and is interruptable. The source and destination registers are calculated using the indirect auto-increment addressing modes. A long register addresses the source and destination pointers which are stored in adjacent double word registers. The number of transfers is specified in the word register. The blocks of data can reside anywhere in memory, but should not overlap.

```

Assembly Language:

BMOVI qwreg,wreg

where:

qwreg = a quad-word register

```

Object Code Format: [E4][wreg][dLreg]

Example:

```

rseg at 1CH

ptrs: dsl 2

count: dsw 1

cseg at OFF2080h

lđ

count,#1000h

lđ

ptrs,#4000h

ld

ptrs+2,#0003h

ld

ptrs+4,#3000h

ptrs+6,#0005h

ld

ebmovi ptrs,count

; moves 1000h words of data from 034000h through

;035000h to 053000h through 054000h

```

#### AP-475

#### 3.5 ECALL—Extended Subroutine call

Operation:

The contents of the program counter (the return address) are pushed onto the stack<sup>\*</sup>. Then the distance from the end of the instruction to the target label is added to the program counter, effecting the call. The offset from the end of the instruction to the call must be in the range of -8,388,608 to +8,388,607 inclusive, which is a 24-bit offset.

Assembly Language: ECALL label

Object Code Format: [F1][24-bit offset]

NOTE:

\*The PC is pushed onto the stack as 4 bytes or 32-bits.

#### 3.6 RET-24-Bit Mode Return

Operation:

The PC is popped off the stack.

Assembly Language: RET

Object Code Format: [F0]

#### NOTE:

Since 32-bits were pushed onto the stack at call of subroutine, 32-bits are popped. Therefore, **RET** in 24-bit mode will execute the following:

PC <= SP SP = SP+4

#### 3.7 EJMP—Extended Jump

Operation:

The distance from the end of this instruction to the target label is added to the program counter, effecting the jump. The operand may be any address in the entire address space.

Assembly Language: EJMP cadd

Object Code Format: [E6][24-bit displacement]

#### 4.0 EPORT

#### 4.1 EPORT Gives 20-Bit External Address

INto

The main feature of the 8XC196NT is its ability to address 1 Mbyte of external memory plus over 32 Kbytes of internal memory on the device. This is accomplished using the extended address port, which is the EPORT. The EPORT can be configured as four additional address lines. Therefore, operating the device in 24-bit mode, external memory is accessed with a **20-bit address** (pins: EP.3  $\rightarrow$  EP.0 and AD15  $\rightarrow$ AD0). The memory map in Figure 5-4 shows the address range accessible using the 20-bit external memory address. The EPORT replaces four of the A/D channels, therefore the 8XC196NT has only four remaining A/D channels. The pin diagram of the 8XC196NT 68pin PLCC is shown in Figure 2-2.

#### 4.2 EPORT is Address Lines or I/O Pins

The EPORT can be used as either additional **address lines or I/O pins**. In addition, the port can function as any combination of additional address lines or I/O pins. For example, two of the EPORT pins can be used as address lines for two additional address bits and the other lines for two additional I/O pins. The user must be aware that this configuration as address or I/O can be changed during normal execution using the EPORT control registers. Therefore, caution should be used when changing the control registers of the EPORT.

#### 4.3 EPORT SFRs

The function, direction, and data of the EPORT are controlled by four special function registers (SFRs) which are: EP\_MODE (1FE1h), EP\_DIR (1FE3h), EP\_REG (1FE5h), and EP\_PIN (1FE7h). Table 4-1 shows the SFR control of the pins.

| EPMode | EPDir | EPReg | Pull-Up | Pull-Down | Pin<br>Function         |  |

|--------|-------|-------|---------|-----------|-------------------------|--|

| x      | 0     | 0     | Off     | On        | Output 0                |  |

| x      | 0     | 1     | On      | Off       | Output 1                |  |

| x      | 1     | 0     | Off     | On        | Open-Drain 0            |  |

| x      | 1     | 1     | Off     | Off       | Open-Drain 1<br>(Input) |  |

#### Table 4-1. EPORT SFRs Control of EPORT Pins

#### 4.3.1 EP\_\_MODE REGISTER

The EP\_MODE register determines the function of the EPORT pins. This register is written as a byte. Each bit of the EP\_MODE indicates whether the pin will be a I/O port pin (EP\_MODE.x = 0) or an address line pin (EP\_MODE.x = 1).

#### 4.3.2 EP\_\_DIR REGISTER

The **EP\_DIR** register indicates whether the pin will be an input or open-drain output (EP\_DIR.x = 1) or a complementary output (EP\_DIR.x = 0). This register is written as a byte.

#### 4.3.3 EP\_\_REG REGISTER

The EP\_\_REG register can be used in two different ways. If the pin is configured as an I/O pin, the EP\_\_REG is written with the data to be placed on the pin. If the pin is configured as an address line, the EP\_REG will supply the extended address on the EPORT when a 16-bit instruction is executed in 24-bit mode. It should be noted that, although the EP\_REG is an 8-bit register, only the lower 4-bits can place data onto the pins while all 8-bits can place an extended address onto the internal extended address bus. This register is written as a byte. If EP\_MODE has configured the pins as standard I/O, the value written to the EP\_REG will appear immediately on the pins.

For example see code 4-1, if the contents of the EP\_REG = 0FFh and a 16-bit instruction is used, the 16-bit address is concatenated to the contents of the EP\_REG to form the 24-bit address.

But extended address instructions will drive the extended address specified in the instruction and the EPORT pins will hold these values throughout the bus cycle.

Ax EQU 1Ch

STB Ax,1FFEh ; if EP\_REG = OFFh (reset value of register) and device in 24-bit mode

; OFF1FFEh <= contents of 1Ch</pre>

#### AP-475

#### 4.3.4 EP\_\_PIN REGISTER

The **EP\_\_PIN register** contains the data that is currently on the port pins. This register is read as a byte.

When the EPORT SFRS are to be used as address lines, they should be initialized in the following order:

- 1. Write to the EP\_\_REG

- since output address line, write the expected value.

- 2. Write to the EP\_DIR

- 0 for complementary output (without external pull-up)

- 1 for open-drain output.

- 3. Write to the EP\_MODE (write FFh since EPORT used for address lines).

#### 4.3.5 RESET VALUES OF EPORT SFRs

The **EPORT registers reset** to the following values: **EP\_MODE** = 0FFh, **EP\_DIR** = 0FFh, **EP\_REG** = 0FFh, **EP\_PIN** = xxh, and the EPORT pins are tri-stated after reset and are weakly pulled high during reset. Also, during the CCB fetch, the EPORT is forced to 0FFh since the CCBs are located in 0FF20xx.

#### 4.3.6 ACCESSING EPORT SFRs

Changing the values of the EPORT SFRs is not possible using the windowing feature of the MCS-96 devices.

### intel

The EPORT, Ports 3, 4, and 5, and the Slave Port SFRs, which are located in the 1FE0h-1FFFh range, are only accessed using 24-bit instructions. All the other SFR registers, which are located in the 1F00h-1FDF range, can be addressed using 8-bit addressing and the windowing feature.

#### 4.4 EPORT

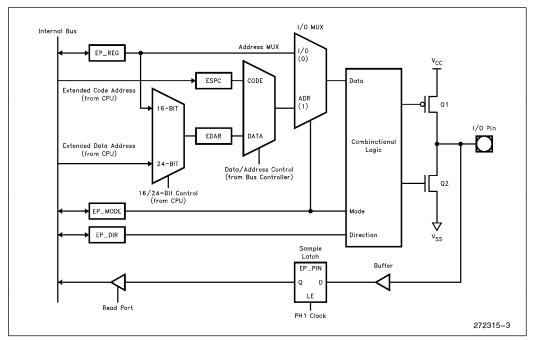

A block diagram of the EPORT is shown in Figure 4-1. The extended address either accesses data using the contents of the extended data address register (EDAR) or executes code using the address in the extended slave program counter (ESPC). If the EP\_MODE and EP\_DIR registers are configured for the addressing function and code is to be executed or data retrieved from an extended address, this extended address will be placed onto the EPORT pins. If a 16-bit instruction is executed and the device is in 24-bit mode, the contents of the EP\_\_REG will determine the highest byte of the extended address. Therefore, the contents of the EP\_\_REG should contain the correct extended address for the registers in the 16-bit instruction. If the device is in 16-bit mode and the port is configured for the addressing function, the EPORT pins will default to 0Fh. If the EP\_\_MODE and the EP\_\_DIR registers are configured for the I/O function, the contents of the EP\_REG register is placed on the EPORT pins and the contents of the EP\_PIN register is updated to the current value on the pins.

Figure 4-1. EPORT Block Diagram

#### 5.0 MEMORY MAP

#### 5.1 Memory Layout

The memory addressing capability of the 8XC196NT is 1 Mbyte of linear address space. Two bits in the chip configuration bytes configure the memory map four different ways. It is conceptually convenient to think of the address space as sixteen 64-Kbyte pages of address space (see Figure 5-5). The lower 8 Kbyte (in page 00h) is specific purpose memory. The specific purpose memory contains the CPU SFRs, the register file, 512 bytes of internal RAM and the peripheral SFRs. The upper 64 Kbyte (page FFh) is where the internal (EP)ROM is located. After RESET, the CCBs are fetched from FF2018h, FF201Ah and FF201CH. Then the program counter is set to FF2080h where execution begins. Like the previous MCS-96 devices, if  $\overline{EA}$  is tied low accesses to locations FF2000h-FF9FFFh go external and access to the internal (EP)ROM is not available. The 512 bytes of internal RAM are mapped to both pages FFh and 00h in locations FF0400h-FF05FFh (and 000400h-0005FFh). In all memory configurations the CPU SFRs (0000h-0017h), peripheral SFRs (1F00h-1FDFh) and Register RAM (0018h-03FFh) are mapped to all pages. Hence, 16-bit loads/stores can be used to access them from any page. When referencing these locations (except page 00h) with extended loads/ stores memory access goes external. Note however that the "memory mapped" peripheral SFRs (1FE0h-1FFFh) are only mapped in page 00h (this includes P3, P4, P5, EPORT and the Slave Port; see Figure 5-5, General Memory Map of the 8XC196NT).

#### 5.2 How the EPORT Affects Memory Accesses

The standard 16-bit address/data bus of the MCS-96 family is extended by the extended addressing port (EPORT). The EPORT is 8 bits wide, however only four bits are bonded out to make the extra four address lines. The EPORT can be used for I/O as discussed in the previous EPORT section of this application note.

Understanding how the EPORT is loaded is important. The EPORT block diagram is shown in Figure 4-1. First, the extended data address register (EDAR) is 8 bits wide and concatenated with the 16-bit data address register (DAR) to make a 24-bit data address register. Notice in the EPORT block diagram that the EDAR is loaded from either the EP\_REG or the CPU data address bus. When using 16-bit instructions (LD, ST), EP\_\_REG is the source for the EDAR. When using the extended addressing instructions (ELD, EST) the CPU data address bus is the source. When using the 16-bit addressing instructions, the 1 Mbyte of memory can be viewed as sixteen 64 Kbyte memory sections. When it is desired to use the 16-bit addressing instructions on a particular page, use the extended store instruction to initialize EP\_\_REG to that page (see Code 5-1).

The code in Code 5-1 changes the EPORT to 23h. So, when 16-bit instructions are used such as LD, ST, CALL, and JMPs they all refer to the 64 Kbytes of memory in page 23h.

Now suppose that instead of the previous code example, the code in Code 5-2 had been used to change the EPORT.

|          |           |                         | Code 5-1. Initializing the EPORT                                                                       |

|----------|-----------|-------------------------|--------------------------------------------------------------------------------------------------------|

|          | -         | age,#23h<br>page,EP_REG | ;initialize so 16-bit instructions will access page 23h<br>;use extended store to write to SFR 001fe5h |

| EP_REG   | equ       | lfe5h                   |                                                                                                        |

| •******* | * * * * * | Initializing            | the EPORT ***********                                                                                  |

EP\_REG equ lfe5h ldb page,#23h ;initialize so 16-bit instructions will access page 23h stb page EP\_REG ;use 16-bit store to write to SFR xxlfe5h

Code 5-2. Erroneously Initializing the EPORT

If the code in Code 5-2 is executed, where will the register "page" be stored? Refer to the 8XC196NT general memory map (Figure 5-5) and look at locations 001FE0h-001FFFh. These SFRs are ONLY mapped to page 00h. So in the code (Code 5-2) it might not be known what value the EP\_\_REG contained before the "stb" is executed. If the EP\_\_REG contained a "01h", the "page" register would have been stored in location "011FE5h" which is external memory. Therefore, when accessing a peripheral SFR in locations 001FE0h-001FFFh, use the extended store instruction.

It is important to note that the 8XC196NT has 20 address lines. The EPORT register is an 8-bit register. Future devices may bond out the upper four bits of the EPORT register to make a total of 24 address lines. Since internally the (EP)ROM is located in page FFh, you must assemble your (EP)ROM code starting at location FF2080h (where execution begins after reset).

It is a good rule of thumb to set the EP\_REG (when the EPORT is configured for address) to 00h and leave it alone. Hence, all 16-bit loads and stores thereafter will occur in page 00h. Changing the page via EP\_REG should be done with attentiveness.

#### 5.2.1 THE IC COMPILER

The iC compiler assumes that the current page is 00h. So, to remain compatible with the iC compiler, it is recommended to keep the page (via EP\_REG) set to 00h.

#### 5.2.2. WARNING ABOUT CHANGING PAGES WITH EP\_REG WHEN THE STACK IS IN EXTERNAL MEMORY

If it is desired to use non-extended instructions such as LD, ST, etc. in any page, then the EP\_\_REG can be loaded with the appropriate page value and non-extended instructions will operate within that page. This also applies to stack operations. For example, lets say you set the stack pointer to 0800H in page 00H (external memory). Then you change to page 01H by loading EP\_\_REG with 01H. Now, any stack operation such as PUSH, POP, CALL, ECALL will use the stack pointer in page 01H. So the new stack location will be 010800H. Therefore, if you enter a subroutine while in page 00H, then once in the subroutine you change the EP\_\_REG to any other value and then return from the

subroutine, you will return to some unknown location. This is because the stack pointer is now operating in a page other than 00H. Remember the following three rules when coding and when EPORT is configured as address.

- 1. You must pay careful attention when changing EP\_\_REG when the stack is located in external memory.

- 2. Before doing any stack operation, make sure EP\_\_REG is loaded with the same page as the stack is in.

- 3. If the stack is in register RAM then there is no problem since register RAM is mapped to all pages.

#### 5.3 The Different Memory Maps

There are many possible memory map configurations with the 8XC196NT (see Figures 5-6 through 5-9). Two bits in chip configuration byte 2 (CCB2) control the memory map configurations and the number of EPORT lines decoded. These bits are named MODE16 (CCB2.1) and REMAP (CCB2.2). First, these two configuration bits are discussed, then the memory map configurations are explained.

#### 5.3.1 MODE 16

When MODE16 is set to a 1 the extended slave program counter (ESPC) is forced to FFh (see the EPORT block diagram Figure 4-1). The extended slave program counter is also 8 bits wide and is concatenated with the 16-bit program counter (PC) to create a 24-bit wide program counter. The extended program counter can be thought of as holding the page location value of the currently executing code. Hence, code fetches are limited to the 64 Kbyte region in page FFh when MODE16 is set to a 1. In this mode extended branching instructions (EBR, EJMP, ECALL) do not work and must not be used.

If MODE16 is set to a 0, then 24-bit mode is entered (see Figures 5-8 and 5-9). Now the extended program counter can be any page value. A simple extended jump instruction across pages changes the extended program counter value to the destination page. For example, if code is executing out of internal (EP)ROM in page FFh, the code can branch to external memory location 003000h by the following instruction (see Code 5-3):

#### FF2090: ld temp,#12h ;some code executing in page FFh st temp,port1 ebr 003000h ;24 bit instruction jump to external location ;003000h (page 00h) . . . . . . . . . . . . . . .

Code 5-3. Using the Extended Branching Instruction

#### 5.3.2 REMAP

int

The REMAP bit, when set to a 1, maps the internal (EP)ROM to both pages 00h and FFh. See Figures 5-6 and 5-7 for the memory maps with REMAP = 1. The disadvantage of having the (EP)ROM mapped in both pages 00h and FFh is that a 32 Kbyte piece of page 00h is used. However, this may be useful if data tables are stored in (EP)ROM. When the REMAP bit is set to a 0, the internal (EP)ROM is only mapped to page FFh. But, if executing externally (EA low) the REMAP bit is a don't care. Hence, the REMAP bit is ONLY effective when  $\overline{EA}$  is high.

#### 5.3.3 64K COMPATIBLE MODE

Now that the two CCB2 bits MODE16 and REMAP have been defined, we can discuss the different memory configurations mentioned earlier. The first configuration is called 64K compatible mode and its memory map is pictured in Figure 5-6. This mode makes the 8XC196NT completely compatible with the 8XC196KR (EP\_REG should be loaded with 00h if complete compatibility is desired). In this mode, MODE16 is set to a 1 so the program counter is limited to a 64K address space and the REMAP bit is set to a 1 so the (EP)ROM is mapped in both page FFh and page 00h. A program written for a 64K MCS-96 device such as the 8XC196KR can be ported over to the 8XC196NT easily. The lower 64 Kbytes of memory looks similar to the 64K MCS-96 devices. If desired, the EPORT lines can be configured as address allowing access to 1 Mbyte of data. Setting the EP\_REG to a page value allows use of the 16-bit addressing instructions (i.e. LD, ST) in any page 01h through 0Eh.

#### 5.3.4 EXAMPLE: USING THE "64K COMPATIBLE MODE" WITH 96 KBYTES OF DATA

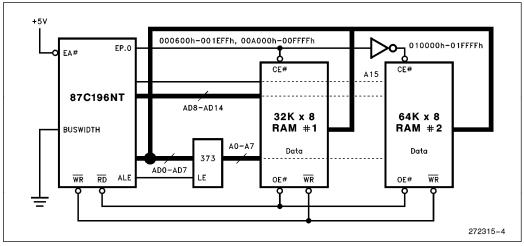

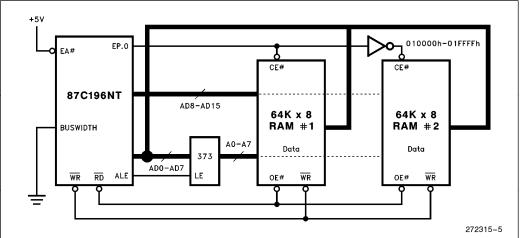

Figure 5-1 shows the 87C196NT running from internal (EP)ROM in 64K compatible mode. External data accesses are allowed using extended addressing instructions. The first 32 Kbyte RAM is mapped to the locations in page 00h that are not mapped for a specific purpose (see general memory map Figure 5-5). The general purpose spaces in page 00h amount to 32 Kbytes of memory. The 64 Kbyte RAM is mapped to page 01h. The 16-bit instructions (LD, ST) access RAM #1 (if the EP\_REG was set to 00h) and the extended instructions access both RAMs. The 16-bit instructions can access RAM #2 if the EP\_REG is loaded with 01h.

11

Figure 5-1. 64K Compatible Mode with 96 Kbytes of External Data Space

The code below applies to Figure 5-1 above. There are two subroutines (A and B). In subroutine A (see Code 5-4) page 01h is accessed using 16-bit stores. However, first the EP\_\_REG has to be initialized to page 01h. In addition the subroutine has to restore the page value to EP\_\_REG upon exiting the subroutine. So there is some overhead involved with using 16-bit loads/stores in different pages. Although if many data accesses are done in subroutine A then 16-bit loads/stores would be advantageous since they are faster. The extended loads/ stores require an extra bus cycle since the internal bus is 16-bits wide.

In subroutine B (see Code 5-5) the extended instructions are used. Notice the overhead from subroutine A has been eliminated. Subroutine B takes less memory space and is more "readable" since fewer instructions are needed. If time is not critical and subroutine B is not called often to do data accesses then it would be justifiable to use extended instructions. Only in time critical applications where many loads and stores are done would it be advantageous to use 16-bit non-extended instructions.

| EP_REG<br>temp:<br>page:<br>current_p<br>result: | ;* Accessing data in page<br>equ 1FE5h<br>rseg at 1ch<br>dsw 1<br>dsb 1<br>page: dsb 1<br>dsw 1                                                     | Olh using 16-bit instructions                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | cseg at OFF2080h<br>•<br>•                                                                                                                          | ;Some code                                                                                                                                                                                                                                                                                                                                                    |

| SubA:                                            | pusha<br>eldb current_page,EP_REG<br>ldb page,#Olh<br>est page,EP_REG<br>ld temp,#1234h<br>st temp,600h<br>add result,temp,#4000h<br>st result,602h | <pre>;save flags, disable interrupts<br/>;save the current setting of the<br/>;page<br/>;all 16-bit accesses go to page Olh<br/>;initialize EP_REG for data access<br/>;in page Olh<br/>;value in "temp" is stored in<br/>;location OlO600h<br/>;do something with registers<br/>;store result in Ol0602h<br/>;more ld/st instructions in page<br/>;Olh</pre> |

| done :                                           | •<br>•<br>•<br>• estb current_page,EP_REG<br>popa<br>ret<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                         | ;restore page value for calling<br>;program<br>;restore flags and interrupts<br>;The rest of the code                                                                                                                                                                                                                                                         |

|                                                  | end                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                               |

Code 5-4: Accessing Page 01h in "64K Compatible Mode" Using 16-Bit instructions

| EP_REG<br>temp:<br>result: | equ 1FE5h<br>rseg at 1ch<br>dsw 1 | Olh using extended instructions                    |

|----------------------------|-----------------------------------|----------------------------------------------------|

| 1054100                    | cseg at OFF2080h                  |                                                    |

|                            | •                                 | ;Somecode                                          |

|                            |                                   |                                                    |

| SubB:                      | ,<br>pusha<br>ld temp,#1234h      | ;save flags, disable interrupts                    |

|                            | est temp,010600h                  | value in "temp" is stored in;<br>location 010600h; |

|                            | add result,temp,#4000h            | do something with registers                        |

|                            | est result, 010602h               | store result in 010602h                            |

|                            | •                                 | ;more eld/est instructions                         |

|                            | •                                 |                                                    |

|                            | •                                 |                                                    |

|                            | popa                              | ;restore flags and interrupts                      |

|                            | ret                               |                                                    |

|                            | •                                 | ;The rest of the code                              |

|                            | •                                 |                                                    |

| done:                      | •<br>brdone                       |                                                    |

|                            | end                               |                                                    |

|                            | ona                               |                                                    |

Code 5-5: Accessing Page 01h in "64K Compatible Mode" Using Extended Instructions

### 5.3.5 64K COMPATIBLE MODE WITH PAGE 00h FREE

The next memory map is pictured in Figure 5-7. This is the same as the previous mode except that the REMAP bit is set to 0. The program counter is still forced to page FFh since MODE16 = 1. So any jumps beyond the page will stay within page FFh. Page 00h is now available with the exception of some of the lower memory (see the general memory map Figure 5-5). This mode can be used for a program that was written for a 64 Kbyte MCS-96 device, which needs more memory for data.

#### 5.3.6 EXAMPLE: USING THE 64K COMPATIBLE MODE WITH 128K OF EXTERNAL DATA

Since page 00h is free to use (except for SFRs, etc.), this next memory configuration takes advantage of page 00h in 64K compatible mode (see Figure 5-2). The program counter is limited to 64 Kbyte. But, the (EP)ROM is only mapped in page FFh and the 32 Kbyte memory space in page 00h is now free. This allows use of a 64 Kbyte RAM instead of the 32 Kbyte RAM shown in Figure 5-1. Hence, there is a total of 128 Kbytes of external data available to access when using only one EPORT address line.

Figure 5-2. 64K Compatible Mode with 128 Kbytes of External Data

#### 5.3.7 24-BIT MODE WITH (EP)ROM REMAPPED

Figure 5-8 shows the third memory map. Here the (EP)ROM is remapped to page 00h as well as page FFh (REMAP = 1) but the program counter is 24 bits wide (MODE16 = 0). Hence, code can be executed from anywhere in the memory space. Remember that 32 Kbytes of memory space in page 00h are dedicated to the internal (EP)ROM which would typically be used to store look-up tables or constants. The ELD/EST instructions work in all modes and always allow access to 1 Mbyte of data.

### 5.3.8 EXAMPLE: USING 24-BIT MODE WITH (EP)ROM REMAPPED

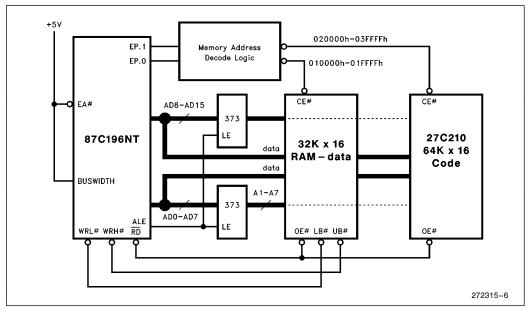

The third memory configuration is extended addressing with the EPROM remapped (Figure 5-3). In this configuration, MODE 16 = 0 so the program counter is 24 bits wide. This memory configuration could be used when a program was written for the 87C196KR but requires more memory space for code. Notice in Figure 5-3 that there are three pages of external memory used. The RAM (page 01h) is used for external data storage. The external EPROM (pages 02h and 03h) is used for 128 Kbytes of code. So in the example below there are 160 Kbytes of code space (32 Kbytes internal EPROM + 128 Kbytes external EPROM) and 64 Kbytes of data space. Note this time a 16-bit buswidth was used.

Figure 5-3. Extended Addressing with 64 Kbytes of External EPROM and 32 Kbytes of External RAM (16-Bit Buswidth)

#### 5.3.9 24-BIT MODE

The 24-bit mode is the most liberal of the memory map configurations (see Figure 5-9). The program counter is 24 bits wide and the internal (EP)ROM is only mapped to page FFh. In this mode, code and data can be accessed almost anywhere in memory.

#### 5.3.10 EXAMPLE: USING 24-BIT MODE

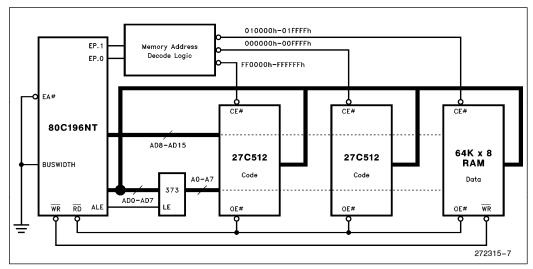

Finally, the normal extended addressing mode is shown in Figure 5-4. Here we are in 24-bit mode and the REMAP bit is a don't care since all code accesses go external. Code begins execution in page FFh. The first 64 Kbyte EPROM is used for page Oh. The 64 Kbyte RAM can be used for data storage; in addition, code can be executed from the RAM. Only two of the EPORT pins need to be decoded. If more memory is needed, then it is easy to decode the additional EPORT pins.

Figure 5-4. Normal Extended Addressing with 128 Kbytes of Code, 64 Kbytes of External Data

#### 5.4 Internal RAM

The 8XC196NT has 512 bytes of internal RAM. This RAM is mapped in both pages FFh and 00h (see Figure 5-5: General Memory Map). The internal RAM is like external RAM that has been brought inside the chip. Hence, the internal RAM can be used to execute code or store data. To access the internal RAM as data, only indexed or indirect addressing can be used. Code can be placed in internal RAM in many ways. For example, if a board executes different code each time it powers up then the boot code can be downloaded via the serial port to the internal RAM.

#### 5.4.1 READING THE EA PIN AND REDIRECTING INTERNAL RAM ACCESSES

It is possible to read the logic level on the  $\overline{EA}$  pin via the internal RAM register (IRAM\_REG). The format of the IRAM\_REG (1FE0h) is shown below:

| 7       | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|---|---|---|---|---|---|

| EA_STAT | IRAM | 0 | 0 | 0 | 0 | 0 | 0 |

**EA\_STAT:** This bit is the complement of the logic level on the  $\overrightarrow{EA}$  pin.

- = 0 means  $\overline{EA}$  = 1 and code accesses in the range FF2000h-FF9FFFh are directed to internal EPROM or ROM.

- = 1 means  $\overline{EA}$  = 0 and code accesses in the range FF2000h-FF9FFFh are directed to external memory.

**IRAM:** direct the internal RAM accesses to external memory

- = 0 means all internal RAM accesses from 400h-5FFh go INTERNAL

- = 1 means all internal RAM accesses from 400h-5FFh go EXTERNAL

#### Bits 5–0: reserved and should be set to 0

The IRAM\_REG is useful when in the design stage and the internal RAM code must be interrogated with a logic analyzer. This can't be accomplished unless all internal RAM accesses are directed to external memory where a logic analyzer can be hooked up. The following initialization code (Code 5-6) can be placed at the beginning of your program to check for internal execution or external execution and configure internal RAM accesses accordingly:

```

IRAM_REG equ 1FE0h

rseg at 1Ch

temp: dsb 1

cseg at OFF2080h

eldb temp,IRAM_REG[0] ;put complement of EA# pin in bit 7 of temp

shrb temp,#1 ;put complement of EA# in bit 6 of temp

estb temp,IRAM_REG[0] ;Allow internal RAM accesses to go either

;INTERNAL(IRAM_REG.6=0) or EXTERNAL

;(IRAMREG.6=1)

```

Code 5-6: Changing Access of Internal RAM with the IRAM\_REG

#### 5.5 Wraparound

Given the memory configuration of Figure 5-2 suppose the following instruction is executed (see code 5-7):

eld temp, 023000h[0]

Code 5-7: An Example of Wraparound

Since EP.1 is not decoded the 02h part of the address is ignored and "temp" gets loaded with the value at location 003000h. Wraparound occurs when referencing a memory location that requires greater than 20 address lines (if all four EPORT lines are used) since internally, extended addresses are 24 bits wide. There is no negative effect of wraparound, just keep it in mind when coding.

| FFFFF                      |                                                |  |

|----------------------------|------------------------------------------------|--|

|                            | External Memory                                |  |

|                            |                                                |  |

| FFA000                     |                                                |  |

| FF9FFF                     | Internal (EP)ROM or External Memory            |  |

| FF2000                     |                                                |  |

| FF1FFF                     |                                                |  |

| FF0600                     | External Memory                                |  |

| FF05FF                     |                                                |  |

| FF0400                     | Internal RAM (mapped to 000400 to 0005FF also) |  |

| FF03FF                     |                                                |  |

| FF0100                     | External Memory                                |  |

| FF00FF                     |                                                |  |

| FFUUFF                     | Reserved for ICE                               |  |

| FF0000                     |                                                |  |

| FEFFFF                     |                                                |  |

|                            | 896K of External Memory                        |  |

| 010000                     |                                                |  |

| 00FFFF                     |                                                |  |

| 00A000                     | External Memory                                |  |

| 009FFF                     | External Memory or Internal (EP)ROM            |  |

| 002000                     | (depends on remap bit)                         |  |

| 001FFF                     | Peripheral Special Function Registers          |  |

| 001FE0                     |                                                |  |

| 001FDF<br>001F00           | Peripheral Special Function Registers*         |  |

| 001EFF<br>000600           | External Memory                                |  |

|                            |                                                |  |

| 0003FF                     | Internal RAM (mapped to FF0400 to FF05FF also) |  |

| 0003FF                     | Register RAM*                                  |  |

|                            |                                                |  |

| 000017                     | CPU Special Function Registers*                |  |

| 0003FF<br>000018<br>000017 | Register RAM*                                  |  |

NOTES: Code accesses to locations 00000h to 003FFFh go external. \*Accessible in every page using 16-bit addressing (LD, ST). External memory in every page (except 00h) when using extend-ed addressing instructions.

#### Figure 5-5. General Memory Map of the 8XC196NT

| FFFFF  | <ul> <li>External code and data</li> <li>32K Internal (EP)ROM</li> <li>512 Bytes of internal RAM (mapped from page 00h)</li> </ul> |

|--------|------------------------------------------------------------------------------------------------------------------------------------|

| FF0000 | • 312 Bytes of Internal RAM (mapped from page oon)                                                                                 |

| FEFFFF | • External data ONLY                                                                                                               |

|        |                                                                                                                                    |

| 010000 |                                               |

|--------|-----------------------------------------------|

| 00FFFF | • External data                               |

|        | <ul> <li>Remapped internal (EP)ROM</li> </ul> |

|        | <ul> <li>512 Bytes of internal RAM</li> </ul> |

|        | • SFRs                                        |

| 000000 | Register File                                 |

Figure 5-6. Memory Map: 64K Compatible Mode

MODE 16 = 1 program counter limited to 64K; no limit to data access

$\label{eq:REMAP} REMAP = 1 \quad \text{internal (EP)ROM mapped in both pages 00h and FFh}$

| FFFFF  | <ul> <li>External code and data</li> <li>32K Internal (EP)ROM</li> <li>512 Bytes of internal RAM (mapped from page 00h)</li> </ul> |

|--------|------------------------------------------------------------------------------------------------------------------------------------|

| FF0000 |                                                                                                                                    |

| FEFFFF | • External data ONLY                                                                                                               |

| 010000 |                                                                                                                                    |

| 00FFFF | <ul> <li>External data</li> <li>512 Bytes of internal RAM</li> <li>SFRs</li> <li>Register File</li> </ul>                          |

| 000000 |                                                                                                                                    |

Figure 5-7. Memory Map: 64K Compatible Mode with Page 00h Available

MODE 16 = 1 program counter limited to 64K; no limit to data access

**REMAP** $= 0 \quad internal (EP)ROM mapped in page FFh ONLY$

$\begin{array}{c} \textbf{NOTES:}\\ \textbf{When } \overline{\underline{EA}} \text{ is high accesses from FF2000h to FF9FFFh go INTERNAL}\\ \textbf{When } \overline{EA} \text{ is low accesses from FF2000h to FF9FFFh go EXTERNAL} \end{array}$

|        | -                                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------|

| FFFFF  | <ul> <li>External code and data</li> <li>32K Internal (EP)ROM</li> <li>512 Bytes of internal RAM (mapped from page 00h)</li> </ul> |

| FF0000 |                                                                                                                                    |

| FEFFFF | • External code and data                                                                                                           |

| 010000 |                                                                                                                                    |

| 00FFFF | <ul> <li>External code and data</li> <li>Remapped internal (EP)ROM</li> <li>512 Bytes of internal RAM</li> <li>SFRs</li> </ul>     |

| 000000 | Register File                                                                                                                      |

Figure 5-8. Memory Map: 24-Bit Mode with (EP)ROM Remapped

MODE 16 = 0 program counter is 24 bits wide; no limit to data access

$\label{eq:REMAP} REMAP = 1 \quad \text{internal (EP)ROM mapped in both pages 00h and FFh}$

| FFFFF  | <ul> <li>External code and data</li> <li>32K Internal (EP)ROM</li> <li>512 Bytes of internal RAM (mapped from page 00h)</li> </ul> |

|--------|------------------------------------------------------------------------------------------------------------------------------------|

| FF0000 |                                                                                                                                    |

| FEFFFF | • External code and data                                                                                                           |

| 010000 |                                                                                                                                    |

| 00FFFF | <ul> <li>External code and data</li> <li>512 Bytes of internal RAM</li> <li>SFRs</li> <li>Register File</li> </ul>                 |

| 000000 |                                                                                                                                    |

#### Figure 5-9. Memory Map: 24-Bit Mode

MODE 16 = 0 program counter is 24 bits wide; no limit to data access REMAP = 0 internal (EP)ROM mapped in page FFh ONLY

NOTES:

When  $\overline{EA}$  is high accesses from FF2000h to FF9FFFh go INTERNAL When  $\overline{EA}$  is low accesses from FF2000h to FF9FFFh go EXTERNAL

#### AP-475

#### 6.0 TIMING IMPROVEMENTS

The 8XC196NT has an enhanced bus controller. The timing improvements as a result of the enhanced bus controller allow the microcontroller to run with no wait states using slower and less expensive memories on the external bus. This section discusses the improvements to the bus controller that allows this flexibility.

#### 6.1 Signals

First, an explanation of the A.C. timing symbols is necessary. Consult the chart below when studying timing diagrams:

#### Timing Name: T<sub>WXYZ</sub>

The signals are W and Y.

The conditions are X and Z.

- A address

- B bus control signals ( $\overline{BHE}$ , INST)

- $BR \overline{BREQ}$  (bus request)

- C CLKOUT

- D data in

- G buswidth

#### $H - \overline{HOLD}$

$HA - \overline{HLDA}$  (hold acknowledge)

intel

- $L ALE / \overline{ADV}$

- Q data out

- $R \overline{RD}$  (read)

- W  $-\overline{WR}/\overline{WRH}/\overline{WRL}$

- X XTAL

- Y READY

#### 6.2 Conditions

- H high

- L low

- V valid X — no longer valid

- Z floating

- 6.3 Critical Memory Timings

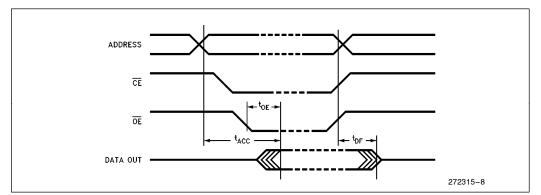

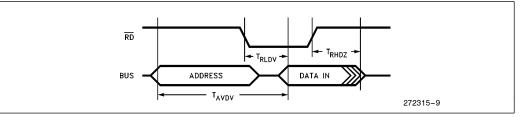

Before discussing the value of the improved bus controller timings, it is necessary to explain the critical memory device timings. The diagram (see Figure 6-1) below illustrates the important memory device READ timing relationships.

Figure 6-1. Critical Memory Device Timings

- $\begin{array}{c} t_{ACC} & -\!\!\!\!\!\!\!- \mbox{ delay time from when the address is valid} \\ & to when the data output from the memory \\ & device is valid. \end{array}$

- t<sub>OE</sub> delay time from when the output enable of the memory device is asserted to when the data output from the device is valid.

- $t_{DF} \qquad \mbox{ delay time from when the output enable is deasserted until when the data output from the memory device floats. The smaller this spec is the better because then the micro-controller can drive the next address on the bus sooner.}$

- $t_{WP}$  the write pulse width

The corresponding MCS-96 BUS READ signals and timings are pictured in Figure 6-2.

- $T_{AVDV}$  address valid to data input valid

- $T_{RLDV}$  read low to data valid

- $T_{\ensuremath{\textbf{RHDZ}}}$  read high to data float

- $T_{WLWH}$  the write low pulse width (this is the only critical write timing spec)

- $\begin{array}{rl} T_{OSC} & \mbox{ The period of the oscillator or $1_2$ the period of CLOCKOUT. $T_{OSC} = $1/F_{XTAL1}$ } \end{array}$

Hence, given the above timings, the following relations can be derived:

- 1. (t<sub>ACC</sub> + latch delay) must be  $< T_{AVDV}$

- 2.  $t_{OE}$  must be  $< T_{RLDV}$

- 3.  $t_{DF}$  must be  $< T_{RHDZ}$

- 4.  $t_{WP} < T_{WLWH}$

#### 6.4 What Can be Done to Use Less Expensive Memories and Run at Maximum Speed with Zero Wait States?

With the standard bus timings it is difficult for inexpensive memory devices to meet the critical timings of the microcontroller. Therefore, either the microcontroller has to run at a slower clock frequency or more expensive, faster memories must be used.

The new timing modes on the 8XC196NT solve the problem of meeting critical memory timings. The 8XC196NT new bus timing modes allow the microcontroller to run at its maximum specified frequency and use standard (slower) memory devices. The method of solving the problem centers around adjusting the microcontroller's critical bus timings to accommodate slower memory devices. Refer to the critical timings diagrams (Figure 6-1 and 6-2) to conceptualize the following explanation: typically the limiting factor with external memories is the  $t_{OE}$  spec (corresponding to  $T_{RLDV}$ ). If  $T_{RLDV}$  is increased enough to meet the  $t_{OE}$ spec then the next limiting spec is  $t_{ACC}$  (corresponding to TAVDV). However, when TAVDV is relaxed (i.e. increased) the  $T_{RHDZ}$  becomes worse (i.e. decreases). Consequently tDF now becomes the limiting factor with the memory device. Hence, there is a tradeoff associated with relaxing the TAVDV spec.

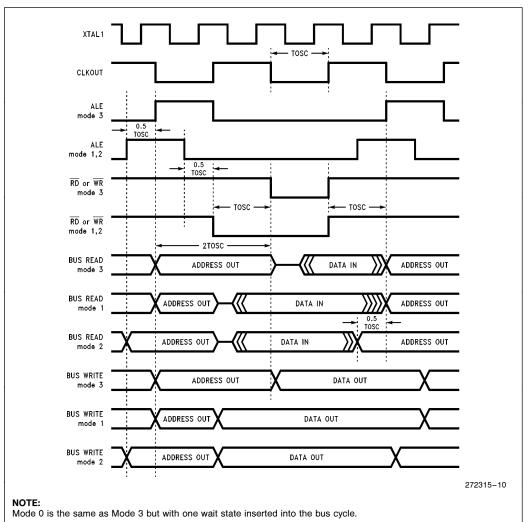

#### 6.5 New Timing Modes

There are four different timing modes available on the 8XC196NT. The modes are: standard timing, standard timing with one wait state, long read/write with advanced ALE, long read/write with advanced address. These modes are selectable by the chip configuration bytes. The chip configuration bytes are loaded into the chip configuration registers after RESET goes high. These bytes configure the microcontroller (see Figure 7-1 for the chip configuration byte definitions). Basically there are two bits in CCB1: MSEL0 and MSEL1 (see Table 6-1) that define the timing modes. A pictorial comparison of these modes is shown in Figure 6-3.

Figure 6-2. Critical 8XC196NT Bus Timings (Read Cycle)

| MSEL0<br>(CCB1.6) | MSEL1<br>(CCB1.7) | Mode | Description                                                                                                                                                                                                                                     |

|-------------------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | 0                 | 0    | Standard Timing with One Wait State inserted into the bus cycle.<br>Also known as Slow External Memory (SEM) mode.                                                                                                                              |

| 0                 | 1                 | 1    | <b>Long R/W:</b> advances $\overline{RD}/\overline{WR}$ by 1 T <sub>OSC</sub> creating a 2 T <sub>OSC</sub> $\overline{RD}/\overline{WR}$ low time. ALE is also advanced by 0.5 T <sub>OSC</sub> but ALE high time remains 1 T <sub>OSC</sub> . |

| 1                 | 0                 | 2    | Early Address: Same as mode 1 but the address is put on the bus 0.5 $T_{OSC}$ earlier in the bus cycle.                                                                                                                                         |

| 1                 | 1                 | 3    | Standard Timing Mode                                                                                                                                                                                                                            |

#### 6.5.1 STANDARD TIMING (MODE 3)

The *standard timing* mode configures the bus controller to operate with timings similiar to the 8XC196KR. This mode is the default bus timing mode after RESET. See Figure 6-3 for a pictorial representation of mode 3 compared to modes 1 and 2.

| Memory<br>Device Spec | Corresponding<br>8XC196NT Spec | Time<br>in ns                 |

|-----------------------|--------------------------------|-------------------------------|

| t <sub>ACC</sub>      | T <sub>AVDV</sub>              | 3 T <sub>OSC</sub> – 55 (Max) |

| t <sub>DF</sub>       | T <sub>RHDZ</sub>              | T <sub>OSC</sub> (Max)        |

| t <sub>OE</sub>       | T <sub>RLDV</sub>              | T <sub>OSC</sub> - 30 (Max)   |

| t <sub>WP</sub>       | T <sub>WLWH</sub>              | T <sub>OSC</sub> - 30 (Min)   |

NOTE:

For latest specs consult the current datasheet for the  $\ensuremath{\mathsf{8XC196NT}}$  .

#### 6.5.2 STANDARD TIMING WITH ONE WAIT STATE (MODE 0)

Mode 0 is the same as the *Standard Timing* mode except that one wait state is inserted into the bus cycle. A wait state is 2  $T_{OSC}$ , which must be added to the relevant "no wait state" spec to get the MODE 0 spec. This mode is also referred to as the *Slow External Memory* (SEM) mode.

#### 6.5.2.1 Mode 0 Timing Specs

| Memory<br>Device Spec | Corresponding<br>8XC196NT Spec | Time<br>in ns                 |

|-----------------------|--------------------------------|-------------------------------|

| t <sub>ACC</sub>      | T <sub>AVDV</sub>              | 5 T <sub>OSC</sub> - 55 (Max) |

| t <sub>DF</sub>       | T <sub>RHDZ</sub>              | T <sub>OSC</sub> (Max)        |

| t <sub>OE</sub>       | T <sub>RLDV</sub>              | 3 T <sub>OSC</sub> - 30 (Max) |

| t <sub>WP</sub>       | T <sub>WLWH</sub>              | $3 \ T_{OSC} - 30$ (Min)      |

#### NOTE:

For latest specs consult the current datasheet for the  $\ensuremath{\mathsf{8XC196NT}}$  .

#### 6.5.3 LONG READ/WRITE WITH ADVANCED ALE (MODE 1)

Mode 1 improves the  $t_{OE}$  spec. Since  $t_{OE}$  corresponds to  $T_{RLDV}$ , it follows that lengthening the READ (or WRITE) pulse also lengthens  $T_{RLDV}$ . Consequently, the memory device has more time to place the data onto the bus. In other words, the  $t_{OE}$  spec of the memory device can now be larger which corresponds to a less expensive device. Hence, MODE 1 is called the Long READ/WRITE mode since the RD/WR signals are advanced by one  $T_{OSC}$  (see Figure 6-3, comparison of the bus timing modes). The time the address is driven on the bus is shortened by one  $T_{OSC}$  from two  $T_{OSC}$ s (see Figure 6-3). ALE is advanced by one-half a  $T_{OSC}$ , but still has a one  $T_{OSC}$  high time. Advancing ALE guarantees that the address will be valid when ALE goes low (shown in Figure 6-3).

### int

#### 6.5.3.1 Mode 1 Timing Specs

| <b>v</b> i            |                                |                               |

|-----------------------|--------------------------------|-------------------------------|

| Memory<br>Device Spec | Corresponding<br>8XC196NT Spec | Time<br>in ns                 |

| t <sub>ACC</sub>      | T <sub>AVDV</sub>              | 3 T <sub>OSC</sub> - 60 (Max) |

| t <sub>DF</sub>       | T <sub>RHDZ</sub>              | T <sub>OSC</sub> (Max)        |

| t <sub>OE</sub>       | T <sub>RLDV</sub>              | 2 T <sub>OSC</sub> - 44 (Max) |

| t <sub>WP</sub>       | T <sub>WLWH</sub>              | 2 T <sub>OSC</sub> - 20 (Min) |

NOTE:

For latest specs consult the current datasheet for the 8XC196NT.

#### 6.5.4 LONG READ/WRITE WITH ADVANCED ALE AND EARLY ADDRESS (MODE 2)

This mode improves the  $t_{ACC}$  spec by lengthening  $T_{AVDV}$ . As shown in Figure 6-3, the address is placed on the bus one-half  $T_{OSC}$  earlier than the other modes. Therefore, the address is driven for one and a half T<sub>OSC</sub>s. Since the address is placed on the bus one-half

#### AP-475

$T_{\mbox{OSC}}$  earlier, the previous data has to be taken off the bus faster. Hence, the T<sub>RHDZ</sub> spec is shortened (i.e., worse than other modes). In Figure 6-3, the mode 2 A/D bus drawing shows the data output being floated earlier due to the early address. The tightening of  $T_{\mbox{\scriptsize RHDZ}}\ (t_{\mbox{\scriptsize DF}})$  is a necessary compromise that results from relaxing  $T_{AVDV}$ .

#### 6.5.4.1 Mode 2 Timing Specs

| Memory<br>Device Spec | Corresponding<br>8XC196NT Spec | Time<br>in ns                   |

|-----------------------|--------------------------------|---------------------------------|

| t <sub>ACC</sub>      | T <sub>AVDV</sub>              | 3.5 T <sub>OSC</sub> - 55 (Max) |

| t <sub>DF</sub>       | T <sub>RHDZ</sub>              | 0.5 T <sub>OSC</sub> (Max)      |

| t <sub>OE</sub>       | T <sub>RLDV</sub>              | 2 T <sub>OSC</sub> - 44 (Max)   |

| t <sub>WP</sub>       | T <sub>WLWH</sub>              | $2  T_{OSC} - 20$ (Min)         |

#### NOTE:

For latest specs consult the current datasheet for the 8XC196NT.

Figure 6-3. Comparison of 8XC196NT Bus Timing Modes

#### 6.6 Given These New Timing Modes, Which Memory Devices Can Be Used with No Wait States?

The timing improvements discussed above allow the memory devices to be used at higher frequencies with no wait states. Included in this application note are four spreadsheets that show the maximum frequency the 8XC196NT can be run at with the given memory device in a given mode. In different modes, the maximum frequency is contingent upon one of the three critical timing specs (i.e.,  $t_{ACC}$ ,  $t_{OE}$  or  $t_{DF}$ ). The spreadsheets show the calculations for each critical timing. For example, it calculates the maximum frequency assuming that  $t_{ACC}$  is the limiting spec. Then the spreadsheets calculate the maximum frequency assuming toE is the limiting spec and so forth. After the maximum frequency is calculated the corresponding 8XC196NT bus timings are calculated based on the maximum frequency just found. For example, in spreadsheet 2, Mode 1 calculations are shown. Three different groups of calculations are done based on either  $t_{ACC}$ ,  $t_{OE}$  and  $t_{DF}$ . Notice that the shaded maximum frequency column is under  $t_{ACC}$ . That means that  $t_{ACC}$  was the limiting spec. Also, the timings  $t_{\mbox{ACC}}\xspace$  ,  $t_{\mbox{OE}}\xspace$  and  $t_{\mbox{DF}}\xspace$  are within the limits of the calculated  $T_{AVDV}$ ,  $T_{RLDV}$  and  $T_{RHDZ}$ respectively. Notice in the other two columns ( $t_{OE}$  and  $t_{\mbox{DF}}\mbox{)},$  that the specs  $t_{\mbox{ACC}}\mbox{, }t_{\mbox{OE}}\mbox{ and }t_{\mbox{DF}}\mbox{ do not all meet}$ TAVDV, TRLDV or TRHDZ. The flash memory parts have the same analysis except just toE and twP are considered. Also, mode 0, the standard timing mode with one wait state is included for completeness. The last spreadsheet (#5) is a summary of the previous four.

#### 6.7 Changes to the Bus Control Timings

The main control signals affected by the enhanced bus controller are ALE,  $\overline{RD}$ , and  $\overline{WR}$ . But, some other control signals changed as well. For example, in modes 1 and 2,  $\overline{ADV}$ , BHE and INST occur one-half a T<sub>OSC</sub> earlier to remain consistent with ALE and  $\overline{RD}/\overline{WR}$ . Also, the  $\overline{WRL}/\overline{WRH}$  lengthened the same as  $\overline{WR}$ .

#### 6.8 8-Bit Bus in Modes 1 and 2

It is required to latch address lines 0 through 15 when running in 8-bit mode when operating in modes 1 (long read/write) and 2 (early address). The reason for the latch is because the upper address lines (A8–A15) are not driven with the address during the write or read portion of the bus cycle. Instead A8–A15 are driven with the data from AD0–AD7 during the write or read cycle.

A latch is not required on the upper address lines A8-A15, when operating in Modes 0 and 3. In these modes the address is driven on A8-A15 during the entire bus cycle. Only a latch on the lower address lines (AD0-AD7) is required.

|              |      |      |     |                                 |                           |                    |           |                                              | Mode 0                   | e 0     |                     |                                                         |                          |                   |                   |

|--------------|------|------|-----|---------------------------------|---------------------------|--------------------|-----------|----------------------------------------------|--------------------------|---------|---------------------|---------------------------------------------------------|--------------------------|-------------------|-------------------|

|              |      |      |     |                                 | Based on t <sub>ACC</sub> | n t <sub>ACC</sub> |           |                                              | Based on t <sub>OE</sub> | on toe  |                     |                                                         | Based on t <sub>DF</sub> | n t <sub>DF</sub> |                   |

| EPROMS       | tacc | toe  | toF | Max Freq                        | TAVDV                     | TRLDV              | TRHDZ     | Max Freq                                     | I TAVDV                  | TRLDV   | T <sub>RHDZ</sub>   | Max Freq                                                | TAVDV                    | TRLDV             | T <sub>RHDZ</sub> |

| 27C256-200   | 200  | 75   | 55  | 18.66                           | 200.00                    |                    |           | 28.57                                        | 107.00                   | 75.00   | 35.00               | 18.18                                                   | 207.00                   | 135.00            | 55.00             |

| 27C256-150   | 150  | 60   | 50  | 22.94                           | 150.00                    | 100.80             | 43.60     | 33.33                                        | 82.00                    | 60.00   | 30.00               | 20.00                                                   | 182.00                   | 120.00            | 50.00             |

| 27C256-120   | 120  | 55   | 30  | 26.60                           | 120.00                    | 82.80              | 37.60     | 35.29                                        | 73.67                    | 55.00   | 28.33               | 33.33                                                   | 82.00                    | 60.00             | 30.00             |

| 27C512-200   | 200  | 70   | 60  | 18.66                           | 200.00                    | 130.80             | 53.60     | 30.00                                        | 98.67                    | 70.00   | 33.33               | 16.67                                                   | 232.00                   | 150.00            | 60.00             |

| 27C512-150   | 150  | 60   | 50  | 22.94                           | 150.00                    | 100.80             | 43.60     | 33.33                                        | 82.00                    | 60.00   | 30.00               | 20.00                                                   | 182.00                   | 120.00            | 50.00             |

| 27C512-120   | 120  | 55   | 30  | 26.60                           | 120.00                    | 82.80              | 37.60     | 35.29                                        | 73.67                    | 55.00   | 28.33               | 33.33                                                   | 82.00                    | 60.00             | 30.00             |

| 27C010-200   | 200  | 70   | 09  | 18.66                           | 200.00                    | 130.80             | 53.60     | 30.00                                        | 98.67                    | 70.00   | 33.33               | 16.67                                                   | 232.00                   | 150.00            | 60.00             |

| 27C010-150   | 150  | 60   | 50  | 22.94                           | 150.00                    | 100.80             | 43.60     | 33.33                                        | 82.00                    | 60.00   | 30.00               | 20.00                                                   | 182.00                   | 120.00            | 50.00             |

| 27C010-120   | 120  | 55   | 30  | 26.60                           | 120.00                    | 82.80              | 37.60     | 35.29                                        | 73.67                    | 55.00   | 28.33               | 33.33                                                   | 82.00                    | 60.00             | 30.00             |

| 27C020-200   | 200  | 70   | 09  | 18.66                           | 200.00                    | 130.80             | 53.60     | 30.00                                        | 98.67                    | 70.00   | 33.33               | 16.67                                                   | 232.00                   | 150.00            | 60.00             |

| 27C020-150   | 150  | 60   | 50  | 22.94                           | 150.00                    | 100.80             | 43.60     | 33.33                                        | 82.00                    | 60.00   | 30.00               | 20.00                                                   | 182.00                   | 120.00            | 50.00             |

| 27C040-200   | 200  | 70   | 09  | 18.66                           | 200.00                    | 130.80             | 53.60     | 30.00                                        | 98.67                    | 70.00   | 33.33               | 16.67                                                   | 232.00                   | 150.00            | 60.00             |