AP-714

### APPLICATION NOTE

### Converting from the 8XC196KB/KC/KD to the 8XC196Nx Family

JENNIE ABELLA APPLICATIONS ENGINEER

July 1995

Order Number: 272625-001

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive and iCOMP trademarks has been issued to Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

### CONVERTING FROM THE 8XC196KB/KC/KD TO THE 8XC196Nx FAMILY

| CONTENTS                                                               | PAGE   |

|------------------------------------------------------------------------|--------|

| 1.0 INTRODUCTION           1.1 Related Documents                       |        |

| 2.0 ARCHITECTURAL OVERVIEW OF<br>THE HSIO AND EPA FAMILY               | 2      |

| 3.0 ADDITIONAL FEATURES OF THE<br>8XC196Nx FAMILY                      | 3      |

| 3.1 Additional Registers and Pins to<br>Support 1 Mbyte Addressability | 3      |

| 3.2 Chip Select Unit of the<br>8XC196NP                                | 6      |

| 3.3 Demultiplexed/Multiplexed Bus of<br>the 8XC196NP                   | f<br>7 |

| 3.4 Lower Voltage (3.3V) Operation o the 8XC196NP                      | f<br>7 |

| 4.0 MEMORY PARTITIONS                                                  | 7      |

| 4.1 Special Purpose Memory                                             | 14     |

| 4.2 Chip Configuration Registers                                       | 15     |

| CONTENTS PAGE                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.0 HARDWARE         13           5.1 Pinout Diagrams         13           5.2 Pinout Differences         17                                                   |

| 6.0 REGISTERS                                                                                                                                                  |

| 7.0 INTERRUPT UNIT                                                                                                                                             |

| 8.0 PERIPHERALS         40           8.1 I/O Ports         40           8.2 Serial I/O Port         41           8.3 High Speed Input/Output (HSIO)         41 |

| and Event Processor Array (EPA)       42         8.4 A/D Converter       43         8.5 Pulse Width Modulator       47                                         |

| 9.0 NEW INSTRUCTIONS TO SUPPORT<br>1 MBYTE ADDRESSABILITY                                                                                                      |

### 1.0 INTRODUCTION

The MCS<sup>®</sup> 96 microcontroller product family has three distinct product lines: the HSIO family consists of devices that have the High Speed Input/Output subsystem and is comprised of the 8XC196KB, 8XC196KC and 8XC196KD; the EPA family consists of devices that have the advanced peripherals, including a flexible input/output system and Event Processer Array (EPA). The EPA family includes the 8XC196KR, 8XC196KT, 8XC196NT and 8XC196NP; and the Motion Control family, which is comprised of devices that support motor control applications, and also uses the EPA system for I/O control, includes the 8XC196MC, 8XC196MD, and 8XC196MH.

As designs require higher performance and greater addressing capability, there is a need for converting from the HSIO family to the EPA family. In addition to the highly integrated peripherals, both the 8XC196NP and the 8XC196NT offer a performance and addressing-upgrade path in the MCS 96 microcontroller family. For even greater performance improvement. the 8XC196NP is the first member of the MCS 96 controller family with a dynamically selectable multiplexed/ demultiplexed bus and low-power operation (3.3V at 16 MHz). Other key features of the 8XC196NP are the chip select unit, 3 PWM outputs, and increased operating frequency of 25 MHz at 5V.

To ease the difficulty in converting from the HSIO family to the 1 Mbyte addressable members of the EPA family, this application note will discuss the design considerations in making this conversion. The focus will be on converting from the 8XC196KB/KC/KD to the 8XC196NX family, which includes the 8XC196NT and the additional features of the 8XC196NP. The purpose of this paper is to highlight the benefits of the new features of the 8XC196NX family, to inform the user of the conversion issues which need to be considered, and to present code examples of several peripherals to make converting as straightforward as possible. For a more in-depth discussion of the differences between the HSIO and EPA, see AP-449 (literature order #270968): "A Comparison of the Event Processor Array and High Speed Input/Output Unit."

### 1.1 Related Documents

This document is intended to serve as a comparison between several of the MCS 96 Microcontroller devices. For details on how to use the features and peripherals of these devices, please refer to the following documents:

- 8XC196NP Microcontroller User's Manual, Order Number 272479

- 8XC196NP Commercial CHMOS 16-Bit Microcontroller datasheet, Order Number 272459

- 8XC196NT Microcontroller User's Manual, Order Number 272317

- 8XC196NT CHMOS Microcontroller with 1 Mbyte Linear Address Space datasheet, Order Number 272267

- AP-475, Using the 8XC196NT, Order Number 272315

- AP-449, A Comparison of the Event Processor Array (EPA) and High Speed Input/Output (HSIO) Unit, Order Number 270968

- AP-445, 8XC196KR Peripherals: A User's Point of View, Order Number 270873

- 8XC196KC/8XC196KD User's Manual, Order Number 272238

- 8XC196KD/8XC196KD20 Commercial CHMOS Microcontroller datasheet, Order Number 272145

- 8XC196KC/8XC196KC20 Commercial/Express CHMOS Microcontroller datasheet, Order Number 270942

- 8XC196KB/8XC196KB16 Commercial/Express CHMOS Microcontroller datasheet, Order Number 270909

- 87C196KB/83C196KB/80C196KB 16-Bit High Performance CHMOS Microcontroller (datasheet), Order Number 270918

- MCS 96 Microcontroller Family Fact Sheet, Order Number 272223

- ApBUILDER Interactive Programming Software Package, Order Number 272216

Also available is Intel's FaxBACK service [(800) 628-2283] which sends documents to your fax machine. Order catalog #2 for a listing of MCS 96 microcontroller documents.

#### 2.0 ARCHITECTURAL OVERVIEW OF THE HSIO AND EPA FAMILY

The 8XC196KB is the first member of the CHMOS\* MCS 96 controller family. It is available in CPU only, 8 Kbyte ROM, and 8 Kbyte OTPROM versions. All versions feature 232 bytes of register RAM. The 8XC196KB uses the High-Speed Input/Output (HSIO) structure for event control. The HSIO has up to 4 input and 6 output lines, and uses either of two 16-bit timer/ counters as a time base. Additional features include a hardware-generated Pulse Width Modulator (PWM), a full-duplex Serial I/O (SIO) port, a watchdog timer and an 8-channel 10-bit resolution Analog to Digital (A/D) converter. The 8XC196KB has 48 Input/Output (I/O) lines that are shared with the peripherals.

The 8XC196KC is the next step up in the CHMOS 196 family. It is available in CPU only, 16 Kbyte ROM and 16 Kbyte OTPROM versions. All versions feature 488 bytes of Register RAM. The 8XC196KC is offered in a 20 MHz version, allowing an immediate 25% increase in performance. The 8XC196KC has all the same peripherals as the 8XC196KB, but adds the following features: There are now a total of three hardware PWM generators, the A/D converter has both 8- and 10-bit conversion modes with programmable sample and conversion times, and a Peripheral Transaction Server (PTS) has been added. The PTS acts as a microcoded interrupt handler, which greatly reduces CPU overhead during interrupt servicing.

The 8XC196KD has all the features of the 8XC196KC, but has extended the on-chip memory. The 8XC196KD is available in 32 Kbyte ROM and 32 Kbyte OTPROM versions. Both versions feature 1000 bytes of Register RAM. With the availability of 32K of memory, program development in high-level languages becomes much more practical. The 8XC196KD is also offered in a 20 MHz version.

The 8XC196KR is a highly integrated, advanced member of the MCS 96 controller family. The 8XC196KR has an optional 16 Kbyte OTPROM and has 488 bytes of Register Ram and 256 bytes of Internal RAM. The Internal RAM can be used for program execution or data storage. The 8XC196KR uses a modular Event Processor Array (EPA) for event monitoring and control. The EPA has 250 ns resolution at 16 MHz, and has 10 capture/compare modules plus two compare only modules. The EPA is extremely flexible, and has pulse width modulation (PWM) generation capability. The 8XC196KR includes the Peripheral Transaction Server (PTS), with modes to support PWM generation with the EPA. The 8XC196KR has a slave port which is used to interface to another system's bus. The slaveport feature can be used to make the 8XC196KR a versatile, programmable peripheral attached to any PC's bus. There are two serial ports on the 8XC196KR; one is the standard SIO module found on the 8XC196KB, and the other is a Synchronous Serial I/O (SSIO) port. The SSIO is capable of full-duplex synchronous communication. Both serial ports have their own programmable baud rate generators. The 8XC196KR A/D converter is based on the 8XC196KC design but offers additional modes which allow programmable threshold detection and offset correction.

The 8XC196KT is an enhanced version of the 8XC196KR with an optional 32 Kbyte OTPROM and has 1000 bytes of Register RAM and 512 bytes of Internal RAM. The 8XC196KT's bus controller has new modes which allow no wait-state operation with slower external memory.

The 8XC196NT has the same features as the 8XC196KT but has 1 Mbyte external addressability, which allows the design to handle large software code. Four of the A/D inputs were replaced with the Extended Address Port (EPORT). The four EPORT pins can be used as additional address lines (A16–A19) or standard low speed I/Os, or a combination of both. The 8XC196NT has increased speed, starting at 20 MHz operation.

The 8XC196NP is the first member of the MCS 96 controller family with a chip-select unit and low voltage-over-power operation (3.3V at 16 MHz). The six programmable chip selects can reduce or eliminate the need for external decode logic. The 3.3V version of the 8XC196NP will be ideal for portable, battery-powered applications. This currently is the only low voltage, 3V part in the MCS 96 controller family. Another new feature of the 8XC196NP is the dynamically selectable multiplexed/demultiplexed bus. The dynamic dual mode bus allows the interface of inexpensive memory devices resulting in lower overall system cost, while at the same time increasing performance. It allows cost-effective, zero wait-state designs at 25 MHz. The dynamic mux/demux bus structure also makes the 8XC196NP compatible with existing MCS 96 microcontroller family designs. The new system bus also compensates for the lack of an OTPROM version of the 8XC196NP by allowing access to low cost external memory. The 8XC196NP also has 1 Mbyte addressing, 3 PWM outputs, and 25 MHz operation at 5V. To

compensate for the additional features, some peripherals were reduced or removed. The 8XC196NP has 4 EPA channels compared to the 10 EPA channels and 2 compare-only channels on the 8XC196NT. The analog to digital convertor, the watch dog timer, the SSIO, and the slave port were removed. Regarding internal memory, the 8XC196NP has 1000 bytes register RAM and optional 4K of ROM.

#### 3.0 ADDITIONAL FEATURES OF THE 8XC196Nx FAMILY

#### 3.1 Additional Registers and Pins to Support 1 Mbyte Addressability

(See Memory Partitions Chapter for the Memory Address Space.) To support 1 Mbyte addressability, new CCBs were added. [See also Memory Partitions (Chip Configuration Register) section 4.2.] The 8XC196NT has 3 CCBs (CCB0-3). An additional bit (LDCCB2) was added to CCR1 that enables the loading of CCR2. The LDCCB2 bit must be set to load the CCB2 register which determines the addressing mode and mapping of internal OTPROM. Additional bits (MSEL0-1) were added to CCR1 to select different bus-timing modes. Both the 8XC196NT and the 8XC196NP have added a CCR (CCR2 and CCR1 respectively) to select either 16-bit or 24-bit addressing mode. This register also controls whether the internal OTPROM is mapped into both page 0FFH and page 00H or into page 0FFH only. The 8XC196NP has added bits in CCR0 for Wait States and Demuxed/Muxed Mode.

The 8XC196NT has selectable bus-timing modes, controlled by the MSEL0 and MSEL1 bits (bit 6 and 7) of CCR1. Mode 3 is the standard timing mode. This mode should be used for systems that need to emulate the 8XC196KR. Mode 0 is the standard timing mode with a minimum of one wait state added to each bus cycle. Mode 1 is the long read/write mode. This allows the memory more time to get its data on the bus without the wait-state penalty of Mode 0. Mode 2 is similar to Mode 1 in that RD#, WR#, and ALE begin  $\frac{1}{2}$  TOSC earlier in the bus cycle and the widths of RD# and WR# are 1 TOSC longer than in Mode 3. It differs from Mode 1 in that the address is also placed onto the bus  $\frac{1}{2}$  TOSC earlier in the bus cycle. This mode trades a longer TRHDX for a shorter TAVDV.

| Table 3 | 3-1. Bus | Timina | Mode | Control |

|---------|----------|--------|------|---------|

|         |          |        |      |         |

| MSEL1<br>(CCR1.7) | MSEL0<br>(CCR1.6) | Bus Timing Mode                                                        |

|-------------------|-------------------|------------------------------------------------------------------------|

| 0                 | 0                 | Mode 0, 8XC196KR compatible<br>timing with one automatic wait<br>state |

| 0                 | 1                 | Mode 1, Long Read/Write Mode                                           |

| 1                 | 0                 | Mode 2, Long Read/Write with early address                             |

| 1                 | 1                 | Mode 3, 8XC196KR compatible mode                                       |

The 8XC196NT and 8XC196NP both control the addressing modes (16 vs. 24-bit) in the same manner. (Only 20 address lines are bonded out so, externally, 24-bit addressing will appear to be 20-bit addressing.) For 24-bit addressing, the MODE16 bit (bit 1 in CCR2/CCR1 for the 8XC196NT/NP) must be cleared. In both 16-bit and 24-bit modes, the 8-bit extended slave program counter (ESPC) is concatenated with the 16-bit master program counter to form a 24-bit PC. In 16-bit mode, the ESPC is forced to 0FFH. Therefore, using non-extended instructions can only access page FFH (64 Kbytes). Extended load, store, and block-move instructions can access data in any page, but extended jump, branch, and call instructions will not function in 16-bit mode. In 24-bit mode, the ESPC can have any value and can therefore access up to 1 Mbyte. By using extended instructions the ESPC is changed to the value of the destination page.

The remapping function is an additional feature that is done the same for the 8XC196NT and 8XC196NP. The REMAP bit (bit 2 in CCR2/CCR1 for the 8XC196NT/NP) controls the memory mapping of internal OTPROM. Set the bit to map the internal OTPROM into both pages 00H and FFH. This allows data tables that are stored in OTPROM to be accessed in page 00H. Clear the bit to map internal OTPROM into page FFH only. This will leave page 00H free for other uses. The REMAP bit is only effective when EA# is high. When EA# is low, execution is external and the REMAP bit is ignored, leaving page 00H free.

Wait-state control is different for the 8XC196NT than it is for the 8XC196NP. For the 8XC196NT, the Internal Ready Control bits (IRC0-IRC2) define the maximum number of wait states that will be inserted; see Table 3-2. When all three bits are set, the bus controller inserts wait states until the external memory device asserts the READY signal high. Otherwise, the bus con-

troller inserts wait states until either the external memory device asserts the READY signal, or the number of wait states equals the number (0, 1, 2, or 3) specified by the bit settings. These wait-state settings apply to all external devices.

| IRC2<br>(CCB1.1) | IRC1<br>(CCB0.5) | IRC0<br>(CCB0.4) | Maximum<br>Wait States                |

|------------------|------------------|------------------|---------------------------------------|

| 0                | 0                | 0                | Limit to 0                            |

| 1                | 0                | 0                | Limit to 1                            |

| 1                | 0                | 1                | Limit to 2                            |

| 1                | 1                | 0                | Limit to 3                            |

| 1                | 1                | 1                | Infinite (controlled by READY signal) |

For the 8XC196NP, the Wait-State control bits (WS0-1) define the number of wait states that will be generated internally. (See Table 3-3.) The READY input can then be used by the external device to insert additional wait states. The wait-state settings programmed by the CCB are the default settings until the BUSCON registers are programmed. (See "Chip Select Unit of the 8XC196NP", section 3.2.)

#### Table 3-3. Wait-State Control for the 8XC196NP

| WS1<br>(BUSCONx.1) | WS0<br>(BUSCONx.0) | Wait States |  |

|--------------------|--------------------|-------------|--|

| 0                  | 0                  | 0 inserted  |  |

| 0                  | 1                  | 1 inserted  |  |

| 1                  | 0                  | 2 inserted  |  |

| 1                  | 1                  | 3 inserted  |  |

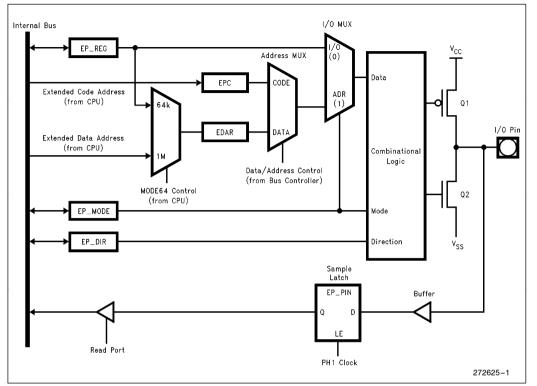

To support 1 Mbyte addressability, the EPORT was added. See Figure 3-1. The EPORT is a four-bit, bi-directional, memory-mapped I/O port that acts as address lines 16-19. If these pins are not needed for address lines, they can also be configured for I/O. The EP\_MODE register controls whether the port pin is an address line or an I/O port. If the port is in address mode (EP\_MODE set) then the ADDRESS MUX determines the address source. For an instruction fetch, the ADDRESS MUX is set to the CODE input and the Extended Slave Program Counter (ESPC) is selected as the address source. For a data fetch, or while there is no bus activity, the ADDRESS MUX is set to the DATA input, and the Extended Data Address Register (EDAR) is selected as the address source. The EDAR is loaded from two different sources, depending on whether the data access is extended or non-extended. For extended data accesses, the DATA MUX is set to the 24-bit input and EDAR is loaded with the extended address. For non-extended data accesses, the DATA MUX is set to the 16-bit input and EDAR is loaded from EP\_REG. The last value loaded remains in EDAR until the next data access.

Figure 3-1. EPORT Block Diagram

### intəl

Keep the following points in mind:

During extended accesses, the EPORT pins are determined by the upper four bits of the address, assuming that the pins are configured for their special function as an extended address port pin. Regardless of the value in EP\_\_REG or the current operating page, any non-extended instruction that accesses address locations 0000H-03FFH will be directed to the Register File and any non-extended instruction that accesses address

#### Example:

locations 1F00H-1FDFH will be directed to the Special Function Registers. Non-extended accesses outside of these ranges will be directed to the page defined by the value currently in EP\_REG. This effectively maps the Register File and the windowable SFRs into every page. Extended instructions can access the "mapped over" areas of each page. For example, if location 010045H is addressed with an extended instruction, i.e., eld, est, 010045H will actually be accessed.

| ldb t | .emp, | #03h   |   |    |         |    |       |      |         |

|-------|-------|--------|---|----|---------|----|-------|------|---------|

| estb  | temp, | EP_REG |   |    |         |    |       |      |         |

| ldb   | temp, | #0aah  |   |    |         |    |       |      |         |

| stb   | temp, | lfd4h  | ; | AA | written | to | P1_RE | G    |         |

| stb   | temp, | 300h   | ; | AA | written | to | upper | reg  | ; file  |

| stb   | temp, | 60h    | ; | AA | written | to | lower | reg  | ; file  |

| stb   | temp, | 3000h  | ; | AA | written | to | page  | 03 @ | 3000h   |

| stb   | temp, | lfe5h  | ; | AA | written | to | page  | 03 @ | ) lfe5h |

|       |       |        |   |    |         |    |       |      |         |

#### 3.2 Chip Select Unit of 8XC196NP

In previous versions of the MCS 96 controller family, chip selects for external devices needed to be decoded through external logic. The bus width was previously determined by BW bits in the CCBs, or it could be controlled dynamically with the BUSWIDTH pin. The 8XC196NP has a chip-select unit that provides six outputs—CS5:0#, for selecting external devices. The chip selects are programmed to be asserted when the external address falls within the range of that chip select. For each separate chip select, the bus width, the num-

ber of wait states, the address range, and multiplexed or demultiplexed address/data lines are programmed independently. These parameters are selected with the BUSCONx register. If the address range falls outside the range for each chip select, then BUSCON5 determines the bus width, the wait states, and multiplexing. The register ADDRCOMx holds the upper 12 bits of the base address of the address range assigned to CSx #. The register ADDRMSKx determines the size of the address range. The first lines of your code should be to set up the stack pointer and to then initialize all of the chip select registers.

#### 3.3 Demultiplexed/Multiplexed Bus of the 8XC196NP

The demultiplexed bus mode allows the interface of slower, less inexpensive memory devices. In multiplexed mode, the address is only on the bus for half of the cycle, so external devices have less time to receive it. In demultiplexed mode, the address and data are both on the bus for the full cycle; consequently, latches are not necessary, and slower external devices can be used. The DEMUX bit (BUSCONx.7) controls the address/data multiplexing on the external bus. Set the DEMUX bit for data only on AD0-15 (demultiplexed mode) and clear it for address Manual for timing comparisons between demuxed/muxed modes.

#### 3.4 Lower Voltage (3.3V) Operation of the 8XC196NP

The 8XC196NP is the first 3.3V MCS 96 controller device. At 5V, the device can run up to 25 MHz and at 3.3V the device can run up to 16 MHz. Although the device functions across 2.97V to 5.5V, it is specified across two ranges, 2.97V-4.5V and 4.5V-5.5V. See the data sheet for exact specifications.

#### 4.0 MEMORY PARTITIONS

This section describes the addressable memory space of the HSIO (8XC196KB/KC/KD) devices and the 8XC196Nx devices. The HSIO family has 64 Kbytes of addressable memory space. The 8XC196Nx devices feature a non-segmented, 24-bit address space, of which only the lower 20 bits are available to the user, providing 1 Mbyte addressability. The lower 16 address/data lines (AD0-AD15) of the 8XC196Nx are the same as those of the HSIO family devices. On the 8XC196Nx, the four extended address lines (A16-A19) are made available on a special port, the EPORT. Since the 8XC196Nx has 24 address bits internally, code must be written as though all 24 bits are being used. Since the device resets from page FFH, code must be written in this page. For example, when generating assembly code, use "CSEG at 0FF2080H" for user code and "CSEG at 0FF2000H" for the interrupt vectors. If using external memory, the device will still reset to page FFH, and this will be overlayed to page 0FH since only 20 lines are bonded out. For future devices may have all 24 address lines bonded out.

The top-level memory maps shown following in Tables 4-1 and 4-2 show the differences in the memory space of the HSIO devices and the 8XC196Nx devices. In addition to the shown pages 00H and FFH on the 1 Mbyte addressable devices pages 10H to EFH are overlayed memory and pages 01H to 0FH are for external memory, which can be considered as 14 pages of 64 Kbytes each for 896 Kbytes total.

| TOP 8XC196KB/KC/KD           |                 |                 |                  |  |  |  |  |  |

|------------------------------|-----------------|-----------------|------------------|--|--|--|--|--|

|                              | 8XC196KB        | 8XC196KC        | 8XC196KD         |  |  |  |  |  |

| External<br>Memory or I/O    | 0FFFFH<br>4000H | 0FFFFH<br>6000H | 0FFFFH<br>0A000H |  |  |  |  |  |

| Program<br>Memory            | 3FFFH<br>2080H  | 5FFFH<br>2080H  | 9FFFH<br>2080H   |  |  |  |  |  |

| Special<br>Purpose<br>Memory | 207FH<br>2000H  | 207FH<br>2000H  | 207FH<br>2000H   |  |  |  |  |  |

| Port 4                       | 1FFFH           | 1FFFH           | 1FFFH            |  |  |  |  |  |

| Port 3                       | 1FFEH           | 1FFEH           | 1FFEH            |  |  |  |  |  |

| External<br>Memory           | 1FFDH<br>100H   | 1FFDH<br>200H   | 1FFDH<br>400H    |  |  |  |  |  |

| Register File                | 0FFH<br>0H      | 1FFH<br>0H      | 3FFH<br>0H       |  |  |  |  |  |

#### Table 4-1. Top-Level Memory Map for 8XC196KB/KC/KD

| Table 4-2. Top Level memory map for oversource |                        |                        |                                          |                      |                      |  |  |  |  |

|------------------------------------------------|------------------------|------------------------|------------------------------------------|----------------------|----------------------|--|--|--|--|

|                                                | 8XC196NT<br>Page 0FFH  | 8XC196NP<br>Page 0FFH  |                                          | 8XC196NT<br>Page 00H | 8XC196NP<br>Page 00H |  |  |  |  |

| External Memory or I/O                         | 0FF FFFFH<br>0FF A000H | 0FF FFFFH<br>0FF 3000H | External Memory or I/O                   | 00 FFFFH<br>00 A000H | 00 FFFFH<br>00 3000H |  |  |  |  |

| Program Memory                                 | 0FF 9FFFH<br>0FF 2080H | 0FF 2FFFH<br>0FF 2080H | External Memory or<br>Remapped Page 0FFH | 00 9FFFH<br>00 2080H | 00 2FFFH<br>00 2080H |  |  |  |  |

| Special Purpose<br>Memory                      | 0FF 207FH<br>0FF 2000H | 0FF 207FH<br>0FF 2000H | External Memory or<br>Remapped Page 0FFH | 00 207FH<br>00 2000H | 00 207FH<br>00 2000H |  |  |  |  |

| External Memory                                | 0FF 1FFFH              | 0FF 1FFFH              | Memory-Mapped<br>Peripheral SFRs         | 00 1FFFH<br>00 1FE0H | 00 1FFFH<br>00 1FE0H |  |  |  |  |

|                                                |                        |                        | Peripheral SFRs                          | 00 1FDFH<br>00 1F00H | 00 1FDFH<br>00 1F00H |  |  |  |  |

| External Memory                                | 0FF 0600H              |                        | External Memory                          | 00 1EFFH<br>00 0600H | 00 1EFFH<br>00 0400H |  |  |  |  |

| Internal RAM (NT)                              | 0FF 05FFH<br>0FF 0400H |                        | Internal RAM (NT)                        | 00 05FFH<br>00 0400H |                      |  |  |  |  |

| External Memory                                | 0FF 03FFH<br>0FF 0100H | 0FF 0100H              | Upper Register File                      | 00 03FFH<br>00 0100H | 00 03FFH<br>00 0100H |  |  |  |  |

| Reserved for ICE                               | 0FF 00FFH<br>0FF 0000H | 0FF 00FFH<br>0FF 0000H | Lower Register File                      | 00 00FFH<br>00 0000H | 00 00FFH<br>00 0000H |  |  |  |  |

Table 4-2. Top Level Memory Map for 8XC196Nx

There are a few key points to keep in mind when using the 1 Mbyte addressability of the 8XC196Nx devices.

- 1. Program and Special-Purpose memory can be located in either internal OTPROM/ROM (87C196NT/ 83C196NP) or external memory, depending on the state of EA#. Just as in earlier MCS 96 controller devices, if EA# is held low, accesses to memory locations 0FF2000H-0FF9FFFH for the 87C196NT or 0FF2000H-0FF2FFFH for the 83C196NP are directed to external memory and internal OTPROM/ROM is unavailable. Although internally there are 24 address lines, keep in mind that only 20 address lines are actually bonded out. Therefore. when addressing locations in 0FF2000H-0FF9FFFH/0FF2FFFH, the external device will actually be addressed as locations 0F2000H-0F9FFFH/0F2FFFH. For example, when code is written at 0FF2080H and EA # is low, the address on the 8XC196Nx address lines will be 0F2080H.

- 2. Internal RAM (on the 8XC196NT only) is mapped into both pages 00H and FFH. This is the same

physical RAM and can be accessed through either page. Internal RAM is not windowable and therefore it must be used with indirect or indexed addressing. This memory may also be used as dynamic program memory.

- 3. The internal OTPROM of the 87C196NT and the internal ROM of the 83C196NP are located in page FFH and can optionally be mapped into page 00H as well. Remapping this internal memory is done by setting the REMAP bit, which for the 87C196NT is bit 2 of the CCR2 register (added to support extended addressing) and for the 83C196NP is bit 2 of the CCR1. This offers compatability with previous MCS 96 devices.

- 4. Memory-mapped Peripheral SFRs (1FE0H-1FFFH) must be accessed using indirect or indexed addressing modes and cannot be windowed. Non-extended instructions can access memory-mapped SFRs only when EP\_REG is equal to 00H. Extended instructions can access these locations from any page as long as an indirect or indexed instruction is used.

#### Example 4.1

Here the Port 4 register will be configured as output ports using non-extended and extended instructions. Non-extended instructions used: tmpreg0, #00h ldb stb tmpreg0, EP\_REG[0] tmpreg0, #0fh ldb stb tmpreg0, lfd8h[0] :#OFh will be stored at location 1FD8h which is the P4\_MODE register on the 8XC196NP only if :EP\_REG contains OOH. Extended instructions used: ldb tmpreg0, #01h estb tmpreg0, EP\_REG[0] ldb tmpreg0, #0fh estb tmpreg0, lfd8h :#OFh will be stored at location 1FD8h which is the P4\_MODE register regardless of the value stored in EP\_REG.

5. The non-memory-mapped peripheral SFRs (1F00H-1FDFH) are physically located in the onchip peripherals, can be addressed as bytes or as words (some registers are addressed as bytes, some as words, and some as both), and they can be windowed. The SFRs are mapped into all pages when non-extended instructions are used, so any value for EP\_\_REG is valid. Therefore, if using only non-extended instructions, a "hole" in memory will exist on each page from 1F00H-1FDFH. Note, this also applies to the Register RAM (000000H-0003FFH). Extended load and store instructions can access these locations through page 00H only. When extended instructions are used, references to these locations in any other page are directed to external memory. To access external locations in page 00 that overlap the register RAM and SFRs, use the following, since page 10H overlays page 00 externally: est temp, 10 0050H. (See Example 4.2.)

6. The registers of the 8XC196Nx can be both read from and written to the same address location. Therefore, horizontal windowing is no longer necessary.

#### Example 4.2: To access non-memory-mapped peripheral SFRs, use non-extended instructions.

Non-extended instructions used: tmpreg0, #00h ldb : EP\_REG must be OOH. stb tmpreg0, EP\_REG[0] ldb tmpreg0, #0c0h stb tmpreg0, lfbah[0] : #OCOH will be written internally to OOlFBAH ; which is the SBUF\_TX register. To access external locations at 051F00H-051FDFH, use extended instructions. A non-extended store would go to special function registers in page 0. Extended intructions used: cseg at 053000h : Program Counter is in Page 05. lđ tmpreg0, #01h est tmpreg0, 051fd0h ; This will access external location 051FDOh. To access external locations at 1F00H-1FDFH in Page 00h, use extended instructions to Page 0x0h. Extended instructions used: cseg at 013000h ; Program Counter is in Page Ol ldb tmpreg0, #0c0h estb tmpreg0, 101fbah ; OCOh will be stored externally in Page O since ; 10H overlays page 0.

#### 4.1 Special-Purpose Memory

There are only a few differences in the Special-Purpose Memory among the different devices (see Table 4-3). Some of the reserved bytes require different values to be written to these locations. For example, make sure that locations 0FF2019H for the 8XC196NT/NP, and locations 0FF201BH, 0FF201DH, and 0FF201FH for the 8XC196NT are written as 20H to prevent possible bus contention during the CCBx fetch. The primary difference is the location and the contents of the Chip Configuration Bytes (CCBs). Section 4.2 discusses the Chip-Configuration Registers for the different devices.

|                | 8XC196KB 8XC196KC/KD       |                            | 8XC196NT               |                            | 8XC196NP                   |

|----------------|----------------------------|----------------------------|------------------------|----------------------------|----------------------------|

| 207FH<br>205EH | Reserved-0FFH              | Reserved-0FFH              | 0FF 207FH<br>0FF 205EH | Reserved-0FFH              | Reserved-0FFH              |

| 205DH<br>2040H | Reserved-0FFH              | PTS Vectors                | 0FF 205DH<br>0FF 2040H | PTS Vectors                | PTS Vectors                |

| 203FH<br>2030H | Upper Interrupt<br>Vectors | Upper Interrupt<br>Vectors | 0FF 203FH<br>0FF 2030H | Upper Interrupt<br>Vectors | Upper Interrupt<br>Vectors |

| 202FH<br>2020H | Security Key               | Security Key               | 0FF 202FH<br>0FF 2020H | Security Key               | Reserved-0FFH              |

| 201FH          | Reserved-0FFH              | Reserved-0FFH              | 0FF 201FH              | Reserved-20H               | Reserved-0FFH              |

| 201EH          | Reserved-0FFH              | Reserved-0FFH              | 0FF 201EH              | Reserved-0FFH              | Reserved-0FFH              |

| 201DH          | Reserved-0FFH              | Reserved-0FFH              | 0FF 201DH              | Reserved-20H               | Reserved-0FFH              |

| 201CH          | Reserved-0FFH              | Reserved-0FFH              | 0FF 201CH              | CCB2                       | Reserved-0FFH              |

| 201BH          | Reserved-0FFH              | Reserved-0FFH              | 0FF 201BH              | Reserved-20H               | Reserved-0FFH              |

| 201AH          | Reserved-0FFH              | Reserved-0FFH              | 0FF 201AH              | CCB1                       | CCB1                       |

| 2019H          | Reserved-20H               | Reserved-20H               | 0FF 2019H              | Reserved-20H               | Reserved-20H               |

| 2018H          | ССВ                        | ССВ                        | 0FF 2018H              | CCB0                       | CCB0                       |

| 2017H<br>2014H | Reserved-0FFH              | Reserved-0FFH              | 0FF 2017H<br>0FF 2014H | Reserved-0FFH              | Reserved-0FFH              |

| 2013H<br>2000H | Lower Interrupt<br>Vectors | Lower Interrupt<br>Vectors | 0FF 2013H<br>0FF 2000H | Lower Interrupt<br>Vectors | Lower Interrupt<br>Vectors |

#### Table 4-3. Special-Purpose Memory Addresses

### 4.2 Chip-Configuration Registers (CCR)

The Chip-Configuration Bytes (CCBs) identify the environment in which the device is operating. The 8XC196KB/KC/KD CCR controls internal memory protection, internal READY mode, bus control signals, bus-width options, and Powerdown mode. The 8XC196NT CCRs control bus width, bus-control

mode, bus-timing mode, and wait states. They also control OTPROM protection, Powerdown mode, the Watchdog timer, internal OTPROM mapping, and addressing mode. The 8XC196NP CCRs control the bus width, bus mode (multiplexed or demultiplexed), writecontrol mode, wait states for the CCB1 fetch, powerdown enabling, and the 1 Mbyte or 64 Kbyte mode. The rest of this section outlines the bits in each CCR.

#### 8XC196KB/KC/KD CCR 8XC196NT CCR0

| Bit 7 |      |      |      |     |    |     | Bit 0 |

|-------|------|------|------|-----|----|-----|-------|

| LOC1  | LOC0 | IRC1 | IRC0 | ALE | WR | BW0 | PD    |

|       |      |      |      |     |    |     |       |

| PD        | Powerdown Enable                 |

|-----------|----------------------------------|

| BW0       | Bus Width Control                |

| WR        | Select Write-Strobe Mode         |

| ALE       | Select Address-Valid-Strobe Mode |

| IRC0-IRC1 | Internal Ready Control           |

| LOC0-LOC1 | Lock Bits                        |

#### 8XC196NT CCR1

| Bit 7                                                                                              |       |       |              |                                                 |                              |                           | Bit 0                      |

|----------------------------------------------------------------------------------------------------|-------|-------|--------------|-------------------------------------------------|------------------------------|---------------------------|----------------------------|

| MSEL1                                                                                              | MSEL0 | 0     | 1            | WDE                                             | BW1                          | IRC2                      | LDCCB2                     |

| LDCCI                                                                                              | 32    | Lo    | ad CC        | B2                                              |                              |                           |                            |

| IRC2                                                                                               |       | Re    | ady C        | ontrol                                          |                              |                           |                            |

| BW1                                                                                                |       | Bu    | s Widt       | th Con                                          | trol                         |                           |                            |

| WDE                                                                                                |       | Wa    | itchdo       | g Tim                                           | er Ena                       | ıble                      |                            |

| MSELC                                                                                              | -MSEL | 1 Ext | ternal       | Access                                          | s Timi                       | ng Mo                     | de Select                  |

| These bits—MSEL0–MSEL1, con-<br>trol the bus-timing modes that have<br>been added to the 8XC196NT. |       |       |              |                                                 |                              |                           |                            |

| I                                                                                                  | MSEL1 | MSE   |              |                                                 |                              |                           |                            |

|                                                                                                    | 0     | 0     | v<br>a<br>e  | Standa<br>vait sta<br>nd TA<br>each 2<br>Mode ( | ate. Th<br>VDV<br>TOSC       | timin<br>longe            | LDV<br>gs are<br>er in     |

|                                                                                                    | 0     | 1     | a<br>t<br>b  |                                                 | the me<br>get its<br>hout t  | emory<br>s data<br>he wa  | more<br>on the<br>it-state |

|                                                                                                    | 1     | 0     | E<br>is<br>t | s simil                                         | Addres<br>ar to M<br>a longe | ss. Thi<br>Mode<br>er TRI | s mode                     |

|                                                                                                    | 1     | 1     | s            | Standa<br>hould<br>in 8XC                       | be use                       | ed to e                   | mulate                     |

#### 8XC196NT CCR2 8XC196NP CCR1

#### Bit 7

| Bit 7 |   |   |   |   |       |        | Bit 0 |

|-------|---|---|---|---|-------|--------|-------|

| 1     | 1 | 1 | 1 | 1 | REMAP | MODE16 | 0     |

#### MODE16 Addressing Mode

Selects 16- or 24-bit addressing.

0 = selects 24-bit addressing

1 = selects 16-bit addressing

REMAP OTPROM/internal ROM Mapping

Controls the internal OTPROM mapping.

0 = maps to page FF only

1 = maps to page 00 and FF

#### 8XC196NP CCR0

| Bit 7 |                       |                      |                |                          |         |           | Bit 0   |

|-------|-----------------------|----------------------|----------------|--------------------------|---------|-----------|---------|

| 1     | 1                     | WS1                  | WS0            | DEMUX                    | BHE#    | BW16      | PDEN    |

| PDEN  | PDEN Powerdown Enable |                      |                |                          |         |           |         |

| BW16  | ,                     | Bus W                | /idth (        | Control                  |         |           |         |

| BHE≉  | ¥                     | Write                | -contro        | ol Mode                  |         |           |         |

| DEM   | UX                    | Select               | Demu           | ltiplexed                | Bus     |           |         |

|       |                       |                      |                | lemultipl<br>h of CC     |         | is mode   | for an  |

|       |                       |                      | Demul<br>AD15: | tiplexed:<br>0.          | data    | u onl     | y on    |

|       |                       |                      |                | lexed: a<br>lexed on     |         |           | ata are |

| WS0-  | WS1                   | Wait S               | States         |                          |         |           |         |

|       |                       |                      | that a         | its contro<br>re used fo |         |           |         |

|       |                       | WS0                  | W              | S1                       |         |           |         |

|       |                       | 0 0 zero wait states |                |                          |         |           |         |

|       |                       | 0 1 one wait state   |                |                          |         |           |         |

|       |                       | 1 0 two wait states  |                |                          |         |           |         |

|       |                       | 1                    |                | 1 t                      | hree wa | ait state | es      |

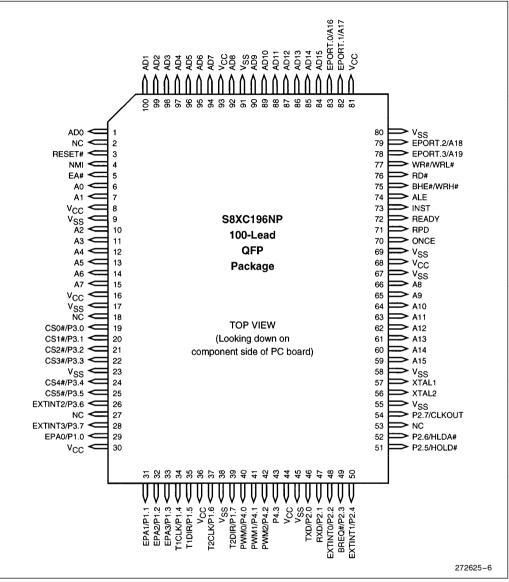

#### 5.0 HARDWARE

The 8XC196KB/KC/KD and 8XC196Nx parts are not socket compatible. The newer 8XC196NT and 8XC196NP have a more flexible EPA and pins were added to support the 1 Mbyte addressability of the 8XC196Nx parts. The addition of the Chip Select Unit and the Demultiplexed bus of the 8XC196NP requires a 100-ld package. This section outlines the differences in the pinouts and compares each of the pins on each device.

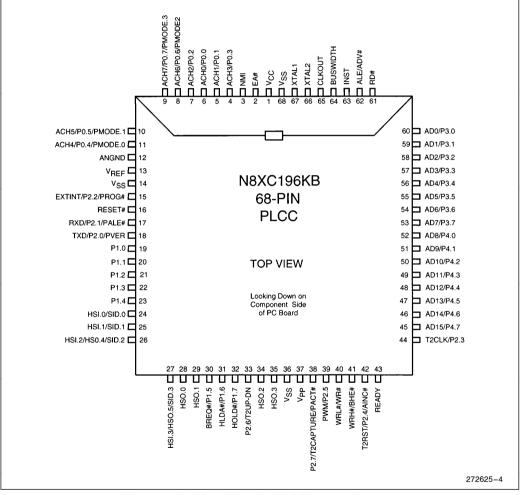

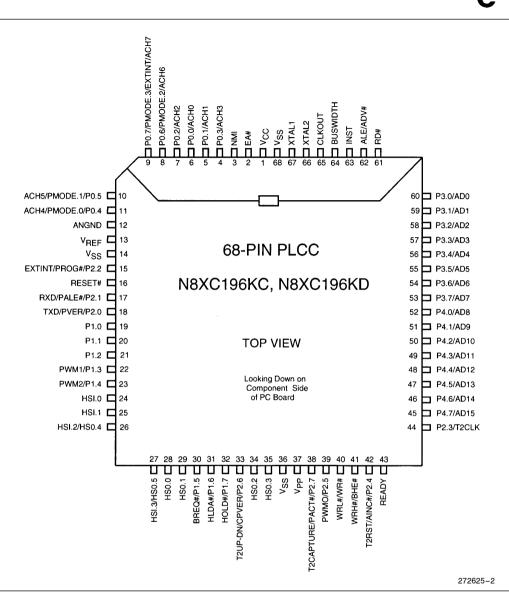

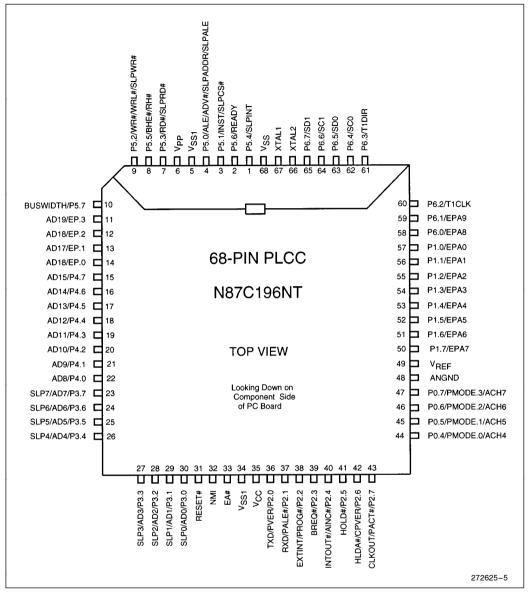

#### 5.1 Pinout Diagrams

Refer to current data sheets to get a complete package description.

Figure 5-1. N8XC196KB 68-Pin PLCC Package Diagram

in

Figure 5-2. N8XC196KC/KD 68-Pin PLCC Package Diagram

Figure 5-3. N8XC196NT 68-Pin PLCC Package Diagram

Figure 5-4. S8XC196NP 100-Pin QFP Package Diagram

### 5.2 Pin Differences

A Yes indicates that the pin is available. A No indicates that the pin is not available. An explanation is included when the pins are not the same for every device.

| Pin<br>Symbol | Pin<br>Description                                  | 8XC196KB                       | 8XC196KC/KD                                                                                               | 8XC196NT                                                                                                 | 8XC196NP                                                                                                                                        |

|---------------|-----------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-15         | System Address<br>Bus.                              | No. Bus is<br>Multiplexed.     | No. Bus is<br>Multiplexed.                                                                                | No. Bus is<br>Multiplexed.                                                                               | Yes.                                                                                                                                            |

| A16-19        | Address Lines<br>19–16.                             | No.                            | No.                                                                                                       | Yes. Shared with EPORT.0-3.                                                                              | Yes. Shared with EPORT.0-3.                                                                                                                     |

| ACH0-ACH7     | Analog Inputs.                                      | Yes. Shared with<br>Port 0.    | Yes. Shared with Port 0.                                                                                  | Yes. Shared with<br>Port 0. Has 4<br>channels<br>(ACH4–7).                                               | No A/D or Port 0.                                                                                                                               |

| AD0-15        | Multiplexed<br>address/data bus.                    | Yes. Shared with Port 3 and 4. | Yes. Shared with Port 3 and 4.                                                                            | Yes. Shared with<br>Port 3 and 4 and<br>the Slave Port<br>address/data bus.                              | Yes. Multiplexed in<br>multiplexed bus<br>mode. Data-only<br>bus in<br>demultiplexed bus<br>mode.                                               |

| AINC#         | Auto Increment.                                     | Yes. Shared with P2.4/T2RST.   | Yes. Shared with P2.4/T2RST.                                                                              | Yes. Shared with P2.4/INTOUT#.                                                                           | No. Programming<br>modes are not<br>supported.                                                                                                  |

| ALE/ADV#      | Address Latch<br>Enable or Address<br>Valid output. | Yes.                           | Yes.                                                                                                      | Yes. Shared with<br>P5.0/SLPADDR/<br>SLPALE.                                                             | Yes. ALE is used<br>in MUX BUS<br>mode. ADV# is<br>not needed for<br>chip select since<br>the Chip Select<br>Unit is used for this<br>function. |

| ANGND         | Reference ground<br>for the A/D<br>converter.       | Yes.                           | Yes.                                                                                                      | Yes.                                                                                                     | No A/D available.                                                                                                                               |

| BHE#          | Byte High Enable.                                   | Yes. Shared with WRH#.         | Yes. Shared with WRH#.                                                                                    | Yes. Shared with WRH # /P5.5.                                                                            | Yes. Shared with WRH#.                                                                                                                          |

| BREQ#         | Bus Request                                         | Yes. Shared with P1.5.         | Yes. Shared with P1.5.                                                                                    | Yes. Shared with P2.3.                                                                                   | Yes. Shared with P2.3.                                                                                                                          |

| BUSWIDTH      | Input for bus width selection.                      | Yes.                           | Yes.                                                                                                      | Yes. Shared with P5.7.                                                                                   | No. Not necessary<br>since bus width is<br>selected through<br>the Chip-Select<br>function.                                                     |

| CLKOUT        | Output of the<br>internal clock<br>generator.       | Yes.                           | Yes.                                                                                                      | Yes. Shared with P2.7/PACT.                                                                              | Yes. Shared with P2.7.                                                                                                                          |

| CPVER         | Cumulative<br>Program Output<br>Verification.       | No.                            | Yes. Verifies that<br>all locations have<br>been correctly<br>programmed.<br>Shared with P2.6/<br>T2UPDN. | Yes. Verifies that<br>all locations have<br>been correctly<br>programmed.<br>Shared with P2.6/<br>HLDA#. | No. Programming<br>modes are not<br>supported.                                                                                                  |

| CS0-5#        | Chip Select<br>Output.                              | No.                            | No.                                                                                                       | No.                                                                                                      | Yes. Shared with P3.0-5.                                                                                                                        |

| Pin<br>Symbol | Pin<br>Description                                                                                                                                                                       | 8XC196KB                                                                                                                                                                                                                 | 8XC196KC/KD                                                                                                                                                                                                              | 8XC196NT                                                                           | 8XC196NP                                                                                      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| EA#           | Input for memory<br>select (External<br>Access). $EA\# = 1$<br>directs memory<br>accesses to OTP/<br>ROM locations.<br>EA# = 0 directs<br>all memory<br>accesses to off-<br>chip memory. | Yes. EA# =<br>12.5V causes<br>execution to begin<br>in the<br>Programming<br>Mode.                                                                                                                                       | Yes. EA# =<br>12.5V causes<br>execution to begin<br>in the<br>Programming<br>Mode.                                                                                                                                       | Yes. EA# =<br>12.5V causes<br>execution to begin<br>in the<br>Programming<br>Mode. | Yes.                                                                                          |

| EPA pins      | Event Processor<br>Array I/O pins.                                                                                                                                                       | No EPA. Use<br>HSIO.                                                                                                                                                                                                     | No EPA. Use<br>HSIO.                                                                                                                                                                                                     | Yes (EPA0-9).<br>Shared with P1.0-<br>1.7 and P6.0-6.1/<br>T2CLK/T2DIR.            | Yes (EPA0–3).<br>Shared with<br>P1.0-3.                                                       |

| EPORT.0-3     | Extended Port.<br>4-bit bi-directional<br>I/O port.                                                                                                                                      | No EPORT.                                                                                                                                                                                                                | No EPORT.                                                                                                                                                                                                                | Yes. Shared with<br>the extended<br>address bus,<br>A16-A19.                       | Yes. Shared with<br>the extended<br>address bus,<br>A16-A19.                                  |

| EXTINTx       | External Interrupt.                                                                                                                                                                      | Yes. EXTINT pins<br>are shared with<br>P2.2/PROG# and<br>P0.7/PMOE.3/<br>ACH7. The IOC1.1<br>register<br>determines if the<br>EXTINT interrupt<br>source is P0.7 or<br>P2.2. The<br>EXTINT1 interrupt<br>source is P2.2. | Yes. EXTINT pins<br>are shared with<br>P2.2/PROG# and<br>P0.7/PMOE.3/<br>ACH7. The IOC1.1<br>register<br>determines if the<br>EXTINT interrupt<br>source is P0.7 or<br>P2.2. The<br>EXTINT1 interrupt<br>source is P2.2. | Yes. EXTINT is<br>shared with P2.2/<br>PROG #.                                     | Yes. 4 External<br>Interrupt signals:<br>EXTINT0-3.<br>Shared with P2.2,<br>P2.4, P3.6, P3.7. |

| HLDA#         | Bus Hold<br>Acknowledge.                                                                                                                                                                 | Yes. Shared with P1.6.                                                                                                                                                                                                   | Yes. Shared with P1.6.                                                                                                                                                                                                   | Yes. Shared with P2.6.                                                             | Yes. Shared with P2.6.                                                                        |

| HOLD#         | Bus Hold request input.                                                                                                                                                                  | Yes. Shared with P1.7.                                                                                                                                                                                                   | Yes. Shared with P1.7.                                                                                                                                                                                                   | Yes. Shared with P2.5.                                                             | Yes. Shared with P2.5.                                                                        |

| HSI           | Inputs to High<br>Speed Input.                                                                                                                                                           | Yes. HSI.0–3 are<br>shared with SID.<br>HSI.2–3 are<br>shared with<br>HSO.4–5.                                                                                                                                           | Yes. HSI.0 shared<br>with T2RST. HSI.1<br>is shared wtih<br>T2CLK. HSI.2–3<br>are shared with<br>HSO.4–5.                                                                                                                | No HSIO. Use<br>EPA.                                                               | No HSIO. Use<br>EPA.                                                                          |

| HSO           | Outputs from High<br>Speed Output.                                                                                                                                                       | Yes. HSO.4–5 are<br>shared with<br>HSI.2–3 and SID.                                                                                                                                                                      | Yes. HSO.4–5 are<br>shared with<br>HSI.2–3.                                                                                                                                                                              | No HSIO. Use<br>EPA.                                                               | No HSIO. Use<br>EPA.                                                                          |

| INST          | Instruction Fetch<br>Signal.                                                                                                                                                             | Yes.                                                                                                                                                                                                                     | Yes.                                                                                                                                                                                                                     | Yes. Shared with P5.1/SLPCS#.                                                      | Yes.                                                                                          |

| NMI           | Non-Maskable<br>interrupt.                                                                                                                                                               | Yes. Vectors<br>through 203EH.                                                                                                                                                                                           | Yes. Vectors<br>through 203EH.                                                                                                                                                                                           | Yes. Vectors<br>through<br>0FF203EH.                                               | Yes. Vectors<br>through<br>0FF203EH.                                                          |

| Pin<br>Symbol | Pin<br>Description               | 8XC196KB                                                                                                                                                                                                                                                                                                                | 8XC196KC/KD                                                                                                                                                                                                                                                                                           | 8XC196NT                                                                                                                                                                                                                                                                                                                                | 8XC196NP                                                                                                                                                                                                                             |

|---------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ONCE          | On-circuit<br>Emulation pin.     | No. ONCE mode<br>entered by driving<br>ALE high, INST<br>low and RD# low<br>on the rising edge<br>of RESET #.                                                                                                                                                                                                           | No. ONCE mode is<br>entered if P2.0 is<br>held low during the<br>rising edge of<br>RESET #.                                                                                                                                                                                                           | No. ONCE mode is<br>entered if HLDA#<br>(P2.6) is held low<br>during the rising<br>edge of RESET#.                                                                                                                                                                                                                                      | Yes. ONCE mode<br>is entered if the<br>ONCE pin is held<br>high during the<br>rising edge of<br>RESET#.                                                                                                                              |

| PACT#         | Programming<br>Active.           | Yes. Shared with P2.7/<br>T2CAPTURE.                                                                                                                                                                                                                                                                                    | Yes. Shared with P2.7/<br>T2CAPTURE.                                                                                                                                                                                                                                                                  | Yes. Shared with P2.7/CLKOUT.                                                                                                                                                                                                                                                                                                           | No. Programming<br>modes are not<br>supported.                                                                                                                                                                                       |

| PALE#         | Programming ALE.                 | Yes. Shared with P2.1/RXD.                                                                                                                                                                                                                                                                                              | Yes. Shared with P2.1/RXD.                                                                                                                                                                                                                                                                            | Yes. Shared with P2.1/RXD.                                                                                                                                                                                                                                                                                                              | No. Programming<br>modes are not<br>supported.                                                                                                                                                                                       |

| PMODE.0-3     | Programming<br>Mode Select Pins. | Yes. Shared with<br>Port 0 pins (also<br>A/D channels).                                                                                                                                                                                                                                                                 | Yes. Shared with<br>Port 0 pins (also<br>A/D channels).                                                                                                                                                                                                                                               | Yes. Shared with<br>Port 0 pins (also<br>A/D channels).                                                                                                                                                                                                                                                                                 | No. Programming<br>modes are not<br>supported.                                                                                                                                                                                       |

| Port 0        | Input-only port.                 | Yes. Also used for<br>A/D converter<br>inputs and<br>programming<br>modes.                                                                                                                                                                                                                                              | Yes. Also used for<br>A/D converter<br>inputs and<br>programming<br>modes. P0.7 is<br>shared with<br>EXTINT.                                                                                                                                                                                          | Yes. Also used for<br>A/D converter<br>inputs (ACH4-7)<br>and programming<br>modes.                                                                                                                                                                                                                                                     | No Port 0 or A/D.                                                                                                                                                                                                                    |

| Port 1        | I/O port.                        | Yes. Quasi-<br>bidirectional. P1.5–<br>7 are shared with<br>BREQ#, HLDA#,<br>and HOLD#.                                                                                                                                                                                                                                 | Yes. Quasi-<br>bidirectional. P1.3–<br>4 are shared with<br>PWM1 and PWM2.<br>P1.5–7 are shared<br>with BREQ#,<br>HLDA#, and<br>HOLD#.                                                                                                                                                                | Yes. P1.0–7 are<br>shared with the<br>EPA, T2CLK, and<br>T2DIR.                                                                                                                                                                                                                                                                         | Yes. P1.0-3 are<br>shared with the<br>EPA. P1.4 is<br>shared with<br>T1CLK. P1.5 is<br>shared with T1DIR.<br>P1.6 is shared with<br>T2CLK. P1.7 is<br>shared with T2DIR.                                                             |

| Port 2        | Multi-functional<br>port.        | Yes. P2.0 is<br>shared with TXD/<br>PVER#. P2.1 is<br>shared with RXD/<br>PALE#. P2.2 is<br>shared with<br>EXTINT/PROG#.<br>P2.3 is shared with<br>T2CLK. P2.4 is<br>shared with T2RST<br>and AINC#. P2.5<br>is shared with<br>PWM. P2.6 is<br>shared with<br>T2UPDN. P2.7 is<br>shared with<br>T2CAPTURE and<br>PACT#. | Yes. P2.0 is<br>shared with TXD/<br>PVER#. P2.1 is<br>shared with RXD/<br>PALE#. P2.2 is<br>shared with<br>EXTINT/PROG#.<br>P2.3 is shared with<br>T2CLK. P2.4 is<br>shared with T2RST<br>and AINC#. P2.5<br>is shared with<br>T2UPDN and<br>CPVER. P2.7 is<br>shared with<br>T2CAPTURE and<br>PACT#. | Yes. P2.0 is<br>shared with TXD/<br>PVER#. P2.1 is<br>shared with RXD/<br>PALE#. P2.2 is<br>shared with<br>EXTINT/PROG#.<br>P2.3 is shared with<br>BREQ#. P2.4 is<br>shared with<br>INTOUT# and<br>AINC#. P2.5 is<br>shared with<br>HOLD#. P2.6 is<br>shared with<br>HLDA# and<br>CPVER. P2.7 is<br>shared with<br>CLKOUT and<br>PACT#. | Yes. P2.0-2 are<br>shared with TXD,<br>RXD and<br>EXTINTO. P2.3 is<br>shared with<br>BREQ #. P2.4 is<br>shared with<br>EXTINT1. P2.5 is<br>shared with<br>HOLD #. P2.6 is<br>shared with<br>HLDA#. P2.7 is<br>shared with<br>CLKOUT. |

| Pin<br>Symbol   | Pin<br>Description                           | 8XC196KB                                                                                                                                                           | 8XC196KC/KD                                                                                                                                               | 8XC196NT                                                                                                                                                  | 8XC196NP                                                                                                                                                       |

|-----------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 3<br>and 4 | Bidirectional I/O<br>ports.                  | Yes. Shared with<br>multiplexed<br>address/data bus<br>and PVAL. During<br>programming, used<br>to pass commands,<br>addresses, and<br>data to and from<br>slaves. | Yes. Shared with<br>multiplexed<br>address/data bus.<br>During<br>programming, used<br>to pass commands,<br>addresses, and<br>data to and from<br>slaves. | Yes. Shared with<br>multiplexed<br>address/data bus.<br>During<br>programming, used<br>to pass commands,<br>addresses, and<br>data to and from<br>slaves. | Yes. P3.0–5 are<br>shared with CS0–<br>5# (Chip-Select<br>output). P3.6–7 are<br>shared with<br>EXTINT2–3. P4.0–<br>2 are shared with<br>PWM0–2. No<br>P4.4–7. |

| Port 5          | 8-bit standard I/O port.                     | No Port 5.                                                                                                                                                         | No Port 5.                                                                                                                                                | Yes. Shared with<br>several other pins<br>(Bus and Slave-<br>Port pins).                                                                                  | No Port 5.                                                                                                                                                     |

| Port 6          | 8-bit standard I/O port.                     | No Port 6.                                                                                                                                                         | No Port 6.                                                                                                                                                | Yes. Shared with<br>several other pins<br>(EPA, Timer 1, and<br>SSIO pins).                                                                               | No Port 6.                                                                                                                                                     |

| PROG#           | Programming Start.                           | Yes. Shared with P2.2/EXTINT.                                                                                                                                      | Yes. Shared with P2.2/EXTINT.                                                                                                                             | Yes. Shared with P2.2/EXTINT.                                                                                                                             | No. Programming<br>modes are not<br>supported.                                                                                                                 |

| PVAL#           | Program Valid.                               | Yes. Indicates<br>success or failure in<br>Auto Programming<br>Mode.                                                                                               | No.                                                                                                                                                       | No.                                                                                                                                                       | No. Programming<br>modes not<br>supported.                                                                                                                     |