# 87C196JV 20 MHz Specification Update

**Automotive**

**December 1998**

**Notice:** The 87C196JV may contain design defects or errors known as errata. Characterized errata that may cause the 87C196JV's behavior to deviate from published specifications are documented in this specification update.

Order Number: 272860-006

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 87C196JV may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1997

\*Third-party brands and names are the property of their respective owners.

# int<sub>e</sub>l。 *Contents*

| Revision History             | . 1 |

|------------------------------|-----|

| Preface                      | . 2 |

| Summary Table of Changes     | . 3 |

| dentification Information    | . 5 |

| Errata                       | . 6 |

| Specification Changes        | . 7 |

| Specification Clarifications | . 8 |

| Documentation Changes        | 11  |

# **Revision History**

| Date     | Version | Description                                                                                         |

|----------|---------|-----------------------------------------------------------------------------------------------------|

| 03/26/96 | 001     | This is the new Specification Update document. It contains all errata published prior to this date. |

| 01/08/97 | 002     | Added documentation changes 1–3.                                                                    |

| 04/07/97 | 003     | Added errata 1 and specification change 2.                                                          |

| 08/21/97 | 004     | Added document changes 4 and 5.                                                                     |

| 12/23/97 | 005     | Revised Specification Change 1, "mA" maximum value.                                                 |

| 12/23/97 | 005     | Added Specification Change 3.                                                                       |

| 11/30/98 | 006     | Added errata 2. Revised Affected Documents.                                                         |

# **Preface**

As of July, 1996, Intel's Computing Enhancement Group has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### **Affected Documents/Related Documents**

| Title                                                                        | Order  |

|------------------------------------------------------------------------------|--------|

| Automotive Products Handbook 1996                                            | 231792 |

| 87C196KR, 87C196JV, 87C196JT, 87C196JR, and 87C196CA Data Sheet - Automotive | 270827 |

| 8XC196Kx, 8XC196Jx, 87C196CA Microcontroller Family User's Manual            | 272258 |

| 87C196JV 20 MHz Advanced 16-Bit CHMOS Microcontroller Data Sheet             | 272580 |

#### **Nomenclature**

**Errata** are design defects or errors. These may cause the Product Name's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

*Note:* Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

# **Summary Table of Changes**

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the Product Name product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

#### **Codes Used in Summary Table**

#### Stepping

| X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------|--|--|

| (No mark)       |                                                                                                               |  |  |

| or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |  |  |

| (Page):         | Page location of item in this document.                                                                       |  |  |

| Doc:            | Document change or update will be implemented.                                                                |  |  |

| Fix:            | This erratum is intended to be fixed in a future step of the component.                                       |  |  |

| Fixed:          | This erratum has been previously fixed.                                                                       |  |  |

| NoFix:          | There are no plans to fix this erratum.                                                                       |  |  |

| Eval:           | Plans to fix this erratum are under evaluation.                                                               |  |  |

#### Row

Page

**Status**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

#### **Errata**

| No. | Steppings |   | Page Status | ERRATA |        |                                                                                               |

|-----|-----------|---|-------------|--------|--------|-----------------------------------------------------------------------------------------------|

| NO. | Α         | # | #           | l age  | otatus |                                                                                               |

| 1   | Х         |   |             | 6      | NoFix  | Executing Routines in the User's ROM While the Device is Operating in Serial Programming Mode |

| 2   | Х         |   |             | 6      | NoFix  | A/D Conversion Error on First Conversion                                                      |

#### **Specification Changes**

|   | No.   | Steppings |   |   | Page | Status      | SPECIFICATION CHANGES                                  |                       |

|---|-------|-----------|---|---|------|-------------|--------------------------------------------------------|-----------------------|

|   | NO. A | Α         | # | # | rage | raye Status | Status                                                 | SPECIFICATION CHANGES |

| ĺ | 1     | Х         |   |   | 7    |             | DC Characteristics, Idle Mode Current                  |                       |

|   | 2     | Х         |   |   | 7    |             | A/D Conversion Times                                   |                       |

| ĺ | 3     | Х         |   |   | 7    |             | Digital and Analog Supply Voltage Operating Conditions |                       |

### **Specification Clarifications**

| No. | Steppings |   | Page | Status | SPECIFICATION CLARIFICATIONS |                                        |

|-----|-----------|---|------|--------|------------------------------|----------------------------------------|

|     | Α         | # | #    | Fage   | Tage Status                  | SI EGINEATION CEANINGATIONS            |

| 1   | Х         |   |      | 8      |                              | EPA Timer Reset/Write Conflict         |

| 2   | Х         |   |      | 8      |                              | Valid Time Matches                     |

| 3   | Х         |   |      | 8      |                              | P6REG.47 Not Updated Immediately       |

| 4   | Х         |   |      | 8      |                              | Write Cycle During Reset               |

| 5   | Х         |   |      | 8      |                              | Indirect Shift Count Value             |

| 6   | Х         |   |      | 8      |                              | P2.7 (CLKOUT)                          |

| 7   | Х         |   |      | 9      |                              | EPA Overruns                           |

| 8   | Х         |   |      | 10     |                              | Indirect Addressing With AutoIncrement |

| 9   | Х         |   |      | 11     |                              | JV Additional Register RAM             |

#### **Documentation Changes**

| No. | Document Revision | Page | Status | DOCUMENTATION CHANGES                                                |

|-----|-------------------|------|--------|----------------------------------------------------------------------|

| 1   | 272258-002        | 12   | Doc    | High address inputs to the low EPROM should be A14:8 in Figure 15-18 |

| 2   | 272258-002        | 13   | Doc    | Addresses 201DH and 201FH should contain FFH in Table 4-2            |

| 3   | 272258-002        | 13   | Doc    | In Table 7-2, P2_DIR description change                              |

| 4   | 231792-009        | 14   | Doc    | Section 7, Page 5-100, Port 5 Register Behavior                      |

| 5   | 272580-003        | 14   | Doc    | Section 7, Page 18, Port 5 Register Behavior                         |

# **Identification Information**

### Markings

A-step devices can be identified by the letter "A" following the eight-digit FPO number on the top of the package.

# Errata

### 1. Executing Routines in the User's ROM While the Device is Operating in Serial Programming Mode

- **Problem:** All code fetches above the first 8K bytes of user ROM while the device is operating in serial port programming mode will be directed to external memory. Therefore, if the user wants to call any routines in the user ROM, the entire routine must be within the first 8K bytes of memory (0A000 0BFFFH in serial port programming mode). For example, if the RISM "GO" command is used with a target address of 0C000H, the device will attempt to fetch code from external memory rather than the on-board ROM.

- **Implication:** This errata only affects code fetches from the user ROM. Data fetches to the entire ROM work correctly. It is not possible to execute code from above the first 8K byte of user ROM while the device is operating in Serial Port Programming mode.

- Workaround: None.

- Status: NoFix. Refer to Summary Table of Changes to determine affected stepping(s).

#### 2. A/D Conversion Error on First Conversion

- **Problem:** The first A/D conversion performed after a reset of the device may produce a result that is less accurate than the accuracy specification in the datasheet. The amount of error is dependent on several environmental conditions including process variation, light exposure, temperature, and  $V_{CC}/V_{REF}$  differential.

- **Implication:** If the application is sensitive to A/D accuracy, an error in the application may occur as a result of the first conversion error.

- **Workaround:** Do not compare for the A/D result on the first conversion. All subsequent conversions should produce accurate results.

NoFix. Refer to the Summary Table of Changes to determine the affected.

# **Specification Changes**

#### 1. DC Characteristics, Idle Mode Current

**Problem:** The DC Characteristics Idle Mode Current specification has been revised from a maximum of 30 mA to a maximum of 40 mA.

#### 2. A/D Conversion Times

**Issue:** The second paragraph on the datasheet cover page incorrectly states the A/D conversion time as "< 5  $\mu$ s". The correction reads: "...analog-to-digital converter with programmable S/H times with conversion times < 15  $\mu$ s at 16 MHz,..."

#### 3. Digital and Analog Supply Voltage Operating Conditions

- **Issue:** The Digital Supply Voltage (VCC) and Analog Supply Voltage (Vref) Operating Conditions have been revised from 4.5 V-5.5 V to 4.75 V-5.25 V.

- **Implication:** The operating conditions for the digital and analog power supplies on the device are now specified to only tolerate a 5% deviation from the 5 V power supply in the application as opposed to the previous 10% deviation tolerance.

Affected Docs: 87C196JV 20MHz Advanced 16-Bit CHMOS Microcontroller - Automotive datasheet - 272580.

# **Specification Clarifications**

#### 1. EPA Timer Reset/Write Conflict

**Problem:** If software writes to the EPA timer at the same time that an EPA channel resets that timer, it is indeterminate which action will take precedence. Software should not write to a timer that is being reset by EPA signals.

#### 2. Valid Time Matches

**Problem:** A timer must increment or decrement to the compare value in order for a match to occur. Loading a timer with a value that is equal to an EPA compare value does cause a match. Likewise, with an EPA compare value of 0, a timer reset does not cause a match.

#### 3. P6\_\_REG.4-.7 Not Updated Immediately

**Problem:** A value written to any of the upper four bits of P6\_REG is temporarily held in a buffer until the corresponding P6\_MODE bit is cleared, at which time the value is loaded into the P6\_REG bit. A value read from a P6\_REG bit is the value currently in the register, not the value in the buffer. Therefore, any change to a P6\_REG bit can be read only after the corresponding P6\_MODE bit is cleared.

#### 4. Write Cycle During Reset

**Problem:** If a reset occurs while the microcontroller is writing to an external memory device, the contents of the external memory device may be corrupted.

#### 5. Indirect Shift Count Value

- **Problem:** The SHRL and SHLL instructions function correctly with count values 0–31, inclusive. However, a shift count value of XX100000B causes 32 shifts, which results in no shift taking place. With all other count values, the upper 3 bits are masked off and the remaining bits specify the number of shifts. Also, a shift count value of XX1XXXXXB causes the overflow flag and the overflow-trap flag to be set.

- Implication: Customers using SHRL and SHLL instructions with a count value greater than 31 will be affected.

- Workaround: Ensure that the count value never exceeds 31.

- Status: There are no plans to fix this.

#### 6. P2.7 (CLKOUT)

Problem: P2.7 (CLKOUT) does not operate in open drain mode.

#### 7. EPA Overruns

**Problem:**

The EPA can lock up if overruns are handled incorrectly. Overruns occur when an EPA input transitions at a rate that cannot be handled by the EPA interrupt service routine. If no overrun handling strategy is in place, and if the following three conditions exist, a situation may occur where both the capture buffer and the EPAx\_TIME register contain data, and no EPA interrupt pending bit is set:

- an input signal with a frequency high enough to cause overruns is present on an enabled EPA pin, and

- the overwrite bit is set (EPAx\_CON.0 = 1; old data is overwritten on overrun), and

- the EPAx\_TIME register is read at the exact instant that the EPA recognizes the captured edge as valid.

The input frequency at which this occurs depends on the length of the interrupt service routine as well as other factors. Unless the interrupt service routine includes a check for overruns, this situation will remain the same until the device is reset or the EPAx\_TIME register is read. The act of reading EPAx\_TIME allows the buffered time value to be moved into EPAx\_TIME. This clears the buffer and allows another event to be captured. Remember that the act of transferring the buffer contents to the EPAx\_TIME register is what actually sets the EPAx interrupt pending bit and generates the interrupt.

Workaround: Any one of the following methods can be used to prevent or recover from an EPA overrun situation.

Clear EPAx\_CON.0

When the overwrite bit (EPAx\_CON.0) is zero and both the EPAx\_TIME register than the buffer are full, the EPA does not consider a captured edge until the EPAx\_TIME register is read and the data in the capture buffer is transferred to EPAx\_TIME. This prevents overruns by ignoring new input capture events when both the capture buffer and EPAx\_TIME contain valid capture times. The OVRx pending bit in EPA PEND is set to indicate that an overrun occurred.

Enable the OVRx interrupt and read the EPAx\_TIME register within the ISR

If an overrun occurs, the overrun (OVRx) interrupt will be generated. The OVRx interrupt will then be acknowledged and its interrupt service routine will read the EPAx\_TIME register. After the CPU reads the EPAx\_TIME register, the buffered data moves from the buffer to the EPAx\_TIME register. This sets the EPA interrupt pending bit.

Check for pending EPAx interrupts before exiting an EPAx ISR

Another method for avoiding this situation is to check for pending EPA interrupts before exiting the EPA interrupt service routine. This is an easy way to detect overruns and additional interrupts. It can also save loop time by eliminating the latency necessary to service the pending interrupt. However, this method cannot be used with the peripheral transaction server (PTS).

Status: This is a design consideration. There are no plans to fix it.

INT

#### 8. Indirect Addressing With AutoIncrement

**Problem:**

For indirect address0ith autoincrement, a pointer that points to itself results in an access to the incremented pointer address rather than the original pointer address.

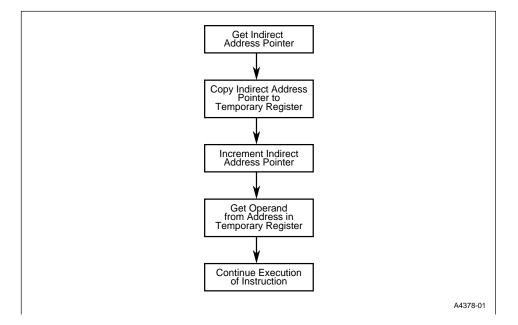

The CPU stores the pointer's value in a temporary register, increments the pointer, then accesses the operand at the address contained in the temporary register, as shown in this flowchart.

Therefore, if the pointer points to itself, the CPU accesses the operand at the incremented address contained in the pointer.

For example, assume ax = 1CH and bx = 40H. The following code causes the CPU to access the operand at the incremented address:

|             | ld<br>ldb                                                                                                                                                   | ax,#ax<br>bx,[ax]+     |                                                                                                                                                                                                                                       |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|             | ld<br>ldb                                                                                                                                                   | 1CH,#1CH<br>40H,[1CH]+ | ;1CH ←1CH;load location 1CH with value 1CH<br>;temp←1CH;save 1CH into temp register<br>;1CH←1DH;increment the contents of 1CH<br>;40H←1DH;load the contents of location 1CH<br>(location 1CH<br>;now contains the value 1DH) into 40H |  |  |  |

| Workaround: | Avoid                                                                                                                                                       | using an indirect      | address pointer that points to itself.                                                                                                                                                                                                |  |  |  |

|             | For example, assume $ax = 1CH$ , $bx = 1DH$ , and $cx = 40H$ . The following code causes the CPU access the operand at the intended, unincremented address: |                        |                                                                                                                                                                                                                                       |  |  |  |

|             | ld<br>ldb                                                                                                                                                   | ax,#bx<br>cx,[ax]+     | ;where bx≠ax                                                                                                                                                                                                                          |  |  |  |

|             | ld<br>ldb                                                                                                                                                   | 1CH,#1DH<br>40H,[1CH]+ | ;1CH←1DH;load location 1CH with value 1DH<br>;temp←1DH;save 1DH (contents of 1CH) into temp<br>register<br>;1CH←1EH;increment the contents of 1CH<br>;40H←1DH;load the contents of temp into 40H                                      |  |  |  |

| Status:     | This is                                                                                                                                                     | the intended ope       | ration. There are no plans to change it.                                                                                                                                                                                              |  |  |  |

to

intel

#### 9. JV Additional Register RAM

Issue:

The 8XC196JV has a total of 1.5 Kbytes of register RAM. The RAM is located in two memory ranges: 000h-03FFh and 1C00h-1DFFh.

# **Documentation Changes**

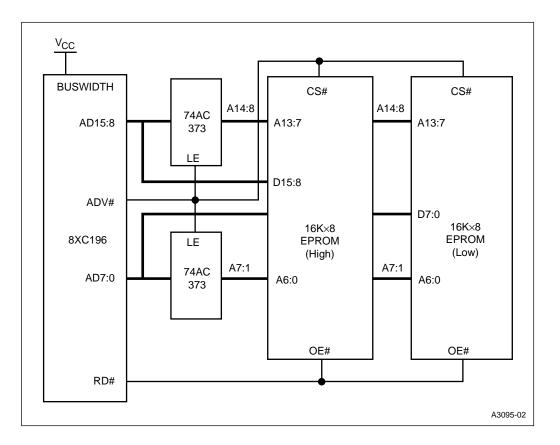

1. High address inputs to the low EPROM should be A14:8 in Figure 15-18

Issue:

The next revision of the user's manual will include the following corrected graphic.

#### Figure 1. 16-bit System with EPROM

#### 2. Addresses 201DH and 201FH should contain FFH in Table 4-2

Issue:

The next revision of the user's manual will include the following corrected table.

#### Table 1. Special-purpose Memory Addresses

| Hex Address  | Description                             |

|--------------|-----------------------------------------|

| 207F<br>205E | Reserved (each byte must contain FFH)   |

| 205D<br>2040 | PTS vectors                             |

| 203F<br>2030 | Upper interrupt vectors                 |

| 202F<br>2020 | Security key                            |

| 201F         | Reserved (must contain FFH)             |

| 201E         | Reserved (must contain FFH)             |

| 201D         | Reserved (must contain FFH)             |

| 201C         | Reserved (must contain FFH)             |

| 201B         | Reserved (must contain 20H)             |

| 201A         | CCB1                                    |

| 2019         | Reserved (must contain 20H)             |

| 2018         | ССВО                                    |

| 2017<br>2016 | OFD flag (see Page 13-12 and Page 16-8) |

| 2015<br>2014 | Reserved (each byte must contain FFH)   |

| 2013<br>2000 | Lower interrupt vectors                 |

#### 3. In Table 7-2, P2\_DIR description change

Issue:

The next revision of the user's manual will include the following corrected register description.

| Mnemonic | Address | Description                                                                                                                                                                                                                                         |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2_DIR   | 1FCBH   | Port Direction Register                                                                                                                                                                                                                             |

|          |         | Each bit controls the configuration of the corresponding pin.<br>Clearing a bit configures the corresponding pin as a complementary<br>output; setting a bit configures the corresponding pin as an<br>open-drain output or a high-impedance input. |

INT

#### 4. Section 7, Page 5-100, Port 5 Register Behavior

Issue:

Description of behavior of bits associated with unbonded-out pins P5.1, P5.4, P5.5, P5.6 and P5.7 in registers P5\_PIN, P5\_MODE, P5\_REG, and P5\_DIR has been changed.

Entire Section 7 (including Table) under "87C196JR/JQ C-STEP TO JV A-STEP DESIGN CONSIDERATIONS":

• Old section 7

On the JR-C, P5.1, P5.4, P5.5, P5.6 and P5.7 are not bonded out but are present internally on the device.

This allows the programmer to write to the port registers and clear, set or read the pin even though it is not available to the outside world. However, to maintain compatibility with JT A-step, JV A-step and future devices, it is recommended that the corresponding bits associated with the removed pins not be used to conditionally branch in software. These bits should be treated as reserved.

On the JT A-step and JV A-step unused port logic for these five port pins has been removed from the device and is not available to the programmer. Corresponding bits in the port registers have been "hardwired" to provide the following results when read:

| Register I | When<br>Read      |   |

|------------|-------------------|---|

| P5_PIN.x   | (x=1,4,5,6,7)     | 1 |

| P5_REG.x   | (x=1,4,5,6,7)     | 1 |

| P5_DIR.x   | (x=1,4,5,6,7)     | 1 |

| P5_MODE.x  | (x=1,4,6)         | 0 |

| P5_MODE.x  | (x = 5) (EA# = 0) | 1 |

| P5_MODE.x  | (x = 5) (EA# = 1) | 0 |

| P5_MODE.x  | (x = 7)           | 1 |

Writing to these bits will have no effect.

New Section 7

On the JR-C, P5.1, P5.4, P5.5, P5.6 and P5.7 are not bonded out but are present internally on the device. This allows the programmer to write to the port registers and clear, set or read the pin even though it is not available to the outside world.

On the JT A-step and JV A-step unused port logic for these five port pins has been removed. The data read from the P5\_PIN, P5\_REG, P5\_MODE, and P5\_DIR register bits associated with these removed pins can be unpredictable on these devices due to the removed logic. Therefore, these bits should not be used to conditionally branch in software. These bits should be treated as reserved.

Affected Docs: Automotive Products Handbook - 231792, 87C196JV 20MHz Advanced 16-Bit CHMOS Microcontroller Datasheet - 272580

#### 5. Section 7, Page 18, Port 5 Register Behavior

(Same as Document Change #004 above).