## **EMBEDDED Intel486<sup>™</sup> SX PROCESSOR**

- 32-Bit RISC Technology Core

- 8-Kbyte Write-Through Cache

- **■** Four Internal Write Buffers

- Burst Bus Cycles

- Dynamic Bus Sizing for 8- and 16-bit Data Bus Devices

- SL Technology

- Data Bus Parity Generation and Checking

- **■** Boundary Scan (JTAG)

- 3.3-Volt Processor

- 208-Lead Shrink Quad Flat Pack (SQFP)

- 5-Volt Processor

- 196-Lead Plastic Quad Flat Pack (PQFP)

- Binary Compatible with Large Software Base

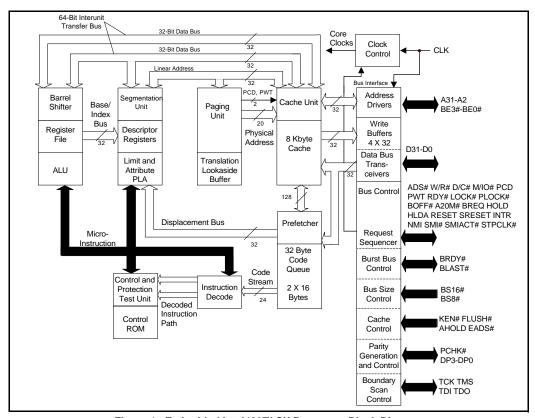

Figure 1. Embedded Intel486™ SX Processor Block Diagram

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microprocessor products may have minor variations to this specification known as errata.

© INTEL CORPORATION, 1995 October 1995 Order Number: 272769-001

# EMBEDDED Intel486<sup>™</sup> SX PROCESSOR

| 1.0  | INTROD   | UCTION                                                                                                                  | 1  |

|------|----------|-------------------------------------------------------------------------------------------------------------------------|----|

|      | 1.1 Fea  | tures                                                                                                                   | 1  |

|      | 1.2 Fan  | nily Members                                                                                                            | 2  |

| 2.0  | HOW TO   | USE THIS DOCUMENT                                                                                                       | 3  |

| 3.0  | PIN DES  | CRIPTIONS                                                                                                               | 3  |

|      | 3.1 Pin  | Assignments                                                                                                             | 3  |

|      | 3.2 Pin  | Quick Reference                                                                                                         | 15 |

| 4.0  | ARCHIT   | ECTURAL AND FUNCTIONAL OVERVIEW                                                                                         | 22 |

|      | 4.1 CPI  | JID Instruction                                                                                                         | 23 |

|      | 4.1      | 1 Operation of the CPUID Instruction                                                                                    | 23 |

|      | 4.2 Ider | ntification After Reset                                                                                                 | 24 |

|      | 4.3 Bou  | ndary Scan (JTAG)                                                                                                       | 24 |

|      | 4.3      | 1 Device Identification                                                                                                 | 24 |

|      | 4.3      | 2 Boundary Scan Register Bits and Bit Order                                                                             | 25 |

| 5.0  | ELECTR   | ICAL SPECIFICATIONS                                                                                                     | 26 |

|      | 5.1 Max  | rimum Ratings                                                                                                           | 26 |

|      | 5.2 DC   | Specifications                                                                                                          | 26 |

|      | 5.3 AC   | Specifications                                                                                                          | 31 |

|      |          | pacitive Derating Curves                                                                                                |    |

| 6.0  |          | NICAL DATA                                                                                                              |    |

|      |          | kage Dimensions                                                                                                         |    |

|      | 6.2 Pac  | kage Thermal Specifications                                                                                             | 43 |

| -10  | LIDEO    |                                                                                                                         |    |

|      | URES     | Forbodde Literate OV Donner on Divid Discourse                                                                          |    |

| _    | ure 1.   | Embedded Intel486™ SX Processor Block Diagram                                                                           |    |

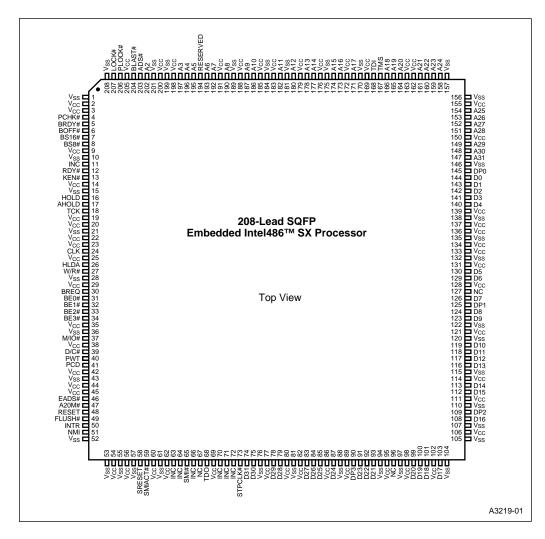

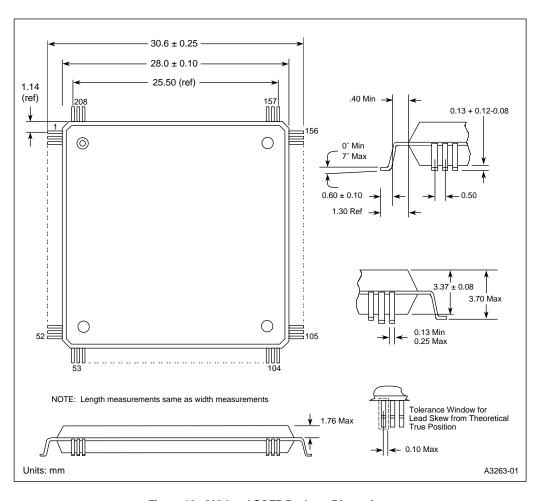

| -    | ıre 2.   | Package Diagram for 208-Lead SQFP Embedded Intel486™ SX Processor                                                       |    |

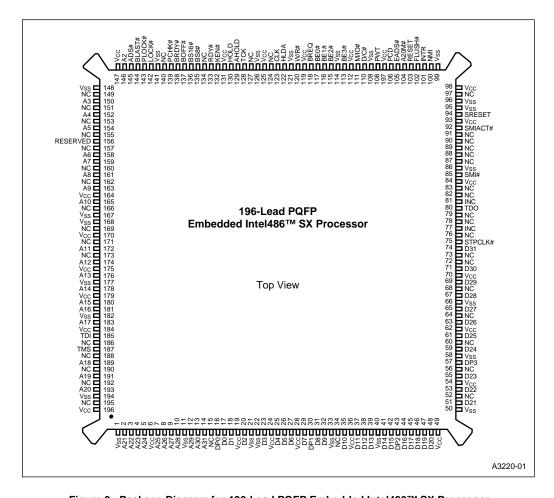

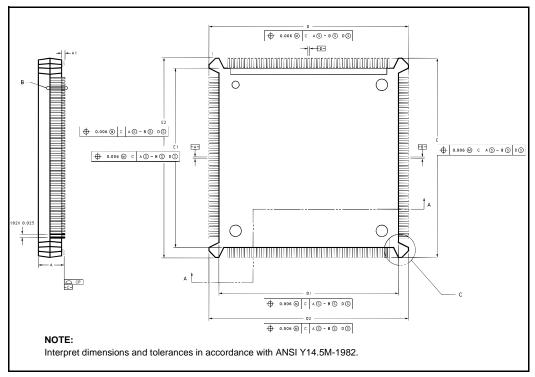

| _    | ure 3.   | Package Diagram for 196-Lead PQFP Embedded Intel486™ SX Processor                                                       |    |

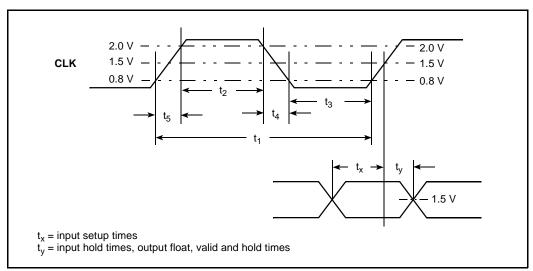

| •    | ıre 4.   | CLK Waveform                                                                                                            |    |

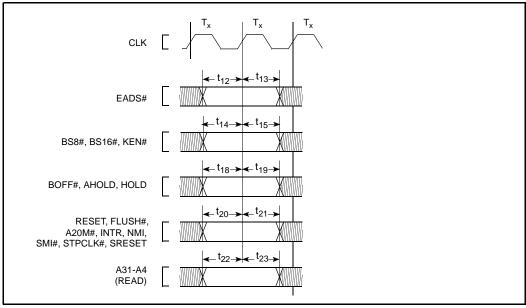

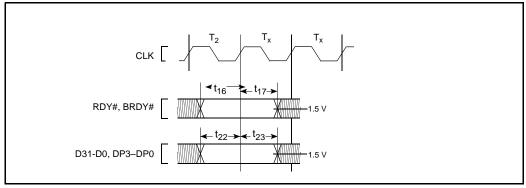

| _    | ıre 5.   | Input Setup and Hold Timing                                                                                             |    |

| -    | ıre 6.   | Input Setup and Hold Timing                                                                                             |    |

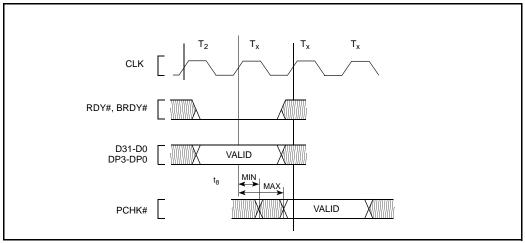

| Figu | ıre 7.   | PCHK# Valid Delay Timing                                                                                                | 35 |

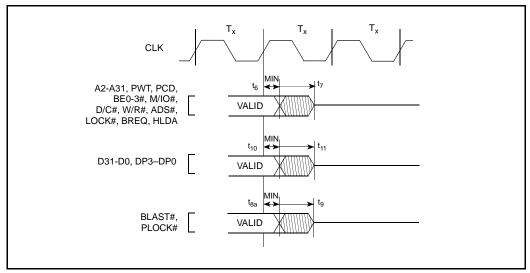

| Figu | ıre 8.   | Output Valid Delay Timing                                                                                               | 35 |

| Figu | ıre 9.   | Maximum Float Delay Timing                                                                                              | 36 |

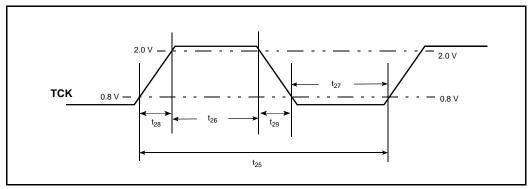

| Figu | ure 10.  | TCK Waveform                                                                                                            | 36 |

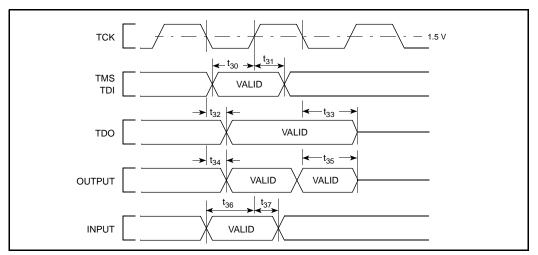

| Figu | ure 11.  | Test Signal Timing Diagram                                                                                              | 37 |

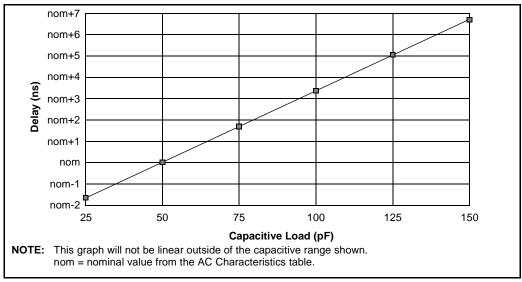

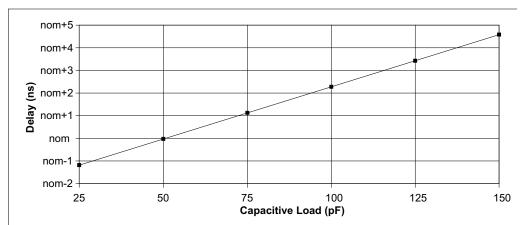

| Figu | ıre 12.  | Typical Loading Delay versus Load Capacitance under Worst-Case Conditions for a Low-to-High Transition, 3.3 V Processor | 38 |

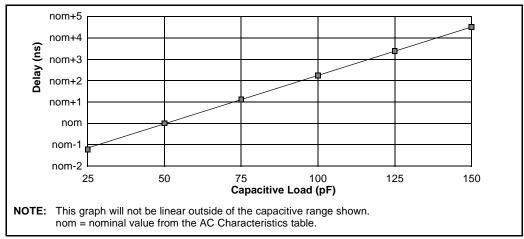

| Figu | ure 13.  | Typical Loading Delay versus Load Capacitance under Worst-Case Conditions for a High-to-Low Transition, 3.3 V Processor | 38 |

## **CONTENTS**

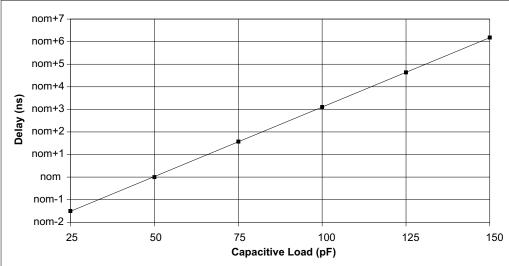

| Figure 14. | Typical Loading Delay versus Load Capacitance under Worst-Case Conditions for a Low-to-High Transition, 5 V Processor | 39 |

|------------|-----------------------------------------------------------------------------------------------------------------------|----|

| Figure 15. | Typical Loading Delay versus Load Capacitance under Worst-Case Conditions for a High-to-Low Transition, 5 V Processor | 39 |

| Figure 16. | 208-Lead SQFP Package Dimensions                                                                                      |    |

| Figure 17. | Principal Dimensions and Data for 196-Lead Plastic Quad Flat Pack Package                                             |    |

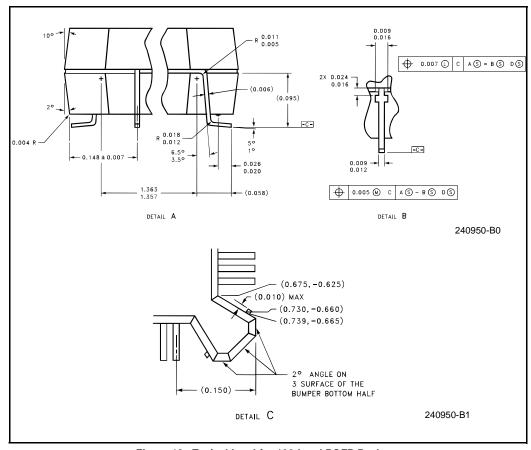

| Figure 18. | Typical Lead for 196-Lead PQFP Package                                                                                |    |

| TABLES     |                                                                                                                       |    |

| Table 1.   | The Embedded Intel486™ SX Processor Family                                                                            | 2  |

| Table 2.   | Pinout Differences for 208-Lead SQFP Package                                                                          | 5  |

| Table 3.   | Pin Assignment for 208-Lead SQFP Package                                                                              | 6  |

| Table 4.   | Pin Cross Reference for 208-Lead SQFP Package                                                                         | 8  |

| Table 5.   | Pin Assignment for 196-Lead PQFP Package                                                                              | 11 |

| Table 6.   | Pin Cross Reference for 196-Lead PQFP Package                                                                         | 13 |

| Table 7.   | Embedded Intel486™ SX Processor Pin Descriptions                                                                      | 15 |

| Table 8.   | Output Pins                                                                                                           | 21 |

| Table 9.   | Input/Output Pins                                                                                                     | 21 |

| Table 10.  | Test Pins                                                                                                             | 21 |

| Table 11.  | Input Pins                                                                                                            | 22 |

| Table 12.  | CPUID Instruction Description                                                                                         | 23 |

| Table 13.  | Boundary Scan Component Identification Code (3.3 Volt Processor)                                                      | 24 |

| Table 14.  | Boundary Scan Component Identification Code (5 Volt Processor)                                                        | 25 |

| Table 15.  | Absolute Maximum Ratings                                                                                              | 26 |

| Table 16.  | Operating Supply Voltages                                                                                             | 26 |

| Table 17.  | 3.3 V DC Specifications                                                                                               | 27 |

| Table 18.  | 3.3 V I <sub>CC</sub> Values                                                                                          | 28 |

| Table 19.  | 5 V DC Specifications                                                                                                 | 29 |

| Table 20.  | 5 V I <sub>CC</sub> Values                                                                                            | 30 |

| Table 21.  | AC Characteristics                                                                                                    | 31 |

| Table 22.  | AC Specifications for the Test Access Port                                                                            | 33 |

| Table 23.  | Symbol List and Dimensions for 196-Lead PQFP Package                                                                  | 41 |

| Table 24.  | Thermal Resistance, $\theta_{JA}$ (°C/W)                                                                              | 43 |

| Table 25.  | Thermal Resistance, $\theta_{JC}$ (°C/W)                                                                              | 43 |

| Table 26.  | Maximum T <sub>ambient</sub> , T <sub>A</sub> max (°C)                                                                | 43 |

#### 1.0 INTRODUCTION

The embedded Intel486™ SX processor provides high performance to 32-bit, embedded applications. Designed for applications that do not need a floating-point unit, the processor is ideal for embedded designs running DOS\*, Microsoft\* Windows\*, OS/2\*, or UNIX\* applications written for the Intel architecture. Projects can be completed quickly by utilizing the wide range of software tools, utilities, assemblers and compilers that are available for desktop computer systems. Also, developers can find advantages in using existing chipsets and peripheral components in their embedded designs.

The embedded Intel486 SX processor is binary compatible with the Intel386™ and earlier Intel processors. Compared with the Intel386 processor, it provides faster execution of many commonly-used instructions. It also provides the benefits of an integrated, 8-Kbyte, write-through cache for code and data. Its data bus can operate in burst mode which provides up to 106-Mbyte-per-second transfers for cache-line fills and instruction prefetches.

Intel's SL technology is incorporated in the embedded Intel486 SX processor. Utilizing Intel's System Management Mode (SMM), it enables designers to develop energy-efficient systems.

Two component packages are available. A 196-lead Plastic Quad Flat Pack (PQFP) is available for 5-Volt designs and a 208-lead Shrink Quad Flat Pack (SQFP) is available for 3.3-Volt designs. Both products operate at CLK frequencies up to 33 MHz.

### 1.1 Features

The embedded Intel486 SX processor offers these features:

- 32-bit RISC-Technology Core The embedded Intel486 SX processor performs a complete set of arithmetic and logical operations on 8-, 16-, and 32-bit data types using a full-width ALU and eight general purpose registers.

- Single Cycle Execution Many instructions execute in a single clock cycle.

- Other brands and names are the property of their respective owners.

- Instruction Pipelining Overlapped instruction fetching, decoding, address translation and execution.

- On-Chip Cache with Cache Consistency Support — An 8-Kbyte, write-through, internal cache is used for both data and instructions. Cache hits provide zero wait-state access times for data within the cache. Bus activity is tracked to detect alterations in the memory represented by the internal cache. The internal cache can be invalidated or flushed so that an external cache controller can maintain cache consistency.

- External Cache Control Write-back and flush controls for an external cache are provided so the processor can maintain cache consistency.

- On-Chip Memory Management Unit Address management and memory space protection mechanisms maintain the integrity of memory in a multitasking and virtual memory environment. Both memory segmentation and paging are supported.

- Burst Cycles Burst transfers allow a new double-word to be read from memory on each bus clock cycle. This capability is especially useful for instruction prefetch and for filling the internal cache

- Write Buffers The processor contains four write buffers to enhance the performance of consecutive writes to memory. The processor can continue internal operations after a write to these buffers, without waiting for the write to be completed on the external bus.

- Bus Backoff When another bus master needs control of the bus during a processor initiated bus cycle, the embedded Intel486 SX processor floats its bus signals, then restarts the cycle when the bus becomes available again.

- Instruction Restart Programs can continue execution following an exception generated by an unsuccessful attempt to access memory. This feature is important for supporting demand-paged virtual memory applications.

- Dynamic Bus Sizing External controllers can dynamically alter the effective width of the data bus. Bus widths of 8, 16, or 32 bits can be used.

- Boundary Scan (JTAG) Boundary Scan provides in-circuit testing of components on printed circuit boards. The Intel Boundary Scan implementation conforms with the IEEE Standard Test Access Port and Boundary Scan Architecture.

#### Embedded Intel486™ SX Processor

Intel's SL technology provides these features:

- Intel System Management Mode (SMM) A

unique Intel architecture operating mode provides

a dedicated special purpose interrupt and address

space that can be used to implement intelligent

power management and other enhanced functions

in a manner that is completely transparent to the

operating system and applications software.

- VO Restart An I/O instruction interrupted by a System Management Interrupt (SMI#) can automatically be restarted following the execution of the RSM instruction.

- Stop Clock The embedded Intel486 SX processor has a stop clock control mechanism that provides two low-power states: a Stop Grant state (20–40 mA typical, depending on input clock

- frequency) and a Stop Clock state ( $\sim$ 100-200  $\mu$ A typical, with input clock frequency of 0 MHz).

- Auto HALT Power Down After the execution of a HALT instruction, the embedded Intel486 SX processor issues a normal Halt bus cycle and the clock input to the processor core is automatically stopped, causing the processor to enter the Auto HALT Power Down state (20–40 mA typical, depending on input clock frequency).

## 1.2 Family Members

Table 1 shows the embedded Intel486 SX processors and briefly describes their characteristics.

Table 1. The Embedded Intel486™ SX Processor Family

| Product       | Supply Voltage<br>V <sub>CC</sub> | Maximum Processor<br>Frequency | Package       |  |  |

|---------------|-----------------------------------|--------------------------------|---------------|--|--|

| SB80486SXSC33 | 3.3 V                             | 33 MHz                         | 208-Lead SQFP |  |  |

| KU80486SXSA33 | 5.0 V                             | 33 MHz                         | 196-Lead PQFP |  |  |

#### 2.0 HOW TO USE THIS DOCUMENT

For a complete set of documentation related to the embedded Intel486 SX processor, use this document in conjunction with the following reference documents:

- Intel486™ Processor Family datasheet Order No. 242202

- Intel486<sup>™</sup> Microprocessor Family Programmer's Reference Manual — Order No. 240486

- Intel Application Note AP-485 Intel Processor Identification with the CPUID Instruction — Order No. 241618

The information in the reference documents for the Intel486 SX processor, 1X Clock (CLK), applies to the embedded Intel486 SX processor. Some of the Intel486 SX processor information is duplicated in this document to minimize the dependence on the reference documents.

#### 3.0 PIN DESCRIPTIONS

### 3.1 Pin Assignments

The following figures and tables show the pin assignments of each package type for the embedded Intel486 SX processor. Tables are provided showing the pin differences between the embedded Intel486 SX processor and other embedded Intel486 processor products.

208-Lead SQFP - Quad Flat Pack

- Figure 2, Package Diagram for 208-Lead SQFP Embedded Intel486™ SX Processor (pg. 4)

- Table 2, Pinout Differences for 208-Lead SQFP Package (pg. 5)

- Table 3, Pin Assignment for 208-Lead SQFP Package (pg. 6)

- Table 4, Pin Cross Reference for 208-Lead SQFP Package (pg. 8)

196-Lead PQFP - Plastic Quad Flat Pack

- Figure 3, Package Diagram for 196-Lead PQFP Embedded Intel486™ SX Processor (pg. 10)

- Table 5, Pin Assignment for 196-Lead PQFP Package (pg. 11)

- Table 6, Pin Cross Reference for 196-Lead PQFP Package (pg. 13)

Figure 2. Package Diagram for 208-Lead SQFP Embedded Intel486™ SX Processor

Table 2. Pinout Differences for 208-Lead SQFP Package

| Pin # | Embedded<br>Intel486™ SX<br>Processor | Embedded<br>IntelDX2™<br>Processor | Embedded Write-Back<br>Enhanced IntelDX4™<br>Processor |

|-------|---------------------------------------|------------------------------------|--------------------------------------------------------|

| 3     | v <sub>cc</sub> <sup>1</sup>          | V <sub>CC</sub>                    | V <sub>CC5</sub>                                       |

| 11    | INC <sup>2</sup>                      | INC                                | CLKMUL                                                 |

| 63    | INC                                   | INC                                | HITM#                                                  |

| 64    | INC                                   | INC                                | WB/WT#                                                 |

| 66    | INC                                   | FERR#                              | FERR#                                                  |

| 70    | INC                                   | INC                                | CACHE#                                                 |

| 71    | INC                                   | INC                                | INV                                                    |

| 72    | INC                                   | IGNNE#                             | IGNNE#                                                 |

- This pin location is for the V<sub>CC5</sub> pin on the embedded IntelDX4 processor. For compatibility with 3.3V processors that have 5V-tolerant input buffers (i.e., embedded IntelDX4 processors), this pin should be connected to a V<sub>CC</sub> trace, not to the V<sub>CC</sub> plane.

- INC. Internal No Connect. These pins are not connected to any internal pad in the embedded Intel486 SX processor.

However, new signals are defined for the location of the INC pins in the embedded IntelDX2 and IntelDX4 processors.

One system design can accommodate any one of these processors provided the purpose of each INC pin is understood before it is used.

Table 3. Pin Assignment for 208-Lead SQFP Package (Sheet 1 of 2)

| Pin# | Description       | Pin# | Description      | Pin# | Description     | Pin# | Description     |

|------|-------------------|------|------------------|------|-----------------|------|-----------------|

| 1    | V <sub>SS</sub>   | 53   | V <sub>SS</sub>  | 105  | V <sub>SS</sub> | 157  | V <sub>SS</sub> |

| 2    | V <sub>CC</sub>   | 54   | V <sub>CC</sub>  | 106  | V <sub>CC</sub> | 158  | A24             |

| 3    | v <sub>cc</sub> 1 | 55   | V <sub>SS</sub>  | 107  | V <sub>SS</sub> | 159  | A23             |

| 4    | PCHK#             | 56   | V <sub>CC</sub>  | 108  | D16             | 160  | A22             |

| 5    | BRDY#             | 57   | V <sub>SS</sub>  | 109  | DP2             | 161  | A21             |

| 6    | BOFF#             | 58   | SRESET           | 110  | V <sub>SS</sub> | 162  | V <sub>CC</sub> |

| 7    | BS16#             | 59   | SMIACT#          | 111  | V <sub>CC</sub> | 163  | V <sub>CC</sub> |

| 8    | BS8#              | 60   | V <sub>CC</sub>  | 112  | D15             | 164  | A20             |

| 9    | V <sub>CC</sub>   | 61   | V <sub>SS</sub>  | 113  | D14             | 165  | A19             |

| 10   | V <sub>SS</sub>   | 62   | V <sub>CC</sub>  | 114  | V <sub>CC</sub> | 166  | A18             |

| 11   | INC <sup>2</sup>  | 63   | INC <sup>2</sup> | 115  | V <sub>SS</sub> | 167  | TMS             |

| 12   | RDY#              | 64   | INC <sup>2</sup> | 116  | D13             | 168  | TDI             |

| 13   | KEN#              | 65   | SMI#             | 117  | D12             | 169  | V <sub>CC</sub> |

| 14   | V <sub>CC</sub>   | 66   | INC <sup>2</sup> | 118  | D11             | 170  | V <sub>SS</sub> |

| 15   | V <sub>SS</sub>   | 67   | NC <sup>3</sup>  | 119  | D10             | 171  | A17             |

| 16   | HOLD              | 68   | TDO              | 120  | V <sub>SS</sub> | 172  | V <sub>CC</sub> |

| 17   | AHOLD             | 69   | V <sub>CC</sub>  | 121  | V <sub>CC</sub> | 173  | A16             |

| 18   | TCK               | 70   | INC <sup>2</sup> | 122  | V <sub>SS</sub> | 174  | A15             |

| 19   | V <sub>CC</sub>   | 71   | INC <sup>2</sup> | 123  | D9              | 175  | V <sub>SS</sub> |

| 20   | V <sub>CC</sub>   | 72   | INC <sup>2</sup> | 124  | D8              | 176  | V <sub>CC</sub> |

| 21   | V <sub>SS</sub>   | 73   | STPCLK#          | 125  | DP1             | 177  | A14             |

| 22   | V <sub>CC</sub>   | 74   | D31              | 126  | D7              | 178  | A13             |

| 23   | Vcc               | 75   | D30              | 127  | NC <sup>3</sup> | 179  | V <sub>CC</sub> |

| 24   | CLK               | 76   | V <sub>SS</sub>  | 128  | V <sub>CC</sub> | 180  | A12             |

| 25   | V <sub>CC</sub>   | 77   | V <sub>CC</sub>  | 129  | D6              | 181  | V <sub>SS</sub> |

| 26   | HLDA              | 78   | D29              | 130  | D5              | 182  | A11             |

| 27   | W/R#              | 79   | D28              | 131  | V <sub>CC</sub> | 183  | V <sub>CC</sub> |

| 28   | V <sub>SS</sub>   | 80   | V <sub>CC</sub>  | 132  | V <sub>SS</sub> | 184  | V <sub>SS</sub> |

| 29   | Vcc               | 81   | V <sub>SS</sub>  | 133  | V <sub>CC</sub> | 185  | V <sub>CC</sub> |

| 30   | BREQ              | 82   | V <sub>CC</sub>  | 134  | V <sub>CC</sub> | 186  | A10             |

| 31   | BE0#              | 83   | D27              | 135  | V <sub>SS</sub> | 187  | A9              |

| 32   | BE1#              | 84   | D26              | 136  | V <sub>CC</sub> | 188  | V <sub>CC</sub> |

| Table 3. Pin Assignment for 208-Lead SQFP Package (Sheet 2 of 2 | Table 3. | Pin Assid | anment for | 208-Lead | SQFP Package | (Sheet 2 of 2 |

|-----------------------------------------------------------------|----------|-----------|------------|----------|--------------|---------------|

|-----------------------------------------------------------------|----------|-----------|------------|----------|--------------|---------------|

| Pin# | Description     | Pin# | Description     | Pin# | Description     | Pin# | Description     |

|------|-----------------|------|-----------------|------|-----------------|------|-----------------|

| 33   | BE2#            | 85   | D25             | 137  | V <sub>CC</sub> | 189  | V <sub>SS</sub> |

| 34   | BE3#            | 86   | v <sub>cc</sub> | 138  | V <sub>SS</sub> | 190  | A8              |

| 35   | V <sub>CC</sub> | 87   | D24             | 139  | V <sub>CC</sub> | 191  | V <sub>CC</sub> |

| 36   | V <sub>SS</sub> | 88   | V <sub>SS</sub> | 140  | D4              | 192  | A7              |

| 37   | M/IO#           | 89   | v <sub>cc</sub> | 141  | D3              | 193  | A6              |

| 38   | V <sub>CC</sub> | 90   | DP3             | 142  | D2              | 194  | RESERVED        |

| 39   | D/C#            | 91   | D23             | 143  | D1              | 195  | A5              |

| 40   | PWT             | 92   | D22             | 144  | D0              | 196  | A4              |

| 41   | PCD             | 93   | D21             | 145  | DP0             | 197  | А3              |

| 42   | V <sub>CC</sub> | 94   | V <sub>SS</sub> | 146  | V <sub>SS</sub> | 198  | V <sub>CC</sub> |

| 43   | V <sub>SS</sub> | 95   | v <sub>cc</sub> | 147  | A31             | 199  | $V_{SS}$        |

| 44   | V <sub>CC</sub> | 96   | NC <sup>3</sup> | 148  | A30             | 200  | V <sub>CC</sub> |

| 45   | V <sub>CC</sub> | 97   | V <sub>SS</sub> | 149  | A29             | 201  | V <sub>SS</sub> |

| 46   | EADS#           | 98   | v <sub>cc</sub> | 150  | V <sub>CC</sub> | 202  | A2              |

| 47   | A20M#           | 99   | D20             | 151  | A28             | 203  | ADS#            |

| 48   | RESET           | 100  | D19             | 152  | A27             | 204  | BLAST#          |

| 49   | FLUSH#          | 101  | D18             | 153  | A26             | 205  | V <sub>CC</sub> |

| 50   | INTR            | 102  | V <sub>CC</sub> | 154  | A25             | 206  | PLOCK#          |

| 51   | NMI             | 103  | D17             | 155  | V <sub>CC</sub> | 207  | LOCK#           |

| 52   | V <sub>SS</sub> | 104  | V <sub>SS</sub> | 156  | V <sub>SS</sub> | 208  | V <sub>SS</sub> |

- This pin location is for the V<sub>CC5</sub> pin on the embedded IntelDX4 processor. For compatibility with 3.3V processors that have 5V-tolerant input buffers (i.e., embedded IntelDX4 processors), this pin should be connected to a V<sub>CC</sub> trace, not to the V<sub>CC</sub> plane.

- INC. Internal No Connect. These pins are not connected to any internal pad in the embedded Intel486 SX processors.

However, signals are defined for the location of the INC pins in the embedded IntelDX2 and IntelDX4 processors. One system design can accommodate any one of these processors provided the purpose of each INC pin is understood before it is used.

- NC. Do Not Connect. These pins should always remain unconnected. Connection of NC pins to V<sub>CC</sub>, or V<sub>SS</sub> or to any other signal can result in component malfunction or incompatibility with future steppings of the Intel486 processors.

Table 4. Pin Cross Reference for 208-Lead SQFP Package (Sheet 1 of 2)

| Address | Pin# | Data | Pin # | Control  | Pin # | NC  | INC | V <sub>CC</sub> | V <sub>SS</sub> |

|---------|------|------|-------|----------|-------|-----|-----|-----------------|-----------------|

| A2      | 202  | D0   | 144   | A20M#    | 47    | 67  | 11  | 2               | 1               |

| А3      | 197  | D1   | 143   | ADS#     | 203   | 96  | 63  | 3               | 10              |

| A4      | 196  | D2   | 142   | AHOLD    | 17    | 127 | 64  | 9               | 15              |

| A5      | 195  | D3   | 141   | BE0#     | 31    |     | 66  | 14              | 21              |

| A6      | 193  | D4   | 140   | BE1#     | 32    |     | 70  | 19              | 28              |

| A7      | 192  | D5   | 130   | BE2#     | 33    |     | 71  | 20              | 36              |

| A8      | 190  | D6   | 129   | BE3#     | 34    |     | 72  | 22              | 43              |

| A9      | 187  | D7   | 126   | BLAST#   | 204   |     |     | 23              | 52              |

| A10     | 186  | D8   | 124   | BOFF#    | 6     |     |     | 25              | 53              |

| A11     | 182  | D9   | 123   | BRDY#    | 5     |     |     | 29              | 55              |

| A12     | 180  | D10  | 119   | BREQ     | 30    |     |     | 35              | 57              |

| A13     | 178  | D11  | 118   | BS16#    | 7     |     |     | 38              | 61              |

| A14     | 177  | D12  | 117   | BS8#     | 8     |     |     | 42              | 76              |

| A15     | 174  | D13  | 116   | CLK      | 24    |     |     | 44              | 81              |

| A16     | 173  | D14  | 113   | D/C#     | 39    |     |     | 45              | 88              |

| A17     | 171  | D15  | 112   | DP0      | 145   |     |     | 54              | 94              |

| A18     | 166  | D16  | 108   | DP1      | 125   |     |     | 56              | 97              |

| A19     | 165  | D17  | 103   | DP2      | 109   |     |     | 60              | 104             |

| A20     | 164  | D18  | 101   | DP3      | 90    |     |     | 62              | 105             |

| A21     | 161  | D19  | 100   | EADS#    | 46    |     |     | 69              | 107             |

| A22     | 160  | D20  | 99    | FLUSH#   | 49    |     |     | 77              | 110             |

| A23     | 159  | D21  | 93    | HLDA     | 26    |     |     | 80              | 115             |

| A24     | 158  | D22  | 92    | HOLD     | 16    |     |     | 82              | 120             |

| A25     | 154  | D23  | 91    | INTR     | 50    |     |     | 86              | 122             |

| A26     | 153  | D24  | 87    | KEN#     | 13    |     |     | 89              | 132             |

| A27     | 152  | D25  | 85    | LOCK#    | 207   |     |     | 95              | 135             |

| A28     | 151  | D26  | 84    | M/IO#    | 37    |     |     | 98              | 138             |

| A29     | 149  | D27  | 83    | NMI      | 51    |     |     | 102             | 146             |

| A30     | 148  | D28  | 79    | PCD      | 41    |     |     | 106             | 156             |

| A31     | 147  | D29  | 78    | PCHK#    | 4     |     |     | 111             | 157             |

|         |      | D30  | 75    | PLOCK#   | 206   |     |     | 114             | 170             |

|         |      | D31  | 74    | PWT      | 40    |     |     | 121             | 175             |

|         |      |      |       | RDY#     | 12    |     |     | 128             | 181             |

|         |      |      |       | RESERVED | 194   |     |     | 131             | 184             |

|         |      |      |       | RESET    | 48    |     |     | 133             | 189             |

|         |      |      |       | SMI#     | 65    |     |     | 134             | 199             |

|         |      |      |       | SMIACT#  | 59    |     |     | 136             | 201             |

|         |      |      |       | SRESET   | 58    |     |     | 137             | 208             |

|         |      |      |       | STPCLK#  | 73    |     |     | 139             |                 |

Table 4. Pin Cross Reference for 208-Lead SQFP Package (Sheet 2 of 2)

| Address | Pin# | Data | Pin# | Control | Pin# | NC | INC | V <sub>CC</sub> | V <sub>SS</sub> |

|---------|------|------|------|---------|------|----|-----|-----------------|-----------------|

|         |      |      |      | TCK     | 18   |    |     | 150             |                 |

|         |      |      |      | TDI     | 168  |    |     | 155             |                 |

|         |      |      |      | TDO     | 68   |    |     | 162             |                 |

|         |      |      |      | TMS     | 167  |    |     | 163             |                 |

|         |      |      |      | W/R#    | 27   |    |     | 169             |                 |

|         |      |      |      |         |      |    |     | 172             |                 |

|         |      |      |      |         |      |    |     | 176             |                 |

|         |      |      |      |         |      |    |     | 179             |                 |

|         |      |      |      |         |      |    |     | 183             |                 |

|         |      |      |      |         |      |    |     | 185             |                 |

|         |      |      |      |         |      |    |     | 188             |                 |

|         |      |      |      |         |      |    |     | 191             |                 |

|         |      |      |      |         |      |    |     | 198             |                 |

|         |      |      |      |         |      |    |     | 200             |                 |

|         |      |      |      |         |      |    |     | 205             |                 |

Figure 3. Package Diagram for 196-Lead PQFP Embedded Intel486™ SX Processor

Table 5. Pin Assignment for 196-Lead PQFP Package (Sheet 1 of 2)

| Pin# | Description     | Pin# | Description      | Pin# | Description     | Pin# | Description     |

|------|-----------------|------|------------------|------|-----------------|------|-----------------|

| 1    | V <sub>SS</sub> | 50   | V <sub>SS</sub>  | 99   | V <sub>SS</sub> | 148  | V <sub>ss</sub> |

| 2    | A21             | 51   | D21              | 100  | NMI             | 149  | NC <sup>1</sup> |

| 3    | A22             | 52   | NC <sup>1</sup>  | 101  | INTR            | 150  | A3              |

| 4    | A23             | 53   | D22              | 102  | FLUSH#          | 151  | NC <sup>1</sup> |

| 5    | A24             | 54   | V <sub>cc</sub>  | 103  | RESET           | 152  | A4              |

| 6    | V <sub>cc</sub> | 55   | D23              | 104  | A20M#           | 153  | NC <sup>1</sup> |

| 7    | A25             | 56   | NC <sup>1</sup>  | 105  | EADS#           | 154  | A5              |

| 8    | A26             | 57   | DP3              | 106  | PCD             | 155  | NC <sup>1</sup> |

| 9    | A27             | 58   | V <sub>SS</sub>  | 107  | V <sub>cc</sub> | 156  | RESERVED        |

| 10   | A28             | 59   | D24              | 108  | PWT             | 157  | NC <sup>1</sup> |

| 11   | V <sub>SS</sub> | 60   | NC <sup>1</sup>  | 109  | V <sub>SS</sub> | 158  | A6              |

| 12   | A29             | 61   | D25              | 110  | D/C#            | 159  | A7              |

| 13   | A30             | 62   | V <sub>cc</sub>  | 111  | M/IO#           | 160  | NC <sup>1</sup> |

| 14   | A31             | 63   | D26              | 112  | V <sub>cc</sub> | 161  | A8              |

| 15   | NC <sup>1</sup> | 64   | NC <sup>1</sup>  | 113  | BE3#            | 162  | NC <sup>1</sup> |

| 16   | DP0             | 65   | D27              | 114  | V <sub>SS</sub> | 163  | A9              |

| 17   | D0              | 66   | V <sub>SS</sub>  | 115  | BE2#            | 164  | V <sub>cc</sub> |

| 18   | D1              | 67   | D28              | 116  | BE1#            | 165  | A10             |

| 19   | V <sub>cc</sub> | 68   | NC <sup>1</sup>  | 117  | BE0#            | 166  | NC <sup>1</sup> |

| 20   | D2              | 69   | D29              | 118  | BREQ            | 167  | V <sub>SS</sub> |

| 21   | V <sub>SS</sub> | 70   | V <sub>cc</sub>  | 119  | V <sub>cc</sub> | 168  | V <sub>SS</sub> |

| 22   | V <sub>SS</sub> | 71   | D30              | 120  | W/R#            | 169  | NC <sup>1</sup> |

| 23   | D3              | 72   | NC <sup>1</sup>  | 121  | V <sub>SS</sub> | 170  | V <sub>cc</sub> |

| 24   | V <sub>cc</sub> | 73   | NC <sup>1</sup>  | 122  | HLDA            | 171  | NC <sup>1</sup> |

| 25   | D4              | 74   | D31              | 123  | CLK             | 172  | A11             |

| 26   | D5              | 75   | STPCLK#          | 124  | NC <sup>1</sup> | 173  | NC <sup>1</sup> |

| 27   | D6              | 76   | NC <sup>1</sup>  | 125  | V <sub>cc</sub> | 174  | A12             |

| 28   | V <sub>cc</sub> | 77   | INC <sup>2</sup> | 126  | V <sub>SS</sub> | 175  | V <sub>cc</sub> |

| 29   | D7              | 78   | NC <sup>1</sup>  | 127  | NC <sup>1</sup> | 176  | A13             |

| 30   | DP1             | 79   | NC <sup>1</sup>  | 128  | TCK             | 177  | V <sub>ss</sub> |

| 31   | D8              | 80   | TDO              | 129  | AHOLD           | 178  | A14             |

| 32   | D9              | 81   | INC <sup>2</sup> | 130  | HOLD            | 179  | V <sub>cc</sub> |

Table 5. Pin Assignment for 196-Lead PQFP Package (Sheet 2 of 2)

| Pin# | Description     | Pin# | Description     | Pin# | Description     | Pin# | Description     |

|------|-----------------|------|-----------------|------|-----------------|------|-----------------|

| 33   | V <sub>SS</sub> | 82   | NC <sup>1</sup> | 131  | V <sub>cc</sub> | 180  | A15             |

| 34   | NC <sup>1</sup> | 83   | NC <sup>1</sup> | 132  | KEN#            | 181  | A16             |

| 35   | D10             | 84   | V <sub>cc</sub> | 133  | RDY#            | 182  | V <sub>SS</sub> |

| 36   | V <sub>cc</sub> | 85   | SMI#            | 134  | NC <sup>1</sup> | 183  | A17             |

| 37   | D11             | 86   | V <sub>SS</sub> | 135  | BS8#            | 184  | V <sub>cc</sub> |

| 38   | D12             | 87   | NC <sup>1</sup> | 136  | BS16#           | 185  | TDI             |

| 39   | D13             | 88   | NC <sup>1</sup> | 137  | BOFF#           | 186  | NC <sup>1</sup> |

| 40   | V <sub>SS</sub> | 89   | NC <sup>1</sup> | 138  | BRDY#           | 187  | TMS             |

| 41   | D14             | 90   | NC <sup>1</sup> | 139  | PCHK#           | 188  | NC <sup>1</sup> |

| 42   | D15             | 91   | NC <sup>1</sup> | 140  | NC <sup>1</sup> | 189  | A18             |

| 43   | DP2             | 92   | SMIACT#         | 141  | V <sub>SS</sub> | 190  | NC <sup>1</sup> |

| 44   | D16             | 93   | V <sub>cc</sub> | 142  | LOCK#           | 191  | A19             |

| 45   | D17             | 94   | SRESET          | 143  | PLOCK#          | 192  | NC <sup>1</sup> |

| 46   | D18             | 95   | V <sub>SS</sub> | 144  | BLAST#          | 193  | A20             |

| 47   | D19             | 96   | V <sub>SS</sub> | 145  | ADS#            | 194  | V <sub>SS</sub> |

| 48   | D20             | 97   | NC <sup>1</sup> | 146  | A2              | 195  | NC <sup>1</sup> |

| 49   | V <sub>CC</sub> | 98   | V <sub>CC</sub> | 147  | V <sub>cc</sub> | 196  | V <sub>cc</sub> |

<sup>1.</sup> NC. Do Not Connect. These pins should always remain unconnected. Connection of NC pins to  $V_{CC}$ , or  $V_{SS}$  or to any other signal can result in component malfunction or incompatibility with future steppings of the Intel486 processors.

<sup>2.</sup> INC. Internal No Connect. These pins are not connected to any internal pad in the embedded Intel486 SX processors.

Table 6. Pin Cross Reference for 196-Lead PQFP Package (Sheet 1 of 2)

| Address | Pin# | Data | Pin# | Control  | Pin# | NC  | INC | V <sub>CC</sub> | V <sub>SS</sub> |

|---------|------|------|------|----------|------|-----|-----|-----------------|-----------------|

| A2      | 146  | D0   | 17   | A20M#    | 104  | 15  | 77  | 6               | 1               |

| А3      | 150  | D1   | 18   | ADS#     | 145  | 34  | 81  | 19              | 11              |

| A4      | 152  | D2   | 20   | AHOLD    | 129  | 52  |     | 24              | 21              |

| A5      | 154  | D3   | 23   | BE0#     | 117  | 56  |     | 28              | 22              |

| A6      | 158  | D4   | 25   | BE1#     | 116  | 60  |     | 36              | 33              |

| A7      | 159  | D5   | 26   | BE2#     | 115  | 64  |     | 49              | 40              |

| A8      | 161  | D6   | 27   | BE3#     | 113  | 68  |     | 54              | 50              |

| A9      | 163  | D7   | 29   | BLAST#   | 144  | 72  |     | 62              | 58              |

| A10     | 165  | D8   | 31   | BOFF#    | 137  | 73  |     | 70              | 66              |

| A11     | 172  | D9   | 32   | BRDY#    | 138  | 76  |     | 84              | 86              |

| A12     | 174  | D10  | 35   | BREQ     | 118  | 78  |     | 93              | 95              |

| A13     | 176  | D11  | 37   | BS16#    | 136  | 79  |     | 98              | 96              |

| A14     | 178  | D12  | 38   | BS8#     | 135  | 82  |     | 107             | 99              |

| A15     | 180  | D13  | 39   | CLK      | 123  | 83  |     | 112             | 109             |

| A16     | 181  | D14  | 41   | D/C#     | 110  | 87  |     | 119             | 114             |

| A17     | 183  | D15  | 42   | DP0      | 16   | 88  |     | 125             | 121             |

| A18     | 189  | D16  | 44   | DP1      | 30   | 89  |     | 131             | 126             |

| A19     | 191  | D17  | 45   | DP2      | 43   | 90  |     | 147             | 141             |

| A20     | 193  | D18  | 46   | DP3      | 57   | 91  |     | 164             | 148             |

| A21     | 2    | D19  | 47   | EADS#    | 105  | 97  |     | 170             | 167             |

| A22     | 3    | D20  | 48   | FLUSH#   | 102  | 124 |     | 175             | 168             |

| A23     | 4    | D21  | 51   | HLDA     | 122  | 127 |     | 179             | 177             |

| A24     | 5    | D22  | 53   | HOLD     | 130  | 134 |     | 184             | 182             |

| A25     | 7    | D23  | 55   | INTR     | 101  | 140 |     | 196             | 194             |

| A26     | 8    | D24  | 59   | KEN#     | 132  | 149 |     |                 |                 |

| A27     | 9    | D25  | 61   | LOCK#    | 142  | 151 |     |                 |                 |

| A28     | 10   | D26  | 63   | M/IO#    | 111  | 153 |     |                 |                 |

| A29     | 12   | D27  | 65   | NMI      | 100  | 155 |     |                 |                 |

| A30     | 13   | D28  | 67   | PCD      | 106  | 157 |     |                 |                 |

| A31     | 14   | D29  | 69   | PCHK#    | 139  | 160 |     |                 |                 |

|         |      | D30  | 71   | PLOCK#   | 143  | 162 |     |                 |                 |

|         |      | D31  | 74   | PWT      | 108  | 166 |     |                 |                 |

|         |      |      |      | RDY#     | 133  | 169 |     |                 |                 |

|         |      |      |      | RESERVED | 156  | 171 |     |                 |                 |

|         |      |      |      | RESET    | 103  | 173 |     |                 |                 |

|         |      |      |      | SMI#     | 85   | 186 |     |                 |                 |

|         |      |      |      | SMIACT#  | 92   | 188 |     |                 |                 |

Table 6. Pin Cross Reference for 196-Lead PQFP Package (Sheet 2 of 2)

| Address | Pin # | Data | Pin # | Control | Pin # | NC  | INC | V <sub>CC</sub> | V <sub>SS</sub> |

|---------|-------|------|-------|---------|-------|-----|-----|-----------------|-----------------|

|         |       |      |       | SRESET  | 94    | 190 |     |                 |                 |

|         |       |      |       | STPCLK# | 75    | 192 |     |                 |                 |

|         |       |      |       | TCK     | 128   | 195 |     |                 |                 |

|         |       |      |       | TDI     | 185   |     |     |                 |                 |

|         |       |      |       | TDO     | 80    |     |     |                 |                 |

|         |       |      |       | TMS     | 187   |     |     |                 |                 |

|         |       |      |       | W/R#    | 120   |     |     |                 |                 |

## 3.2 Pin Quick Reference

The following is a brief pin description. For detailed signal descriptions refer to "Signal Description" in section 9 of the *Intel486™ Processor Family* datasheet.

**Table 7. Embedded Intel486™ SX Processor Pin Descriptions** (Sheet 1 of 6)

| Symbol                       | Туре     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLK                          | I        | Clock provides the fundamental timing and internal operating frequency for the embedded Intel486 SX processor. All external timing parameters are specified wit respect to the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ADDRESS B                    | US       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| A31-A4<br>A3-A2              | I/O<br>O | Address Lines A31–A2, together with the byte enable signals, BE3#–BE0#, define the physical area of memory or input/output space accessed. Address lines A31–A4 are used to drive addresses into the embedded Intel486 SX processor to perform cache line invalidation. Input signals must meet setup and hold times t <sub>22</sub> and t <sub>23</sub> . A31–A2 are not driven during bus or address hold.                                                                                                                                                                                                                                                                                                                                                                                         |  |

| BE3#<br>BE2#<br>BE1#<br>BE0# | 0 0 0    | Byte Enable signals indicate active bytes during read and write cycles. During the first cycle of a cache fill, the external system should assume that all byte enables are active. BE3#_BE0# are active LOW and are not driven during bus hold.  BE3# applies to D31-D24  BE2# applies to D23-D16  BE1# applies to D15-D8                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DATA BUS                     |          | BE0# applies to D7–D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| D31-D0                       | I/O      | <b>Data Lines.</b> D7–D0 define the least significant byte of the data bus; D31–D24 define the most significant byte of the data bus. These signals must meet setup and hold times t <sub>22</sub> and t <sub>23</sub> for proper operation on reads. These pins are driven during the second and subsequent clocks of write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| DATA PARIT                   | Y        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| DP3-DP0                      | I/O      | There is one <b>Data Parity</b> pin for each byte of the data bus. Data parity is generated on all write data cycles with the same timing as the data driven by the embedded Intel486 SX processor. Even parity information must be driven back into the processor on the data parity pins with the same timing as read information to ensure that the correct parity check status is indicated by the embedded Intel486 SX processor. The signals read on these pins do not affect program execution. Input signals must meet setup and hold times t <sub>22</sub> and t <sub>23</sub> . DP3–DP0 must be connected to V <sub>CC</sub> through a pull-up resistor in systems that do not use parity. DP3–DP0 are active HIGH and are driven during the second and subsequent clocks of write cycles. |  |

| РСНК#                        | 0        | Parity Status is driven on the PCHK# pin the clock after ready for read operations. The parity status is for data sampled at the end of the previous clock. A parity error is indicated by PCHK# being LOW. Parity status is only checked for enabled bytes as indicated by the byte enable and bus size signals. PCHK# is valid only in the clock immediately after read data is returned to the processor. At all other times PCHK# is inactive (HIGH). PCHK# is never floated.                                                                                                                                                                                                                                                                                                                    |  |

Table 7. Embedded Intel486™ SX Processor Pin Descriptions (Sheet 2 of 6)

| Symbol                | Туре                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               | Name and Fun                                                                                                                                         | ction                                                                              |             |  |  |

|-----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------|--|--|

| <b>BUS CYCLE</b>      | BUS CYCLE DEFINITION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |                                                                                                                                                      |                                                                                    |             |  |  |

| M/IO#<br>D/C#<br>W/R# | 0 0 0                | definition signal M/IO# D/C# 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | s. These sig                  | nals are driven valing Bus Cycle Inition Interrupt Acknown HALT/Special Color I/O Readol I/O Write Code Readol Reservedol Memory Readol Memory Write |                                                                                    |             |  |  |

|                       |                      | Cycle Nan<br>Shutdown<br>HALT<br>Stop Gran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               | <b>BE3# - BE0#</b><br>1110<br>1011<br>1011                                                                                                           | <b>A4-A2</b> 000 000 100                                                           |             |  |  |

| LOCK#                 | 0                    | Bus Lock indicates that the current bus cycle is locked. The embedded Intel486 SX processor does not allow a bus hold when LOCK# is asserted (address holds are allowed). LOCK# goes active in the first clock of the first locked bus cycle and goes inactive after the last clock of the last locked bus cycle. The last locked cycle ends when Ready is returned. LOCK# is active LOW and not driven during bus hold. Locked read cycles are not transformed into cache fill cycles when KEN# is returned active.                                                                                                                       |                               |                                                                                                                                                      |                                                                                    |             |  |  |

| PLOCK#                | 0                    | Pseudo-Lock indicates that the current bus transaction requires more than one bus cycle to complete. For the embedded Intel486 SX processor, examples of such operations are segment table descriptor reads (64 bits) and cache line fills (128 bits).  The embedded Intel486 SX processor drives PLOCK# active until the addresses for the last bus cycle of the transaction are driven, regardless of whether RDY# or BRDY# have been returned.  PLOCK# is a function of the BS8#, BS16# and KEN# inputs. PLOCK# should be sampled only in the clock in which Ready is returned. PLOCK# is active LOW and is not driven during bus hold. |                               |                                                                                                                                                      |                                                                                    |             |  |  |

| BUS CONTR             | OL                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                                                                                                                                                      |                                                                                    |             |  |  |

| ADS#                  | 0                    | available on the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | cycle definit<br>hich the add | ion lines and addre                                                                                                                                  | us cycle definition and addess bus. ADS# is driven act<br>ADS# is active LOW and r | tive in the |  |  |

Table 7. Embedded Intel486™ SX Processor Pin Descriptions (Sheet 3 of 6)

| Symbol    | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDY#      | I    | Non-burst Ready input indicates that the current bus cycle is complete. RDY# indicates that the external system has presented valid data on the data pins in response to a read or that the external system has accepted data from the embedded Intel486 SX processor in response to a write. RDY# is ignored when the bus is idle and at the end of the first clock of the bus cycle.                                                                                                                                                                              |

|           |      | RDY# is active during address hold. Data can be returned to the embedded Intel486 SX processor while AHOLD is active.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           |      | RDY# is active LOW and is not provided with an internal pull-up resistor. RDY# must satisfy setup and hold times $t_{16}$ and $t_{17}$ for proper chip operation.                                                                                                                                                                                                                                                                                                                                                                                                   |

| BURST CON | TROL |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BRDY#     | I    | <b>Burst Ready</b> input performs the same function during a burst cycle that RDY# performs during a non-burst cycle. BRDY# indicates that the external system has presented valid data in response to a read or that the external system has accepted data in response to a write. BRDY# is ignored when the bus is idle and at the end of the first clock in a bus cycle.                                                                                                                                                                                         |

|           |      | BRDY# is sampled in the second and subsequent clocks of a burst cycle. Data presented on the data bus is strobed into the embedded Intel486 SX processor when BRDY# is sampled active. If RDY# is returned simultaneously with BRDY#, BRDY# is ignored and the burst cycle is prematurely aborted.                                                                                                                                                                                                                                                                  |

|           |      | BRDY# is active LOW and is provided with a small pull-up resistor. BRDY# must satisfy the setup and hold times $t_{16}$ and $t_{17}$ .                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BLAST#    | 0    | <b>Burst Last</b> signal indicates that the next time BRDY# is returned, the burst bus cycle is complete. BLAST# is active for both burst and non-burst bus cycles. BLAST# is active LOW and is not driven during bus hold.                                                                                                                                                                                                                                                                                                                                         |

| INTERRUPT | S    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RESET     | I    | Reset input forces the embedded Intel486 SX processor to begin execution at a known state. The processor cannot begin executing instructions until at least 1 ms after $V_{CC}$ , and CLK have reached their proper DC and AC specifications. The RESET pin must remain active during this time to ensure proper processor operation. However, for warm resets, RESET should remain active for at least 15 CLK periods. RESET is active HIGH. RESET is asynchronous but must meet setup and hold times $t_{20}$ and $t_{21}$ for recognition in any specific clock. |

| INTR      | I    | Maskable Interrupt indicates that an external interrupt has been generated. When the internal interrupt flag is set in EFLAGS, active interrupt processing is initiated. The embedded Intel486 SX processor generates two locked interrupt acknowledge bus cycles in response to the INTR pin going active. INTR must remain active until the interrupt acknowledges have been performed to ensure processor recognition of the interrupt.                                                                                                                          |

|           |      | INTR is active HIGH and is not provided with an internal pull-down resistor. INTR is asynchronous, but must meet setup and hold times t <sub>20</sub> and t <sub>21</sub> for recognition in any specific clock.                                                                                                                                                                                                                                                                                                                                                    |

Table 7. Embedded Intel486™ SX Processor Pin Descriptions (Sheet 4 of 6)

| Symbol     | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NMI        | I      | Non-Maskable Interrupt request signal indicates that an external non-maskable interrupt has been generated. NMI is rising-edge sensitive and must be held LOW for at least four CLK periods before this rising edge. NMI is not provided with an internal pull-down resistor. NMI is asynchronous, but must meet setup and hold times $t_{20}$ and $t_{21}$ for recognition in any specific clock.                                                                                                                                                                                                                                         |  |  |  |

| SRESET     | I      | <b>Soft Reset</b> pin duplicates all functionality of the RESET pin except that the SMBASE register retains its previous value. For soft resets, SRESET must remain active for at least 15 CLK periods. SRESET is active HIGH. SRESET is asynchronous but must meet setup and hold times $t_{20}$ and $t_{21}$ for recognition in any specific clock.                                                                                                                                                                                                                                                                                      |  |  |  |

| SMI#       | ı      | System Management Interrupt input invokes System Management Mode (SMM). SMI# is a falling-edge triggered signal which forces the embedded Intel486 SX processor into SMM at the completion of the current instruction. SMI# is recognized on an instruction boundary and at each iteration for repeat string instructions. SMI# does not break LOCKed bus cycles and cannot interrupt a currently executing SMM. The embedded Intel486 SX processor latches the falling edge of one pending SMI# signal while it is executing an existing SMI#. The nested SMI# is not recognized until after the execution of a Resume (RSM) instruction. |  |  |  |

| SMIACT#    | 0      | System Management Interrupt Active, an active LOW output, indicates that the embedded Intel486 SX processor is operating in SMM. It is asserted when the processor begins to execute the SMI# state save sequence and remains active LOW until the processor executes the last state restore cycle out of SMRAM.                                                                                                                                                                                                                                                                                                                           |  |  |  |

| STPCLK#    | I      | Stop Clock Request input signal indicates a request was made to turn off or change the CLK input frequency. When the embedded Intel486 SX processor recognizes a STPCLK#, it stops execution on the next instruction boundary (unless superseded by a higher priority interrupt), empties all internal pipelines and write buffers, and generates a Stop Grant bus cycle. STPCLK# is active LOW. STPCLK# is an asynchronous signal, but must remain active until the embedded Intel486 SX processor issues the Stop Grant bus cycle. STPCLK# may be de-asserted at any time after the processor has issued the Stop Grant bus cycle.       |  |  |  |

| BUS ARBITE | RATION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| BREQ       | 0      | <b>Bus Request</b> signal indicates that the embedded Intel486 SX processor has internally generated a bus request. BREQ is generated whether or not the processor is driving the bus. BREQ is active HIGH and is never floated.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |