# AP-502 APPLICATION NOTE

# Quick Upgrade from the 80C186XL to the 80C186EA

LARRY BATES

80C186 APPLICATIONS ENGINEERING

February 1994

Order Number: 272475-001

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive and iCOMP trademarks has been issued to Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

# Quick Upgrade from the 80C186XL to the 80C186EA

| CONTENTS                                                                     | PAGE      | CONTENTS                                         | PAGE         |

|------------------------------------------------------------------------------|-----------|--------------------------------------------------|--------------|

| 1.0 PURPOSE OF THIS APPLICAT                                                 | ION       | 4.3 Peripheral Logic                             | 14           |

| NOTE                                                                         |           | 4.4 Miscellaneous Control Logic                  | 14           |

| 2.0 THE 80C186EA/80C188EA<br>ARCHITECTURE                                    | 1         | 4.4.1 Chip-Selects and Wait S<br>Generation      |              |

|                                                                              |           | 4.4.2 DRAM Control                               | 15           |

| 3.0 SIMILARITIES AND DIFFEREN<br>BETWEEN THE 80C186EA AND<br>STANDARD 80C186 | THE       | 4.4.3 82C59A Interface 5.0 OTHER UPGRADE         | 15           |

| 3.1 Program Execution                                                        |           | CONSIDERATIONS                                   | 17           |

| 3.2 Available Packages                                                       |           | APPENDIX A: 80C186EA DRAM                        |              |

| 3.3 Available Temperature                                                    |           | CONTROLLER EXAMPLE                               | A-1          |

| Selections                                                                   |           | A.1 Design Requirements                          | A-1          |

| 3.4 Operating Modes                                                          |           | A.2 What the 80C186EA Provide                    | es A-1       |

| 3.5 Modular Core and Peripherals                                             |           | A.3 The Design Solution                          | A-2          |

| 3.6 Power Management                                                         |           | A.3.1 Design Overview                            | A-3          |

| 3.6.1 Idle Mode                                                              |           | A.3.2 How the Design Solves Problem              |              |

| 3.6.3 Power-Save Mode                                                        | 3         | A.3.3 How the DRAM Control Works                 |              |

| 3.7 Pin Compatibility                                                        | Chip      | A.3.4 Programming the 80C1<br>Refresh Controller | 86EA<br>A-10 |

| Carrier (PLCC)                                                               |           | A.3.5 Loading and Transmiss Line Effects         |              |

| 3.7.3 80-Lead Shrink Quad Fla<br>Pack (SQFP)                                 | ıt        | A.3.6 Modifications for the 80C188EA             | A-10         |

| 3.8 DC Compatibility                                                         |           | A.4 Adapting the Design to Your System           | A-10         |

| 3.9 AC Compatibility                                                         | 10        | A.5 Bibliography                                 |              |

| 4.0 SYSTEM DESIGN CONSIDERATIONS                                             | 12        |                                                  |              |

| 4.1 Designing for High-Speed CP                                              | Us 12     |                                                  |              |

| 4.2 Memory Speed Requirements                                                | 3 12      |                                                  |              |

| 4.2.1 EPROM, Flash Memory a SRAM Devices                                     | and<br>12 |                                                  |              |

| 4.0.0 DDAM Davisas                                                           | 10        |                                                  |              |

The 80C186EA/80C188EA is the second member of the 80C186 modular core family. It retains the 80C186XL's versatile DMA capabilities and adds two power management modes. The 80C186EA is well-suited for a broad spectrum of embedded data control designs where power consumption is a concern. The 80C186EA is ideal for compact, portable designs, including those operated from batteries.

# 1.0 PURPOSE OF THIS APPLICATION NOTE

This application note has two purposes. First, it highlights the features and benefits of the 80C186EA. Second, it shows how easy it is to upgrade an existing standard 80C186XL application to the 80C186EA. Upgrades require no software modification and little or no hardware modification in most cases.

# 2.0 THE 80C186EA/80C188EA ARCHITECTURE

The 80C186EA is a high integration embedded processor belonging to the 80C186XL modular core family. It is 100 percent code-compatible with the standard 80C186XL and includes the following 80C186XL integrated feature set:

- 16-Bit Execution Unit (EU) using familiar x86 instruction set and 1 Mbyte address space.

- Bus Interface Unit (BIU) with a full complement of control signals and support for alternate bus masters.

- Timer/Counter Unit (TCU) with three programmable 16-bit timers and internal or external clocking options.

- Refresh Control Unit (RCU) to simplify the interface to dynamic memory.

- Chip-Select Unit (CSU) with up to 13 external pins to support memory and I/O devices, including programmable wait states.

- Interrupt Control Unit (ICU) which allows complex interrupt priority schemes.

- Direct Memory Access Unit (DMU) with two channels for efficient data transfers.

- · ONCE high-impedance test mode.

Intel offers the 80C188EA with an 8-bit wide data bus for economical product design. Intel also offers 3V (rated 2.7V-5.5V) versions designated as the 80L186EA and the 80L188EA. With the emphasis on low power, 3V operation and power management, Intel commands a leadership position with the 80C186EA family.

# 3.0 SIMILARITIES AND DIFFERENCES BETWEEN THE 80C186EA AND THE 80C186XL

The 80C186EA, with its 80C186 modular core, is 100 percent code-compatible to the 80C186XL. The 80C186EA's Chip-Select, Refresh Control, Interrupt Control, Timer/Counter and DMA Units are identical to the 80C186XL, too.

There are AC and DC specification differences. Before embarking on your design, obtain the latest specifications from the following data sheet:

80C186EA/80C188EA and 80L186EA/80L188EA Data Sheet #272432

To gain the most advantage from this application note, refer to the 80C186EA User's Manual (#270950). This note highlights differences between the 80C186EA and the 80C188EA where applicable.

# 3.1 Program Execution

All existing 80C186XL programs execute correctly on the 80C186EA without modification. All 80C186XL control registers have the same offsets in the 80C186EA Peripheral Control Block. Although the register functions are identical, many register and bit names differ on the 80C186EA to conform to other 80C186 modular core family members.

# 3.2 Available Packages

The 80C186EA comes only in economical plastic packages: a 68-lead Plastic Leaded Chip Carrier (PLCC), and 80-lead Shrink Quad Flat Pack (SQFP), and an 80-lead EIAJ Quad Flat Pack (QFP). Except as discussed in Section 3.7.1, the PLCC 80C186EA pinout is equivalent to the standard 80C186XL PLCC pinout and the SQFP 80C186EA pinout is identical to the SQFP 80C186XL pinout. The QFP (EIAJ) 80C186EA pinout differs somewhat from its 80C186XL counterpart.

The pinout of a socketed PLCC 80C186EA is equivalent to the pinout of a Pin Grid Array (PGA) standard 80C186 and the pinout of a socketed ceramic Leadless Chip Carrier (LCC) standard 80C186.

# 3.3 Available Temperature Selections

Intel offers the standard 80C186XL with either commercial (0°C-70°C ambient) or extended (-40°C to +85°C ambient) temperature ratings. 80C186EA operation is specified for case temperatures, but the commercial and extended temperature ranges do exactly match the 0°C-70°C and -40°C to +85°C ambient temperature ranges, respectively.

# 3.4 Operating Modes

The concept of operating mode is different between the 80C186XL and the 80C186EA.

The standard 80C186XL leaves reset in either compatible mode or enhanced mode, depending on the TEST/BUSY pin state. Compatible mode derived its name because of its likeness to the NMOS 80186. The 80C186XL requires enhanced mode operation for power-save mode, the refresh control unit and the 80C187 math coprocessor interface. Enhanced mode changes three Mid-range Chip Select (MCS) pins to handshaking pins for the math coprocessor.

The 80C186EA leaves reset with either numerics mode or regular operation. The TEST/BUSY pin must be high on the rising edge of Reset Input (RESIN) and low four clocks later to enable numerics mode. Numerics mode changes the three MCS pins to 80C187 handshaking pins. Power-save mode and the refresh control unit are always available on the 80C186EA.

An 80C186EA placed into an unmodified standard 80C186XL design responds correctly, whether the original configuration was compatible or enhanced. All exe-

cution proceeds identically on a clock-for-clock basis. The processor activates new power management features only if the user programs them.

The 80C188EA, like the 80C188XL, does not have an interface for the 80C187. If an existing design configured the 80C188XL for enhanced mode, the 80C188EA responds with regular operation.

Queue status and ONCE modes are identical between the standard 80C186XL and the 80C186EA.

# 3.5 Modular Core and Peripherals

The 80C186EA execution and bus interface units are 100 percent compatible with the standard 80C186 on a clock-for-clock basis. The TCU, RCU, CSU, ICU, DMU and clock generator (with power-save mode) are also identical to their 80C186XL counterparts.

Although the programming and operation of these peripherals is 100 percent compatible, some of the register and bit names changed in the data sheets and User's Manual to conform to other modular core products.

# 3.6 Power Management

The 80C186EA has three power management modes: idle, powerdown and power-save. Power-save mode is a clock generation function, while idle and powerdown modes are clock distribution functions. Power-save mode is identical to the 80C186XL but powerdown and idle are new features.

# 3.6.1 IDLE MODE

During idle mode operation the clock signal goes only to the integrated peripheral devices, so the peripherals operate normally. The clocks to the modular core (execution and bus interface units) freeze in a logic low state, so execution stops. CLKOUT continues to toggle. Idle mode reduces current draw about a third, depending on the activity in the peripheral units.

Setting the IDLE bit in the power control register arms idle mode. The processor actually enters idle mode when it executes a HLT (halt) instruction. DMA requests, DRAM refresh requests and HOLD requests temporarily turn on the core clocks. DMA and DRAM refresh cycles running under idle mode are no different from other DMA and DRAM refresh cycles. After the bus activity ends, the core clocks again turn off.

The core clocks also turn on temporarily to issue HLDA (hold acknowledge) in response to a HOLD request. After the external bus master finishes using the bus and deasserts HOLD, the processor deasserts HLDA and again turns off the core clocks. Refresh requests occurring during bus hold force the BIU to deassert HLDA to regain control of the bus for the refresh cycle.

There are three ways to exit idle mode: unmasked interrupt, non-maskable interrupt (NMI) or reset. The processor does not retain any information after reset, so the user must reprogram the power control register and reexecute HLT to resume idle mode operation.

After the processor executes the IRET (interrupt return instruction) in the interrupt service routine, the instruction pointer points to the instruction following the HLT instruction. Interrupt execution does not clear the power control register, so the processor can resume idle mode operation by executing another HLT instruction.

### 3.6.2 POWERDOWN MODE

Powerdown mode freezes the clocks to the entire device (core and peripherals), disables the crystal oscillator and stops CLKOUT. All internal units (registers, state machines, etc.) maintain their state as long as  $V_{\rm CC}$  is applied. The BIU cannot run DMA or DRAM refresh cycles nor honor HOLD requests in powerdown mode because the clocks are off. Current consumption in powerdown mode consists of just transistor leakage, typically less than 100  $\mu$ A.

The procedure for entering powerdown is similar to the procedure for idle mode. Setting the PWRDN bit in the power control register arms powerdown mode. All clocks stop immediately upon execution of the HLT instruction.

The 80C186EA exits powerdown mode via an NMI or a reset. Unless an external oscillator feeds the CLKIN input, the circuit must allow some time for the crystal oscillator to restart.

For a reset, follow the usual procedure for a powerup (cold) reset. A simple RC network at the RESIN input pin fulfills this requirement.

For an NMI, an external Powerdown Timer (PDTMR) pin provides the timing delay. First, determine the startup time for your exact circuit over its full operating range using a storage oscilloscope. Be careful to compensate for scope loading. Then multiply the startup time by the constant C<sub>PD</sub>, given in the 80C186EA data sheet, to obtain a capacitance value. With typical

oscillator startup on the order of a couple of milliseconds, the PDTMR capacitor value will be less than 1  $\mu F$ . After the processor executes the IRET in the NMI routine, the instruction pointer points to the instruction following the HLT. Remember that the PWRDN bit in the power control register remains set and that the processor can re-enter powerdown via HLT.

Driving the CLKIN input with a continuous external frequency source presents a special case. The processor doesn't need to wait for a crystal to start vibrating, so leave the PDTMR pin unconnected. The 80C186EA can exit powerdown mode without a timing delay.

### 3.6.3 POWER-SAVE MODE

Power-save mode is not a new feature. It is identical on the 80C186XL and the 80C186EA. However, powersave mode deserves special attention on the 80C186EA because you can now use it to greater advantage.

Power-save mode enables a programmable clock divisor in the clock generation circuit. This divider operates in addition to the usual divide-by-two counter. Possible clock divisor settings are 1, 4, 8 and 16 (1 has no effect). The divided frequency feeds the core, the integrated peripherals and CLKOUT. The processor operates at the divided clock rate as if you used a lower frequency crystal or external oscillator. Unlike the 80C186XL, the 80C186EA has no lower frequency limit. You can use the maximum divisor, 16, regardless of the undivided frequency.

Operation of *both* the core and the integrated peripherals continues in power-save mode. It may be necessary to reprogram units such as the timer counter unit and the refresh control unit to compensate for the overall reduced clock rate.

The procedure for entering power-save mode is to program the divisor bits and the PSEN (Power-Save Enable) bit in the power-save register. The choices for leaving power-save mode are clearing the PSEN bit, an unmasked (hardware) interrupt or an NMI. Power-save changes go into effect only at the falling edge of T<sub>3</sub> bus cycle states.

Since current is linear with respect to frequency, power-save mode reduces current draw at least half. If the processor can run background tasks at reduced speed, power-save mode is well-suited, although the overhead might be considerable. Concurrent power management (entering power-save mode and entering idle mode) is an attractive option because the power reductions multiply.

# 3.7 Pin Compatibility

The functionality of the 80C186EA is directly compatible to the standard 80C186XL. The degree of pin compatibility

depends on the package being used. Table 1 lists all pin names and their numbers, highlighting all changes. Functional differences noted for the 80C188XL also apply to the 80C188EA.

Table 1. 80C186XL to 80C186EA Pin Comparison Chart

|                  | lubi                |                                | TO 80C186EA F                  |                                | T Onart                        | I           |

|------------------|---------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|-------------|

| 80C186XL<br>Name | 80C186EA<br>Name    | 80C186XL<br>68-Lead<br>Package | 80C186EA<br>68-Lead<br>Package | 80C186XL<br>80-Lead<br>Package | 80C186EA<br>80-Lead<br>Package | Notes       |

| AD0              | AD0                 | 17                             | 17                             | 64                             | 64                             |             |

| AD1              | AD1                 | 15                             | 15                             | 66                             | 66                             |             |

| AD2              | AD2                 | 13                             | 13                             | 68                             | 68                             |             |

| AD3              | AD3                 | 11                             | 11                             | 70                             | 70                             |             |

| AD4              | AD4                 | 8                              | 8                              | 74                             | 74                             |             |

| AD5              | AD5                 | 6                              | 6                              | 76                             | 76                             |             |

| AD6              | AD6                 | 4                              | 4                              | 78                             | 78                             |             |

| AD7              | AD7                 | 2                              | 2                              | 80                             | 80                             |             |

| AD8              | AD8                 | 16                             | 16                             | 65                             | 65                             | A8 (C188)   |

| AD9              | AD9                 | 14                             | 14                             | 67                             | 67                             | A9 (C188)   |

| AD10             | AD10                | 12                             | 12                             | 69                             | 69                             | A10 (C188)  |

| AD11             | AD11                | 10                             | 10                             | 71                             | 71                             | A11 (C188)  |

| AD12             | AD12                | 7                              | 7                              | 75                             | 75                             | A12 (C188)  |

| AD13             | AD13                | 5                              | 5                              | 77                             | 77                             | A13 (C188)  |

| AD14             | AD14                | 3                              | 3                              | 79                             | 79                             | A14 (C188)  |

| AD15             | AD15                | 1                              | 1                              | 1                              | 1                              | A15 (C188)  |

| A16              | A16                 | 68                             | 68                             | 3                              | 3                              |             |

| A17              | A17                 | 67                             | 67                             | 4                              | 4                              |             |

| A18              | A18                 | 66                             | 66                             | 5                              | 5                              |             |

| A19/S6           | A19/ <del>S</del> 6 | 65                             | 65                             | 6                              | 6                              |             |

| ALE/QS0          | ALE/QS0             | 61                             | 61                             | 10                             | 10                             |             |

| BHE              | BHE                 | 64                             | 64                             | 7                              | 7                              | RFSH (C188) |

| <u>\$0</u>       | <u>\$0</u>          | 52                             | 52                             | 23                             | 23                             |             |

| S1               | S1                  | 53                             | 53                             | 22                             | 22                             |             |

| S2               | S2                  | 54                             | 54                             | 21                             | 21                             |             |

| RD/QSMD          | RD/QSMD             | 62                             | 62                             | 9                              | 9                              |             |

| WR/QS1           | WR/QS1              | 63                             | 63                             | 8                              | 8                              |             |

| ARDY             | ARDY                | 55                             | 55                             | 20                             | 20                             |             |

| SRDY             | SRDY                | 49                             | 49                             | 27                             | 27                             |             |

Table 1. 80C186XL to 80C186EA Pin Comparison Chart (Continued)

| 80C186XL<br>Name | 80C186EA<br>Name | 80C186XL<br>68-Lead<br>Package | 80C186EA<br>68-Lead<br>Package | 80C186XL<br>80-Lead<br>Package | 80C186EA<br>80-Lead<br>Package | Notes                      |

|------------------|------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|----------------------------|

| DEN              | DEN              | 39                             | 39                             | 38                             | 39                             |                            |

| DT/R             | DT/R             | 40                             | _                              | 37                             | 37                             | See PDTMR                  |

| LOCK             | LOCK             | 48                             | 48                             | 28                             | 28                             |                            |

| HOLD             | HOLD             | 50                             | 50                             | 26                             | 26                             |                            |

| HLDA             | HLDA             | 51                             | 51                             | 25                             | 25                             |                            |

| RES              | RESIN            | 24                             | 24                             | 55                             | 55                             | Name Change                |

| RESET            | RESOUT           | 57                             | 57                             | 18                             | 18                             | Name Change                |

| X1               | CLKIN            | 59                             | 59                             | 16                             | 16                             | Name Change                |

| X2               | OSCOUT           | 58                             | 58                             | 17                             | 17                             | Name Change                |

| CLKOUT           | CLKOUT           | 56                             | 56                             | 19                             | 19                             |                            |

| TEST/BUSY        | TEST/BUSY        | 47                             | 47                             | 29                             | 29                             | TEST (C188)                |

| _                | PDTMR            | _                              | 40                             | _                              | 38                             | See DT/R                   |

| NMI              | NMI              | 46                             | 46                             | 30                             | 30                             |                            |

| INT0             | INT0             | 45                             | 45                             | 31                             | 31                             |                            |

| INT1             | INT1/SELECT      | 44                             | 44                             | 32                             | 32                             | Name Change                |

| INT2/INTA0       | INT2/INTA0       | 42                             | 42                             | 35                             | 35                             |                            |

| INT3/INTA1       | INT3/INTA1/IRQ   | 41                             | 41                             | 36                             | 36                             | Name Change                |

| <u>UCS</u>       | <u>UCS</u>       | 34                             | 34                             | 45                             | 45                             |                            |

| <u>ICS</u>       | <u>LCS</u>       | 33                             | 33                             | 46                             | 46                             |                            |

| MCS0/PEREQ       | MCS0/PEREQ       | 38                             | 38                             | 39                             | 40                             | MCS0 (C188)                |

| MCS1/ERROR       | MCS1/ERROR       | 37                             | 37                             | 40                             | 41                             | MCS1 (C188)                |

| MCS2             | MCS2             | 36                             | 36                             | 41                             | 42                             |                            |

| MCS3/NPS         | MCS3/NCS         | 35                             | 35                             | 42                             | 43                             | Name Change<br>MCS3 (C188) |

| PCS0             | PCS0             | 25                             | 25                             | 54                             | 54                             |                            |

| PCS1             | PCS1             | 27                             | 27                             | 52                             | 52                             |                            |

| PCS2             | PCS2             | 28                             | 28                             | 51                             | 51                             |                            |

| PCS3             | PCS3             | 29                             | 29                             | 50                             | 50                             |                            |

| PCS4             | PCS4             | 30                             | 30                             | 49                             | 49                             |                            |

| PCS5/A1          | PCS5/A1          | 31                             | 31                             | 48                             | 48                             |                            |

| PCS6/A2          | PCS6/A2          | 32                             | 32                             | 47                             | 47                             |                            |

| TMR OUT 0        | T0OUT            | 22                             | 22                             | 57                             | 57                             | Name Change                |

| TMR IN 0         | TOIN             | 20                             | 20                             | 59                             | 59                             | Name Change                |

| TMR OUT 1        | T1OUT            | 23                             | 23                             | 56                             | 56                             | Name Change                |

| TMR IN 1         | T1IN             | 21                             | 21                             | 58                             | 58                             | Name Change                |

Table 1. 80C186XL to 80C186EA Pin Comparison Chart (Continued)

| 80C186XL<br>Name | 80C186EA<br>Name | 80C186XL<br>68-Lead<br>Package | 80C186EA<br>68-Lead<br>Package | 80C186XL<br>80-Lead<br>Package          | 80C186EA<br>80-Lead<br>Package | Notes |

|------------------|------------------|--------------------------------|--------------------------------|-----------------------------------------|--------------------------------|-------|

| DRQ0             | DRQ0             | 18                             | 18                             | 61                                      | 61                             |       |

| DRQ1             | DRQ1             | 19                             | 19                             | 60                                      | 60                             |       |

| V <sub>SS</sub>  | V <sub>SS</sub>  | 26, 60                         | 26, 60                         | 12, 13, 53                              | 12, 13, 24,<br>53, 62          |       |

| Vcc              | Vcc              | 9, 43                          | 9, 43                          | 33, 34,<br>72, 73                       | 2, 33, 34,<br>44, 72, 73       |       |

| NO CONNECT       | NO CONNECT       | _                              | _                              | 2, 11, 14,<br>15, 24, 43,<br>44, 62, 63 | 11, 14,<br>15, 63              |       |

# 3.7.1 68-LEAD PLASTIC LEADED CHIP CARRIER (PLCC)

Upgrades to existing 80C186 PLCC designs may not require a new layout. The only PLCC pin difference is lead #40, which is the Data Transmit/Receive (DT/ $\overline{R}$ ) lead on the standard 80C186 and the PDTMR lead on the 80C186EA. If the original design does not use DT/ $\overline{R}$  to control the data direction in bus transceivers, no layout changes are needed. If you wish to use the 80C186EA powerdown mode, you must connect a capacitor at PDTMR to time the processor's exit from powerdown mode (unless you also use an external oscillator).

If  $\overline{DT/R}$  is needed, reconstruct it by latching status signal  $\overline{S1}$  with a transparent latch gated by Address Latch Enable (ALE). The timing difference between the processor's  $\overline{DT/R}$  (if it were available) and synthesized  $\overline{DT/R}$  equals the propagation delay through the latch, since  $\overline{DT/R}$ , bus cycle status ( $\overline{S2:0}$ ) and ALE all change state at the falling edge of  $\overline{T_4}$ .

# 3.7.2 80-LEAD QUAD FLAT PACK (QFP-EIAJ)

The 80C186EA fine pitch QFP package does provide the  $DT/\overline{R}$  signal. The 80C186EA has four more power and ground pins than the standard 80C186 and several pin functions changed position. You must use a new board layout for the 80C186EA QFP package.

# 3.7.3 80-LEAD SHRINK QUAD FLAT PACK (SQFP)

The 80C186EA SQFP package is identical to the 80C186XL SQFP package, with the exception of lead #55. This lead is a no connect on the 80C186XL and PDTMR on the 80C186EA.

The 80C186EA SQFP is a direct replacement for the 80C186XL. No layout changes are required, unless the PDTMR pin functionality is required.

### 3.8 DC Compatibility

Intel manufactures both the standard 80C186XL and the 80C186EA in CMOS logic. However, the standard 80C186XL has TTL-compatible inputs while the 80C186EA has CMOS-compatible inputs. TTL logic in existing 80C186XL designs must change to CMOS logic if the outputs drive the 80C186EA. For all-CMOS circuits, use devices such as those from the HC and AC logic families. Corresponding members of the HCT and ACT families have TTL-compatible inputs. Pullup resistors are inconsistent with choosing the 80C186EA for low power because of added current draw.

CMOS-level inputs have several advantages. The main advantage is improved noise margin. The 80C186XL has a  $V_{OH}$  minimum of 2.4V and a  $V_{IH}$  minimum of  $0.2\ V_{CC}+0.9V$ , for a noise margin of 0.5V (with 5V operation). The 80C186EA has a  $V_{OH}$  minimum of  $V_{CC}-0.5V$  and a  $V_{IH}$  minimum of  $0.7\ V_{CC}$ , for a noise margin of 1.0V (with 5V operation).

The 80C186XL data sheet references AC timings to 1.5V (the TTL switchpoint). The 80C186EA data sheet references AC timings to  $V_{\rm CC}/2$  (the CMOS switchpoint). Reducing the operating voltage (80L186EA/80L188EA) directly scales the specified reference point.

Table 2. 80C186XL to 80C186EA Pin Comparison Chart—SQFP Package

| 80C186XL            | 80C186EA            | 80C186XL           | 80C186EA           |             |

|---------------------|---------------------|--------------------|--------------------|-------------|

| Name                | Name                | 80-Lead<br>Package | 80-Lead<br>Package | Notes       |

| AD0                 | AD0                 | 1                  | 1                  |             |

| AD1                 | AD1                 | 3                  | 3                  |             |

| AD2                 | AD2                 | 6                  | 6                  |             |

| AD3                 | AD3                 | 8                  | 8                  |             |

| AD4                 | AD4                 | 12                 | 12                 |             |

| AD5                 | AD5                 | 14                 | 14                 |             |

| AD6                 | AD6                 | 16                 | 16                 |             |

| AD7                 | AD7                 | 18                 | 18                 |             |

| AD8                 | AD8                 | 2                  | 2                  | A8 (C188)   |

| AD9                 | AD9                 | 5                  | 5                  | A9 (C188)   |

| AD10                | AD10                | 7                  | 7                  | A10 (C188)  |

| AD11                | AD11                | 9                  | 9                  | A11 (C188)  |

| AD12                | AD12                | 13                 | 13                 | A12 (C188)  |

| AD13                | AD13                | 15                 | 15                 | A13 (C188)  |

| AD14                | AD14                | 17                 | 17                 | A14 (C188)  |

| AD15                | AD15                | 19                 | 19                 | A15 (C188)  |

| A16                 | A16                 | 21                 | 21                 |             |

| A17                 | A17                 | 22                 | 22                 |             |

| A18                 | A18                 | 23                 | 23                 |             |

| A19/ <del>S</del> 6 | A19/ <del>S</del> 6 | 24                 | 24                 |             |

| ALE/QS0             | ALE/QS0             | 29                 | 29                 |             |

| BHE                 | BHE                 | 26                 | 26                 | RFSH (C188) |

| <u>S0</u>           | S0                  | 40                 | 40                 |             |

| <del>S</del> 1      | S1                  | 39                 | 39                 |             |

| S2                  | S2                  | 38                 | 38                 |             |

| RD/QSMD             | RD/QSMD             | 28                 | 28                 |             |

| WR/QS1              | WR/QS1              | 27                 | 27                 |             |

| ARDY                | ARDY                | 37                 | 37                 |             |

| SRDY                | SRDY                | 44                 | 44                 |             |

Table 2. 80C186XL to 80C186EA Pin Comparison Chart—SQFP Package (Continued)

| 80C186XL<br>Name | 80C186EA<br>Name | 80C186XL<br>80-Lead<br>Package | 80C186EA<br>80-Lead<br>Package | Notes                   |

|------------------|------------------|--------------------------------|--------------------------------|-------------------------|

| DEN              | DEN              | 56                             | 56                             |                         |

| DT/R             | DT/R             | 54                             | 54                             | See PDTMR               |

| LOCK             | LOCK             | 45                             | 45                             |                         |

| HOLD             | HOLD             | 43                             | 43                             |                         |

| HLDA             | HLDA             | 42                             | 42                             |                         |

| RES              | RESIN            | 73                             | 73                             | Name Change             |

| RESET            | RESOUT           | 34                             | 34                             | Name Change             |

| X1               | CLKIN            | 32                             | 32                             | Name Change             |

| X2               | OSCOUT           | 33                             | 33                             | Name Change             |

| CLKOUT           | CLKOUT           | 36                             | 36                             |                         |

| TEST/BUSY        | TEST/BUSY        | 46                             | 46                             | TEST (C188)             |

| _                | PDTMR            | _                              | 55                             | See DT/R                |

| NMI              | NMI              | 47                             | 47                             |                         |

| INT0             | INT0             | 48                             | 48                             |                         |

| INT1             | INT1/SELECT      | 49                             | 49                             | Name Change             |

| INT2/INTA0       | INT2/INTA0       | 52                             | 52                             |                         |

| INT3/INTA1       | INT3/INTA1/IRQ   | 53                             | 53                             | Name Change             |

| <u>UCS</u>       | UCS              | 62                             | 62                             |                         |

| <u>LCS</u>       | <u>LCS</u>       | 63                             | 63                             |                         |

| MCS0/PEREQ       | MCS0/PEREQ       | 57                             | 57                             | MCS0 (C188)             |

| MCS1/ERROR       | MCS1/ERROR       | 58                             | 58                             | MCS1 (C188)             |

| MCS2             | MCS2             | 59                             | 59                             |                         |

| MCS3/NPS         | MCS3/NCS         | 60                             | 60                             | Name Change MCS3 (C188) |

| PCS0             | PCS0             | 71                             | 71                             |                         |

| PCS1             | PCS1             | 69                             | 69                             |                         |

| PCS2             | PCS2             | 68                             | 68                             |                         |

| PCS3             | PCS3             | 67                             | 67                             |                         |

| PCS4             | PCS4             | 66                             | 66                             |                         |

| PCS5/A1          | PCS5/A1          | 65                             | 65                             |                         |

| PCS6/A2          | PCS6/A2          | 64                             | 64                             |                         |

| TMR OUT 0        | TOOUT            | 75                             | 75                             | Name Change             |

| TMR IN 0         | TOIN             | 77                             | 77                             | Name Change             |

| TMR OUT 1        | T1OUT            | 74                             | 74                             | Name Change             |

| TMR IN 1         | T1IN             | 76                             | 76                             | Name Change             |

Table 2. 80C186XL to 80C186EA Pin Comparison Chart—SQFP Package (Continued)

| 80C186XL<br>Name | 80C186EA<br>Name | 80C186XL<br>80-Lead<br>Package | 80C186EA<br>80-Lead<br>Package | Notes |

|------------------|------------------|--------------------------------|--------------------------------|-------|

| DRQ0             | DRQ0             | 79                             | 79                             |       |

| DRQ1             | DRQ1             | 78                             | 78                             |       |

| $V_{SS}$         | V <sub>SS</sub>  | 30, 31, 41, 70, 80             | 30, 31, 41, 70, 80             |       |

| V <sub>CC</sub>  | V <sub>CC</sub>  | 10, 11, 20, 50, 51, 61         | 10, 11, 20, 50, 51, 61         |       |

| NO CONNECT       | NO CONNECT       | 4, 25, 35, 55, 72              | 4, 25, 35, 72                  |       |

# 3.9 AC Compatibility

family members. Table 3 lists all  $80C186XL\ AC$  timing mnemonics and their 80C186EA equivalents.

Intel specifies 80C186EA AC timings in a simplified format consistent with other 80C186 modular core

Table 3. 80C186XL to 80C186EA AC Timing Mnemonic Comparison

| 80C186XL<br>AC Timing<br>Mnemonic | Parameter                              | Equivalent 80C186EA<br>AC Timing Mnemonic                                 |

|-----------------------------------|----------------------------------------|---------------------------------------------------------------------------|

| T <sub>DVCL</sub>                 | Data in Setup (A/D)                    | T <sub>CLIS</sub>                                                         |

| T <sub>CLDX</sub>                 | Data in Hold (A/D)                     | T <sub>CLIH</sub>                                                         |

| T <sub>CHSV</sub>                 | Status Active Delay                    | T <sub>CHOV1</sub>                                                        |

| T <sub>CLSH</sub>                 | Status Inactive Delay                  | T <sub>CLOV2</sub>                                                        |

| T <sub>CLAV</sub>                 | Address Valid Delay                    | T <sub>CLOV1</sub> (A19:16, <del>DEN</del> ), T <sub>CLOV2</sub> (AD15:0) |

| T <sub>CLAX</sub>                 | Address Hold                           | T <sub>CLOV1</sub> (A19:16), T <sub>CLOV2</sub> (AD15:0)                  |

| T <sub>CLDV</sub>                 | Data Valid Delay                       | T <sub>CLOV1</sub> (A19:16), T <sub>CLOV2</sub> (AD15:0)                  |

| T <sub>CHDX</sub>                 | Status Hold Time                       | Eliminated                                                                |

| T <sub>CHLH</sub>                 | ALE Active Delay                       | T <sub>CHOV1</sub>                                                        |

| T <sub>LHLL</sub>                 | ALE Width                              | T <sub>LHLL</sub>                                                         |

| T <sub>CHLL</sub>                 | ALE Inactive Delay                     | T <sub>CHOV1</sub>                                                        |

| T <sub>AVLL</sub>                 | Address Valid to ALE Low               | T <sub>AVLL</sub>                                                         |

| T <sub>LLAX</sub>                 | Address Hold from ALE Inactive         | T <sub>LLAX</sub>                                                         |

| T <sub>AVCH</sub>                 | Address Valid to Clock High            | Eliminated                                                                |

| T <sub>CLAZ</sub>                 | Address Float Delay                    | T <sub>CLOF</sub>                                                         |

| T <sub>CLCSV</sub>                | Chip-Select Active Delay               | T <sub>CLOV2</sub>                                                        |

| T <sub>CXCSX</sub>                | Chip-Select Hold from Command Inactive | T <sub>RHPH</sub> (RD), T <sub>WHPH</sub> (WR)                            |

| T <sub>CHCSX</sub>                | Chip-Select Inactive Delay             | T <sub>CHOV2</sub>                                                        |

| T <sub>DXDL</sub>                 | DEN Inactive to DT/R Low               | T <sub>DXDL</sub>                                                         |

| T <sub>CVCTV</sub>                | Control Active Delay 1                 | T <sub>CHOV1</sub> (DEN), T <sub>CLOV2</sub> (WR, INTA)                   |

| T <sub>CVDEX</sub>                | DEN Inactive Delay                     | T <sub>CLOV1</sub>                                                        |

| T <sub>CHCTV</sub>                | Control Active Delay 2                 | T <sub>CHOV1</sub>                                                        |

| T <sub>CLLV</sub>                 | LOCK Valid/Invalid Delay               | T <sub>CLOV1</sub>                                                        |

| T <sub>AZRL</sub>                 | Address Float to Read Active           | T <sub>AFRL</sub>                                                         |

| T <sub>CLRL</sub>                 | RD Active Delay                        | T <sub>CLOV2</sub>                                                        |

| T <sub>RLRH</sub>                 | RD Pulse Width                         | T <sub>RLRH</sub>                                                         |

| T <sub>CLRH</sub>                 | RD Inactive Delay                      | T <sub>CLOV2</sub>                                                        |

| T <sub>RHLH</sub>                 | RD Inactive to ALE High                | T <sub>RHLH</sub>                                                         |

| T <sub>RHAV</sub>                 | RD Inactive to Address Active          | T <sub>RHAV</sub>                                                         |

| T <sub>CLDOX</sub>                | Data Hold Time                         | T <sub>CLOV2</sub>                                                        |

| T <sub>CVCTX</sub>                | Control Inactive Delay                 | T <sub>CLOV2</sub> (WR, INTA), T <sub>CHOV1</sub> (DEN)                   |

Table 3. 80C186XL to 80C186EA AC Timing Mnemonic Comparison (Continued)

| 80C186XL<br>AC Timing<br>Mnemonic | Parameter                                      | Equivalent 80C186EA<br>AC Timing Mnemonic                                       |

|-----------------------------------|------------------------------------------------|---------------------------------------------------------------------------------|

| T <sub>WLWH</sub>                 | WR Pulse Width                                 | Twlwh                                                                           |

| T <sub>WHLH</sub>                 | WR Inactive to ALE High                        | T <sub>WHLH</sub>                                                               |

| T <sub>WHDX</sub>                 | Data Hold after WR                             | T <sub>WHDX</sub>                                                               |

| T <sub>WHDEX</sub>                | WR Inactive to DEN Inactive                    | T <sub>WHDEX</sub>                                                              |

| T <sub>CKIN</sub>                 | CLKIN Period                                   | T <sub>C</sub>                                                                  |

| T <sub>CLCK</sub>                 | CLKIN Low Time                                 | T <sub>CL</sub>                                                                 |

| T <sub>CHCK</sub>                 | CLKIN High Time                                | T <sub>CH</sub>                                                                 |

| T <sub>CKHL</sub>                 | CLKIN Fall Time                                | T <sub>CF</sub>                                                                 |

| T <sub>CKLH</sub>                 | CLKIN Rise Time                                | T <sub>CR</sub>                                                                 |

| T <sub>CICO</sub>                 | CLKIN to CLKOUT Skew                           | T <sub>CD</sub>                                                                 |

| T <sub>CLCL</sub>                 | CLKOUT Period                                  | Т                                                                               |

| T <sub>CLCH</sub>                 | CLKOUT Low Time                                | T <sub>PL</sub>                                                                 |

| T <sub>CHCL</sub>                 | CLKOUT High Time                               | T <sub>PH</sub>                                                                 |

| T <sub>CH1CH2</sub>               | CLKOUT Rise Time                               | T <sub>PR</sub>                                                                 |

| T <sub>CL2CL1</sub>               | CLKOUT Fall Time                               | T <sub>PF</sub>                                                                 |

| T <sub>SRYCL</sub>                | Synchronous Ready (SRDY) Transition Setup Time | T <sub>CLIS</sub>                                                               |

| T <sub>CLSRY</sub>                | SRDY Transition Hold Time                      | T <sub>CLIH</sub>                                                               |

| T <sub>ARYCH</sub>                | ARDY Resolution Transition<br>Setup Time       | Тснін                                                                           |

| T <sub>CLARX</sub>                | ARDY Active Hold Time                          | T <sub>CLIH</sub>                                                               |

| T <sub>ARYCHL</sub>               | ARDY Inactive Holding Time                     | Тснін                                                                           |

| T <sub>ARYLCL</sub>               | Asynchronous Ready (ARDY)<br>Setup Time        | T <sub>CLIS</sub>                                                               |

| T <sub>INVCH</sub>                | INTx, NMI, TEST/BUSY, TMR IN<br>Setup Time     | Тснін                                                                           |

| T <sub>INVCL</sub>                | DRQ0, DRQ1 Setup Time                          | T <sub>CLIH</sub>                                                               |

| T <sub>CLTMV</sub>                | Timer Output Delay                             | T <sub>CLOV1</sub>                                                              |

| T <sub>CHQSV</sub>                | Queue Status Delay                             | Eliminated                                                                      |

| T <sub>RESIN</sub>                | RES Setup                                      | T <sub>CLIS</sub>                                                               |

| T <sub>HVCL</sub>                 | HOLD Setup                                     | T <sub>CLIS</sub>                                                               |

| T <sub>CLRO</sub>                 | Reset Delay                                    | T <sub>CLOV1</sub>                                                              |

| T <sub>CLHAV</sub>                | HLDA Valid Delay                               | T <sub>CLOV1</sub>                                                              |

| T <sub>CHCZ</sub>                 | Command Lines Float Delay                      | T <sub>CHOF</sub>                                                               |

| T <sub>CHCV</sub>                 | Command Lines Valid Delay (after Float)        | T <sub>CHOV1</sub> (A19:16, BHE, DT/R, S2:0, LOCK), T <sub>CHOV2</sub> (RD, WR) |

Please note DATA SHEET SPECIFICATIONS ARE SUBJECT TO CHANGE. If timing margins appear very tight in your new 80C186EA design, be sure to consider the difference in reference points for AC timings as well as the timing values. 80C186EA output specifications generally show equivalent or better maximum timings.

# 4.0 SYSTEM DESIGN CONSIDERATIONS

Microprocessor-based hardware falls into four broad categories: CPU, memory, peripheral logic and miscellaneous control logic. This section contains information applicable to each portion of your 80C186EA design. This section may be particularly helpful if you are considering a speed upgrade to an existing 80C186XL design.

# 4.1 Designing for High-Speed CPUs

High-speed design techniques are vital for all 80C186EA circuits. Anticipate significant switching noise on  $V_{\rm CC}$  and  $V_{\rm SS}$ . To reduce the impedance in power and ground connections, use a circuit board with power and ground planes and avoid sockets. Use a bypass capacitor for every logic device package and at least four for the 80C186EA.

Pay careful attention to board layout. Minimize trace lengths for clocks, buses and other high-frequency signals and terminate long bus lines wherever practical.

At 20 MHz, you may find that more memory devices and peripherals have trouble floating the data bus fast enough after a read operation. Compare the 80C186EA  $T_{RHAV}$  specification with the output float time given for the memory or peripheral. If the memory or peripheral cannot meet the timing requirement, you need to place it on a buffered bus to prevent bus contention.

# 4.2 Memory Speed Requirements

The following sections show access time requirements for various memory types. Note that 8 MHz calculations use 80L186EA timings and 10 MHz calculations use 80C186EA12 timings.

# 4.2.1 EPROM, FLASH MEMORY AND SRAM DEVICES

Access time from address valid to data valid for EPROM, flash memory and SRAMs is calculated as  $3 * T - T_{\rm CLOV2} - T_{\rm PD} - T_{\rm CLIS}.$  T is the CLKOUT period,  $T_{\rm CLOV2}$  is the maximum 80C186EA address output delay,  $T_{\rm PD}$  is the maximum propagation delay through an address latch, and  $T_{\rm CLIS}$  is the data setup time to the falling edge of  $T_4$  in an 80C186EA read cycle. Table 4 lists commonly available component access times which satisfy the timing requirements with at least a small amount of timing margin. At high frequencies, you may need faster memory than shown in the table to satisfy bus float time  $(T_{\rm RHAV})$  requirements.

Table 4. 80C186EA Access Time

Requirements for Flash Memory and SRAMs

| Speed<br>(MHz) | SRAM, Flash<br>Access Time | @<br>Wait States |

|----------------|----------------------------|------------------|

| 13             | 200<br>170                 | 1<br>0           |

| 20             | 120<br>85                  | 1<br>0           |

### 4.2.2 DRAM DEVICES

DRAMs have numerous critical timing parameters, so one computes DRAM speeds differently. The key parameters to consider are the DRAM's row access time and cycle time. Cycle time relates directly to the minimum length of a processor bus cycle. The timing analysis must also consider delays introduced by the DRAM controller, a necessary circuit for any DRAM memory system.

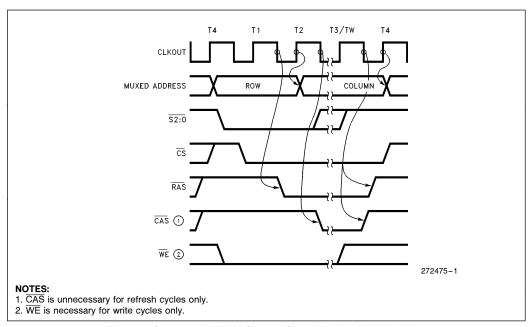

The DRAM control timing relationships shown in Figure 1 are well-proven compromises between DRAM requirements and the 80C186 Modular Core's four-state bus cycle. The DRAM controller generates Row Address Strobe ( $\overline{RAS}$ ) approximately on the falling edge of  $T_2$ . Access time from  $\overline{RAS}$  is calculated as  $2*T-TpD-T_{CLIS}$ . T is the CLKOUT period,  $T_{PD}$  is the propagation delay from falling CLKOUT to  $\overline{RAS}$  active due to the DRAM controller, and  $T_{CLIS}$  is the data setup time to the falling edge of  $T_4$ . If the DRAM controller cannot meet specifications for the  $\overline{RAS}$  to column address Strobe) delay or the  $\overline{RAS}$  to column address delay, you can compute access time differently. Table 5 lists common component access times which satisfy the timing requirements with at least a small amount of timing margin. At high fre-

quencies, you may need faster DRAMs than shown in the table to satisfy bus float time requirements. Section 4.4.2 and Appendix A discuss using DRAMs in more detail.

Table 5. 80C186EA Access Time Requirements for DRAMs

| Speed<br>(MHz) | DRAM<br>Access Time | @<br>Wait States |

|----------------|---------------------|------------------|

| 13             | 150                 | 1                |

|                | 120                 | 0                |

| 20             | 120                 | 1                |

|                | 70                  | 0                |

Figure 1. Suggested DRAM Control Signal Timing Relationships

13

# 4.3 Peripheral Logic

The application usually dictates the choice of peripherals. If a peripheral is too slow or lacks the necessary interface signals, the user adds extra components to generate wait states, buffer the bus or form control log-

Among the peripheral devices used with the 80C186EA is Intel's 80C187 numerics coprocessor. Intel does not market a 20 MHz version of the 80C187. However, the interface is asynchronous and all speed combinations meet all timing requirements. This includes a 20 MHz 80C186EA and a 16 MHz 80C187.

### 4.4 Miscellaneous Control Logic

This broad category includes all the "glue logic" necessary to make the rest of the system work, including such circuits as:

- DRAM Controllers

- Controllers for pseudo-static RAMs and dual-ported memory

- Wait State Generators (extra chip-selects, too)

- Bus Control Signal Decoders

- DMA Acknowledge Generators

- Bus Arbiters

- Peripheral Interfaces

- · Control and Diagnostic Registers

In some cases, this logic must synthesize signals not directly provided by the processor to "glue on" peripherals. In other cases, this circuitry must overcome timing mismatches or errata. Some of these logic subsystems must synchronously track the operation of the 80C186EA and its control signals. With higher CPU speeds and shorter minimum AC timings, the 80C186EA may require faster logic for bus tracking than its standard 80C186 predecessor.

The remainder of Section 4.4 describes situations which call for special control logic.

# 4.4.1 CHIP-SELECTS AND WAIT STATE GENERATION

The 80C186EA chip-select unit is identical to the standard 80C186 chip-select unit. It is not possible to cover the entire one Mbyte address space with the chip-selects provided. The maximum number of programmable wait states is three, which may be a limitation at high frequencies. 80C186EA users may need additional decoding circuitry to generate chip-selects and control the Asynchronous Ready (ARDY) or Synchronous Ready (SRDY) input pins to generate wait states. (The 80C186EB and the 80C186EC have an improved chip-select unit which overcomes such limitations.)

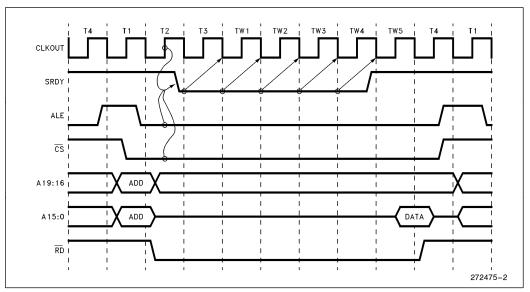

Figure 2 is an 80C186EA bus cycle with five wait states. You can build a synchronous wait state generator using a programmable logic device (PLD) clocked by the CPU's CLKOUT. The circuit samples ALE and a programmed chip-select pin. At the rising edge of T<sub>2</sub>, the wait state generator drives the SRDY input low. The processor samples SRDY low at the falling edge of T<sub>3</sub> and each falling CLKOUT edge during the wait states. When the wait state generator counts up to the fourth wait state, it drives SRDY high on rising clock. After the 80C186EA samples SRDY high, it runs the fifth wait state before continuing with T<sub>4</sub>.

There are several timings to check carefully for this wait state controller. The PLD flip-flops must need a hold time less than 3 ns because that is the minimum value for the 80C186EA's ALE valid (T<sub>CHOV1</sub>) and chip-select valid (T<sub>CHOV2</sub>) specifications. The PLD must also be fast enough so that the minimum CLKOUT High Time (T<sub>PH</sub>) minus the maximum PLD Clock to Output Valid Time (T<sub>CO</sub>) is greater than the minimum SRDY setup time (T<sub>CLIS</sub>).

Figure 2. 80C186EA Bus Cycles with Five Wait States

### 4.4.2 DRAM CONTROL

All members of the 80C186 modular core family contain a refresh control unit. A complete DRAM controller requires additional circuitry outside the processor even in the simplest configurations.

There are four basic functions which a DRAM controller must provide:

- Map 80C186EA-generated addresses into the DRAM address pins.

- Translate processor control signals into DRAM control signals.

- Refresh the DRAMs at regular intervals.

- Overcome loading and transmission line effects.

Turn back to Figure 1 and examine the DRAM bus cycle. A general DRAM cycle has six phases:

- 1. First, the controller supplies a row address to the DRAM (meeting setup and hold times).

- 2. Next, the controller asserts  $\overline{RAS}$ , which latches the row address inside the DRAMs.

- 3. Then the controller supplies a column address to the DRAMs (meeting setup and hold times). Row and column addresses are multiplexed on the same DRAM pins to minimize the pin count.

- The controller asserts a CAS, which latches the column address inside the DRAMs.

- Data is written to the DRAM if Write Enable (WE) is asserted. Otherwise, the DRAM drives data on the bus for a read operation.

- After the strobes go inactive, the controller must provide a recovery interval (RAS precharge) before the next cycle.

In the simplest DRAM refresh scheme, the controller provides only row addresses and  $\overline{RAS}$  to perform DRAM refresh on a row-by-row basis. Appendix A describes an 80C186EA DRAM controller in detail.

# 4.4.3 82C59A INTERFACE

A popular peripheral for the 80C186EA is the 82C59A programmable interrupt controller. Unfortunately, the speed selections of the 82C59A have not kept up with the increasing speed capability of the 80C186 family.

For the 80C186 family, find the fastest 82C59A you can. At least one vendor manufactures a "10 MHz" version which avoids frustrating interface problems. The 82C59A is not a clocked device; "10 MHz" refers to a microprocessor speed to which it is matched. The following recommendations are based on using a "10 MHz" 82C59A device with a 16 MHz or 20 MHz 80C186EA.

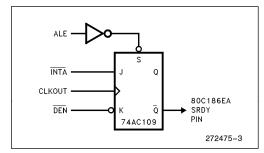

Read access time for the 82C59A is calculated as 3 \* T -  $T_{CLOV2} - T_{PD} - T_{CLIS}$ . The 80C186EA's minimum read, write and interrupt acknowledge ( $\overline{INTA}$ ) pulse width is (2 \* T) - 5. Bus accesses to the 82C59A must have at least one wait state. The wait state gives the 82C59A longer to return data to the 80C186EA and it ensures the widths of the  $\overline{RD}$ ,  $\overline{WR}$  and  $\overline{INTA}$  strobes are wide enough for the 82C59A. Program a peripheral chip-select to provide wait states during 82C59A read and write cycles. Wait states for 82C59A INTA cycles require an external wait state generator (see Figure 3) because programmable chip-selects do not apply to INTA cycles.

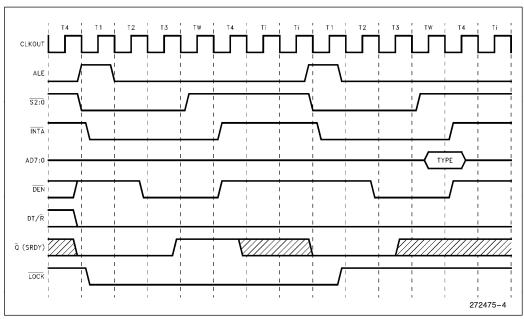

Figure 4 shows 80C186EA Cascade Mode INTA cycles with wait state control furnished by the 74AC109 J- $\overline{K}$  Flip-Flop circuit of Figure 3. Inverted ALE asynchronously sets the flip-flop on every bus cycle, driving the  $\overline{Q}$  output to a logic 0. The  $\overline{Q}$  output connects to the processor's  $\overline{SRDY}$  pin. At the rising edge of  $T_2$ , the J input from  $\overline{INTA}$  is a logic 0 and the  $\overline{K}$  input from

$\overline{DEN}$  is a logic 1, so the flip-flop state does not change. The CPU asserts  $\overline{DEN}$  upon rising  $T_2.$  On the falling edge of  $T_3$ , the 80C186EA recognizes SRDY as low and prepares to insert one wait state. At the rising edge of  $T_3$ , both inputs to the flip-flop are low, clearing the flip-flop. At the falling edge of  $T_W$ , the processor recognizes SRDY as high and prepares to terminate the bus cycle.

Figure 3. Wait State Generator for 82C59A Interface (1 Wait State)

This simple circuit drives the SRDY input signal to logic 0 on non-INTA cycles. Provide bus ready for other bus cycle types through chip-select programming or the ARDY pin. Also note that the timing margin for the SRDY setup time T<sub>CLIS</sub> disappears as the processor speed approaches 20 MHz.

Figure 4. 80C186EA Cascade Mode INTA Cycles with One Wait State

Lock all reads and writes to the control registers of the 82C59A with the LOCK instruction prefix. This precaution ensures meeting the 82C59A Command Recovery Time for dissimilar cycles by inserting two idle T-states at the end of reads and writes. The 80C186EA automatically adds two idle states to each INTA bus cycle (see Figure 4), ensuring the system meets a similar recovery time specification for back-to-back INTA cycles.

Finally, be sure to place the 82C59A on a buffered data bus. At high CPU speeds the interrupt controller cannot float its data buffers fast enough after read cycles to avoid contention with the microprocessor.

# 5.0 OTHER UPGRADE CONSIDERATIONS

The following is a rundown of all known 80C186XL errata and their disposition on the 80C186EA:

• INTx/INTAx Errata—If an external 82C59A is cascaded into one of the 80C186XL interrupt pins, a higher priority interrupt may cause the cascaded interrupt not to be acknowledged. This only occurs in cascade mode and is corrected on the C-Step 80C186XL.

This errata also occurred on the 80C186EA, but is corrected on the C-Step as well.

The 80C186EA has one register not found on the standard 80C186XL. The Power Control Register (PWRCON) is located at offset F2H. It enables and disables idle mode and powerdown (see Section 3.8). Check existing software for writes to the power control register location. Accidentally programming the register with either 0000H or FFFFH disables both modes.

# APPENDIX A 80C186EA DRAM CONTROLLER EXAMPLE

This section demonstrates how to incorporate the 80C186EA DRAM Refresh Unit into a fully functional DRAM control system.

# A.1 Design Requirements

Designing DRAM controllers is not as intuitive as designing other types of digital logic. DRAMs pose particularly fussy timing problems, and the choices of access time, wait states and refresh method can be overwhelming. This design applies only to the basic DRAM access method described in Section 4.2.2. DRAM systems employing the basic access method are suitable for most 80C186EA designs.

A successful controller must respond correctly to all 80C186EA bus cycles. It must discriminate between bus cycles intended for the DRAMs and other accesses. For DRAM bus cycles, it must generate all the necessary outputs, including chip-selects, Write Enables and Output Enables, with timing relationships similar to

Figure 1. It must also be fast enough to not require excessive wait states.

# A.2 What the 80C186EA Provides

The 80C186EA bus interface unit provides 20-bit addresses for routine read and write cycles. The integrated RCU provides similar 20-bit addresses for refresh cycles. The benefits of the DRAM refresh feature come from how the 80C186EA generates them and encodes them in the control signals.

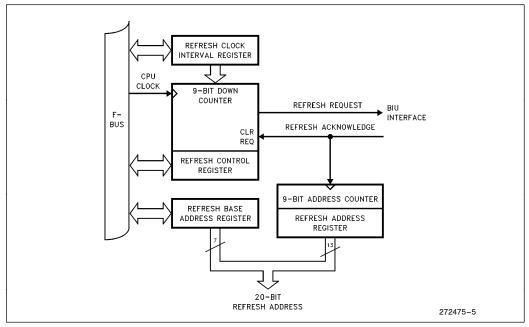

Figure 5 is a block diagram of the RCU. It consists of a nine-bit timing counter, a nine-bit address counter, three control registers and interface logic. When the RCU is enabled, the timing counter decrements every CLKOUT cycle until it reaches a count of 1. At that time a refresh bus request is initiated, the timing counter reloads, and the operation continues. A refresh bus cycle has high priority, and runs as soon as the 80C186EA bus is free.

Figure 5. 80C186EA Refresh Control Unit Block Diagram

80C186 users refer to refresh bus cycles as "dummy read" cycles. They appear on the 80C186EA bus like ordinary read cycles except that no data is transferred. The states of  $\overline{BHE}/\overline{RFSH}$  (Byte High Enable/Refresh) and A0 identify refresh cycles according to Table 5.

Table 5. Identification of 80C186EA/80C188EA

Refresh Cycles

| Data Bus Width | BHE/RFSH | A0 |

|----------------|----------|----|

| 80C186EA       | 1        | 1  |

| 80C188EA       | 0        | 1  |

# A.3 The Design Solution

Several vendors offer fully-integrated, single-chip DRAM controllers. Some of these devices are useful with the 80C186EA. However, most designers prefer to design their own DRAM controllers for the following reasons:

- Off-the-shelf DRAM controllers are relatively expensive, rivaling the cost of the 80C186EA.

- Off-the-shelf DRAM controllers may have relatively high pin counts and power needs. Such devices are more appropriate for larger DRAM arrays than those commonly used with the 80C186 family.

- Off-the-shelf DRAM controllers may not be a "best fit" because of slow operation or lack of flexibility for specific applications.

Off-the-shelf DRAM controllers may offer special features such as nibble, page and static-column modes, which are not commonly used in 80C186 family designs. Therefore, the user may be paying for excess functionality.

DRAM controllers can be implemented using discrete logic, delay lines, programmable logic devices or some combination. Analog delay lines provide accurate timing relationships, but are inflexible and require additional discrete logic. Discrete logic alone takes excessive board space due to complex state logic and decoding.

A PLD solution (with or without additional discrete logic) is a good choice. PLDs have the following advantages:

- PLDs are available in speed selections to match the processor's speed.

- A wide variety of PLDs are available for optimal price versus performance.

- PLDs are ideal for a mixture of synchronous state logic and combinatorial decoding logic.

- PLDs are flexible and allow rapid design changes.

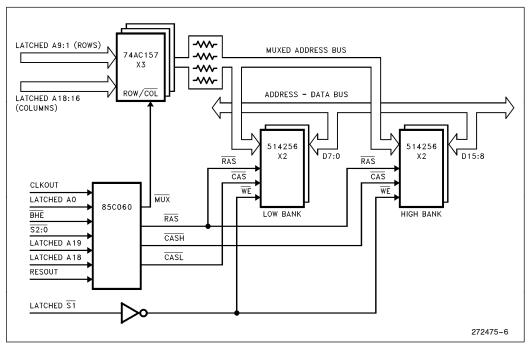

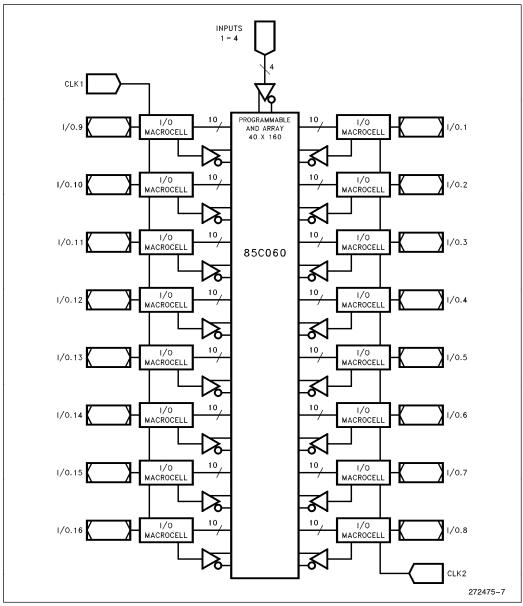

The next section presents a design solution using the Intel 85C060 CMOS Programmable Logic Device. The 85C060 contains all the decoding and state logic. 74AC157s multiplex the row and column addresses.

# A.3.1 DESIGN OVERVIEW

Figure 6 is a block diagram of the DRAM controller and memory array. Address decoding within the controller selects the memory devices, so the user can readily change the base address (40000H as tested) or the array size (512 Kbytes as tested). Intel verified this design in the laboratory and incorporated it into the EV80C186EA/XL Evaluation Board. This board runs at 20 MHz, accessing Toshiba TC514256AP-70 DRAMs with zero wait states.

The 85C060 is a general purpose, 16-macrocell device. The 85C060 has several advantages over other programmable devices for this design. It is relatively high-speed, allowing the DRAM controller to work up to 20 MHz with the -15 ( $T_{\rm PD}=15~{\rm ns}$ ) version. It has eight product terms per macrocell. The 85C060 also has an asynchronous clocking option, which is very advantageous in this design.

The DRAM controller uses nine of the 85C060's 24 pins as inputs. It uses nine macrocells, with a maximum of five product terms per macrocell.

Figure 6. 80C186EA DRAM Memory System Block Diagram

Figure 7. Intel 85C060 Architecture Diagram

# A.3.2 HOW THE DESIGN SOLVES THE PROBLEM

Study Figure 1 once more. The 80C186EA's status signals  $\overline{S2.0}$  can be conveniently decoded to detect the bus cycle beginning, type and end. However, notice that the status lines go active on a *rising* CLKOUT edge and inactive on a *falling* CLKOUT edge.  $\overline{RAS}$  and  $\overline{CAS}$  should both go active on *falling* clock edges and our controller should toggle between row and column addresses near the *rising* CLKOUT edge in between.

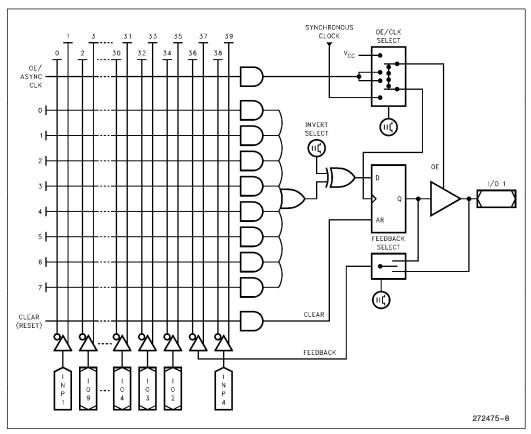

A good solution should somehow operate on both edges of the processor's CLKOUT signal and that is exactly what the 85C060 does. With the asynchronous clocking option, each 85C060 macrocell can derive its clock separately from the programmable AND array. The DRAM controller uses CLKOUT as an input. The 85C060 input buffers provide both true and comple-

mented signals to the programmable array (see Figure 8) so each edge of CLKOUT can clock some of the macrocells. The maximum skew between the true and complemented signals is about 500 ps and can be neglected in a timing analysis.

The dual state machine aspect of the 85C060 makes the DRAM controller independent of wait states. It uses the 80C186EA's  $\overline{52.0}$  lines to sense the end of the bus cycle rather than just counting clocks. This dependence on the status lines does have a drawback. The 80C186EA's minimum specifications for  $T_{CHOV1}$  (Status Active) and  $T_{CLOV2}$  (Status Inactive) are both 3 ns. In asynchronous clock mode, the 85C060 has a minimum hold time  $T_{AH}$  of 6 ns. The solution is to avoid using status signals directly. A decoded status signal feeds back to the programmable AND array through a macrocell, adding enough delay time to meet the hold requirement.

Figure 8. 85C060 Macrocell Architecture with D-Type Flip-Flop Configuration

### A.3.3 HOW THE DRAM CONTROLLER WORKS

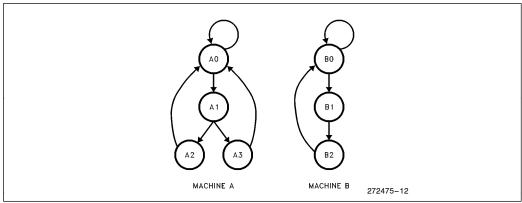

Figure 9 lists the complete source code for the DRAM controller. It consists mostly of two interconnected

state machines. State Machine A and the address multiplexing signal  $(\overline{MUX})$  are clocked on rising CLKOUT. State Machine B and the logic for  $\overline{RAS}$  and  $\overline{CAS}$  are clocked on falling CLKOUT.

```

DRAMCON;

Name

Partno

80C186EA/XL-xxx;

Revision

01;

8/9/91;

Date

LARRY BATES;

Designer

Company

Intel EMD Applications;

28-Pin EPLD;

Assembly

Uxx;

Location

Device

EP600;

/* Compilation switch */

/* Target Device Type: Intel 85C060-15

/* File written for the CUPL PLD Design Program.

/* CUPL is a trademark of Logical Devices Inc.

/** Inputs **/

pin 3 = nS0;

/* Status pins need pullups because the

pin 4 = nS1;

/* processor will not always drive them.

pin 5 = nS2;

pin 8 = LA19;