# Mobile Intel<sup>®</sup> Celeron<sup>®</sup> Processor (0.18µ and 0.13µ) Specification Update

Release Date: November 2001

Order Number: 245421-021

The Mobile Intel® Celeron® processor (0.18µ and 0.13µ) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Information in this document is provided in connection with Intel® products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document.

Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Mobile Intel® Celeron® processor (0.18µ and 0.13µ) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

Intel®, Pentium®, Celeron®, and Xeon ™ are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries

\*Other names and brands may be claimed as the property of others.

Copyright © 1998-2001, Intel Corporation

i

# **CONTENTS**

| REVISION HISTORY                                                                      | ii |

|---------------------------------------------------------------------------------------|----|

| PREFACE                                                                               | iv |

| GENERAL INFORMATION                                                                   | 1  |

| Mobile Intel® Celeron® Processor (Micro-PGA2) Markings                                | 1  |

| Mobile Intel® Celeron® Processor (BGA2) Markings                                      | 2  |

| Mobile Intel <sup>®</sup> Celeron <sup>®</sup> Processor 0.18μ (Micro-FCPGA) Markings | 3  |

| Mobile Intel <sup>®</sup> Celeron <sup>®</sup> Processor 0.18μ (Micro-FCBGA) Markings | 4  |

| Mobile Intel <sup>®</sup> Celeron <sup>®</sup> Processor 0.13μ (Micro-FCPGA) Markings | 5  |

| Mobile Intel <sup>®</sup> Celeron <sup>®</sup> Processor 0.13μ (Micro-FCBGA) Markings | 6  |

| Intel® Celeron® Processor Mobile Module Markings                                      | 7  |

| IDENTIFICATION INFORMATION                                                            | 9  |

| SUMMARY OF CHANGES                                                                    | 14 |

| Summary of Errata                                                                     | 15 |

| Summary of Documentation Changes                                                      | 20 |

| Summary of Specification Clarifications                                               | 20 |

| Summary of Specification Changes                                                      | 21 |

| ERRATA                                                                                | 22 |

| DOCUMENTATION CHANGES                                                                 | 61 |

| SPECIFICATION CLARIFICATIONS                                                          | 64 |

| SPECIFICATION CHANGES                                                                 | 66 |

# **REVISION HISTORY**

| Date of Revision | Version | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2000    | -001    | Initial release                                                                                                                                                                                                                                                                                                                                                                                          |

| March 2000       | -002    | Revised Errata M38, M43, and M47. Added Erratum M53. Added new Specification Clarification M1.                                                                                                                                                                                                                                                                                                           |

| April 2000       | -003    | Updated the Preface with new references; Updated "Intel Celeron Processor Mobile Module Markings" section; Updated Identification Information for BGA2, micro-PGA2 packages, and mobile modules; Updated Erratum M34; Added Erratum M54; Added Documentation Change M5; Added Specification Clarifications M2, M3.                                                                                       |

| May 2000         | -004    | Updated Identification Information for mobile modules. Updated Erratum M53. Added Erratum M55, M56                                                                                                                                                                                                                                                                                                       |

| June 2000        | -005    | Updated the Preface with new document references; Updated Identification Information for BGA2, micro-PGA2 packages, and mobile modules. Added Erratum M57.                                                                                                                                                                                                                                               |

| July 2000        | -006    | Updated Identification Information for BGA2, micro-PGA2 packages, and mobile modules; Updated Summary of Changes Tables to include C0-step products; Added Erratum M58, M59; Updated the Specification Clarifications and Documentation Changes section by removing old items that were incorporated in the new documents referenced in this spec update; Added new Specification Clarifications M1, M2. |

| August 2000      | -007    | Added Erratum M60.                                                                                                                                                                                                                                                                                                                                                                                       |

| September 2000   | -008    | Added Erratum M61, M62; Revised Erratum M22, M43, M52; Added Documentation Changes M5, M6.                                                                                                                                                                                                                                                                                                               |

| October 2000     | -009    | Updated the list of referenced documents in the preface;<br>Updated Identification Information for BGA2, micro-PGA2<br>packages, and mobile modules; Added Erratum M63; Added<br>Documentation Changes M7, M8                                                                                                                                                                                            |

| November 2000    | -010    | Added Erratum M64.                                                                                                                                                                                                                                                                                                                                                                                       |

| December 2000    | -011    | Updated Specification Update product key to include the Intel® Pentium® 4 processor, Revised Erratum M2; Added Documentation Changes M9 thru M14                                                                                                                                                                                                                                                         |

| January 2001     | -012    | Revised Erratum M2; Added Documentation Changes M15, M16.                                                                                                                                                                                                                                                                                                                                                |

| February 2001    | -013    | Updated the list of referenced documents in the preface;<br>Updated Identification Information for BGA2 packages; Revised<br>Documentation Change M15 and Added M17.                                                                                                                                                                                                                                     |

# **REVISION HISTORY**

| Date of Revision | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2001       | -014    | Added Erratum M65 and M66. Revised Specification Clarification M2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| April 2001       | -015    | Updated the list of referenced documents in the preface;<br>Updated Identification Information for BGA2 and micro-PGA2<br>packages; Updated the Specification Clarifications section by<br>removing old items that were incorporated in the new<br>documents referenced in this spec update.                                                                                                                                                                                                                                                                                                                                                                                                        |

| May 2001         | -016    | Updated the list of referenced documents in the preface;<br>Updated Identification Information for BGA2 and micro-PGA2<br>packages; Changed "NoFix" plan for Erratum K38 to "Fixed" in<br>D0 stepping; Added Erratum M67.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| June 2001        | -017    | Updated Summary of Changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| July 2001        | -018    | Updated the list of referenced documents in the preface;<br>Updated Identification Information for BGA2 and micro-PGA2<br>packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| August 2001      | -019    | Updated Summary of Changes; Added Erratum M68 and M69; Added Documentation Change M18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| October 2001     | -020    | Updated list of referenced documents in the preface; Updated the Celeron® mark to a registered trademark; Added micro-FCPGA and micro-FCBGA package marking diagrams for Mobile Intel Celeron Processor (0.18µ and 0.13µ) to general information section; Added identification information for Mobile Intel Celeron Processor (0.18µ and 0.13µ) micro-FCPGA and micro-FCBGA packages; Updated Summary of Changes; Updated columns with FBD0, FPD0, FPA1, FBA1 steppings in Summary of Changes; Added Errata M2AP and M70; Updated the Documentation Changes by removing old items that were incorporated in the new documents references in this spec update; Added Specification Clarification M1. |

| November 2001    | -021    | Updated Summary of Changes; Added Documentation Changes M1, M2, M3, M4, M5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **PREFACE**

This document is an update to the specifications contained in the following documents:

- Mobile Intel® Celeron® Processor in BGA2 and Micro-PGA2 Packages at 900 MHz, 850 MHz, 800 MHz, 750 MHz, 700 MHz, 650 MHz, 600 MHz, 550 MHz, 500 MHz, 450 MHz, Low voltage 600 MHz, Low voltage 500 MHz, Low voltage 400A MHz, Ultra Low Voltage 600MHz and Ultra Low Voltage 500 MHz datasheet (Order Number 283654-003)

- Mobile Intel® Celeron® Processor (0.18) in Micro-FCBGA and Micro-FCPGA packages at 933, 866, 800A, and 733 MHz (Order Number 298514-001)

- Mobile Intel<sup>®</sup> Celeron<sup>®</sup> Processor (0.13) in Micro-FCBGA in Low Voltage Package at 650 MHz (Order Number 298517-001)

- Intel® Celeron® Processor Mobile Module: Mobile Module Connector 2 (MMC-2) at 700 MHz, 650 MHz, 600 MHz, 550 MHz, 500 MHz and 450 MHz datasheet (Order Number 243357-005)

- Intel Architecture Software Developer's Manual, Volumes 1, 2, and 3 (Order Numbers 243190, 243191, and 243192, respectively)

- P6 Family of Processors Hardware Developer's Manual (Order Number 244001)

This document intended for hardware system manufacturers and software developers of applications, operating systems, or tools. It contains Errata, Documentation Changes, Specification Clarifications, and Specification Changes.

#### Nomenclature

**S-Spec Number** is a five-digit code used to identify products. Products are differentiated by their unique characteristics, e.g., core speed, L2 cache size, package type, etc. as described in the processor identification information table. Care should be taken to read all notes associated with each S-Spec number.

**Errata** are design defects or errors. Errata may cause the processor's behavior to deviate from published specifications. Hardware and software designed to be used with any given processor must assume that all errata documented for that processor are present on all devices unless otherwise noted.

**Documentation Changes** include errors (including typographical), or omissions from the current published specifications. These changes will be incorporated in the next release of the appropriate documentation(s).

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the appropriate documentation(s).

**Specification Changes** are modifications to the current published specifications for the processor. These changes will be incorporated in the next release of the appropriate documentation(s).

# Specification Update for the Mobile Intel<sup>®</sup> Celeron<sup>®</sup> Processor (0.18μ and 0.13μ)

# **GENERAL INFORMATION**

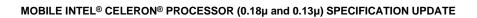

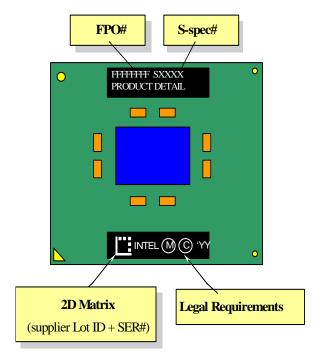

## Mobile Intel® Celeron® Processor (Micro-PGA2) Markings

1

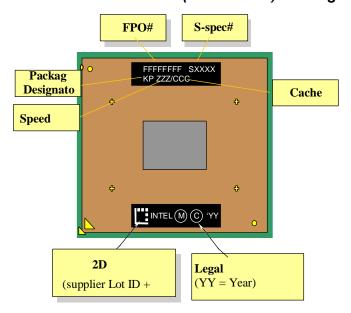

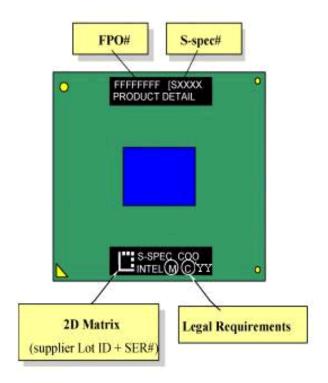

# Mobile Intel® Celeron® Processor (BGA2) Markings

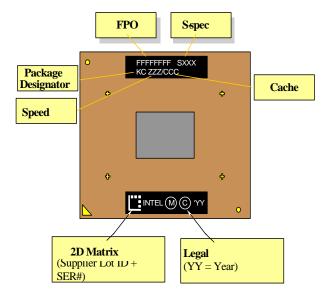

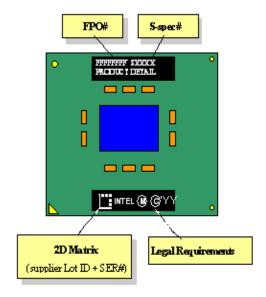

# Mobile Intel<sup>®</sup> Celeron<sup>®</sup> Processor 0.18μ (Micro-FCPGA) Markings

# Mobile Intel<sup>®</sup> Celeron<sup>®</sup> Processor 0.18μ (Micro-FCBGA) Markings

# Mobile Intel® Celeron® Processor 0.13µ (Micro-FCPGA) Markings

# Mobile Intel<sup>®</sup> Celeron<sup>®</sup> Processor 0.13μ (Micro-FCBGA) Markings

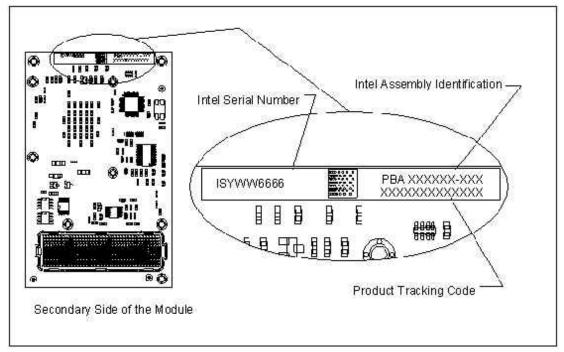

## Intel® Celeron® Processor Mobile Module Markings

The Product Tracking Code (PTC) determines the Intel assembly level of the module. The PTC is on the secondary side of the module and provides the following information:

Example: PMN70001201AA

The PTC will consist of 13 characters as identified in the above example and can be broken down as follows:

#### **AABCCCDDEEEFF**

Definition:

AA - Processor Module = PM

B - Celeron Processor (.18 $\mu$ ) Mobile Module (MMC-2) = N CCC - Speed Identity = 700, 650, 600, 550, 500 or 450, etc.

DD - Cache Size = 01 (128 KB)

EEE - Notifiable Design Revision (Start at 001)

FF - Notifiable Processor Revision (Start at AA)

Note: For other Intel Mobile Modules, the second field (B) is defined as:

Pentium® II Processor Mobile Module (MMC-1) = D Pentium® II Processor Mobile Module (MMC-2) = E

Pentium® II Processor Mobile Module With On-die Cache (MMC-1) = F Pentium® II Processor Mobile Module With On-die Cache (MMC-2) = G

Celeron® Processor Mobile Module (MMC-1) = H Celeron® Processor Mobile Module (MMC-2) = I Pentium® III Processor Mobile Module = L

Pentium® III Processor Mobile Module Featuring Intel® SpeedStep™

Technology = M

Intel® Celeron® Processor Mobile Module at 650 MHz, 600 MHz, 550 MHz, 500 MHz and 450 MHz

#### **IDENTIFICATION INFORMATION**

The Mobile Intel® Celeron® processor (0.18µ and 0.13µ) can be identified by the following values:

| Family <sup>1</sup> | Model <sup>2</sup> | Brand ID <sup>3</sup> |

|---------------------|--------------------|-----------------------|

| 0110                | 1000               | 0000001               |

#### NOTES:

- 1. The Family corresponds to bits [11:8] of the EDX register after Reset, bits [11:8] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Device ID register accessible through Boundary Scan.

- 2. The Model corresponds to bits [7:4] of the EDX register after Reset, bits [7:4] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the model field of the Device ID register accessible through Boundary Scan.

- 3. The Brand ID is returned by the CPUID instruction in the EBX[7:0] when CPUID is executed with the value of 1 in the EAX.

#### Intel® Mobile Celeron® Processor (0.18µ) in BGA2 and micro-PGA2 Packages Identification Information

| S-Spec | Product<br>Stepping | CPUID | Speed (MHz)<br>Core/Bus | Integrated L2<br>Size (Kbytes) | Package | Notes |

|--------|---------------------|-------|-------------------------|--------------------------------|---------|-------|

| SL3UL  | BA2                 | 0681h | 400/100                 | 128                            | BGA2    | 1     |

| SL43W  | BB0                 | 0683h | 400/100                 | 128                            | BGA2    | 1     |

| SL45A  | BB0                 | 0683h | 500/100                 | 128                            | BGA2    | 1     |

| SL3PD  | BA2                 | 0681h | 450/100                 | 128                            | BGA2    | 2     |

| SL43T  | BB0                 | 0683h | 450/100                 | 128                            | BGA2    | 2     |

| SL3PC  | BA2                 | 0681h | 500/100                 | 128                            | BGA2    | 2     |

| SL43Q  | BB0                 | 0683h | 500/100                 | 128                            | BGA2    | 2     |

| SL3ZE  | BB0                 | 0683h | 550/100                 | 128                            | BGA2    | 2     |

| SL4AR  | BB0                 | 0683h | 600/100                 | 128                            | BGA2    | 2     |

| SL4AD  | BB0                 | 0683h | 650/100                 | 128                            | BGA2    | 2     |

| SL4J8  | BC0                 | 0686h | 400/100                 | 128                            | BGA2    | 1     |

| SL4JC  | BC0                 | 0686h | 450/100                 | 128                            | BGA2    | 2     |

| SL4JD  | BC0                 | 0686h | 500/100                 | 128                            | BGA2    | 2     |

| SL4J9  | BC0                 | 0686h | 500/100                 | 128                            | BGA2    | 1     |

| SL4ZR  | BC0                 | 0686h | 500/100                 | 128                            | BGA2    | 3     |

Intel® Mobile Celeron® Processor (0.18 $\mu$ ) in BGA2 and micro-PGA2 Packages Identification Information

| S-Spec | Product<br>Stepping | CPUID | Speed (MHz)<br>Core/Bus | Integrated L2<br>Size (Kbytes) | Package    | Notes |

|--------|---------------------|-------|-------------------------|--------------------------------|------------|-------|

| SL4JE  | BC0                 | 0686h | 550/100                 | 128                            | BGA2       | 2     |

| SL4JF  | BC0                 | 0686h | 600/100                 | 128                            | BGA2       | 2     |

| SL4JG  | BC0                 | 0686h | 650/100                 | 128                            | BGA2       | 2     |

| SL4GU  | BC0                 | 0686h | 700/100                 | 128                            | BGA2       | 2     |

| SL56P  | BC0                 | 0686h | 750/100                 | 128                            | BGA2       | 2     |

| SL5DR  | BD0                 | 068Ah | 500/100                 | 128                            | BGA2       | 3     |

| SL5V5  | BD0                 | 068Ah | 600/100                 | 128                            | BGA2       | 4     |

| SL5DS  | BD0                 | 068Ah | 600/100                 | 128                            | BGA2       | 3     |

| SL582  | BD0                 | 068Ah | 600/100                 | 128                            | BGA2       | 1     |

| SL53V  | BD0                 | 068Ah | 700/100                 | 128                            | BGA2       | 2     |

| SL53U  | BD0                 | 068Ah | 750/100                 | 128                            | BGA2       | 2     |

| SL57X  | BD0                 | 068Ah | 800/100                 | 128                            | BGA2       | 2     |

| SL57Y  | BD0                 | 068Ah | 850/100                 | 128                            | BGA2       | 2     |

| SL3PF  | PA2                 | 0681h | 450/100                 | 128                            | Micro-PGA2 | 2     |

| SL43U  | PB0                 | 0683h | 450/100                 | 128                            | Micro-PGA2 | 2     |

| SL3PE  | PA2                 | 0681h | 500/100                 | 128                            | Micro-PGA2 | 2     |

| SL43R  | PB0                 | 0683h | 500/100                 | 128                            | Micro-PGA2 | 2     |

| SL3ZF  | PB0                 | 0683h | 550/100                 | 128                            | Micro-PGA2 | 2     |

| SL4AP  | PB0                 | 0683h | 600/100                 | 128                            | Micro-PGA2 | 2     |

| SL4AE  | PB0                 | 0683h | 650/100                 | 128                            | Micro-PGA2 | 2     |

| SL4JS  | PC0                 | 0686h | 450/100                 | 128                            | Micro-PGA2 | 2     |

| SL4JT  | PC0                 | 0686h | 500/100                 | 128                            | Micro-PGA2 | 2     |

| SL4JU  | PC0                 | 0686h | 550/100                 | 128                            | Micro-PGA2 | 2     |

| SL4JV  | PC0                 | 0686h | 600/100                 | 128                            | Micro-PGA2 | 2     |

| SL4JW  | PC0                 | 0686h | 650/100                 | 128                            | Micro-PGA2 | 2     |

| SL4GX  | PC0                 | 0686h | 700/100                 | 128                            | Micro-PGA2 | 2     |

#### MOBILE INTEL® CELERON® PROCESSOR (0.18μ and 0.13μ) SPECIFICATION UPDATE

#### Intel® Mobile Celeron® Processor (0.18µ) in BGA2 and micro-PGA2 Packages Identification Information

| S-Spec | Product<br>Stepping | CPUID | Speed (MHz)<br>Core/Bus | Integrated L2<br>Size (Kbytes) | Package    | Notes |

|--------|---------------------|-------|-------------------------|--------------------------------|------------|-------|

| SL56Q  | PC0                 | 0686h | 750/100                 | 128                            | Micro-PGA2 | 2     |

| SL53D  | PD0                 | 068Ah | 700/100                 | 128                            | Micro-PGA2 | 2     |

| SL53C  | PD0                 | 068Ah | 750/100                 | 128                            | Micro-PGA2 | 2     |

| SL584  | PD0                 | 068Ah | 800/100                 | 128                            | Micro-PGA2 | 2     |

| SL585  | PD0                 | 068Ah | 850/100                 | 128                            | Micro-PGA2 | 2     |

#### NOTES:

1.  $VID[4:0] = 01101; V_{CC\_CORE} = 1.35 V$

2.  $VID[4:0] = 01000; V_{CC\_CORE} = 1.60 V$

3.  $VID[4:0] = 10111; V_{CC\_CORE} = 1.10 V$

4. VID[4:0] = 10101; VCC\_CORE = 1.15V

| Identification information for Mobile Celeron® (0.18μ) Micro-FCBGA and Micro-FCPGA Packages |                     |       |                         |                                |             |       |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|---------------------|-------|-------------------------|--------------------------------|-------------|-------|--|--|--|--|--|--|

| S-Spec                                                                                      | Product<br>Stepping | CPUID | Speed (MHz)<br>Core/Bus | Integrated L2<br>Size (Kbytes) | Package     | Notes |  |  |  |  |  |  |

| SL5SU                                                                                       | FPD0                | 068Ah | 933/133                 | 128                            | Micro-FCPGA | 1     |  |  |  |  |  |  |

| SL5SR                                                                                       | FBD0                | 068Ah | 933/133                 | 128                            | Micro-FCBGA | 1     |  |  |  |  |  |  |

| SL5Q3                                                                                       | FPD0                | 068Ah | 866/133                 | 128                            | Micro-FCPGA | 1     |  |  |  |  |  |  |

| SL5Q2                                                                                       | FBD0                | 068Ah | 866/133                 | 128                            | Micro-FCBGA | 1     |  |  |  |  |  |  |

| SL5ST                                                                                       | FPD0                | 068Ah | 800A/133                | 128                            | Micro-FCPGA | 1     |  |  |  |  |  |  |

| SL5SQ                                                                                       | FBD0                | 068Ah | 800A/133                | 128                            | Micro-FCBGA | 1     |  |  |  |  |  |  |

| SL5SS                                                                                       | FPD0                | 068Ah | 733/133                 | 128                            | Micro-FCPGA | 1     |  |  |  |  |  |  |

| SL5SP                                                                                       | FBD0                | 068Ah | 733/133                 | 128                            | Micro-FCBGA | 1     |  |  |  |  |  |  |

#### NOTES:

1. VID[4:0] = 00001; VCC\_CORE = 1.70V

# MOBILE INTEL® CELERON® PROCESSOR (0.18 $\mu$ and 0.13 $\mu$ ) SPECIFICATION UPDATE

| Identification information for Mobile Celeron® (0.13μ) Micro-FCBGA and Micro-FCPGA Packages |                     |       |                         |                                |             |       |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|---------------------|-------|-------------------------|--------------------------------|-------------|-------|--|--|--|--|--|--|

| S-Spec                                                                                      | Product<br>Stepping | CPUID | Speed (MHz)<br>Core/Bus | Integrated L2<br>Size (Kbytes) | Package     | Notes |  |  |  |  |  |  |

| SL5YA                                                                                       | FBA1                | 06B1  | 650/100                 | 256                            | Micro-FCBGA | 1     |  |  |  |  |  |  |

#### NOTES:

1. VID[4:0] = 01100; VCC\_CORE = 1.15V

#### MOBILE INTEL® CELERON® PROCESSOR (0.18μ and 0.13μ) SPECIFICATION UPDATE

#### Intel® Celeron® Processor (0.18µ) Mobile Module Identification Information

| Product Tracking<br>Code (PTC) | Core Stepping | CPUID | Speed (MHz)<br>Core/Bus | Integrated L2 Size (Kbytes) | Package | Notes |

|--------------------------------|---------------|-------|-------------------------|-----------------------------|---------|-------|

| PMN45001001AA                  | MA2           | 0681h | 450/100                 | 128                         | MMC2    | 1     |

| PMN50001001AA                  | MA2           | 0681h | 500/100                 | 128                         | MMC2    | 1     |

| PMN45001101AB                  | MB0           | 0683  | 450/100                 | 128                         | MMC2    | 1     |

| PMN50001101AB                  | MB0           | 0683  | 500/100                 | 128                         | MMC2    | 1     |

| PMN55001101AA                  | MB0           | 0683h | 550/100                 | 128                         | MMC2    | 1     |

| PMN60001101AA                  | MB0           | 0683h | 600/100                 | 128                         | MMC2    | 1     |

| PMN65001101AA                  | MB0           | 0683h | 650/100                 | 128                         | MMC2    | 1     |

| PMN45001201AC                  | MC0           | 0686  | 450/100                 | 128                         | MMC-2   | 1     |

| PMN50001201AC                  | MC0           | 0686  | 500/100                 | 128                         | MMC-2   | 1     |

| PMN55001201AB                  | MC0           | 0686  | 550/100                 | 128                         | MMC-2   | 1     |

| PMN60001201AB                  | MC0           | 0686  | 600/100                 | 128                         | MMC-2   | 1     |

| PMN65001201AB                  | MC0           | 0686  | 650/100                 | 128                         | MMC-2   | 1     |

| PMN70001201AA                  | MC0           | 0686  | 700/100                 | 128                         | MMC-2   | 1     |

#### NOTES:

1.  $V_{CC\_CORE} = 1.60 \text{ V}$

#### **SUMMARY OF CHANGES**

The following table indicates the Errata, Documentation Changes, Specification Clarifications, or Specification Changes that that apply to Mobile Celeron processors Intel intends to fix some of the errata in a future stepping of he component, and to account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notation:

#### **CODES USED IN SUMMARY TABLE**

Specification Change, Erratum, Specification Clarification, or Documentation

X: Change applies to the given processor stepping.

(No mark) or (blank box): This item is fixed in or does not apply to the given stepping.

Doc: Intel intends to update the appropriate documentation in a future revision.

Fix: This erratum is intended to be fixed in a future stepping of the component.

Fixed: This erratum has been previously fixed.

NoFix: There are no plans to fix this erratum.

Doc: Intel intends to update the appropriate documentation in a future revision.

AP: APIC related erratum.

MO: Mobile processor related erratum

PKG: This column refers to errata on the mobile processor substrate.

Shaded: This item is either new or modified from the previous version of the document.

Each Specification Update item will be prefixed with a capital letter to distinguish the product. The key below details the letters that are used in Intel's microprocessor Specification Updates:

A = Intel® Pentium® II processor

B = Mobile Intel® Pentium® II processor

C = Intel® Celeron® processor

D = Intel® Pentium® II Xeon™ processor

E = Intel® Pentium® III processor

G = Intel® Pentium® III Xeon™ processor

H = Mobile Intel® Celeron® processor at 466 MHz, 433 MHz, 400 MHz, 366 MHz, 333 MHz, 300 MHz, and 266 MHz

K = Mobile Intel® Pentium® III processor

M = Mobile Intel® Celeron® processor

N = Intel® Pentium® 4 processor

P = Intel® Xeon™ processor

The Specification Updates for the Pentium® processor, Pentium® Pro processor, and other Intel products do not use this convention.

14

# MOBILE INTEL® CELERON® PROCESSOR (0.18 $\mu$ and 0.13 $\mu$ ) SPECIFICATION UPDATE

|     | Summary of Errata |     |     |     |     |     |     |     |     |     |     |      |      |      |      |        |                                                                                                                    |

|-----|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|--------|--------------------------------------------------------------------------------------------------------------------|

| Ö   | BA2               | PA2 | MA2 | BB0 | PB0 | MB0 | BC0 | PC0 | MC0 | BD0 | PD0 | FBDO | FPDO | FBA1 | FPA1 | Plans  | ERRATA                                                                                                             |

| M1  | х                 | Х   | Х   | x   | Х   | x   | Х   | Х   | Х   | Х   | Х   | Х    | x    | Х    | Х    | NoFix  | FP data operand pointer may be incorrectly calculated after FP access which wraps 64-Kbyte boundary in 16-bit code |

| M2  | Х                 | X   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | Differences exist in debug exception reporting                                                                     |

| М3  | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | Code fetch matching disabled debug register may cause debug exception                                              |

| M4  | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | Double ECC error on read may result in BINIT#                                                                      |

| M5  | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | FP inexact-result exception flag may not be set                                                                    |

| M6  | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | BTM for SMI will contain incorrect FROM EIP                                                                        |

| M7  | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | I/O restart in SMM may fail after simultaneous MCE                                                                 |

| M8  | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | Branch traps do not function if BTMs are also enabled                                                              |

| M9  | х                 | Х   | х   | х   | Х   | х   | Х   | Х   | Х   | Х   | Х   | Х    | х    | Х    | х    | NoFix  | Machine check exception handler may not always execute successfully                                                |

| M10 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | MCE due to L2 parity error gives L1 MCACOD.LL                                                                      |

| M11 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | LBER may be corrupted after some events                                                                            |

| M12 | х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | BTMs may be corrupted during simultaneous L1 cache line replacement                                                |

| M13 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix  | Near CALL to ESP creates unexpected EIP address                                                                    |

| M14 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | No Fix | Memory type undefined for non-<br>memory operations                                                                |

|     | Summary of Errata |     |     |     |     |     |     |     |     |              |     |      |      |      |      |       |                                                                                                           |

|-----|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|--------------|-----|------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------|

| Ö   | BA2               | PA2 | MA2 | 088 | PB0 | MB0 | BC0 | 0Od | 0ОМ | 0 <b>0</b> 8 | 0Qd | FBDO | FPDO | FBA1 | FPA1 | Plans | ERRATA                                                                                                    |

| M15 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | FP Data operand pointer may not be zero after power on or Reset                                           |

| M16 | х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | MOVD following zeroing instruction can cause incorrect result                                             |

| M17 | х                 | Х   | Х   | X   | Х   | Х   | Х   | X   | X   | X            | X   | X    | X    | Х    | X    | NoFix | Premature execution of a load operation prior to exception handler invocation                             |

| M18 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | Read portion of RMW instruction may execute twice                                                         |

| M19 | х                 | X   | X   | X   | X   | X   | X   | X   | X   | X            | X   | X    | Х    | X    | X    | NoFix | MC2_STATUS MSR has model-<br>specific error code and machine<br>check architecture error code<br>reversed |

| M20 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | MOV with debug register causes debug exception                                                            |

| M21 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | Upper four PAT entries not usable with Mode B or Mode C paging                                            |

| M22 | x                 | X   | X   | X   | Х   | Х   | Х   | X   | X   | X            | X   | X    | X    | Х    | X    | NoFix | Data breakpoint exception in a displacement relative near call may corrupt EIP                            |

| M23 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | RDMSR and WRMSR to invalid MSR may not cause GP fault                                                     |

| M24 | х                 | Х   | Х   | х   | х   | х   | х   | х   | х   | х            | х   | х    | Х    | х    | х    | NoFix | SYSENTER/SYSEXIT instructions can implicitly load null segment selector to SS and CS registers            |

| M25 | Х                 | X   | X   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | PRELOAD followed by EXTEST does not load boundary scan data                                               |

| M26 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | INT 1 instruction handler execution could generate a debug exception                                      |

| M27 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | Misaligned Locked access to APIC space results in a hang                                                  |

| M28 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | Processor may assert DRDY# on a write with no data.                                                       |

| M29 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х            | Х   | Х    | Х    | Х    | Х    | NoFix | GP# Fault on WRMSR to<br>ROB_CR_BKUPTMPDR6                                                                |

## MOBILE INTEL® CELERON® PROCESSOR (0.18μ and 0.13μ) SPECIFICATION UPDATE

|     | Summary of Errata |     |     |     |     |     |     |     |     |     |     |      |      |      |      |       |                                                                            |

|-----|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|-------|----------------------------------------------------------------------------|

| Ö   | BA2               | PA2 | MA2 | BB0 | PB0 | MB0 | BC0 | PC0 | MC0 | BD0 | PD0 | FBDO | FPDO | FBA1 | FPA1 | Plans | ERRATA                                                                     |

| M30 | х                 | Х   | Х   | х   | х   | х   |     |     |     |     |     |      |      |      |      | Fixed | Machine check exception may occur due to improper line eviction in the IFU |

| M31 | х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | Performance counters include<br>streaming SIMD extensions L1<br>prefetch   |

| M32 | Х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | Processor will erroneously report a BIST failure                           |

| M33 |                   |     |     |     |     |     |     |     |     |     |     |      |      |      |      | Fix   | Internal snooping mechanism causes livelock condition                      |

| M34 |                   |     |     |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | Cache coherency may be lost if snoop occurs during cache line invalidation |

| M35 |                   |     |     |     |     |     |     |     |     |     |     |      |      |      |      | Fix   | Extra DRDY# assertion when eviction back-to-back write combining lines     |

| M36 | Х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | ECC detection and correction issue                                         |

| M37 | x                 | X   | X   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | L2_LD and L2_M_LINES_OUTM performance-monitoring counters do not work      |

| M38 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |     |     |      |      |      |      | Fixed | Snoop request may cause DBSY# hang                                         |

| M39 | Х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | IFU/DCU deadlock may cause system hang                                     |

| M40 |                   |     |     |     |     |     |     |     |     |     |     |      |      |      |      | Fix   | WBINVD may lock write out buffer                                           |

| M41 | х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | L2_DBUS_BUSY performance<br>monitoring counter will not count<br>writes    |

| M42 | х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix | Lower bits of SMRAM SMBASE register cannot be written with an ITP          |

| M43 | Х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | Task switch may cause wrong PTE and PDE access bit to be set               |

|     | Summary of Errata |     |     |     |     |     |     |     |     |     |     |      |      |      |      |       |                                                                                                   |

|-----|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|-------|---------------------------------------------------------------------------------------------------|

| O   | BA2               | PA2 | MA2 | BB0 | PB0 | MB0 | BC0 | PC0 | MC0 | BD0 | PD0 | FBDO | FPDO | FBA1 | FPA1 | Plans | ERRATA                                                                                            |

| M44 | Х                 | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | X    | X    | X    | X    | NoFix | Unsynchronized cross-modifying code operations may cause unexpected instruction execution results |

| M45 | х                 | Х   | Х   | Х   | Х   | Х   |     |     |     |     |     |      |      |      |      | Fixed | Deadlock May Occur Due To<br>Illegal-Instruction/Page-Miss<br>Combination                         |

| M46 | X                 | Х   | X   | Х   | X   | X   |     |     |     |     |     |      |      |      |      | Fixed | MASKMOVQ Instruction Interaction with String Operation May Cause Deadlock                         |

| M47 | Х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | Noise Sensitivity Issue on Processor SMI# Pin                                                     |

| M48 | х                 | Х   | Х   | х   | Х   | Х   | х   | Х   | Х   | Х   | х   | х    | Х    | Х    | Х    | NoFix | MOVD or CVTSI2SS following zeroing instruction can cause incorrect result                         |

| M49 | X                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix | FLUSH# assertion following<br>STPCLK# may prevent CPU clocks<br>from stopping                     |

| M50 | Х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | Intermittent failure to assert ADS# during processor power-on                                     |

| M51 | Х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | Floating-point exception signal may be deferred                                                   |

| M52 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    |      |      | NoFix | Floating-point exception condition may be deferred                                                |

| M53 |                   |     | Х   |     |     | Х   |     |     | Х   |     |     |      |      |      |      | NoFix | Race conditions may exist on thermal sensor SMBus collision detection/arbitration circuitry       |

| M54 | Х                 | Х   | Х   | Х   | Х   | Х   |     |     |     |     |     |      |      |      |      | Fixed | Cache line reads may result in eviction of invalid data                                           |

| M55 | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix | Snoop probe during FLUSH# could cause L2 to be left in shared state                               |

| M56 | Х                 | Х   | Х   | Х   | Х   | Х   |     |     |     |     |     |      |      |      |      | Fixed | Livelock may occur due to IFU line eviction                                                       |

| M57 | х                 | Х   | Х   |     |     |     |     |     |     |     |     |      |      |      |      | Fixed | Intermittent power-on failure due to uninitialized processor internal nodes                       |

# MOBILE INTEL® CELERON® PROCESSOR (0.18 $\mu$ and 0.13 $\mu$ ) SPECIFICATION UPDATE

|      | Summary of Errata |     |     |     |     |     |     |     |     |     |     |      |      |      |      |       |                                                                                                                        |

|------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|-------|------------------------------------------------------------------------------------------------------------------------|

| Ö.   | BA2               | PA2 | MA2 | 088 | 08d | 08W | 028 | 0Od | ОЭМ | BD0 | 0Qd | FBDO | FPDO | FBA1 | FPA1 | Plans | ERRATA                                                                                                                 |

| M58  | Х                 | Х   | Х   | Х   | Х   | Х   |     |     |     |     |     |      |      |      |      | Fixed | Selector for the LTR/LLDT register may get corrupted                                                                   |

| M59  | Х                 | Х   | X   | X   | X   | X   | X   | Х   | X   | Х   | Х   | X    | X    | X    | X    | NoFix | INIT does not clear global entries in the TLB                                                                          |

| M60  | Х                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix | VM bit cleared on a double fault handler                                                                               |

| M61  | X                 | Х   | X   | X   | X   | X   | X   | X   | X   | Х   | X   | X    | X    | X    | X    | NoFix | Memory aliasing with inconsistent A and D bits may cause processor deadlock                                            |

| M62  | X                 | Х   | Х   | Х   | Х   | Х   | Х   | X   | Х   | Х   | X   | Х    | Х    | Х    | Х    | NoFix | Use of memory aliasing with inconsistent memory type may cause system hang                                             |

| M63  | X                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix | Processor may report invalid TSS fault instead of Double fault during mode C paging                                    |

| M64  | X                 | X   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | X   | Х   | Х    | Х    | Х    | Х    | NoFix | Machine check exception may occur when interleaving code between different memory types                                |

| M2AP | X                 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | NoFix | Write to mask LVT (programmed as EXTINT) will not deassert outstanding interrupt                                       |

| M65  | Х                 | X   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | X   | Х   | Х    | Х    | Х    | Х    | NoFix | Wrong ESP Register Values During a Fault in VM86 Mode                                                                  |

| M66  | X                 | Х   | X   | X   | X   | X   | X   | X   | X   | Х   | X   | X    | X    | X    | X    | NoFix | APIC ICR Write May Cause<br>Interrupt Not to be Sent When ICR<br>Delivery Bit Pending                                  |

| M67  | Х                 | Χ   | X   | X   | X   | Х   | Х   | X   | Х   | Χ   | X   | X    | X    | Х    | Х    | NoFix | Processor Incorrectly Samples<br>NMI Interrupt after RESET#<br>Deassertion When Processor<br>APIC is Hardware-Disabled |

| M68  | х                 | Х   | Х   | Х   | Х   | x   | x   | Х   | x   | Х   | Х   | Х    | Х    | x    | x    | NoFix | The Instruction Fetch Unit (IFU) May Fetch Instructions Based Upon Stale CR3 Data After a Write to CR3 Register        |

| M69  |                   |     |     |     |     |     |     |     |     | Х   | Х   | Х    | Х    |      |      | NoFix | Processor Might not Exit Sleep<br>State Properly Upon De-assertion<br>of CPUSLP# Signal                                |

Summary of Errata

| Ö   | BA2 | PA2 | MA2 | BB0 | PB0 | MB0 | BC0 | PC0 | MC0 | BD0 | PD0 | FBDO | FPDO | FBA1 | FPA1 | Plans | ERRATA                                                                        |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|-------|-------------------------------------------------------------------------------|

| M70 |     |     |     |     |     |     |     |     |     |     |     |      |      | X    | X    | NoFix | During Boundary Scan, BCLK Not<br>Sampled High When DPSLP# is<br>Asserted Low |

**Summary of Documentation Changes**

|     | Summary of bounnersation changes |     |     |     |     |     |     |     |     |     |     |      |      |      |      |       |                                                                                                                                                                                   |

|-----|----------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | BA2                              | PA2 | MA2 | BB0 | PB0 | MB0 | BC0 | PC0 | MC0 | BD0 | PD0 | FBDO | FPDO | FBA1 | FPA1 | Plans | Documentation Changes                                                                                                                                                             |

| M1  | Х                                | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | Doc   | Machine Check Exception detected when BINIT# drive enabled                                                                                                                        |

| M2  | Х                                | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | Doc   | Encoding of "Immediate to register" of "AND" instruction                                                                                                                          |

| МЗ  | Х                                | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х    | Х    | Х    | Х    | Doc   | The 'reg' field of CMPXCHG8B instruction encoding must be 001                                                                                                                     |

| M4  | X                                | X   | X   | X   | X   | Х   | Х   | X   | X   | X   | Х   | Х    | Х    | X    | Х    | Doc   | SCAS/SCASB/SCASW/SCASD encoding operand is incorrect                                                                                                                              |

| M5  | x                                | х   | x   | x   | x   | х   | X   | x   | x   | x   | х   | х    | х    | x    | х    | Doc   | XCHG encoding operand information<br>(1-byte form) does not have a w-bit,<br>hence the reg size is implied. The AL<br>register is not a valid option for this 1-<br>byte encoding |

**Summary of Specification Clarifications**

| NO. | BA2 | PA2 | MA2 | 088 | 08d | MB0 | 028 | 0O4 | MC0 | одв | PDO | FBDO | FPDO | FBA1 | FPA1 | Plans | Specification Clarifications                                    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|-------|-----------------------------------------------------------------|

| M1  |     |     |     |     |     |     |     |     |     | Х   | Х   |      |      |      |      | Doc   | Temperature Specification Clarification for Measuring Currents. |

## MOBILE INTEL® CELERON® PROCESSOR (0.18 $\mu$ and 0.13 $\mu$ ) SPECIFICATION UPDATE

**Summary of Specification Changes**

| NO. | BA2 | PA2 | MA2 | 088 | 084 | MB0 | 028 | PC0 | WC0 | ООЯ | PDO | FBDO | FPDO | FBA1 | FPA1 | Plans | Specification Changes              |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|-------|------------------------------------|

|     |     |     |     |     |     |     |     |     |     |     |     |      |      |      |      | Doc   | There are no Specification Changes |

#### **ERRATA**

## M1. WBINVD May Lock Write Out Buffer

**Problem:** The FP Data Operand Pointer is the effective address of the operand associated with the last noncontrol floating-point instruction executed by the machine. If an 80-bit floating-point access (load or store) occurs in a 16-bit mode other than protected mode (in which case the access will produce a segment limit violation), the memory access wraps a 64-Kbyte boundary, and the floating-point environment is subsequently saved, the value contained in the FP Data Operand Pointer may be incorrect.

**Implication:** A 32-bit operating system running 16-bit floating-point code may encounter this erratum, under the following conditions:

- The operating system is using a segment greater than 64 Kbytes in size.

- An application is running in a 16-bit mode other than protected mode.

- An 80-bit floating-point load or store which wraps the 64-Kbyte boundary is executed.

- The operating system performs a floating-point environment store (FSAVE/FNSAVE/FSTENV/FNSTENV) after the above memory access.

- The operating system uses the value contained in the FP Data Operand Pointer.

Wrapping an 80-bit floating-point load around a segment boundary in this way is not a normal programming practice. Intel has not currently identified any software which exhibits this behavior.

**Workaround:** If the FP Data Operand Pointer is used in an OS which may run 16-bit floating-point code, care must be taken to ensure that no 80-bit floating-point accesses are wrapped around a 64-Kbyte boundary.

#### M2. Differences Exist in Debug Exception Reporting

**Problem:** There exist some differences in the reporting of code and data breakpoint matches between that specified by previous Intel processor specifications and the behavior of the Intel® Mobile Celeron® processor, as described below:

Case 1: The first case is for a breakpoint set on a MOVSS or POPSS instruction, when the instruction following it causes a debug register protection fault (DR7.gd is already set, enabling the fault). The processor reports delayed data breakpoint matches from the MOVSS or POPSS instructions by setting the matching DR6.bi bits, along with the debug register protection fault (DR6.bd). If additional breakpoint faults are matched during the call of the debug fault handler, the processor sets the breakpoint match bits (DR6.bi) to reflect the breakpoints matched by both the MOVSS or POPSS breakpoint and the debug fault handler call. The Intel® Mobile Celeron® processor only sets DR6.bd in either situation, and does not set any of the DR6.bi bits.

**Case 2:** In the second breakpoint reporting failure case, if a MOVSS or POPSS instruction with a data breakpoint is followed by a store to memory which:

a) crosses a 4-Kbyte page boundary,

OR

b) causes the page table Access or Dirty (A/D) bits to be modified,

the breakpoint information for the MOVSS or POPSS will be lost. Previous processors retain this information under these boundary conditions.

**Case 3:** If they occur after a MOVSS or POPSS instruction, the INT*n*, INTO, and INT3 instructions zero the DR6.bi bits (bits B0 through B3), clearing pending breakpoint information, unlike previous processors.

**Case 4:** If a data breakpoint and an SMI (System Management Interrupt) occur simultaneously, the SMI will be serviced via a call to the SMM handler, and the pending breakpoint will be lost.

**Case 5:** When an instruction that accesses a debug register is executed, and a breakpoint is encountered on the instruction, the breakpoint is reported twice.

Case 6: Unlike previous versions of Intel Architecture processors, Intel® Mobile Celeron® processors will not set the Bi bits for a matching disabled breakpoint unless at least one other breakpoint is

**Implication:** When debugging or when developing debuggers for a Intel® Mobile Celeron® processor-based system, this behavior should be noted. Normal usage of the MOVSS or POPSS instructions (i.e., following them with a MOV ESP) will not exhibit the behavior of cases 1-3. Debugging in conjunction with SMM will be limited by case 4.

**Workaround:** Following MOVSS and POPSS instructions with a MOV ESP instruction when using breakpoints will avoid the first three cases of this erratum. No workaround has been identified for cases 4, 5, or 6.

Status: For the steppings affected see the Summary of Changes at the beginning of this section.

# M3. Code Fetch Matching Disabled Debug Register May Cause Debug Exception

**Problem:** The bits L0-3 and G0-3 enable breakpoints local to a task and global to all tasks, respectively. If one of these bits is set, a breakpoint is enabled, corresponding to the addresses in the debug registers DR0-DR3. If at least one of these breakpoints is enabled, any of these registers are *disabled* (i.e., Ln and Gn are 0), and RWn for the disabled register is 00 (indicating a breakpoint on instruction execution), normally an instruction fetch will not cause an instruction-breakpoint fault based on a match with the address in the disabled register(s). However, if the address in a disabled register matches the address of a code fetch which also results in a page fault, an instruction-breakpoint fault will occur.

**Implication:** The bits L0-3 and G0-3 enable breakpoints local to a task and global to all tasks, respectively. If one of these bits is set, a breakpoint is enabled, corresponding to the addresses in the debug registers DR0-DR3. If at least one of these breakpoints is enabled, any of these registers are *disabled* (i.e., Ln and Gn are 0), and RWn for the disabled register is 00 (indicating a breakpoint on instruction execution), normally an instruction fetch will not cause an instruction-breakpoint fault based on a match with the address in the disabled register(s). However, if the address in a disabled register matches the address of a code fetch which also results in a page fault, an instruction-breakpoint fault will occur.

Workaround: The debug handler should clear breakpoint registers before they become disabled.

## M4. Double ECC Error on Read May Result in BINIT#

**Problem:** For this erratum to occur, the following conditions must be met:

- Machine Check Exceptions (MCEs) must be enabled.

- A dataless transaction (such as a write invalidate) must be occurring simultaneously with a transaction which returns data (a normal read).

- The read data must contain a double-bit uncorrectable ECC error.

If these conditions are met, the mobile processor will not be able to determine which transaction was erroneous, and instead of generating an MCE, it will generate a BINIT#.

**Implication:** The bus will be reinitialized in this case. However, since a double-bit uncorrectable ECC error occurred on the read, the MCE handler (which is normally reached on a double-bit uncorrectable ECC error for a read) would most likely cause the same BINIT# event.

**Workaround:** Though the ability to drive BINIT# can be disabled in the mobile processor, which would prevent the effects of this erratum, overall system behavior would not improve, since the error which would normally cause a BINIT# would instead cause the machine to shut down. No other workaround has been identified.

## M5. FP Inexact-Result Exception Flag May Not Be Set

**Problem:** When the result of a floating-point operation is not exactly representable in the destination format (1/3 in binary form, for example), an inexact-result (precision) exception occurs. When this occurs, the PE bit (bit 5 of the FPU status word) is normally set by the processor. Under certain rare conditions, this bit may not be set when this rounding occurs. However, other actions taken by the processor (invoking the software exception handler if the exception is unmasked) are not affected. This erratum can only occur if the floating-point operation which causes the precision exception is immediately followed by one of the following instructions:

- FST m32real

- FST m64real

- FSTP m32real

- FSTP m64real

- FSTP m80real

- FIST m16int

- FIST m32int

- FISTP m16int

- FISTP m32int

- FISTP m64int

Note that even if this combination of instructions is encountered, there is also a dependency on the internal pipelining and execution state of both instructions in the processor.

**Implication:** Inexact-result exceptions are commonly masked or ignored by applications, as it happens frequently, and produces a rounded result acceptable to most applications. The PE bit of the FPU status word may not always be set upon receiving an inexact-result exception. Thus, if these exceptions are unmasked, a floating-point error exception handler may not recognize that a precision exception occurred. Note that this is a "sticky" bit, i.e., once set by an inexact-result condition, it remains set until cleared by software.

**Workaround:** This condition can be avoided by inserting two NOP instructions between the two floating-point instructions.

#### M6. BTM for SMI Will Contain Incorrect FROM EIP

**Problem:** A system management interrupt (SMI) will produce a Branch Trace Message (BTM), if BTMs are enabled. However, the FROM EIP field of the BTM (used to determine the address of the instruction which was being executed when the SMI was serviced) will not have been updated for the SMI, so the field will report the same FROM EIP as the previous BTM.

**Implication:** A BTM which is issued for an SMI will not contain the correct FROM EIP, limiting the usefulness of BTMs for debugging software in conjunction with System Management Mode (SMM).

Workaround: None identified

Status: For the steppings affected see the Summary of Changes at the beginning of this section.

## M7. I/O Restart in SMM May Fail After Simultaneous MCE

**Problem:** If an I/O instruction (IN, INS, REP INS, OUT, OUTS, or REP OUTS) is being executed, and if the data for this instruction becomes corrupted, the mobile processor will signal a machine check exception (MCE). If the instruction is directed at a device which is powered down, the processor may also receive an assertion of SMI#. Since MCEs have higher priority, the processor will call the MCE handler, and the SMI# assertion will remain pending. However, upon attempting to execute the first instruction of the MCE handler, the SMI# will be recognized and the processor will attempt to execute the SMM handler. If the SMM handler is completed successfully, it will attempt to restart the I/O instruction, but will not have the correct machine state, due to the call to the MCE handler.

**Implication:** A simultaneous MCE and SMI# assertion may occur for one of the I/O instructions above. The SMM handler may attempt to restart such an I/O instruction, but will have corrupted state due to the MCE handler call, leading to failure of the restart and shutdown of the processor.

**Workaround:** If a system implementation must support both SMM and MCEs, the first thing the SMM handler code (when an I/O restart is to be performed) should do is check for a pending MCE. If there is an MCE pending, the SMM handler should immediately exit via an RSM instruction and allow the machine check exception handler to execute. If there is not, the SMM handler may proceed with its normal operation.

## M8. Branch Traps Do Not Function If BTMs Are Also Enabled

**Problem:** If branch traps or branch trace messages (BTMs) are enabled alone, both function as expected. However, if both are enabled, only the BTMs will function, and the branch traps will be ignored.

**Implication:** The branch traps and branch trace message debugging features cannot be used together.

Workaround: If branch trap functionality is desired, BTMs must be disabled.

Status: For the steppings affected see the Summary of Changes at the beginning of this section.

# M9. Machine Check Exception Handler May Not Always Execute Successfully

**Problem:** An MCE may not always result in the successful execution of the MCE handler. However, asynchronous MCEs usually occur upon detection of a catastrophic system condition that would also hang the processor. Leaving MCEs disabled will result in the condition which caused the asynchronous MCE instead causing the processor to enter shutdown. Therefore, leaving MCEs disabled may not improve overall system behavior.

**Implication:** No workaround which would guarantee successful MCE handler execution under this condition has been identified.

Workaround: If branch trap functionality is desired, BTMs must be disabled.

Status: For the steppings affected see the Summary of Changes at the beginning of this section.

#### M10. MCE Due to L2 Parity Error Gives L1 MCACOD.LL

**Problem:** If a Cache Reply Parity (CRP) error, Cache Address Parity (CAP) error, or Cache Synchronous Error (CSER) occurs on an access to the mobile processor's L2 cache, the resulting Machine Check Architectural Error Code (MCACOD) will be logged with '01' in the LL field. This value indicates an L1 cache error; the value should be '10', indicating an L2 cache error. Note that L2 ECC errors have the correct value of '10' logged.

**Implication:** An L2 cache access error, other than an ECC error, will be improperly logged as an L1 cache error in MCACOD.LL.

Workaround: None identified

### M11. LBER May Be Corrupted After Some Events

**Problem:** The last branch record (LBR) and the last branch before exception record (LBER) can be used to determine the source and destination information for previous branches or exceptions. The LBR contains the source and destination addresses for the last branch or exception, and the LBER contains similar information for the last branch taken before the last exception. This information is typically used to determine the location of a branch which leads to execution of code which causes an exception. However, after a catastrophic bus condition which results in an assertion of BINIT# and the re-initialization of the buses, the value in the LBER may be corrupted. Also, after either a CALL which results in a fault or a software interrupt, the LBER and LBR will be updated to the same value, when the LBER should not have been updated.

**Implication:** The LBER and LBR registers are used only for debugging purposes. When this erratum occurs, the LBER will not contain reliable address information. The value of LBER should be used with caution when debugging branching code; if the values in the LBR and LBER are the same, then the LBER value is incorrect. Also, the value in the LBER should not be relied upon after a BINIT# event.

Workaround: None identified

Status: For the steppings affected see the Summary of Changes at the beginning of this section.

# M12. BTMs May Be Corrupted During Simultaneous L1 Cache Line Replacement

**Problem:** When Branch Trace Messages (BTMs) are enabled and such a message is generated, the BTM may be corrupted when issued to the bus by the L1 cache if a new line of data is brought into the L1 data cache simultaneously. Though the new line being stored in the L1 cache is stored correctly, and no corruption occurs in the data, the information in the BTM may be incorrect due to the internal collision of the data line and the BTM.