# intel.

# Intel<sup>®</sup> Pentium<sup>®</sup> II Processor Specification Update

Release Date: August 2001

Order Number: 243337-043

The Pentium<sup>®</sup> II processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium<sup>®</sup> II processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

The Specification Update should be publicly available following the last shipment date for a period of time equal to the specific product's warranty period. Hardcopy Specification Updates will be available for one (1) year following End of Life (EOL). Web access will be available for three (3) years following EOL.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at <a href="http://www.intel.com">http://www.intel.com</a>

Copyright © Intel Corporation 1999, 2000, 2001.

Intel, Pentium, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and foreign countries.

\*Other names and brands may be claimed as the property of others.

### CONTENTS

| REVISION HISTORY                                                                              | ii |

|-----------------------------------------------------------------------------------------------|----|

| PREFACE                                                                                       | vi |

| Specification Update for the Pentium <sup>®</sup> II Processor                                |    |

| GENERAL INFORMATION                                                                           | 1  |

| Pentium <sup>®</sup> II Processor and Boxed Pentium <sup>®</sup> II Processor 3 Line Markings | 1  |

| Pentium <sup>®</sup> II Processor Markings                                                    | 2  |

| Boxed Pentium <sup>®</sup> II Processor Markings                                              | 3  |

| Pentium <sup>®</sup> II OverDrive <sup>®</sup> Processor Line Markings                        | 4  |

| IDENTIFICATION INFORMATION                                                                    | 5  |

| Mixed Steppings in DP Systems                                                                 | 6  |

| SUMMARY OF CHANGES                                                                            | 12 |

| Summary of Errata                                                                             | 13 |

| Summary of Documentation Changes                                                              | 20 |

| Summary of Specification Clarifications                                                       | 21 |

| Summary of Specification Changes                                                              | 22 |

| ERRATA                                                                                        | 23 |

| DOCUMENTATION CHANGES                                                                         | 75 |

| SPECIFICATION CLARIFICATIONS                                                                  |    |

| SPECIFICATION CHANGES                                                                         |    |

i

int<sub>el</sub>.

| Date of Revision                      | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|---------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| May 1997                              | -001    | This document is the first Specification Update for the Pentium <sup>®</sup> II processor.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| June 1997                             | -002    | Added Erratum 25. Update Erratum 13 status in the Summary Table<br>of Changes. Added Documentation Change Table and<br>Documentation Change 1. Added 300-MHz Pentium II processor<br>information.                                                                                                                                                                                                                                                         |  |  |  |  |  |

| July 1997                             | -003    | Added Erratum 26. Added Specification Change Table and Specification Changes 1 and 2.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| August 1997                           | -004    | Added Erratum 27. Added Document Change 2 and Spec Changes 3, 4, 5, 6, and 7.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| September 1997                        | -005    | Updated Erratum 27. Added Errata 28 and 29. Added Document<br>Change 3 and Spec Clarification 1. Added C1 stepping information.<br>Updated Spec Change 6.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| October 1997                          | -006    | Updated Errata 6 and 18, and S-spec table.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| November 1997                         | -007    | Updated Erratum 22. Added Specification Clarification 2, 3, and 4.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| December 1997                         | -008    | Updated and added notes to S-spec table. Updated package information table. Updated Errata 24. Added Errata 30, 31, and 32.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| January 1998                          | -009    | Added notes to Pentium II processor markings. Updated Erratum 28.<br>Added Erratum 33. Added Documentation Change 4 and 5. Added<br>Specification Change 5.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| January 26, 1998<br>(Special Edition) | -010    | Updated S-spec table. Added dA0 stepping information. Added Errata 34, 35, 36, 37, and 38.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| February 1998                         | -011    | Added new processor markings. Corrected Errata 13 and 34 for<br>steppings affected. Corrected typos in summary table for Errata 34,<br>35, and 36. Added Erratum 39. Added Documentation Change 6.                                                                                                                                                                                                                                                        |  |  |  |  |  |

| March 1998                            | -012    | Added new boxed processor markings. Updated Documentation<br>Changes section, Specification Clarifications section, and<br>Specification Changes section. Corrected Erratum 8. Added Errata<br>40, and 41. Added Documentation Changes 6 and 7. Added<br>Specification Clarification 6. Added Specification Changes 1 and 2.                                                                                                                              |  |  |  |  |  |

| April 1998                            | -013    | Added new Mobile Pentium <sup>®</sup> II processor markings and Pentium II<br>Mobile Modules markings. Updated Documentation Changes<br>section, Specification Clarifications section, and Specification<br>Changes section. Updated S-spec table. Added new steppings to<br>Summary Table of Changes. Corrected Erratum 1. Added Errata 42,<br>43 and 44. Added Documentation Change 8. Updated Specification<br>Change 1. Added Specification Change 3. |  |  |  |  |  |

| May 1998                              | -014    | Updated S-spec table. Updated Errata 2 and 42. Added Errata 45<br>through 51. Corrected Documentation Change 7. Updated<br>Specification Change 2.                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

# intel

| Date of Revision | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 1998        | -015    | Updated S-spec Table. Updated Summary Table of Changes.<br>Updated Erratum 47. Added Errata 52 and 53. Added<br>Documentation Changes 9 through 16. Added Specification<br>Clarifications 7 though 9. Updated Specification Change 1. Added<br>Specification Change 4 and 5.                                                                                                                                                     |

| July 1998        | -016    | Added Pentium II Processor and Boxed Pentium II Processor 3 Line<br>Markings. Updated Preface, Documentation Changes section,<br>Specification Clarifications section, and Specification Changes<br>section. Updated S-spec Table. Updated Summary Table of<br>Changes. Added Errata 54 and 55. Added Documentation Changes<br>17 through 21. Added Specification Clarifications 10 through 15.<br>Added Specification Change 6. |

| August 1998      | -017    | Moved all references to the Mobile Pentium II processor to the <i>Mobile Pentium</i> <sup>®</sup> <i>II Processor Specification Update.</i> Updated S-spec Table. Updated Summary Table of Changes. Updated Errata 6 and 38. Added Errata 56 through 59. Updated Specification Clarification 5.                                                                                                                                  |

| September 1998   | -018    | Added new Pentium II OverDrive <sup>®</sup> processor markings. Updated S-<br>spec table. Updated Errata 56 and 57. Added Errata 60 through 62.<br>Added Specification Changes 6 and 7.                                                                                                                                                                                                                                          |

| October 1998     | -019    | Implemented new numbering nomenclature. Updated S-spec table.<br>Updated Errata A1 and A48. Added Errata A62, A63 and A64.<br>Added Specification Change A8. Added Specification Clarifications<br>A16 and A17.                                                                                                                                                                                                                  |

| November 1998    | -020    | Updated Specification Change A1, Documentation Change A11,<br>Erratum A44, Specification Change A6 and the Pentium II Processor<br>Identification Information table. Added Erratum A65 and<br>Documentation Change A18.                                                                                                                                                                                                          |

| December 1998    | -021    | Updated Specification Change A1 and the Pentium II Processor<br>Identification Information table. Added Erratum A66. Updated status<br>for Errata A16 through A29, A31, A35 through A39, A42, A48, A54,<br>A57, and A60. Changed affected steppings for Erratum A32.                                                                                                                                                             |

| January 1999     | -022    | Updated Specification Change A1 and the Pentium II Processor<br>Identification Information table. Added Errata A67 through A69, and<br>Documentation Change A19 through A21.                                                                                                                                                                                                                                                     |

| February 1999    | -023    | Updated Processor Identification Information table. Added Erratum A70.                                                                                                                                                                                                                                                                                                                                                           |

| March 1999       | -024    | Added Specification Change A8 and updated the Pentium II<br>Processor Identification Information table. Added S-Spec definition.<br>Removed Specification Changes, Specification Clarifications, and<br>Document Changes that have been incorporated into the appropriate<br>documentation. Renumbered remaining items.                                                                                                          |

| April 1999       | -025    | Added Documentation Change A4 and updated the Pentium II<br>Processor Identification Information table. Moved revised Mixed<br>Steppings statement to the General Information section and                                                                                                                                                                                                                                        |

| Date of Revision | Version | Description                                                                                                                                                                                                                                                                                                                                                            |

|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |         | renumbered remaining items.                                                                                                                                                                                                                                                                                                                                            |

| May 1999         | -026    | Removed Specification and Documentation Changes that have been incorporated into the appropriate documentation and renumbered remaining items. Added Specification Change A3. Updated Erratum A57 Plans status to "Fix."                                                                                                                                               |

| June 1999        | -027    | Added Erratum A71. Added Documentation Change A2. Added<br>Specification Clarifications A2 and A3. Added Specification Change<br>A4. Corrected Pentium II Processor Identification Information table,<br>Note 10.                                                                                                                                                      |

| July 1999        | -028    | Added Erratum A72. Corrected Pentium II Processor Identification<br>Information table, Note 10 and table references to that note.<br>Corrections in the May 1999 version were incorrect.                                                                                                                                                                               |

| August 1999      | -029    | Added Documentation Change A3. Updated the Pentium II<br>Processor Identification Information table and added Note 22.<br>Moved Identification Information into the General Information<br>section. Updated Codes Used in Summary Table. Updated column<br>heading in Errata, Documentation Changes, Specification<br>Clarifications and Specification Changes tables. |

| October 1999     | -030    | Added Errata A73. Added 'Brand Id' to Identification Information table.                                                                                                                                                                                                                                                                                                |

| November 1999    | -031    | Updated references at the beginning of each section. Updated<br><i>Pentium<sup>®</sup> II Processor Identification Information</i> table. Added Errata<br>A74 and A75. Added Documentation Change A4.                                                                                                                                                                  |

| December 1999    | -032    | Added Errata A76. Added Documentation Change A5. Added Specification Clarification A4.                                                                                                                                                                                                                                                                                 |

| January 2000     | -033    | Added Errata A77-A78. Added Documentation Change A6.                                                                                                                                                                                                                                                                                                                   |

| February 2000    | -034    | Updated Erratum A75. Added Documentation Change A7. Updated<br>Summary of Changes product letter codes.                                                                                                                                                                                                                                                                |

| March 2000       | -035    | Updated Erratum A74.                                                                                                                                                                                                                                                                                                                                                   |

| May 2000         | -036    | Added Erratum A79 & A80.                                                                                                                                                                                                                                                                                                                                               |

| September 2000   | -037    | Added New Errata A81, A82, A83, A84, A85. Added Errata Re-<br>Writes A58, A69, A74, A78. Added Document Changes A8, A9.                                                                                                                                                                                                                                                |

| October 2000     | -038    | Added New Erratum A86Added Document Changes A10, A11.                                                                                                                                                                                                                                                                                                                  |

| November 2000    | -039    | Added New Erratum A87.                                                                                                                                                                                                                                                                                                                                                 |

| December 2000    | -040    | Updated Specification Update product key to include the Intel®<br>Pentium® 4 processor, Revised Erratum A2. Added Documentation<br>Changes A12 - A17.                                                                                                                                                                                                                  |

| January 2001     | -041    | Revised Erratum A2. Added Documentation Changes A18 and A19.                                                                                                                                                                                                                                                                                                           |

| February 2001    | -042    | Revised Document Change A18. Added Documentation Change A20.                                                                                                                                                                                                                                                                                                           |

v

| Date of Revision | Version | Description               |

|------------------|---------|---------------------------|

| March 2001       | -043    | Added Errata A88 and A89. |

| August 2001      | -044    | Added Erratum A90         |

#### PREFACE

This document is an update to the specifications contained in the following documents:

- P6 Family of Processors Hardware Developer's Manual (Order Number 244001)

- Pentium<sup>®</sup> II Processor Developer's Manual (Order Number 243341)

- Pentium<sup>®</sup> II Processor at 233 MHz, 266 MHz, 300 MHz, and 333 MHz datasheet (Order Number 243335)

- Pentium<sup>®</sup> II Processor at 350 MHz, 400 MHz, and 450 MHz datasheet (Order Number 243657)

- Intel Architecture Software Developer's Manual, Volumes 1, 2, and 3 (Order Numbers 243190, 243191, and 243192, respectively)

It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools. It contains S-Specs, Errata, Documentation Changes, Specification Clarifications and, Specification Changes.

#### Nomenclature

**S-Spec Number** is a five-digit code used to identify products. Products are differentiated by their unique characteristics, e.g., core speed, L2 cache size, package type, etc. as described in the processor identification information table. Care should be taken to read all notes associated with each S-Spec number.

**Errata** are design defects or errors. Errata may cause the Pentium II processor's behavior to deviate from published specifications. Hardware and software designed to be used with any given processor must assume that all errata documented for that processor are present on all devices unless otherwise noted.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the specifications.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the specifications.

**Specification Changes** are modifications to the current published specifications for the Mobile Pentium<sup>®</sup> II processor or the Intel<sup>®</sup> Pentium<sup>®</sup> II Processor Mobile Module. These changes will be incorporated in the next release of the specifications.

Specification Update for the Pentium<sup>®</sup> II Processor

1

# intel

### **GENERAL INFORMATION**

# Pentium<sup>®</sup> II Processor and Boxed Pentium<sup>®</sup> II Processor 3 Line Markings

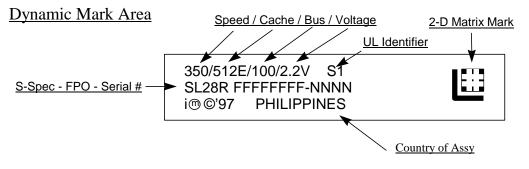

### Pentium<sup>®</sup> II Processor Markings

### Dynamic Mark Area

#### NOTES:

- ZZZ = Speed (MHz).

- SYYYY = S-spec Number.

- LLL = Level 2 Cache Size (in Kilobytes).

- FFFFFFF = FPO # (Test Lot Traceability #).

- XXXX = Serialization Code.

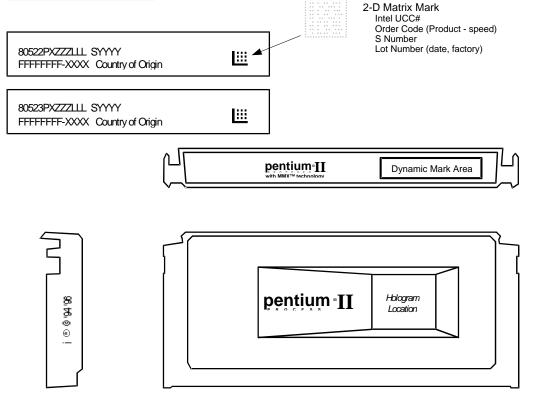

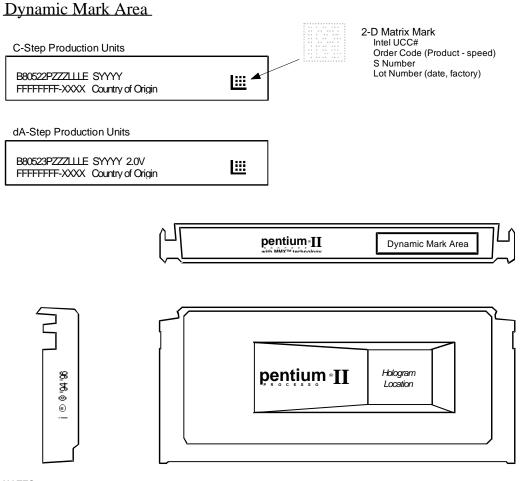

### Boxed Pentium® II Processor Markings

NOTES:

- ZZZ = Speed (MHz).

- LLL = Level 2 Cache Size (in Kilobytes).

- E = ECC Support in Level 2 Cache

- SYYYY = S-spec Number.

- FFFFFFF = FPO # (Test Lot Traceability #).

- XXXX = Serialization Code.

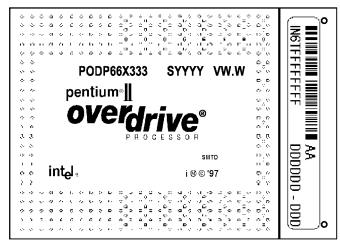

## Pentium<sup>®</sup> II OverDrive<sup>®</sup> Processor Line Markings

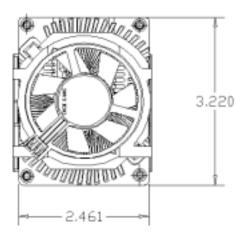

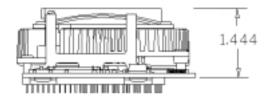

Bottom View of Pentium® II OverDrive® Processor

#### NOTES:

4

#### Label Markings

- FFFFFF = FPO # (Test Lot Traceability #).

- DDDDDD DDD = Altered Assembly Number.

#### **Bottom Cover Markings**

- PODP66X333 = Product Code.

- SYYYY = S-spec Number.

- VW.W = Version Number.

#### NOTES:

1. Attached fan heat sink is not end user removable.

2. Fan power is provided through external fan power connector, not through the processor socket.

#### **IDENTIFICATION INFORMATION**

The Pentium II processor can be identified by the following values:

| Fam   | ilv/l            | 233-, 266-, 300-, 333 <sup>3</sup> -                                                 | 266-, 300-, 333-, 350-, 400-, and 450-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Brand ID <sup>4</sup>           |

|-------|------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Fam   | iiy <sup>.</sup> | MHz Model 3 <sup>2</sup>                                                             | MHz Model 5 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Brand ID.                       |

| 011   | 0                | 0011                                                                                 | 0101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00h = Not Supported             |

| NOTES | S:               |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |

| 1.    | instru           |                                                                                      | B) of the EDX register after RESET, bits [11:8] of the EAX register, and the generation field of the Development of the Development (1) and the generation field of the Development (1) and the generation (1) an |                                 |

| 2.    | instru           |                                                                                      | of the EDX register after RESET, bits [7:4] of the e EAX register, and the model field of the Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

| 3.    |                  | s a Pentium <sup>®</sup> II OverDrive <sup>®</sup> pr<br>um II processor CPUID 065xh | ocessor. Please note that although this processor<br>processor core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | has a CPUID of 163xh, it uses a |

| 4.    | The E<br>regist  |                                                                                      | :0] of the EBX register after the CPUID instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | is executed with a 1 in the EAX |

The Pentium II processor's second level (L2) cache size can be determined by the following register contents:

| 512-Kbyte Unified L2 Cache <sup>1</sup> | 43h |

|-----------------------------------------|-----|

| NOTES                                   |     |

NOTES:

1

For the Pentium<sup>®</sup> II processor, the unified L2 cache size corresponds to the value in bits [3:0] of the EDX register after the CPUID instruction is executed with a 2 in the EAX register. Other Intel microprocessor models or families may move this information to other bit positions or otherwise reformat the result returned by this instruction; generic code should parse the resulting token stream according to the definition of the CPUID instruction.

#### Mixed Steppings in DP Systems

Intel Corporation fully supports mixed steppings of Pentium II processors. The following list and processor matrix describes the requirements to support mixed steppings:

- While Intel has done nothing to specifically prevent processors operating at differing frequencies from functioning within a dual processor system, there may be uncharacterized errata that exist in such configurations. Intel does not support such configurations. In mixed stepping systems, all processors must operate at identical frequencies (i.e., the highest frequency rating commonly supported by all processors).

- While there are no known issues associated with the mixing of processors with differing cache sizes in a dual processor system, and Intel has done nothing to specifically prevent such system configurations from operating, Intel does not support such configurations since there may be uncharacterized errata that exist. In mixed stepping systems, all processors must be of the same cache size.

- While Intel believes that certain customers may wish to perform validation of system configurations with

mixed frequency or cache sizes, and that those efforts are an acceptable option to our customers,

customers would be fully responsible for the validation of such configurations.

- The workarounds identified in this and following specification updates must be properly applied to each processor in the system. Certain errata are specific to the multiprocessor environment and are identified in the *Mixed Stepping Processor Matrix* found at the end of this section. Errata for all processor steppings will affect system performance if not properly worked around. Also see the "Pentium<sup>®</sup> II Processor Identification and Package Information" table for additional details on which processors are affected by specific errata.

- In mixed stepping systems, the processor with the lowest feature-set, as determined by the CPUID Feature Bytes, must be the Bootstrap Processor (BSP). In the event of a tie in feature-set, the tie should be resolved by selecting the BSP as the processor with the lowest stepping as determined by the CPUID instruction.

In the following processor matrix, "NI" indicates that there are currently no known issues associated with mixing these steppings. A number indicates that a known issue has been identified as listed in the table following the matrix. A dual processor system using mixed processor steppings must assure that errata are addressed appropriately for each processor.

| Pentium <sup>®</sup> II<br>Processor<br>Stepping | 266<br>MHz<br>C0 | 300<br>MHz<br>C0 | 233<br>MHz<br>C1 | 266<br>MHz<br>C1 | 300<br>MHz<br>C1 | 266<br>MHz<br>dA0 | 333<br>MHz<br>dA0 | 300<br>MHz<br>dA1 | 333<br>MHz<br>dA1 | 266<br>MHz<br>dB0 | 300<br>MHz<br>dB0 | 333<br>MHz<br>dB0 |

|--------------------------------------------------|------------------|------------------|------------------|------------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| 266-MHz C0                                       | 1                | Х                | Х                | 1                | Х                | 1                 | Х                 | Х                 | Х                 | 1                 | Х                 | Х                 |

| 300-MHz C0                                       | Х                | 1                | Х                | Х                | 1                | Х                 | Х                 | 1                 | Х                 | Х                 | 1                 | Х                 |

| 233-MHz C1                                       | Х                | Х                | NI               | Х                | Х                | Х                 | Х                 | Х                 | Х                 | Х                 | Х                 | Х                 |

| 266-MHz C1                                       | 1                | Х                | Х                | NI               | Х                | NI                | Х                 | Х                 | Х                 | NI                | Х                 | Х                 |

| 300-MHz C1                                       | Х                | 1                | Х                | Х                | NI               | Х                 | Х                 | NI                | Х                 | Х                 | NI                | Х                 |

| 266-MHz dA0                                      | 1                | Х                | Х                | NI               | Х                | NI                | Х                 | Х                 | Х                 | NI                | Х                 | Х                 |

| 333-MHz dA0                                      | Х                | Х                | Х                | Х                | Х                | Х                 | NI                | Х                 | NI                | Х                 | Х                 | NI                |

| 300-MHz dA1                                      | Х                | 1                | Х                | Х                | NI               | Х                 | Х                 | NI                | Х                 | Х                 | NI                | Х                 |

| 333-MHz dA1                                      | Х                | Х                | Х                | Х                | Х                | Х                 | NI                | Х                 | NI                | Х                 | Х                 | NI                |

| 266-MHz dB0                                      | 1                | Х                | Х                | NI               | Х                | NI                | Х                 | Х                 | Х                 | NI                | Х                 | Х                 |

#### DP Platform Population Matrix for the Pentium® II Processor with 66 MHz System Bus

# intel

#### PENTIUM® II PROCESSOR SPECIFICATION UPDATE

| Pentium <sup>®</sup> II<br>Processor<br>Stepping | 266<br>MHz<br>C0 | 300<br>MHz<br>C0 | 233<br>MHz<br>C1 | 266<br>MHz<br>C1 | 300<br>MHz<br>C1 | 266<br>MHz<br>dA0 | 333<br>MHz<br>dA0 | 300<br>MHz<br>dA1 | 333<br>MHz<br>dA1 | 266<br>MHz<br>dB0 | 300<br>MHz<br>dB0 | 333<br>MHz<br>dB0 |

|--------------------------------------------------|------------------|------------------|------------------|------------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| 300-MHz dB0                                      | Х                | 1                | Х                | Х                | NI               | Х                 | Х                 | NI                | Х                 | Х                 | NI                | Х                 |

| 333-MHz dB0                                      | Х                | Х                | Х                | Х                | Х                | Х                 | NI                | Х                 | NI                | Х                 | Х                 | NI                |

#### DP Platform Population Matrix for the Pentium® II Processor with 66 MHz System Bus

NOTES:

Errata A16 and A17, as listed in the Pentium<sup>®</sup> II Processor Specification Update, may be problematic for DP systems that use Pentium<sup>®</sup> II processor, model 3 C0 stepping. Please see the Pentium<sup>®</sup> II Processor Specification Update for further information.

X = Mixing processors at different frequencies is not supported.

NI = No known issues associated with mixing these steppings.

#### DP Platform Population Matrix for the Pentium® II Processor with 100 MHz System Bus

| Pentium <sup>®</sup> II Processor<br>Stepping | 350<br>MHz<br>dA0 | 350<br>MHz<br>dA1 | 400<br>MHz<br>dA1 | 350<br>MHz<br>dB0 | 400<br>MHz<br>dB0 | 450<br>MHz<br>dB0 | 350<br>MHz<br>dB1 | 400 MHz<br>dB1 |

|-----------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------|

| 350-MHz dA0                                   | NI                | NI                | Х                 | NI                | Х                 | Х                 | NI                | Х              |

| 350-MHz dA1                                   | NI                | NI                | Х                 | NI                | Х                 | Х                 | NI                | Х              |

| 400-MHz dA1                                   | Х                 | Х                 | NI                | Х                 | NI                | Х                 | Х                 | NI             |

| 350-MHz dB0                                   | NI                | NI                | Х                 | NI                | Х                 | Х                 | NI                | Х              |

| 400-MHz dB0                                   | Х                 | Х                 | NI                | Х                 | NI                | Х                 | Х                 | NI             |

| 450-MHz dB0                                   | Х                 | Х                 | Х                 | Х                 | Х                 | NI                | Х                 | Х              |

| 350-MHz dB1                                   | NI                | NI                | Х                 | NI                | Х                 | Х                 | NI                | Х              |

| 400-MHz dB1                                   | Х                 | Х                 | NI                | Х                 | NI                | Х                 | Х                 | NI             |

NOTE:

X = Mixing processors at different frequencies is not supported.

NI = No known issues associated with mixing these steppings.

#### PENTIUM® II PROCESSOR SPECIFICATION UPDATE

| Pentium® II Processor identification information |                   |       |                            |                     |                     |                 |                                    |                            |                                  |  |  |

|--------------------------------------------------|-------------------|-------|----------------------------|---------------------|---------------------|-----------------|------------------------------------|----------------------------|----------------------------------|--|--|

| S-Spec                                           | Core<br>Steppings | CPUID | Speed<br>(MHz)<br>Core/Bus | L2 Size<br>(Kbytes) | TagRAM/<br>Stepping | ECC/Non<br>-ECC | Processor<br>Substrate<br>Revision | Package<br>and<br>Revision | Notes                            |  |  |

| SL264                                            | C0                | 0633h | 233/66                     | 512                 | T6/B0               | non-ECC         | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL265                                            | C0                | 0633h | 266/66                     | 512                 | T6/B0               | non-ECC         | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL268                                            | C0                | 0633h | 233/66                     | 512                 | T6/B0               | ECC             | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL269                                            | C0                | 0633h | 266/66                     | 512                 | T6/B0               | ECC             | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL28K                                            | C0                | 0633h | 233/66                     | 512                 | T6/B0               | non-ECC         | D                                  | SECC 3.00                  | 1, 2, 3, 9,<br>13, 20, 21        |  |  |

| SL28L                                            | C0                | 0633h | 266/66                     | 512                 | T6/B0               | non-ECC         | D                                  | SECC 3.00                  | 1, 2, 3, 9,<br>13, 20, 21        |  |  |

| SL28R                                            | C0                | 0633h | 300/66                     | 512                 | T6/B0               | ECC             | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL2MZ                                            | C0                | 0633h | 300/66                     | 512                 | T6/B0               | ECC             | D                                  | SECC 3.00                  | 1, 2, 3, 13,<br>20, 21           |  |  |

| SL2HA                                            | C1                | 0634h | 300/66                     | 512                 | T6/B0               | ECC             | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL2HC                                            | C1                | 0634h | 266/66                     | 512                 | T6/B0               | non-ECC         | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL2HD                                            | C1                | 0634h | 233/66                     | 512                 | T6/B0               | non-ECC         | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL2HE                                            | C1                | 0634h | 266/66                     | 512                 | T6/B0               | ECC             | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL2HF                                            | C1                | 0634h | 233/66                     | 512                 | T6/B0               | ECC             | D                                  | SECC 3.00                  | 1, 2, 13, 20,<br>21              |  |  |

| SL2QA                                            | C1                | 0634h | 233/66                     | 512                 | T6/B0               | non-ECC         | D                                  | SECC 3.00                  | 1, 2, 3, 9,<br>13, 20, 21        |  |  |

| SL2QB                                            | C1                | 0634h | 266/66                     | 512                 | T6/B0               | non-ECC         | D                                  | SECC 3.00                  | 1, 2, 3, 9,<br>13, 20, 21        |  |  |

| SL2QC                                            | C1                | 0634h | 300/66                     | 512                 | T6/B0               | ECC             | D                                  | SECC 3.00                  | 1, 2, 3, 13,<br>20, 21           |  |  |

| SL2KA                                            | dA0               | 0650h | 333/66                     | 512                 | T6P/A3              | ECC             | B1                                 | SECC 3.00                  | 4, 5, 8, 14,<br>(20 or 21)       |  |  |

| SL2QF                                            | dA0               | 0650h | 333/66                     | 512                 | T6P/A3              | ECC             | B1                                 | SECC 3.00                  | 3, 4, 5, 8, 14                   |  |  |

| SL2K9                                            | dA0               | 0650h | 266/66                     | 512                 | T6P/A3              | ECC             | B1                                 | SECC 3.00                  | 4, 5, 8, 14,<br>21               |  |  |

| SL35V                                            | dA1               | 0651h | 300/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 5, 7, 8,<br>15             |  |  |

| SL2QH                                            | dA1               | 0651h | 333/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 5, 7, 8,<br>15             |  |  |

| SL2S5                                            | dA1               | 0651h | 333/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 5, 7, 8,<br>15, (20 or<br>21) |  |  |

#### Pentium<sup>®</sup> II Processor Identification Information

# intel®

#### PENTIUM® II PROCESSOR SPECIFICATION UPDATE

| Pentium <sup>®</sup> II Processor Identification Information |                   |       |                            |                     |                     |                 |                                    |                            |                                      |  |  |  |

|--------------------------------------------------------------|-------------------|-------|----------------------------|---------------------|---------------------|-----------------|------------------------------------|----------------------------|--------------------------------------|--|--|--|

| S-Spec                                                       | Core<br>Steppings | CPUID | Speed<br>(MHz)<br>Core/Bus | L2 Size<br>(Kbytes) | TagRAM/<br>Stepping | ECC/Non<br>-ECC | Processor<br>Substrate<br>Revision | Package<br>and<br>Revision | Notes                                |  |  |  |

| SL2ZP                                                        | dA1               | 0651h | 333/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 5, 7, 8,<br>15, 19, 20            |  |  |  |

| SL2ZQ                                                        | dA1               | 0651h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 5, 7, 8,<br>15, 19, 20            |  |  |  |

| SL2S6                                                        | dA1               | 0651h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 6, 7, 8,<br>15, (20 or<br>21), 22 |  |  |  |

| SL2S7                                                        | dA1               | 0651h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 6, 7, 8,<br>10, 15, (20<br>or 21) |  |  |  |

| SL2SF                                                        | dA1               | 0651h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 6, 7, 8,<br>15                 |  |  |  |

| SL2SH                                                        | dA1               | 0651h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 6, 7, 8,<br>10, 15             |  |  |  |

| SL2VY                                                        | dA1               | 0651h | 300/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 6, 7, 8,<br>15                 |  |  |  |

| SL33D                                                        | dB0               | 0652h | 266/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 5, 7, 8,<br>15, 20             |  |  |  |

| SL2YK                                                        | dB0               | 0652h | 300/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 5, 7, 8,<br>15, 20             |  |  |  |

| SL2WZ                                                        | dB0               | 0652h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 6, 7, 8,<br>15, 20             |  |  |  |

| SL2YM                                                        | dB0               | 0652h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 6, 7, 8,<br>10, 15, 20         |  |  |  |

| SL37G                                                        | dB0               | 0652h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC2<br>OLGA              | 3, 7, 10, 12,<br>15, 18              |  |  |  |

| SL2WB                                                        | dB0               | 0652h | 450/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 7, 8,<br>10, 11, 15,<br>20     |  |  |  |

| SL37H                                                        | dB0               | 0652h | 450/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC2<br>OLGA              | 3, 4, 7, 8,<br>10, 15, 18            |  |  |  |

| SL2KE                                                        | TdB0              | 1632h | 333/66                     | 512                 | C6C/A3              | ECC             | N/A                                | PGA                        | 4, 7, 8, 12                          |  |  |  |

| SL2W7                                                        | dB0               | 0652h | 266/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 2.00                  | 4, 5, 7, 8,<br>15, 20                |  |  |  |

| SL2W8                                                        | dB0               | 0652h | 300/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 5, 7, 8,<br>15, 20                |  |  |  |

| SL2TV                                                        | dB0               | 0652h | 333/66                     | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 5, 7, 8,<br>15, 20                |  |  |  |

| SL2U3                                                        | dB0               | 0652h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 6, 7, 8,<br>15, 20                |  |  |  |

| SL2U4                                                        | dB0               | 0652h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 6, 7, 8,<br>15, 20                |  |  |  |

#### Pentium<sup>®</sup> II Processor Identification Information

9

| S-Spec | Core<br>Steppings | CPUID | Speed<br>(MHz)<br>Core/Bus | L2 Size<br>(Kbytes) | TagRAM/<br>Stepping | ECC/Non<br>-ECC | Processor<br>Substrate<br>Revision | Package<br>and<br>Revision | Notes                             |

|--------|-------------------|-------|----------------------------|---------------------|---------------------|-----------------|------------------------------------|----------------------------|-----------------------------------|

| SL2U5  | dB0               | 0652h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 6, 7, 8,<br>10, 15, 20,<br>22  |

| SL2U6  | dB0               | 0652h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 6, 7, 8,<br>10, 15, 20         |

| SL2U7  | dB0               | 0652h | 450/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 7, 8, 10,<br>11, 15, 20        |

| SL356  | dB0               | 0652h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC2<br>PLGA              | 4, 7, 8, 10,<br>15, 16, 20,<br>22 |

| SL357  | dB0               | 0652h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC2<br>OLGA              | 4, 7, 8, 10,<br>15, 18, 20        |

| SL358  | dB0               | 0652h | 450/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC2<br>OLGA              | 4, 7, 8, 10,<br>15, 17, 18,<br>20 |

| SL37F  | dB0               | 0652h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC2<br>PLGA              | 3, 4, 7, 8,<br>10, 15, 16,<br>20  |

| SL3FN  | dB0               | 0652h | 350/100                    | 512                 | T6P-e/0             | ECC             | B1                                 | SECC2<br>OLGA              | 4, 7, 8, 10,<br>15, 18, 20        |

| SL3EE  | dB0               | 0652h | 400/100                    | 512                 | T6P-e/0             | ECC             | B1                                 | SECC2<br>PLGA              | 1, 7, 8, 15,<br>16, 20, 22        |

| SL3F9  | dB0               | 0652h | 400/100                    | 512                 | T6Pe/A0             | ECC             | B1                                 | SECC2<br>PLGA              | 3, 4, 7, 8,<br>10, 15, 16         |

| SL38M  | dB1               | 0653h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 6, 7, 8,<br>10, 15, 20      |

| SL38N  | dB1               | 0653h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 3, 4, 6, 7, 8,<br>10, 15, 20      |

| SL36U  | dB1               | 0653h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 6, 7, 8,<br>10, 15, 20         |

| SL38Z  | dB1               | 0653h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC 3.00                  | 4, 6, 7, 8,<br>10, 15, 20         |

| SL3D5  | dB1               | 0653h | 400/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC2<br>OLGA              | 3, 7, 8, 10,<br>15, 18            |

| SL3J2  | dB1               | 0653h | 350/100                    | 512                 | T6P-e/A0            | ECC             | B1                                 | SECC2<br>PLGA              | 4, 7, 8, 10,<br>15, 16, 22        |

#### Pentium<sup>®</sup> II Processor Identification Information

NOTES:

1.  $V_{CC\_CORE}$  is specified for 2.8 V +100/-70 mV for all Pentium<sup>®</sup> II processors.

TPLATE is specified for 5° C – 75° C for these Pentium II processors with S.E.C. cartridge packages except for s-specs SL28R , SL2HA, SL2MZ, and SL2QC which have a TPLATE specification for 5° C – 72° C.

3. This is a boxed Pentium II processor with an attached fan heatsink.

4. V<sub>CCCORE</sub> is specified for 2.0 V +100/-70 mV for these Pentium II processors.

5. TPLATE is specified for  $5^{\circ}$  C –  $65^{\circ}$  C for these Pentium II processors.

6. TPLATE is specified for 5° C – 75° C with ETP (extended thermal plate) for these Pentium II processors.

# intel®

#### PENTIUM® II PROCESSOR SPECIFICATION UPDATE

- 7. Cacheable address space supports up to 4 Gbytes for these Pentium II processors.

- 8. These processors will not shut down automatically on THERMTRIP#.

- 9. These boxed processors may have packaging which incorrectly indicates ECC support in the L2 cache.