## PENTIUM® PRO PROCESSOR WITH 1 MB L2 CACHE AT 200 MHZ

- Large integrated cache for multiprocessing systems

- Binary compatible with applications running on previous members of the Intel microprocessor family

- Optimized for 32-bit applications running on advanced 32-bit operating systems

- Dynamic Execution microarchitecture

- Single package includes Pentium<sup>®</sup> Pro processor CPU, cache and system bus interface

- Scaleable up to four processors and 4 GB memory

- Separate dedicated external system bus, and dedicated internal full-speed cache bus

- 8 KB/8 KB separate data and instruction, nonblocking, level one cache

- Data integrity and reliability features include ECC, Fault Analysis/Recovery, and Functional Redundancy Checking

- Fits Intel Pentium Pro processor 387-Pin Socket 8

- Meets All AC timings and levels of Pentium Pro processor

- 50% lighter package vs. ceramic

- Scratch resistant anodized aluminum heat spreader

- Designed for LIF and ZIF sockets

The Pentium® Pro processor with 1 MB L2 cache is designed for high-end 4 way multiprocessor capable server systems. The Pentium Pro processor with 1 MB L2 cache delivers more performance than previous generation processors through an innovation called Dynamic Execution. This is the next step beyond the superscalar architecture implemented in the Pentium processor. This makes possible the advanced 3D visualization and interactive capabilities required by today's high-end commercial and technical applications and tomorrow's emerging applications. The Pentium Pro processor with 1 MB L2 cache also includes advanced data integrity, reliability, and serviceability features for mission critical applications.

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Information contained herein supersedes previously published specifications on these devices from Intel.

© INTEL CORPORATION 1995

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium<sup>®</sup> Pro processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com

Copyright © Intel Corporation 1996, 1997.

\* Third-party brands and names are the property of their respective owners.

## PENTIUM® PRO PROCESSOR WITH 1 MB L2 CACHE AT 200 MHZ

## CONTENTS

## PAGE

| 1.0. INTRODUCTION                                           | 7 |

|-------------------------------------------------------------|---|

| 1.1. Terminology                                            | 7 |

| 1.2. References                                             | 7 |

| 2.0. ELECTRICAL SPECIFICATIONS                              | 8 |

| 2.1. The Pentium <sup>®</sup> Pro Processor Bus<br>and VREF | 8 |

| 2.2. Power Management: Stop Grant and Auto<br>HALT          | 9 |

| 2.3. Power and Ground Pins                                  | 9 |

| 2.4. Decoupling Recommendations                             | 9 |

| 2.4.1. GTL+ DECOUPLING                                      | 0 |

| 2.4.2. PHASE LOCK LOOP (PLL)<br>DECOUPLING11                | 0 |

| 2.5. BCLK Clock Input Guidelines1                           | 0 |

| 2.5.1. SETTING THE CORE CLOCK TO                            |   |

| BUS CLOCK RATIO1                                            |   |

| 2.6. Voltage Identification1                                |   |

| 2.7. JTAG Connection1                                       | 3 |

| 2.8. Signal Groups1                                         | 3 |

| 2.8.1. ASYNCHRONOUS VS.<br>SYNCHRONOUS1                     | 4 |

| 2.9. PWRGOOD1                                               | 4 |

| 2.10. THERMTRIP#1                                           | 6 |

| 2.11. Unused Pins1                                          | 6 |

| 2.12. Maximum Ratings1                                      | 6 |

| 2.13. DC Specifications1                                    | 7 |

| 2.14. GTL+ Bus Specifications2                              | 0 |

| 2.15. AC Specifications                                     |   |

| 3.0. GTL+ INTERFACE SPECIFICATION                           | 0 |

| 4.0. 3.3 V TOLERANT SIGNAL QUALITY<br>SPECIFICATIONS        | 0 |

| 4.1. Overshoot/Undershoot Guidelines                        | 0 |

| 4.2. Ringback Specification                                 | 1 |

| 4.3. Settling Limit Guideline                               |   |

| 5.0. THERMAL SPECIFICATIONS                                 | 2 |

| 5.1. Thermal Parameters                                     | 2 |

| 5.1.1. AMBIENT TEMPERATURE                                  |   |

|                                                             |   |

|                                                                          | PAGE  |

|--------------------------------------------------------------------------|-------|

| 5.1.2. MEASURING CASE                                                    |       |

| TEMPERATURE                                                              |       |

| 5.1.3. THERMAL RESISTANCE                                                |       |

| 5.2. Thermal Analysis                                                    | 34    |

| 5.2.1. TYPICAL PASSIVE HEAT SINK<br>DESIGNS                              | 34    |

| 5.2.2. TABLES AND CURVES FOR<br>PASSIVE HEAT SINKS VS. AIR<br>FLOW RATES | 36    |

| 5.2.3. FAN HEAT SINK DESIGNS                                             |       |

| 5.2.4. EFFECT OF THERMAL GREASE<br>PEDESTAL SIZE ON THERMAL              | E AND |

| PERFORMANCE                                                              |       |

| 6.0. MECHANICAL SPECIFICATIONS                                           | 20    |

| 6.1. Pinout                                                              |       |

| 6.2. Introduction of Flatness                                            |       |

| 6.3. Critical Zone and Pedestal Area                                     |       |

| 6.3.1. BACKPLATE PRESSURE                                                |       |

| SPECIFICATION                                                            | 57    |

| 6.4. Heat Sink Design Recommendations .                                  | 57    |

| 6.4.1. FAN HEAT SINK                                                     |       |

| 6.5. Lid Strength Specification                                          |       |

| 6.6. Coplanarity Specification                                           |       |

| 6.7. Predicted Storage Failure Rates                                     | 59    |

| A.0. ALPHABETICAL LISTING OF SIGNAL                                      | .S 60 |

| A.1. A[35:3]# (I/O)                                                      | 60    |

| A.2. A20M# (I)                                                           | 60    |

| A.3. ADS# (I/O)                                                          |       |

| A.4. AERR# (I/O)                                                         | 62    |

| A.5. AP[1:0]# (I/O)                                                      |       |

| A.6. ASZ[1:0]# (I/O)                                                     |       |

| A.7. ATTR[7:0]# (I/O)                                                    |       |

| A.8. BCLK (I)                                                            | 63    |

| A.9. BE[7:0]# (I/O)                                                      |       |

| A.10. BERR# (I/O)                                                        |       |

| A.11. BINIT# (I/O)                                                       |       |

| A.12. BNR# (I/O)                                                         |       |

| A.13. BP[3:2]# (I/O)                                                     |       |

| A.14. BPM[1:0]# (I/O)                                                    | 65    |

## PENTIUM® PRO PROCESSOR WITH 1 MB L2 CACHE AT 200 MHZ

| A.15. BPRI# (I)                 |

|---------------------------------|

| A.16. BR0#(I/O), BR[3:1]# (I)65 |

| A.17. BREQ[3:0]# (I/O)66        |

| A.18. D[63:0]# (I/O)66          |

| A.19. DBSY# (I/O)               |

| A.20. DEFER# (I)                |

| A.21. DEN# (I/0)                |

| A.22. DEP[7:0]# (I/O)67         |

| A.23. DID[7:0]# (I/O)           |

| A.24. DRDY# (I/O)               |

| A.25. DSZ[1:0]# (I/O)68         |

| A.26. EXF[4:0]# (I/O)68         |

| A.27. FERR# (O)                 |

| A.28. FLUSH# (I)                |

| A.29. FRCERR (I/O)              |

| A.30. HIT# (I/O), HITM# (I/O)69 |

| A.31. IERR# (O)70               |

| A.32. IGNNE# (I)70              |

| A.33. INIT# (I)                 |

| A.34. INTR (I)                  |

| A.35. LEN[1:0]# (I/O)71         |

| A.36. LINT[1:0] (I)71           |

| A.37. LOCK# (I/O)71             |

| A.38. NMI (I)                   |

| A.39. PICCLK (I)                |

| A.40. PICD[1:0] (I/O)72         |

| A.41. PWRGOOD (I)               |

| A.42. REQ[4:0]# (I/O)72         |

| A.43. RESET# (I)                |

| A.44. RP# (I/O)73               |

| A.45. RS[2:0]# (I)74            |

| A.46. RSP# (I)75                |

| A.47. SMI# (I)                  |

| A.48. SMMEM# (I/O)75            |

| A.49. SPLCK# (I/O)75            |

| A.50. STPCLK# (I)75             |

| A.51. TCK (I)                   |

| A.52. TDI(I)                    |

| A.53. TDO (O)76                 |

| A.54. TMS (I)                   |

| A.55. TRDY (I)                  |

| A.56. TRST (I)                  |

## FIGURES

| Figure 1. Pentium <sup>®</sup> Pro Processor with 1 MB<br>L2 Cache Block Diagram | 8    |

|----------------------------------------------------------------------------------|------|

| Figure 2. GTL+ Bus Topology                                                      | 8    |

| Figure 3. Transient Types                                                        | . 10 |

| Figure 4. Timing Diagram of Clock Ratio<br>Signals                               | . 12 |

| Figure 5. Example Schematic for Clock Ratio<br>Pin Sharing                       | . 12 |

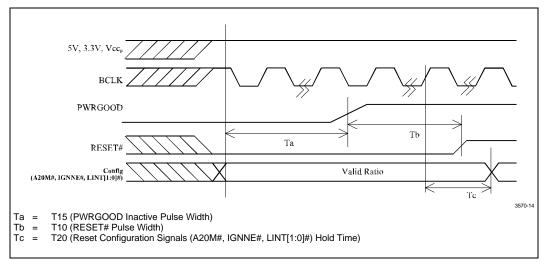

| Figure 6. PWRGOOD Relationship at<br>Power-On                                    | . 16 |

| Figure 7. 3.3 V Tolerant Group Derating Curve .                                  | . 23 |

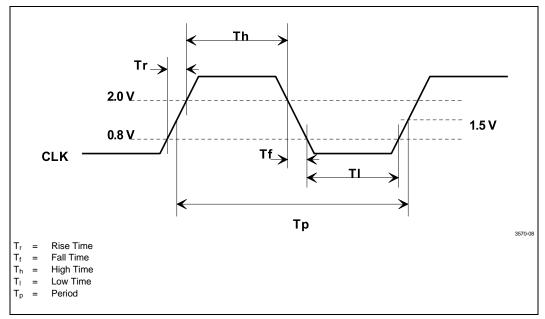

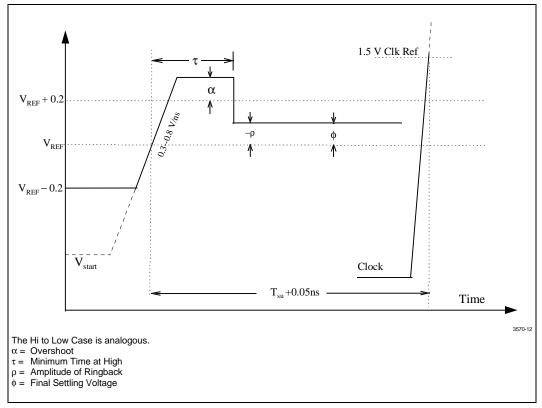

| Figure 8. Generic Waveform                                                       | .26  |

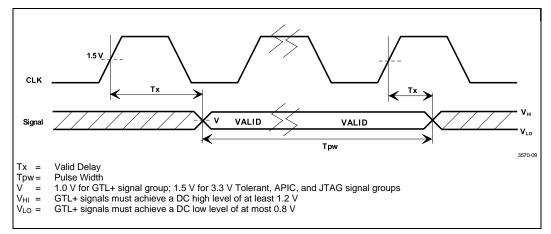

| Figure 9. Valid Delay Timings                                                    | . 26 |

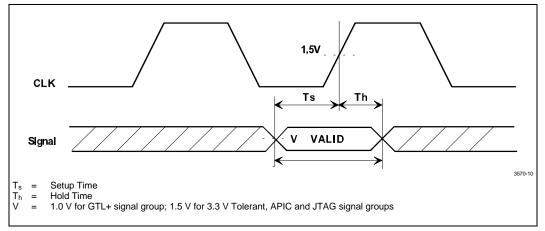

| Figure 10. Setup and Hold Timings                                                | . 27 |

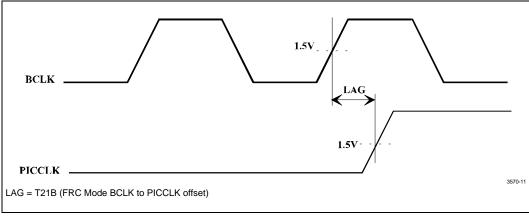

| Figure 11. FRC Mode BCLK to PICCLK<br>Timing                                     | .27  |

| Figure 12. Low to High GTL+ Receiver Ringbac<br>Tolerance                        |      |

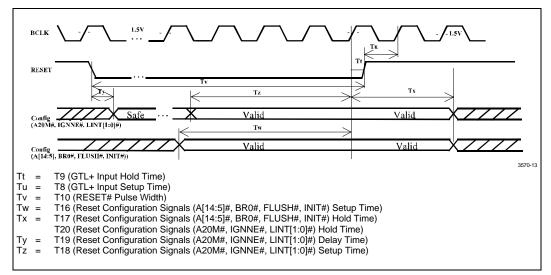

| Figure 13. Reset and Configuration Timings                                       | .29  |

| Figure 14. Power-On Reset and Configuration<br>Timings                           | .29  |

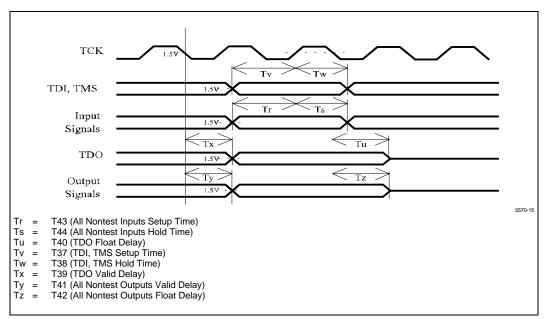

| Figure 15. Test Timings (Boundary Scan)                                          | . 30 |

| Figure 16. Test Reset Timings                                                    | . 30 |

| Figure 17. 3.3 V Tolerant Signal<br>Overshoot/Undershoot and<br>Ringback         | .31  |

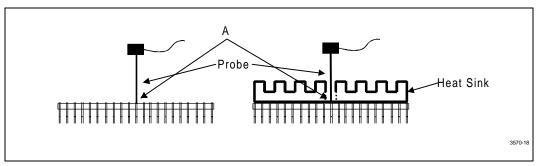

| Figure 18. Technique for Measuring T <sub>C</sub> on<br>Processor                |      |

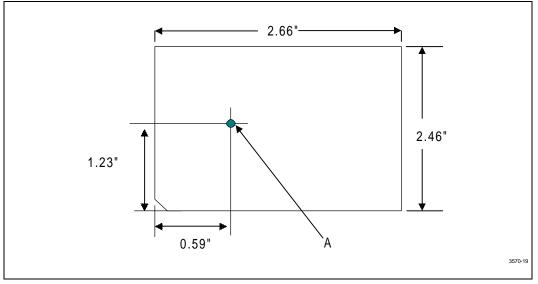

| Figure 19. Location for TC Measurement on<br>Back Plate (not to scale)           |      |

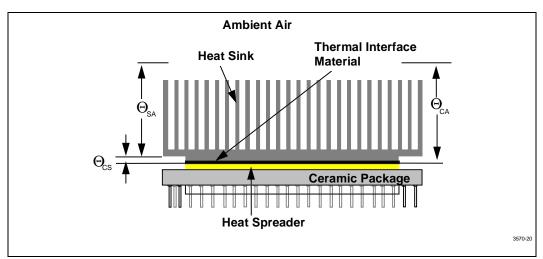

| Figure 20. Thermal Resistance Relationships                                      |      |

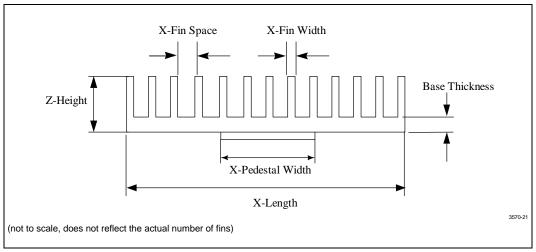

| Figure 21. Typical Heat Sink Dimensions<br>(View from Side-X)                    |      |

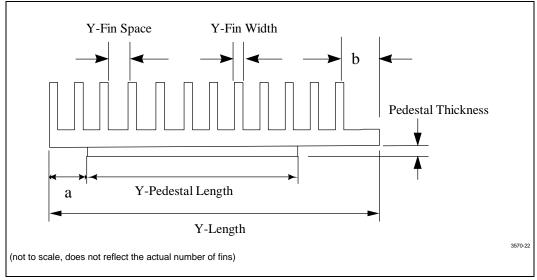

| Figure 22. Typical Heat Sink Dimensions<br>(View from Side-Y)                    |      |

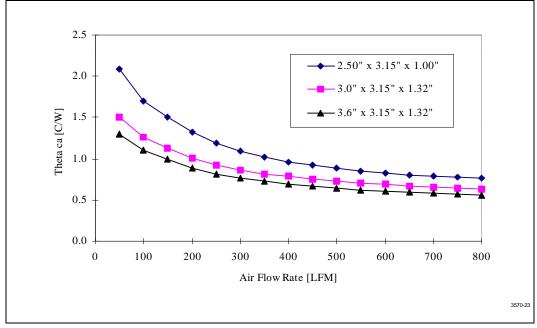

| Figure 23. OCA for Different Heat Sink Sizes<br>vs. Air Flow Rates               |      |

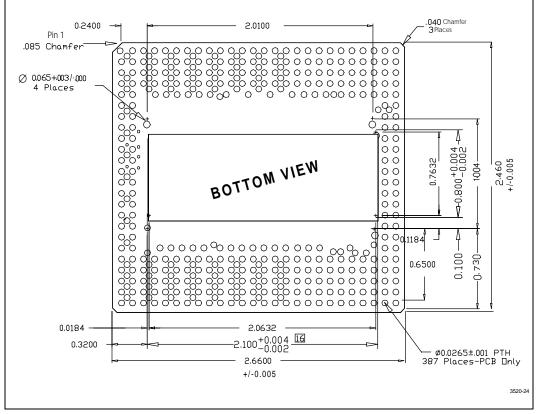

| Figure 24. Pentium <sup>®</sup> Pro Processor with 1 MB<br>L2 Cache Pin Side     |      |

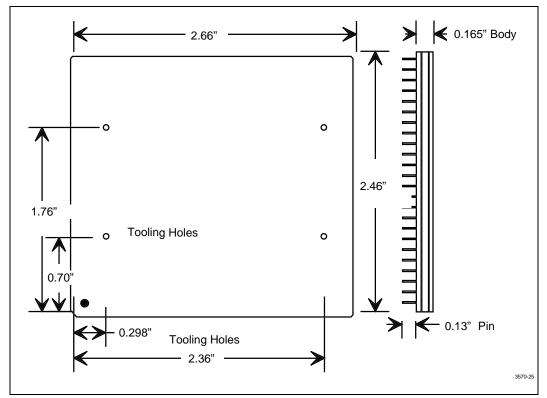

| Figure 25. Top View of Package                                                   | . 39 |

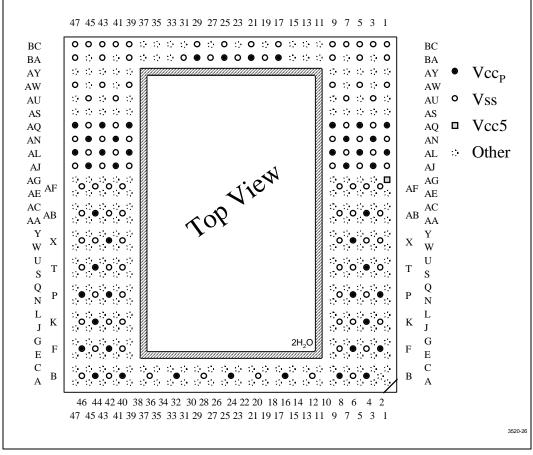

| Figure 26. Pentium <sup>®</sup> Pro Processor Top View with Power Pin Locations  | .41  |

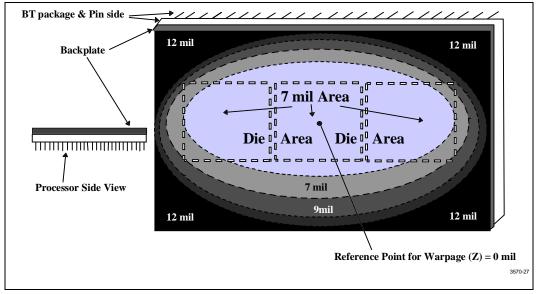

| Figure 27. Processor Top View with Back Plate<br>Warpage Mapping                 |      |

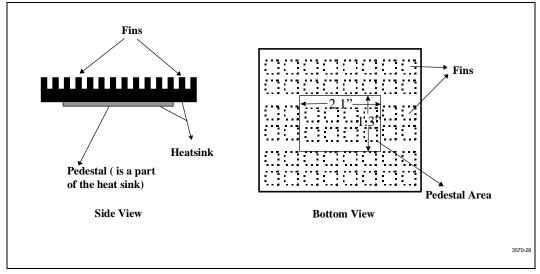

| Figure 28. Pedestal Shape Bottom and<br>Side View                                |      |

|                                                                                  |      |

## PENTIUM® PRO PROCESSOR WITH 1 MB L2 CACHE AT 200 MHZ

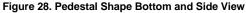

| Figure 29. Heat Sink with Pedestal Placement                                 |      |

|------------------------------------------------------------------------------|------|

| on Processor Side View                                                       | . 57 |

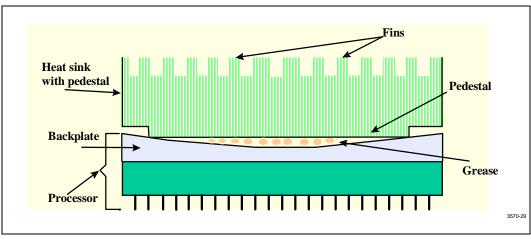

| Figure 30. Example Fan Heat Sink                                             | . 58 |

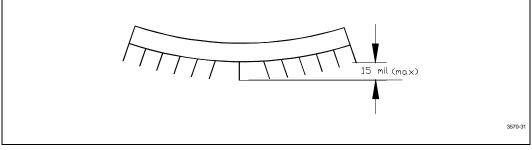

| Figure 31. Coplanarity Specification                                         | . 58 |

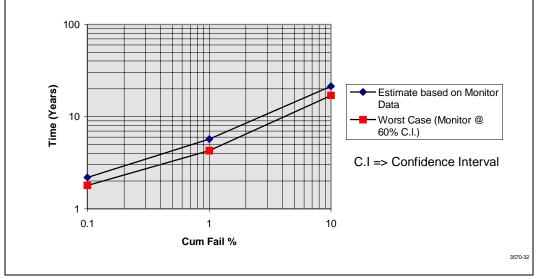

| Figure 32. Expected Storage Failure Rates in<br>Stringent Storage Conditions | . 59 |

## TABLES

| Table 1. Voltage Identification Definition                     |

|----------------------------------------------------------------|

| Table 2. Signal Groups15                                       |

| Table 3. Absolute Maximum Ratings 17                           |

| Table 4. Power and Voltage Specifications           (Option 1) |

| Table 5. Power and Voltage Specifications           (Option 2) |

| Table 6. GTL+ Signal Groups DC<br>Specifications               |

| Table 7. Non-GTL+ Signal Groups DC<br>Specifications19         |

| Table 8. GTL+ Bus Voltage Specifications 20                    |

| Table 9. Bus Clock AC Specifications20                         |

| Table 10. Supported Clock Ratios21                             |

| Table 11. GTL+ Signal Groups AC<br>Specifications21            |

| Table 12. GTL+ Signal Groups Ringback<br>Tolerance             |

| Table 13. 3.3 V Tolerant Signal Groups AC<br>Specifications    |

| Table 14. Reset Conditions AC Specifications 23                |

| Table 15. APIC Clock and APIC I/O AC<br>Specifications24       |

| Table 16. Boundary Scan Interface AC<br>Specifications25       |

| Table 17. Signal Ringback Specifications                       |

| Table 18. Typical Heat Sink Designs<br>(View from Side-X)      |

| Table 19. Typical Heat Sink Designs<br>(View from Side-Y)                                  | . 35 |

|--------------------------------------------------------------------------------------------|------|

| Table 20. OCA For Different Passive Heat Sink<br>Sizes and 50 - 300 LFM Air Flow<br>Rates  | .36  |

| Table 21. OCA For Different Passive Heat Sink<br>Sizes and 350 - 600 LFM Air Flow<br>Rates | .36  |

| Table 22. OCA For Different Passive Heat Sink<br>Sizes and 650 - 800 LFM Air Flow<br>Rates | .36  |

| Table 23. OCA for Different Fan Heat Sinks<br>and Air Flow Rates                           | .37  |

| Table 24. Pentium <sup>®</sup> Pro Processor with 1 MB           L2 Cache Package          | .40  |

| Table 25. Pin Listing in Pin # Order                                                       | .42  |

| Table 26. Pin Listing in Alphabetic Order                                                  | .48  |

| Table 27. Flatness Specification                                                           | 56   |

| Table 28. Pedestal Specification                                                           | .56  |

| Table 29. Dimensions for Figure 30                                                         | .57  |

| Table 30. Request Phase Decode                                                             | 60   |

| Table 31. Bus Clock Ratios Versus Pin Logic<br>Levels                                      | .61  |

| Table 32. ASZ[1:0]# Signal Decode                                                          |      |

| Table 33. ATTR[7:0]# Field Descriptions                                                    |      |

| Table 34. Special Transaction Encoding on BE[7:0]#                                         |      |

| Table 35. BR[3:0]# Signals Rotating<br>Interconnect                                        | .65  |

| Table 36. BR[3:0]# Signal Agent IDs                                                        | . 66 |

| Table 37. DID[7:0]# Encoding                                                               | . 68 |

| Table 38. EXF[4:0]# Signal Definitions                                                     | . 69 |

| Table 39. LEN[1:0]# Data Transfer Lengths                                                  | .71  |

| Table 40. Transaction Types Defined by<br>REQa#/REQb# Signals                              | .73  |

| Table 41. Transaction Response Encodings                                                   | .75  |

## 1.0. INTRODUCTION

The Pentium Pro processor with 1 MB L2 cache is a multichip module targeted for use in high-end 4-way multiprocessor capable server systems. The component package contains an Intel Pentium Pro processor core, and 1 MB of L2 cache. The 1 MB cache is built using two of the 512 KB SRAM die found in the 512 KB version of the Pentium Pro processor. While the 512 K version uses a conventional ceramic package, the Pentium Pro processor with 1 MB L2 cache integrates the three die in a plastic package with an aluminum heat spreader. This 387-pin package is compatible with the current Pentium Pro processor footprint. The Pentium Pro processor with 1 MB L2 cache routes all of the processor's high-speed cache interface bus through balanced nets on a thin film interconnect substrate to the two L2 SRAMs. This allows for internal component operation speeds of 200 MHz between the Pentium Pro processor and the I 2 cache die.

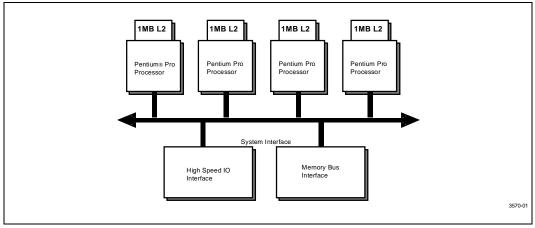

Figure 1 shows how a typical Pentium Pro processor system is implemented.

## 1.1. Terminology

A '#' symbol after a signal name refers to an active low signal. This means that a signal is in the active state (based on the name of the signal) when driven low. For example, when FLUSH# is low a flush has been requested. When Nonmaskable Interrupt (NMI) is high, a nonmaskable interrupt has occurred. In the case of lines where the name does not imply an active state but describes part of a binary sequence (such as address or data), the '#' symbol implies that the signal is inverted. For example, D[3:0] ='HLHL' refers to a hex 'A', and D#[3:0] ='LHLH' also refers to a hex 'A'. (H= High logic level, L= Low logic level)

The word **Preliminary** appears occasionally. Check with your local Field Applications Engineer for recent information.

## 1.2. References

The following are referenced within this specification:

- Pentium<sup>®</sup> Pro Processor I/O Buffer Models— IBIS Format (on World Wide Web page http://www.intel.com)

- AP-523, Pentium<sup>®</sup> Pro Processor Power Distribution Guidelines (Order Number 242764)

- AP-524, Pentium<sup>®</sup> Pro Processor GTL+ Layout Guidelines (Order Number 242765)

- AP-525, Pentium<sup>®</sup> Pro Processor Thermal Design Guidelines (Order Number 242766)

- Pentium<sup>®</sup> Pro Processor Family Developer's Manual, Volume 1: Specifications (Order Number 242690)

- Pentium<sup>®</sup> Pro Processor Family Developer's Manual, Volume 2: Programmer's Reference Manual (Order Number 242691)

- Pentium<sup>®</sup> Pro Processor Family Developer's Manual, Volume 3: Operating System Writer's Guide (Order Number 242692)

- Pentium<sup>®</sup> Pro Specification Update (Order Number 242689)

Figure 1. Pentium® Pro Processor with 1 MB L2 Cache Block Diagram

## 2.0. ELECTRICAL SPECIFICATIONS

#### 2.1. The Pentium<sup>®</sup> Pro Processor Bus and V<sub>REF</sub>

Most of the Pentium Pro processor signals use a **variation** of the low voltage Gunning Transceiver Logic (GTL) signaling technology.

The Pentium Pro processor bus specification is similar to the GTL specification but has been enhanced to provide larger noise margins and reduced ringing. This is accomplished by increasing the termination voltage level and controlling the edge rates. Because this specification is different from the standard GTL specification, it is referred to as **GTL+** in this document.

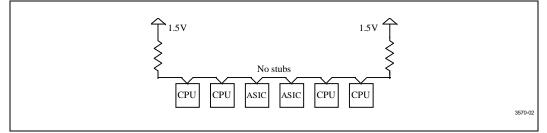

The GTL+ signals are open-drain and require external termination to a supply that provides the high signal level. The GTL+ inputs use differential receivers which require a reference signal ( $V_{REF}$ ). Termination (usually a resistor on each end of the signal trace) is used to pull the bus up to the high voltage level and to control reflections on the stub-free transmission line.  $V_{REF}$  is used by the receivers to determine if a signal is a logical 0 or a logical 1. See Table 8 for the bus termination voltage specifications for GTL+, and Section 4.0. for the GTL+ Interface Specification.

There are 8 V<sub>REF</sub> pins on the Pentium Pro processor to ensure that internal noise will not affect the performance of the I/O buffers. Pins A1, C7, S7 and Y7 (V<sub>REF</sub>[3:0]) must be tied together and pins A47, U41, AE47 and AG45 (V<sub>REF</sub>[7:4]) must be tied together. The two groups may also be tied to each other if desired.

Figure 2. GTL+ Bus Topology

The GTL+ bus depends on incident wave switching. Therefore timing calculations for GTL+ signals are based on **flight time** as opposed to capacitive deratings. Analog signal simulation of the Pentium Pro processor bus including trace lengths is highly recommended when designing a system with a heavily loaded GTL+ bus. See Intel's World Wide Web page (http://www.intel.com) to download the buffer models for the Pentium Pro processor in IBIS format.

## 2.2. Power Management: Stop Grant and Auto HALT

The Pentium Pro processor allows the use of Stop Grant and Auto HALT modes to immediately reduce the power consumed by the device. When enabled, these cause the clock to be stopped to most of the CPU's internal units and thus significantly reduces power consumption by the CPU as a whole.

Stop Grant is entered by asserting the STPCLK# pin of the Pentium Pro processor. When STPCLK# is recognized by the Pentium Pro processor, it will stop execution and will not service interrupts. It will continue snooping the bus. Stop Grant power is specified assuming no snoop hits occur.

Auto HALT is a low-power state entered when the Pentium Pro processor executes a halt (HLT) instruction. In this state, the Pentium Pro processor behaves as if it executed a halt instruction, and it additionally powers-down most internal units. In Auto HALT, the Pentium Pro processor will recognize all interrupts and snoops. Auto HALT power is specified assuming no snoop hits or interrupts occur.

The low-power stand-by mode of Stop Grant or Auto HALT can be defined by a **Low-Power Enable** configuration bit to be either the lowest power achievable by the Pentium Pro processor (Stop Grant power), or a power state in which the clock distribution is left running (Idle power). "Low-power stand-by" **disabled** leaves the core logic running, while "Low-power stand-by" **enabled** allows the Pentium Pro processor to enter its lowest power mode.

## 2.3. Power and Ground Pins

There are 4 pins defined on the package for voltage identification (VID). These pins specify the voltage

required by the CPU die. These have been added to cleanly support voltage specification variations on the Pentium Pro processor and future processors. See Section 2.6. for an explanation of the voltage identification pins.

For clean on-chip power distribution, the Pentium Pro processor has 47 V<sub>CC</sub> (power) and 101 V<sub>SS</sub> (ground) inputs. On the circuit board, **all** V<sub>CC</sub>P pins must be connected to a voltage island. Similarly, **all** V<sub>SS</sub> pins must be connected to a system ground plane. See Figure 26 for the locations of power and ground pins.

## 2.4. Decoupling Recommendations

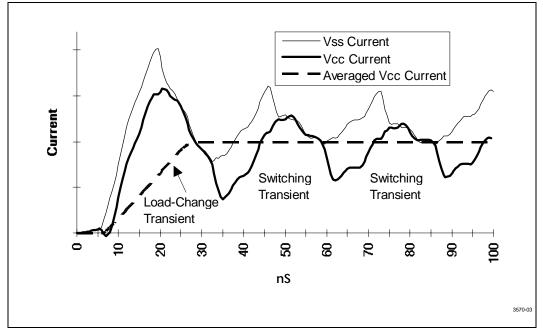

Due to the large number of transistors and high internal clock speeds, the Pentium Pro processor can create large, short duration transient (switching) current surges that occur on internal clock edges which can cause power planes to spike above and below their nominal value if not properly controlled. The Pentium Pro processor is also capable of generating large average current swings between low and full power states, called Load-Change Transients, which can cause power planes to sag below their nominal value if bulk decoupling is not adequate. See Figure 3 for an example of these current fluctuations. Care must be taken in the board design to guarantee that the voltage provided to the Pentium Pro processor remains within the specifications listed in this volume. Failure to do so may result in timing violations and/or a reduced lifetime of the component.

Adequate decoupling capacitance should be placed near the power pins of the Pentium Pro processor. Low inductance capacitors such as the 1206 package surface mount capacitors are recommended for the best high frequency electrical performance. Forty (40) 1 µF 1206-style capacitors with a ±22% tolerance make a good starting point for simulations as this is our recommended decoupling when using a Pentium Pro Processor Voltage Regulator Module. Inductance should be reduced by connecting capacitors directly to the V<sub>CC</sub>P and V<sub>SS</sub> planes with minimal trace length between the component pads and vias to the plane. Be sure to include the effects of board inductance within the simulation. Also, when choosing the capacitors to use, bear in mind the operating temperatures they will see and the tolerance that they are rated at. Type Y5S or better are recommended (±22% tolerance over the temperature range -30 °C to +85 °C).

Figure 3. Transient Types

Bulk capacitance with a low Effective Series Resistance (ESR) should also be placed near the Pentium Pro processor in order to handle changes in average current between the low-power and normal operating states. About 4000  $\mu F$  of capacitance with an ESR of 5 m $\Omega$  makes a good starting point for simulations, although more capacitance may be needed to bring the ESR down to this level due to the current technology in the industry. The Pentium Pro Processor Voltage Regulator Modules already contain this bulk capacitance. Be sure to determine what is available on the market before choosing parameters for the models. Also, include power supply response time and cable inductance in a full simulation.

See AP-523, *Pentium<sup>®</sup> Pro Processor Power Distribution Guidelines* (Order Number 242764), for power modeling for the Pentium Pro processor.

#### 2.4.1. GTL+ DECOUPLING

Although the Pentium Pro processor GTL+ bus receives power external to the Pentium Pro processor, it should be noted that this power supply will also require the same diligent decoupling methodologies as the processor. Notice that the existence of external power entering through the I/O buffers causes the V<sub>SS</sub> current to be higher than the V<sub>CC</sub> current as evidenced in Figure 3.

#### 2.4.2. PHASE LOCK LOOP (PLL) DECOUPLING

Isolated analog decoupling is required for the internal PLL. This should be equivalent to  $0.1 \,\mu\text{F}$  of ceramic capacitance. The capacitor should be type Y5R or better and should be across the PLL1 and PLL2 pins of the Pentium Pro processor. ("Y5R" implies ±15% tolerance over the temperature range -30 °C to +85 °C.)

## 2.5. BCLK Clock Input Guidelines

The BCLK input directly controls the operating speed of the GTL+ bus interface. All GTL+ external timing parameters are specified with respect to the rising edge of the BCLK input. Clock multiplying within the processor is provided by an internal Phase Lock Loop (PLL) which requires a constant frequency BCLK input. Therefore the BCLK frequency cannot

be changed dynamically. It can however be changed when RESET# is active assuming that all reset specifications are met for the clock and the configuration signals.

The Pentium Pro processor core frequency must be configured during reset by using the A20M#, IGNNE#, LINT1/NMI, and LINT0/INTR pins. The value on these pins during RESET#, and until two clocks beyond the end of the RESET# pulse, determines the multiplier that the PLL will use for the internal core clock. See Appendix A for the definition of these pins during reset. At all other times their functionality is defined as the compatibility signals that the pins are named after. These signals are 3.3 V tolerant and may be driven by existing logic devices. This is important for both functions of the pins.

Supplying a bus clock multiplier this way is required in order to increase processor performance without changing the processor design, and to maintain the bus frequency such that system boards can be designed to function properly as CPU frequencies increase.

## 2.5.1. SETTING THE CORE CLOCK TO BUS CLOCK RATIO

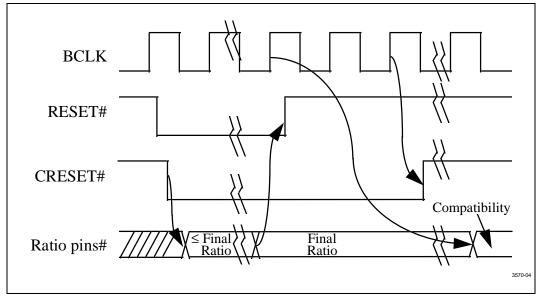

Table 31 lists the configuration pins and the values that must be driven at reset time in order to set the core clock to bus clock ratio. Figure 4 shows the timing relationship required for the clock ratio signals with respect to RESET# and BCLK. CRESET# from an 82453GX (or 82453KX or 82440FX) is shown since its timing is useful for controlling the multiplexing function that is required for sharing the pins.

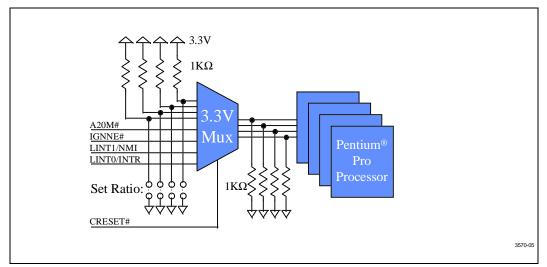

Using CRESET# (CMOS reset), the circuit in Figure 5 can be used to share the pins. The pins of the processors are bussed together to allow any one of them to be the compatibility processor. The component used as the multiplexer must not have outputs that drive higher than 3.3 V in order to meet the Pentium Pro processor's 3.3 V tolerant buffer specifications. The multiplexer output current should be limited to 200 mA maximum, in case the  $V_{CC}P$  supply to the processor ever fails.

The pull-down resistors between the multiplexer and the processor (1 K $\Omega$ ) force a ratio of 2x into the processor in the event that the Pentium Pro processor powers up before the multiplexer and/or the chip set. This prevents the processor from ever seeing a ratio higher than the final ratio.

If the multiplexer were powered by V<sub>CC</sub>P, CRESET# would still be unknown until the 3.3 V supply came up to power the CRESET# driver. A pull-down can be used on CRESET# instead of the four between the multiplexer and the Pentium Pro processor. In this case, the multiplexer must be designed such that the compatibility inputs are truly ignored as their state is unknown.

In any case, the compatibility inputs to the multiplexer must meet the input specifications of the multiplexer. This may require a level translation before the multiplexer inputs unless the inputs and the signals driving them are already compatible.

For FRC mode processors, one multiplexer will be needed per FRC pair, and the multiplexer will need to be clocked using BCLK to meet setup and hold times to the processors. This may require the use of high speed programmable logic.

Figure 4. Timing Diagram of Clock Ratio Signals

Figure 5. Example Schematic for Clock Ratio Pin Sharing

## 2.6. Voltage Identification

There are four Voltage Identification Pins on the Pentium Pro processor package. These pins can be used to support automatic selection of power supply voltage. These pins are not signals but are each either an open circuit in the package or a short circuit to  $V_{SS}$ .

The opens and shorts define the voltage required by the processor. This has been added to cleanly support voltage specification variations on future Pentium Pro processors. These pins are named VID0 through VID3 and the definition of these pins is shown in Table 1. A '1' in this table refers to an open pin and '0' refers to a short to ground. The V<sub>CC</sub>P power supply should supply the voltage that is requested *or* disable itself.

| VID[3:0] | Voltage<br>Setting | VID[3:0] | Voltage<br>Setting |

|----------|--------------------|----------|--------------------|

| 0000     | 3.5                | 1000     | 2.7                |

| 0001     | 3.4                | 1001     | 2.6                |

| 0010     | 3.3                | 1010     | 2.5                |

| 0011     | 3.2                | 1011     | 2.4                |

| 0100     | 3.1                | 1100     | 2.3                |

| 0101     | 3.0                | 1101     | 2.2                |

| 0110     | 2.9                | 1110     | 2.1                |

| 0111     | 2.8                | 1111     | No CPU<br>Present  |

#### NOTES:

- Nominal setting requiring regulation to ±5% at the Pentium<sup>®</sup> Pro processor V<sub>CC</sub>P pins under all conditions. Support not expected for 2.1 V—2.3 V.

- 2. 1= Open circuit; 0= Short to V<sub>SS</sub>

Support for a wider range of VID settings will benefit the system in meeting the power requirements of future Pentium Pro processors. Note that the '1111' (or all opens) ID can be used to detect the absence of a processor in a given socket as long as the power supply used does not affect these lines.

To use these pins, they may need to be pulled up by an external resistor to another power source. The power source chosen should be one that is guaranteed to be stable whenever the supply to the voltage regulator is stable. This will prevent the possibility of the Pentium Pro processor supply running up to 3.5 V in the event of a failure in the supply for the VID lines. Note that the specification for the Pentium Pro Processor Voltage Regulator Modules allows the use of these signals either as TTL compatible levels or as opens and shorts. Using them as TTL compatible levels will require the use of pull-up resistors to 5 V if the input voltage to the regulator is 5 V and the use of a voltage divider if the input voltage to the regulator is 12 V. The resistors chosen should not cause the current through a VID pin to exceed its specification in Table 3. There must not be any other components on these signals if the VRM uses them as opens and shorts.

## 2.7. JTAG Connection

The debug port described in the Pentium® Pro Processor Family Developer's Manual, Volume 1: Specifications (Order Number 242690), should be at the start and end of the JTAG chain with TDI to the first component coming from the Debug Port and TDO from the last component going to the Debug Port. The recommended pull-up value for Pentium Pro processor TDO pins is 240  $\Omega$ . Due to the voltage levels supported by the Pentium Pro processor JTAG logic, it is recommended that the Pentium Pro processors and any other 3.3 V logic level components within the system be first in the JTAG chain. A translation buffer should be used to connect to the rest of the chain unless a 5 V component can be used next that is capable of accepting a 3.3 V input. Similar considerations must be made for TCK, TMS and TRST#. Components may need these signals buffered to match required logic levels.

In a multiprocessor system, be cautious when including empty Pentium Pro processor sockets in the scan chain. All sockets in the scan chain must have a processor installed to complete the chain or the system must support a method to bypass the empty sockets.

See the *Pentium® Pro Processor Family Developer's Manual, Volume 1: Specifications* (Order Number 242690), for full information on putting a debug port in the JTAG chain.

## 2.8. Signal Groups

In order to simplify the following discussion, signals have been combined into groups by buffer type. All outputs are open drain and require an external high-level source provided externally by the termination or a pull-up resistor.

GTL+ input signals have differential input buffers which use  $V_{REF}$  as their reference signal. GTL+ output signals require termination to 1.5 V. Later in this document, the term "GTL+ Input" refers to the GTL+ input group as well as the GTL+ I/O group when receiving. Similarly, "GTL+ Output" refers to the GTL+ output group as well as the GTL+ I/O group when driving.

The 3.3 V tolerant, Clock, APIC and JTAG inputs can each be driven from ground to 3.3 V. The 3.3 V tolerant, APIC, and JTAG outputs can each be pulled high to as much as 3.3 V. See Table 7 for specifications.

The groups and the signals contained within each group are shown in Table 2. Note that the signals ASZ[1:0]#, ATTR[7:0]#, BE[7:0]#, BREQ#[3:0], DEN#, DID[7:0]#, DSZ[1:0]#, EXF[4:0]#, LEN[1:0]#, SMMEM#, and SPLCK# are all GTL+ signals that are shared onto another pin. Therefore they do not appear in this table.

#### 2.8.1. ASYNCHRONOUS VS. SYNCHRONOUS

All GTL+ signals are synchronous. All of the 3.3 V tolerant signals can be applied asynchronously, except when running two processors in FRC mode. To run in FRC mode, synchronization logic is required on all signals (except PWRGOOD) going to both processors. Also note the timing requirements

for PICCLK with respect to BCLK. With FRC enabled, PICCLK must be ¼X BCLK and synchronized with respect to BCLK. PICCLK must always lag BCLK by at least 1 ns and no more than 5 ns.

## 2.9. PWRGOOD

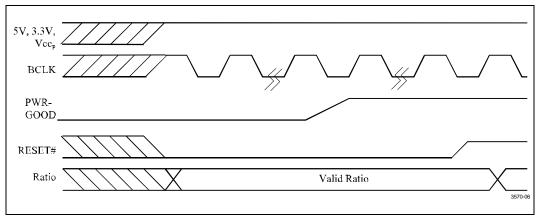

PWRGOOD is a 3.3 V tolerant input. It is expected that this signal will be a clean indication that clocks and the system 3.3 V. 5 V and VccP supplies are stable and within their specifications. Clean implies that the signal will remain low (capable of sinking leakage current) without glitches, from the time that the power supplies are turned on until they come within specification. The signal will then transition monotonically to a high (3.3 V) state. Figure 6 illustrates the relationship of PWRGOOD to other system signals. PWRGOOD can be driven inactive at any time, but power and clocks must again be stable before the rising edge of PWRGOOD. It must also meet the minimum pulse width specification in Table 13 and be followed by a 1mS RESET# pulse, per Table 10.

This signal must be supplied to the Pentium Pro processor as it is used to protect internal circuits against voltage sequencing issues. Use of this signal is recommended for added reliability.

This signal does not need to be synchronized for FRC operation. It should remain high throughout boundary scan testing.

| Group Name               | Signals                                                                                                                                                        |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GTL+ Input               | BPRI#, BR[3:1]#1, DEFER#, RESET#, RS[2:0]#, RSP#, TRDY#                                                                                                        |

| GTL+ Output              | PRDY#                                                                                                                                                          |

| GTL+ I/O                 | A[35:3]#, ADS#, AERR#, AP[1:0]#, BERR#, BINIT#, BNR#, BP[3:2]#, BPM[1:0]#, BR0#, D[63:0]#, DBSY#, DEP[7:0]#, DRDY#, FRCERR, HIT#, HITM#, LOCK#, REQ[4:0]#, RP# |

| 3.3 V Tolerant<br>Input  | A20M#, FLUSH#, IGNNE#, INIT#, LINT0/INTR, LINT1/NMI, PREQ#, PWRGOOD2, SMI#, STPCLK#                                                                            |

| 3.3 V Tolerant<br>Output | FERR#, IERR#, THERMTRIP#3                                                                                                                                      |

| Clock <sup>4</sup>       | BCLK                                                                                                                                                           |

| APIC Clock <sup>4</sup>  | PICCLK                                                                                                                                                         |

| APIC I/O <sup>4</sup>    | PICD[1:0]                                                                                                                                                      |

| JTAG Input <sup>4</sup>  | TCK, TDI, TMS, TRST#                                                                                                                                           |

| JTAG Output <sup>4</sup> | тро                                                                                                                                                            |

| Power/Other <sup>5</sup> | CPUPRES#, PLL1, PLL2, TESTHI, TESTLO, UP#, V <sub>CC</sub> P, V <sub>CC</sub> 5, VID[3:0], V <sub>REF</sub> [7:0], V <sub>SS</sub>                             |

#### Table 2. Signal Groups

#### NOTES:

- 1. The BR0# pin is the only BREQ# signal that is bi-directional. The internal BREQ# signals are mapped onto BR# pins after the agent ID is determined.

- 2. See PWRGOOD in Section 2.9.

- 3. See THERMTRIP# in Section 2.10.

- 4. These signals are tolerant to 3.3 V. Use a 150  $\Omega$  pull-up resistor on PICD[1:0] and 240 $\Omega$  on TDO.

- CPUPRES# is a ground pin defined to allow a designer to detect the presence of a processor in a socket. (preliminary) PLL1 and PLL2 are for decoupling the internal PLL (see Section 2.4.2.).

- TESTHI pins should be tied to  $V_{CC}P$ . A 10K pull-up may be used. See Section 2.11.

- TESTLO pins should be tied to  $V_{SS}$ . A 1K pull-down may be used. See Section 2.11.

- UP# is an open in the Pentium® Pro processor.

- V<sub>CC</sub>P is the primary power supply.

- V<sub>CC</sub>5 is unused by Pentium Pro processor.

- VID[3:0] lines are described in Section 2.6.

- V<sub>REF</sub> [7:0] are the reference voltage pins for the GTL+ buffers.

- V<sub>SS</sub> is ground.

Figure 6. PWRGOOD Relationship at Power-On

## 2.10. THERMTRIP#

The Pentium Pro processor protects itself from catastrophic overheating by use of an internal thermal sensor. This sensor is set well above the normal operating temperature to ensure that there are no false trips. The processor will stop all execution when the junction temperature exceeds ~135 °C. This is signaled to the system by the THERMTRIP# pin. Once activated, the signal remains latched, and the processor stopped, until RESET# goes active. There is no hysteresis built into the thermal sensor itself, so as long as the die temperature drops below the trip level, a RESET# pulse will reset the processor and execution will continue. If the temperature has not dropped beyond the trip level, the processor will continue to drive THERMTRIP# and remain stopped.

## 2.11. Unused Pins

All RESERVED pins must remain unconnected. All pins named TESTHI must be pulled up, no higher than  $V_{CC}P$ , and may be tied directly to  $V_{CC}P$ . All pins named TESTLO must be pulled low and may be tied directly to  $V_{SS}$ .

PICCLK must be driven with a clock input, and the PICD[1:0] lines must each be pulled-up to 3.3 V with a separate 150  $\Omega$  resistor, even when the APIC will not be used.

For reliable operation, always connect unused inputs to an appropriate signal level. Unused GTL+ inputs should be pulled-up to V<sub>TT</sub>. Unused active low 3.3 V tolerant inputs should be connected to 3.3 V with a 150  $\Omega$  resistor and unused active high inputs should be connected to ground (V<sub>SS</sub>). A resistor must also be used when tying bi-directional signals to power or ground. When tying any signal to power or ground, a resistor will also allow for fully testing the processor after board assembly.

For unused pins, it is suggested that ~10 K $\Omega$  resistors be used for pull-ups (except for PICD[1:0] discussed above), and ~1 K $\Omega$  resistors be used as pull-downs. Never tie a pin directly to a supply other than the processor's own V<sub>CC</sub>P supply or to V<sub>SS</sub>.

## 2.12. Maximum Ratings

Table 3 contains Pentium Pro processor stress ratings only. Functional operation at the absolute maximum and minimum is not implied nor guaranteed. The Pentium Pro processor should not receive a clock while subjected to these conditions. Functional operating conditions are given in the AC and DC tables. Extended exposure to the maximum ratings may affect device reliability. Furthermore, although the Pentium Pro processor contains protective circuitry to resist damage from static electric discharge, one should always take precautions to avoid high static voltages or electric fields.

| Symbol                 | Parameter                                                       | Min  | Max                                          | Unit | Notes |

|------------------------|-----------------------------------------------------------------|------|----------------------------------------------|------|-------|

| T <sub>Storage</sub>   | Storage Temperature                                             | -65  | 40                                           | °C   |       |

| T <sub>Bias</sub>      | Case Temperature under Bias                                     | -65  | 110                                          | °C   |       |

| V <sub>CC</sub> P(Abs) | Primary Supply Voltage with respect to $V_{SS}$                 | -0.5 | Operating Voltage + 1.4                      | V    | 2     |

| V <sub>IN</sub>        | GTL+ Buffer DC Input Voltage<br>with respect to V <sub>SS</sub> | -0.5 | $V_{CC}P$ + 0.5 but not to exceed 4.3        | V    | 3     |

| V <sub>IN3</sub>       | 3.3 V Tolerant Buffer DC Input Voltage with respect to $V_{SS}$ | -0.5 | V <sub>CC</sub> P+ 0.9 but not to exceed 4.7 | V    | 4     |

| l <sub>l</sub>         | Maximum input current                                           |      | 200                                          | mA   | 5     |

| I <sub>VID</sub>       | Maximum VID pin current                                         |      | 5                                            | mA   |       |

#### Table 3. Absolute Maximum Ratings<sup>1</sup>

NOTES:

1. Functional operation at the absolute maximum and minimum is not implied or guaranteed.

- 2. Operating voltage is the voltage that the component is designed to operate at. See Table 4 and Table 5.

- 3. Parameter applies to the GTL+ signal groups only.

- 4. Parameter applies to 3.3 V tolerant, APIC, and JTAG signal groups only.

- Current may flow through the buffer ESD diodes when V<sub>IH</sub> > V<sub>CC</sub>P+1.1 V, as in a power supply fault condition or while power supplies are sequencing. Thermal stress should be minimized by cycling power off if the V<sub>CC</sub>P supply fails.

## 2.13. DC Specifications

Table 4 through Table 7 list the DC specifications associated with the Pentium Pro processor. Specifications are valid only while meeting the processor specifications for case temperature, clock frequency and input voltages. **Care should be taken to read all notes associated with each parameter.**

The Pentium Pro processor with 1 MB L2 cache dissipates more power than the Pentium Pro processor with 256 KB or 512 KB L2 cache. DC-DC converter for the Pentium Pro processor with 512 KB L2 cache Pmax limit, need to be re-designed for new Pmax values as well as new V<sub>CC</sub>P values. There are two options for this redesign. (Table 4 and Table 5 list the specifications for these two options.) The first option is to increase the current available from the DC-DC converter to "l<sub>CC</sub>P1" while keeping the normal 3.3 V<sub>CC</sub>P. The second option is to ignore the VID[0:3] value from the processor, and supply 3.2 V V<sub>CC</sub>P (typical) instead. This will require a lower

"I<sub>CC</sub>P2" current and a tighter limit for undershoot and overshoot values for the power supply in the range of +/- 0.1 V. The benefit of the second option is the lower "Pmax2" power dissipation requirement as compared to the "Pmax1", which is required from the first option. The Pentium Pro processor with 1 MB L2 cache is tested to satisfy either solution.

Most of the signals on the Pentium Pro processor are in the GTL+ signal group. These signals are specified to be terminated to 1.5 V. The DC specifications for these signals are listed in Table 6. Care should be taken to read all notes associated with each parameter.

To allow compatibility with other devices, some of the signals are 3.3 V tolerant and can therefore be terminated or driven to 3.3 V. The DC specifications for these 3.3 V tolerant inputs are listed in Table 7. Care should be taken to read all notes associated with each parameter.

| Symbol             | Parameter                       | Min   | Typical | Max   | Unit | Notes |

|--------------------|---------------------------------|-------|---------|-------|------|-------|

| V <sub>CC</sub> P1 | Primary V <sub>CC</sub>         | 3.135 | 3.3     | 3.465 | V    | 1     |

| Pmax1              | Thermal Design Power            |       | 43      | 47    | W    | 3     |

| I <sub>CC</sub> P1 | V <sub>CC</sub> P1 Current      |       |         | 15.0  | А    | 2     |

| I <sub>SGntP</sub> | Stop Grant Current              | 0.3   |         | 1.2   | А    | 4     |

| Τ <sub>C</sub>     | Operational Case<br>Temperature | 0     |         | 80    | °C   |       |

#### Table 4. Power and Voltage Specifications (Option 1)

#### Table 5. Power and Voltage Specifications (Option 2)

| Symbol             | Parameter                       | Min | Typical | Max   | Unit | Notes |  |  |

|--------------------|---------------------------------|-----|---------|-------|------|-------|--|--|

| V <sub>CC</sub> P2 | Primary V <sub>CC</sub>         | 3.1 | 3.2     | 3.3   | V    |       |  |  |

| Pmax2              | Thermal Design Power            |     | 40      | 44    | W    | 3     |  |  |

| I <sub>CC</sub> P2 | V <sub>CC</sub> P2 Current      |     |         | 14.25 | А    | 2     |  |  |

| I <sub>SGntP</sub> | Stop Grant Current              | 0.3 |         | 1.2   | А    | 4     |  |  |

| Τ <sub>C</sub>     | Operational Case<br>Temperature | 0   |         | 80    | °C   |       |  |  |

#### NOTES:

All other DC specifications, AC specifications and timings are identical to the Pentium<sup>®</sup> Pro processor with 256 K and 512 K L2 cache components.

- 1. To meet this 5% tolerance, the equivalent of forty (40) 1  $\mu$ F capacitors (1206 packages) should be placed near the power pins of the device. At least 40  $\mu$ F of capacitance should exist on the power planes, with less than 250 pH of inductance and 4 m $\Omega$  resistance between the capacitance and the pins of the processor, assuming a regulator setting of +/-1%.

- Max current is measured at Max V<sub>CC</sub>, all CMOS pins driven with V<sub>IH</sub>= V<sub>CC</sub>P and V<sub>IL</sub>=0V during the execution of Max I<sub>CC</sub> and Max I<sub>CC</sub>-StopGrant/AutoHalt Tests.

- 3. Maximum values are measured at typical V<sub>CC</sub> but take into account the thermal time constant of the package. Typical values are not tested, but suggest the maximum power expected in a system during actual operation. If designing the system to the typical power level, a fail safe mechanism should be used to guarantee the component Tcase specification in case of workload anomalies.

- Values are measured at typical V<sub>CC</sub>P by asserting the STPCLK# pin or by executing the HALT instruction, with the Low\_Power\_Enable bit set to enabled. Min values are not tested but guaranteed by design.

| · · · · · · · · · · · · · · · · · · · |                           |                        |                       |      |                             |  |  |  |  |

|---------------------------------------|---------------------------|------------------------|-----------------------|------|-----------------------------|--|--|--|--|

| Symbol                                | Parameter                 | Min                    | Max                   | Unit | Notes                       |  |  |  |  |

| V <sub>IL</sub>                       | Input Low Voltage         | -0.3                   | V <sub>REF</sub> -0.2 | V    | 1, See Table 8              |  |  |  |  |

| V <sub>IH</sub>                       | Input High Voltage        | V <sub>REF</sub> + 0.2 | V <sub>CC</sub> P     | V    | 1                           |  |  |  |  |

| V <sub>OL</sub>                       | Output Low Voltage        | 0.30                   | 0.60                  | V    | 2                           |  |  |  |  |

| V <sub>OH</sub>                       | Output High Voltage       | —                      | —                     | V    | See $V_{TT}$ max in Table 8 |  |  |  |  |

| I <sub>OL</sub>                       | Output Low Current        | 36                     | 48                    | mA   | 2                           |  |  |  |  |

| IL                                    | Leakage Current           |                        | ±100                  | mA   | 3                           |  |  |  |  |

| I <sub>REF</sub>                      | Reference Voltage Current |                        | ± 15                  | mA   | 4                           |  |  |  |  |

| C <sub>GTL+</sub>                     | GTL+ Pin Capacitance      |                        | 8.5                   | pF   | 5                           |  |  |  |  |

#### Table 6. GTL+ Signal Groups DC Specifications

#### NOTES:

- 1.  $V_{REF}$  worst case, not nominal. Noise on  $V_{REF}$  should be accounted for.

- 2. Parameter measured into a 25  $\Omega$  resistor to 1.5 V. Min. V<sub>OL</sub> and max. I<sub>OL</sub> are guaranteed by design/characterization.

- 3.  $(0 \le V_{PIN} \le V_{CC}P)$

- 4. Total current for all V<sub>REF</sub> pins. Section 2.1. details the V<sub>REF</sub> connections.

- Total of I/O buffer, package parasitics and 0.5 pF for a socket. Capacitance values guaranteed by design for all GTL+ buffers.

| Symbol           | Parameter                  | Min  | Max        | Unit   | Notes                  |

|------------------|----------------------------|------|------------|--------|------------------------|

| VIL              | Input Low Voltage          | -0.3 | 0.8        | V      |                        |

| VIH              | Input High Voltage         | 2.0  | 3.6        | V      |                        |

| V <sub>OL</sub>  | Output Low Voltage         |      | 0.4<br>0.2 | V<br>V | 2<br>3                 |

| V <sub>OH</sub>  | Output High Voltage        | N/A  | N/A        | V      | All Outputs Open-Drain |

| ۱L               | Input Leakage Current      |      | ±100       | mA     | 4                      |

| C <sub>TOL</sub> | 3.3 V Tol. Pin Capacitance |      | 10         | pF     | Except BCLK & TCK, 5   |

| C <sub>CLK</sub> | BCLK Input Capacitance     |      | 9          | pF     | 5                      |

| Стск             | TCK Input Capacitance      |      | 8          | pF     | 5                      |

#### Table 7. Non-GTL+1 Signal Groups DC Specifications

#### NOTES:

- 1. Table 7 applies to the 3.3 V tolerant, APIC, and JTAG signal groups.

- 2. Parameter measured at 4 mA (for use with TTL inputs).

- 3. Parameter guaranteed by design at 100 µA (for use with CMOS inputs).

- 4.  $(0 \le Vpin \le V_{CC}P)$

- 5. Total of I/O buffer, package parasitics and 0.5 pF for a socket. Capacitance values are guaranteed by design.

## 2.14. GTL+ Bus Specifications

The GTL+ bus must be routed in a daisy-chain fashion with termination resistors at each end of every signal trace. These termination resistors are placed between the ends of the signal trace and the  $V_{TT}$  voltage supply and generally are chosen to approximate the board impedance. The valid high and low levels are determined by the input buffers using a reference voltage called  $V_{REF}$ . Table 8 lists

the nominal specifications for the GTL+ termination voltage ( $V_{TT}$ ) and the GTL+ reference voltage ( $V_{REF}$ ). It is important that the printed circuit board impedance be specified and held to a ±20% tolerance, and that the intrinsic trace capacitance for the GTL+ signal group traces is known. For more details on GTL+, see the GTL+ interface specification in the Pentium® Pro Processor Family Developer's Manual, Volume 1: Specifications (Order Number 242690).

| Symbol          | Parameter               | Min                     | Typical             | Max                     | Units | Notes  |

|-----------------|-------------------------|-------------------------|---------------------|-------------------------|-------|--------|

| V <sub>TT</sub> | Bus Termination Voltage | 1.35                    | 1.5                 | 1.65                    | V     | ±10%   |

| $V_{REF}$       | Input Reference Voltage | 2/3 V <sub>TT</sub> -2% | 2/3 V <sub>TT</sub> | 2/3 V <sub>TT</sub> +2% | V     | ±2%, 1 |

Table 8. GTL+ Bus Voltage Specifications

NOTE:

1. VREF should be created from VTT by a voltage divider of 1% resistors.

## 2.15. AC Specifications

Table 9 through Table 16 list the AC specifications associated with the Pentium Pro processor. Timing Diagrams begin with Figure 8. The AC specifications are broken into categories. Table 9 contains the clock specifications, Table 11 and Table 12 contain the GTL+ specifications, Table 13 is the 3.3 V tolerant Signal group specifications, Table 14 contains timings for the reset conditions, Table 15

covers APIC bus timing, and Table 16 covers Boundary Scan timing.

All AC specifications for the GTL+ signal group are relative to the rising edge of the BCLK input. All GTL+ timings are referenced to  $V_{REF}$  for both '0' and '1' logic levels unless otherwise specified.

Care should be taken to read all notes associated with a particular timing parameter.

| T#  | Parameter             | Min   | Max   | Unit | Figure | Notes                         |

|-----|-----------------------|-------|-------|------|--------|-------------------------------|

|     | Core Frequency        | 150   | 200   | MHz  |        | @ 200 MHz,1                   |

|     | Bus Frequency         | 50.00 | 66.67 | MHz  |        | 1                             |

| T1: | BCLK Period           | 15    | 20    | ns   | 8      |                               |

| T2: | BCLK Period Stability |       | 300   | ps   |        | 2, 3                          |

| T3: | BCLK High Time        | 4     |       | ns   | 8      | @>2.0 V, <sup>2</sup>         |

| T4: | BCLK Low Time         | 4     |       | ns   | 8      | @<0.8 V, 2                    |

| T5: | BCLK Rise Time        | 0.3   | 1.5   | ns   | 8      | (0.8 V - 2.0 V), <sup>2</sup> |

| T6: | BCLK Fall Time        | 0.3   | 1.5   | ns   | 8      | (2.0 V- 0.8 V), <sup>2</sup>  |

Table 9. Bus Clock AC Specifications

#### NOTES:

- 1. The internal core clock frequency is derived from the bus clock. A clock ratio must be driven into the Pentium<sup>®</sup> Pro processor on the signals LINT[1:0], A20M# and IGNNE# at reset. See the descriptions for these signals in Appendix A.

- 2. Not 100% tested. Guaranteed by design/characterization.

- 3. Measured on rising edge of adjacent BCLKs at 1.5 V.

The jitter present must be accounted for as a component of BCLK skew between devices. Clock jitter is measured from one rising edge of the clock signal to the next rising edge at 1.5 V. To remain within the clock jitter specifications, all clock periods must be within 300 ps of the ideal clock period for a given frequency. For example, a 66.67 MHz clock with a nominal period of 15 ns, must not have any single clock period that is greater than 15.3 ns or less than 14.7 ns. To ensure 1:1 relationship between the amplitude of the input jitter and the internal and external clocks, the jitter frequency spectrum should not have any power spectrum peaking between 100 kHz and 10 MHz. A spectrum analyzer can display the frequency spectrum of the clock driver in your system.

#### Table 10. Supported Clock Ratios<sup>1</sup>

| Component | 2X | 5/2X | 3X | 7/2X | 4X |

|-----------|----|------|----|------|----|

| 200 MHz   |    | х    | х  |      | х  |

NOTE:

1. Only those indicated by an 'X' are tested during the manufacturing test process.

|      |                                           | -    |     |      |        |         |

|------|-------------------------------------------|------|-----|------|--------|---------|

| T#   | Parameter                                 | Min  | Max | Unit | Figure | Notes   |

| T7A: | GTL+ Output Valid Delay $H \rightarrow L$ | 0.80 | 4.4 | ns   | 9      | 1       |

| T7B: | GTL+ Output Valid Delay L $\rightarrow$ H | 0.80 | 3.9 | ns   | 9      | 1       |

| T8:  | GTL+ Input Setup Time                     | 2.2  |     | ns   | 10     | 2, 3, 4 |

| T9:  | GTL+ Input Hold Time                      | 0.70 |     | ns   | 10     | 4       |

| T10: | RESET# Pulse Width                        | 1    |     | ms   | 13, 14 | 5       |

#### Table 11. GTL+ Signal Groups AC Specifications

#### NOTES:

Valid delay timings for these signals are specified into an idealized 25 Ω resistor to 1.5 V with V<sub>REF</sub> at 1.0 V. Minimum values guaranteed by design. See the GTL+ interface specification in the *Pentium<sup>®</sup> Pro Processor Family Developer's Manual, Volume 1: Specifications* (Order Number 242690), for the actual test configuration.

- 2. A minimum of 3 clocks must be guaranteed between 2 active-to-inactive transitions of TRDY#.

- 3. RESET# can be asserted (active) asynchronously, but must be deasserted synchronously.

- 4. Specification takes into account a 0.3 V/ns edge rate and the allowable V<sub>REF</sub> variation. Guaranteed by design.

- 5. After V<sub>CC</sub>, V<sub>TT</sub>, V<sub>REF</sub>, BCLK and the clock ratio become stable.

|    | Parameter                        | Min  | Unit | Figure | Notes |

|----|----------------------------------|------|------|--------|-------|

| α: | Overshoot                        | 100  | mV   | 12     | 1     |

| τ: | Minimum Time at High             | 1.5  | ns   | 12     | 1     |

| ρ: | Amplitude of Ringback            | -100 | mV   | 12     | 1     |

| δ: | Duration of Square wave Ringback | N/A  | ns   | 12     | 1     |

| ф: | Final Settling Voltage           | 100  | mV   | 12     | 1     |

#### Table 12. GTL+ Signal Groups Ringback Tolerance

NOTE:

1. Specified for an edge rate of 0.3-0.8 V/ns. See the GTL+ interface specification in the Pentium® Pro Processor Family Developer's Manual, Volume 1: Specifications (Order Number 242690), for the definition of these terms, and for the generic waveforms. All values determined by design/characterization.

| Table 13. 3.3 V Tolerant Signal Groups AC Specification | S |

|---------------------------------------------------------|---|

|                                                         |   |

| T#   | Parameter                                        | Min | Max | Unit  | Figure | Notes         |

|------|--------------------------------------------------|-----|-----|-------|--------|---------------|

| T11: | 3.3 V Tolerant Output Valid Delay                | 1   | 8   | ns    | 9      | 1             |

| T12: | 3.3 V Tolerant Input Setup Time                  | 5   |     | ns    | 10     | 2, 3, 4, 5, 7 |

| T13: | 3.3 V Tolerant Input Hold Time                   | 1.5 |     | ns    | 10     | 7             |

| T14: | 3.3 V Tolerant Input Pulse Width, except PWRGOOD | 2   |     | BCLKs | 9      | Both levels   |

| T15: | PWRGOOD Inactive Pulse Width                     | 10  |     | BCLKs | 9, 14  | 6             |

NOTES:

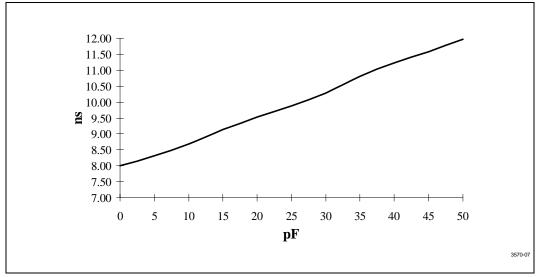

1. Valid delay timings for these signals are specified into 150  $\Omega$  to 3.3 V. See Figure 7 for a capacitive derating curve.

2. These inputs may be driven asynchronously. However, to guarantee recognition on a specific clock, the setup and hold times with respect to BCLK must be met.

- 3. These signals must be driven synchronously in FRC mode.

- 4. A20M#, IGNNE#, INIT# and FLUSH# can be asynchronous inputs, but to guarantee recognition of these signals following a synchronizing instruction such as an I/O write instruction, they must be valid with active RS[2:0]# signals of the corresponding synchronizing bus transaction.

- 5. INTR and NMI are only valid in APIC disable mode. LINT[1:0]# are only valid in APIC enabled mode.

6. When driven inactive, or after Power, VREF, BCLK, and the ratio signals are stable.

7. Specified over the clock rise time (T<sub>r</sub>) and fall time (T<sub>f</sub>) ranges of 0.3 ns to 2 ns for these signals, between 0.8 V and 2.0 V (as defined by Figure 8).

Figure 7. 3.3 V Tolerant Group Derating Curve

| T#   | Parameter                                                                 | Min | Max | Unit  | Figure | Notes                             |

|------|---------------------------------------------------------------------------|-----|-----|-------|--------|-----------------------------------|

| T16: | Reset Configuration Signals<br>(A[14:5]#, BR0#, FLUSH#, INIT#) Setup Time | 4   |     | BCLKs | 13     | Before deassertion of<br>RESET#   |

| T17: | Reset Configuration Signals<br>(A[14:5]#, BR0#, FLUSH#, INIT#) Hold Time  | 2   | 20  | BCLKs | 13     | After clock that deasserts RESET# |

| T18: | Reset Configuration Signals<br>(A20M#, IGNNE#, LINT[1:0]#) Setup Time     | 1   |     | ms    | 13     | Before deassertion of<br>RESET#   |

| T19: | Reset Configuration Signals<br>(A20M#, IGNNE#, LINT[1:0]#) Delay Time     |     | 5   | BCLKs | 13     | After assertion of RESET# 1       |

| T20: | Reset Configuration Signals<br>(A20M#, IGNNE#, LINT[1:0]#) Hold Time      | 2   | 20  | BCLKs | 13, 14 | After clock that deasserts RESET# |

#### **Table 14. Reset Conditions AC Specifications**

#### NOTE:

intel

1. For a reset, the clock ratio defined by these signals must be a safe value (their final or lower multiplier) within this delay unless PWRGOOD is being driven inactive.

| T#    | Parameter                      | Min | Max  | Unit | Figure | Notes      |  |  |  |

|-------|--------------------------------|-----|------|------|--------|------------|--|--|--|

| T21A: | PICCLK Frequency               | 2   | 33.3 | MHz  |        |            |  |  |  |

| T21B: | FRC Mode BCLK to PICCLK offset | 1   | 5    | ns   | 11     | 1          |  |  |  |

| T22:  | PICCLK Period                  | 30  | 500  | ns   | 8      |            |  |  |  |

| T23:  | PICCLK High Time               | 12  |      | ns   | 8      |            |  |  |  |

| T24:  | PICCLK Low Time                | 12  |      | ns   | 8      |            |  |  |  |

| T25:  | PICCLK Rise Time               | 1   | 5    | ns   | 8      |            |  |  |  |

| T26:  | PICCLK Fall Time               | 1   | 5    | ns   | 8      |            |  |  |  |

| T27:  | PICD[1:0] Setup Time           | 8   |      | ns   | 10     | 2          |  |  |  |

| T28:  | PICD[1:0] Hold Time            | 2   |      | ns   | 10     | 2, 5       |  |  |  |

| T29:  | PICD[1:0] Valid Delay          | 2.1 | 10   | ns   | 9      | 2, 3, 4, 5 |  |  |  |

#### Table 15. APIC Clock and APIC I/O AC Specifications

#### NOTES:

1. With FRC enabled PICCLK must be ¼X BCLK and synchronized with respect to BCLK. PICCLK must always lag BCLK by at least 1 ns and no more than 5 ns.

- 2. Referenced to PICCLK Rising Edge.

- 3. For open drain signals, Valid Delay is synonymous with Float Delay.

- 4. Valid delay timings for these signals are specified into 150  $\Omega$  to 3.3 V.

- 5. Specified over the rise time ( $T_r$ ) and fall time ( $T_f$ ) ranges of 0.3 ns to 2 ns for these signals, between 0.8 V and 2.0 V (as defined by Figure 8).

| T#   | Parameter                       | Min  | Max | Unit | Figure | Notes                       |

|------|---------------------------------|------|-----|------|--------|-----------------------------|

| T30: | TCK Frequency                   | _    | 16  | MHz  |        |                             |

| T31: | TCK Period                      | 62.5 | _   | ns   | 8      |                             |

| T32: | TCK High Time                   | 25   |     | ns   | 8      | @2.0 V, 1                   |

| T33: | TCK Low Time                    | 25   |     | ns   | 8      | @0.8 V, 1                   |

| T34: | TCK Rise Time                   |      | 5   | ns   | 8      | (0.8 V-2.0 V), 1, 2         |

| T35: | TCK Fall Time                   |      | 5   | ns   | 8      | (2.0 V-0.8 V), 1, 2         |

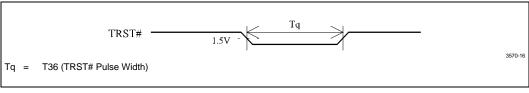

| T36: | TRST# Pulse Width               | 40   |     | ns   | 16     | <sup>1</sup> , Asynchronous |

| T37: | TDI, TMS Setup Time             | 5    |     | ns   | 15     | 3                           |

| T38: | TDI, TMS Hold Time              | 14   |     | ns   | 15     | 3                           |

| T39: | TDO Valid Delay                 | 1    | 10  | ns   | 15     | 4, 5                        |

| T40: | TDO Float Delay                 |      | 25  | ns   | 15     | 1, 4, 5                     |

| T41: | All Nontest Outputs Valid Delay | 2    | 25  | ns   | 15     | 4, 6, 7                     |

| T42: | All Nontest Outputs Float Delay |      | 25  | ns   | 15     | 1, 4, 6, 7                  |

| T43: | All Nontest Inputs Setup Time   | 5    |     | ns   | 15     | 3, 6, 7, 8                  |

| T44: | All Nontest Inputs Hold Time    | 13   |     | ns   | 15     | 3, 6, 7, 8                  |

#### Table 16. Boundary Scan Interface AC Specifications

#### NOTES:

- 1. Not 100% tested. Guaranteed by design/characterization.

- 2. 1 ns can be added to the maximum TCK rise and fall times for every 1 MHz below 16 MHz.

- 3. Referenced to TCK rising edge.

- 4. Referenced to TCK falling edge.

- 5. Valid delay timing for this signal is specified into 150  $\Omega$  terminated to 3.3 V.

- Nontest Outputs and Inputs are the normal output or input signals (besides TCK, TRST#, TDI, TDO and TMS). These

timings correspond to the response of these signals due to boundary scan operations. PWRGOOD should be driven high

throughout boundary scan testing.

- 7. During Debug Port operation, use the normal specified timings rather than the boundary scan timings.

- Specified over the rise time (T<sub>r</sub>) and fall time (T<sub>f</sub>) ranges of 0.3 ns to 2 ns for these signals, between 0.8 V and 2.0 V (as defined by Figure 8).

Figure 9. Valid Delay Timings

Figure 10. Setup and Hold Timings

Figure 11. FRC Mode BCLK to PICCLK Timing

Figure 12. Low to High GTL+ Receiver Ringback Tolerance

Figure 13. Reset and Configuration Timings

Figure 14. Power-On Reset and Configuration Timings

Figure 15. Test Timings (Boundary Scan)

Figure 16. Test Reset Timings

#### 3.0. **GTL+ INTERFACE** SPECIFICATION

For the generic GTL+ interface specification, see the Pentium<sup>®</sup> Pro Processor Family Developer's Manual Volume 1: Specifications (Order Number 242690), Chapter 12.

#### 3.3 V TOLERANT SIGNAL 4.0. QUALITY SPECIFICATIONS

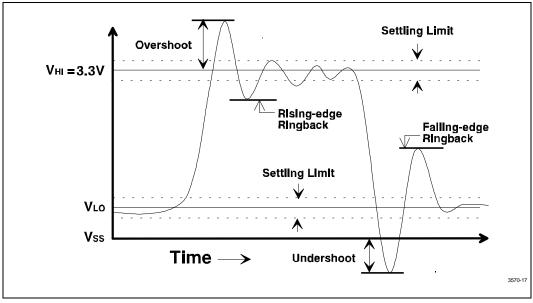

The signals that are 3.3 V tolerant should also meet signal quality specifications to guarantee that the components read data properly and to ensure that incoming signals do not affect the long term reliability of the component. There are three signal quality parameters defined for the 3.3 V tolerant signals. They are Overshoot/Undershoot, Ringback and Settling Limit. All three signal quality parameters are shown in Figure 17. The Pentium® Pro Processor I/O Buffer Models-IBIS Format (on World Wide Web page http://www.intel.com) contain models for simulating 3.3 V tolerant signal distribution.

#### 4.1. **Overshoot/Undershoot** Guidelines

Overshoot (or undershoot) is the absolute value of the maximum voltage allowed above the nominal high voltage or below V<sub>SS</sub>. The overshoot/undershoot guideline limits transitions beyond V<sub>CC</sub>P or V<sub>SS</sub> due to the fast signal edge rates. See Figure 17. The processor can be damaged by repeated overshoot events on 3.3 V tolerant buffers if the charge is large

enough (i.e., if the overshoot is great enough). However, excessive ringback is the dominant harmful effect resulting from overshoot or undershoot (i.e., violating the overshoot/undershoot guideline will make satisfying the ringback specification difficult). The overshoot/undershoot auideline is 0.8 V and assumes the absence of diodes on the input. These quidelines should be verified in simulations without the on-chip ESD protection diodes present because the diodes will begin clamping the 3.3 V tolerant signals beginning at approximately 1.5 V above V<sub>CC</sub>P and 0.5 V below V<sub>SS</sub>. If signals are not reaching the clamping voltage, then this is not an issue. A system should not rely on the diodes for overshoot/undershoot protection as this will negatively affect the life of the components and make meeting the ringback specification very difficult.

## 4.2. Ringback Specification

Ringback refers to the amount of reflection seen after a signal has undergone a transition. The ringback specification is the voltage that the signal rings **back to after achieving its farthest excursion.** See Figure 17 for an illustration of ringback. Excessive ringback can cause false signal detection or extend the propagation delay. The ringback specification applies to the input pin of each receiving agent. Violations of the signal Ringback specification are not allowed under any circumstances.

Ringback can be simulated with or without the input protection diodes that can be added to the input buffer model. However, signals that reach the clamping voltage should be evaluated further. See Table 17 for the signal ringback specifications for Non-GTL+ signals.

| Table 17. | Signal | Ringback | Specifications |

|-----------|--------|----------|----------------|

|           |        |          |                |

| Transition | Maximum Ringback<br>(with input diodes present) |

|------------|-------------------------------------------------|

| 0→1        | 2.5 V                                           |

| 1→0        | 0.8 V                                           |

Figure 17. 3.3 V Tolerant Signal Overshoot/Undershoot and Ringback

## 4.3. Settling Limit Guideline

A Settling Limit defines the maximum amount of ringing at the receiving pin that a signal must be limited to before its next transition. The amount allowed is 10% of the total signal swing ( $V_{HI}$ - $V_{LO}$ ) above and below its final value. A signal should be within the settling limits of its final value, when either in its high state of low state, before it transitions again.

Signals that are not within their settling limit before transitioning are at risk of unwanted oscillations which could jeopardize signal integrity. Simulations to verify Settling Limit may be done either with or without the input protection diodes present. Violation of the Settling Limit guideline is acceptable if simulations of 5-10 successive transitions do not show the amplitude of the ringing increasing in the subsequent transitions.

## 5.0. THERMAL SPECIFICATIONS

This section defines the thermal specification of the Pentium Pro processor with 1 MB L2 cache.

## 5.1. Thermal Parameters

This section defines terms used for the Pentium Pro processor with 1 MB L2 cache thermal analysis.

### 5.1.1. AMBIENT TEMPERATURE

Ambient temperature,  $T_A$ , is the temperature of the ambient air surrounding the package. In a system environment, ambient temperature is the temperature of the air upstream from the package and in its close vicinity; or in an active cooling system, it is the inlet air to the active cooling device.