### int PENTIUM<sup>™</sup> PROCESSOR AT iCOMP INDEX 510\60 MHz PENTIUM<sup>™</sup> PROCESSOR AT iCOMP INDEX 567\66 MHz

Binary Compatible with Large Software Base

– DOS, OS/2, UNIX, and WINDOWS

- 32-Bit Microprocessor - 32-Bit Addressing - 64-Bit Data Bus

- Superscalar Architecture

- Two Pipelined Integer Units

- Capable of under One Clock per Instruction

- Pipelined Floating Point Unit

- Separate Code and Data Caches

- 8K Code, 8K Write Back Data

- 2-Way 32-Byte Line Size

- Software Transparent

- MESI Cache Consistency Protocol

- Advanced Design Features - Branch Prediction

- Virtual Mode Extensions

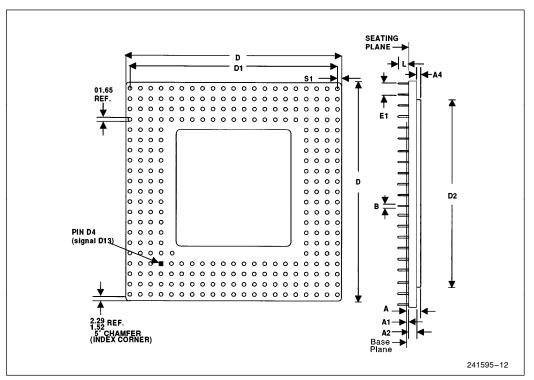

- 273-Pin Grid Array Package

- BiCMOS Silicon Technology

- Increased Page Size - 4M for Increased TLB Hit Rate

- Multi-Processor Support - Multiprocessor Instructions - Support for Second Level Cache

- Internal Error Detection

- Functional Redundancy Checking - Built in Self Test

- Parity Testing and Checking

- IEEE 1149.1 Boundary Scan Compatibility

- Performance Monitoring

- Counts Occurrence of Internal Events

- Traces Execution through Pipelines

The Pentium processor (510\60, 567\66) provides the next generation of power for high-end workstations and servers. The Pentium processor (510\60, 567\66) is compatible with the entire installed base of applications for DOS, Windows, OS/2, and UNIX. The Pentium processor's superscalar architecture can execute two instructions per clock cycle. Branch Prediction and separate caches also increase performance. The pipelined floating point unit of the Pentium processor (510\60, 567\66) delivers workstation level performance. Separate code and data caches reduce cache conflicts while remaining software transparent. The Pentium processor (510\60, 567\66) has 3.1 million transistors and is built on Intel's 0.8 Micron BiCMOS silicon technology.

241595-1

MS-DOS and Windows are registered trademarks of Microsoft Corporation. OS/2 is a trademark of International Business Machines Corporation. UNIX is a registered trademark of UNIX System Laboratories, Inc.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel. November 1994 Order Number: 241595-002

© INTEL CORPORATION, 1994

### Pentium<sup>™</sup> Processor (510\60, 567\66)

| CONTENTS                                    | PAGE | CONTENTS       |

|---------------------------------------------|------|----------------|

| 1.0 MICROPROCESSOR                          |      | 3.0 ELECTRICA  |

| ARCHITECTURE OVERVIEW .                     | 3    | 3.1 Power and  |

| 2.0 PINOUT                                  | 6    | 3.2 Decoupling |

| 2.1 Pinout and Pin Descriptions             | 6    | 3.3 Connectio  |

| 2.1.1 Pentium™ Processor                    |      | 3.4 Maximum    |

| (510\60, 567\66) Pinout .                   | 6    | 3.5 D.C. Speci |

| 2.2 Design Notes                            | 9    | 3.6 A.C. Speci |

| 2.3 Quick Pin Reference                     | 9    |                |

| 2.4 Pin Reference Tables                    | 16   | 4.0 MECHANICA  |

| 2.5 Pin Grouping According to<br>Function   |      | 5.0 THERMAL S  |

| 2.6 Output Pin Grouping Accordi when Driven |      |                |

| 3.0 ELECTRICAL SPECIFICATIONS 18  |

|-----------------------------------|

| 3.1 Power and Ground              |

| 3.2 Decoupling Recommendations 19 |

| 3.3 Connection Specifications 19  |

| 3.4 Maximum Ratings 19            |

| 3.5 D.C. Specifications 20        |

| 3.6 A.C. Specifications 20        |

| 4.0 MECHANICAL SPECIFICATIONS 29  |

| 5.0 THERMAL SPECIFICATIONS        |

PAGE

#### 1.0 MICROPROCESSOR ARCHITECTURE OVERVIEW

The Pentium<sup>™</sup> processor (510\60, 567\66) is the next generation member of the Intel386<sup>™</sup> and Intel486<sup>™</sup> microprocessor family. It is 100% binary compatible with the 8086/88, 80286, Intel386 DX CPU, Intel386 SX CPU, Intel486 DX CPU, Intel486 SX and the Intel486 DX2 CPUs.

The Pentium processor (510\60, 567\66) contains all of the features of the Intel486 CPU, and provides significant enhancements and additions including the following:

- Superscalar Architecture

- Dynamic Branch Prediction

- Pipelined Floating-Point Unit

- Improved Instruction Execution Time

- Separate 8K Code and Data Caches

- Writeback MESI Protocol in the Data Cache

- 64-Bit Data Bus

- Bus Cycle Pipelining

- Address Parity

- Internal Parity Checking

- Functional Redundancy Checking

- Execution Tracing

- Performance Monitoring

- IEEE 1149.1 Boundary Scan

- System Management Mode

- Virtual Mode Extensions

The application instruction set of the Pentium processor (510\60, 567\66) includes the complete Intel486 CPU instruction set with extensions to accommodate some of the additional functionality of the Pentium processor (510\60, 567\66). All application software written for the Intel386 and Intel486 microprocessors will run on the Pentium processor (510\60, 567\66) without modification. The on-chip memory management unit (MMU) is completely compatible with the Intel386 and Intel486 CPUs.

The Pentium processor (510\60, 567\66) implements several enhancements to increase performance. The two instruction pipelines and floatingpoint unit on the Pentium processor (510\60, 567/66) are capable of independent operation. Each pipeline issues frequently used instructions in a single clock. Together, the dual pipes can issue two integer instructions in one clock, or one floating point instruction (under certain circumstances, 2 floating point instructions) in one clock.

#### **PENTIUM™ PROCESSOR (510\60, 567\66)**

Branch prediction is implemented in the Pentium processor (510\60, 567\66). To support this, the Pentium processor (510\60, 567\66) implements two prefetch buffers, one to prefetch code in a linear fashion, and one that prefetches code according to the BTB so the needed code is almost always prefetched before it is needed for execution.

The floating-point unit has been completely redesigned over the Intel486 CPU. Faster algorithms provide up to 10X speed-up for common operations including add, multiply, and load.

The Pentium processor (510\60, 567\66) includes separate code and data caches integrated on chip to meet its performance goals. Each cache is 8 Kbytes in size, with a 32-byte line size and is 2-way set associative. Each cache has a dedicated Translation Lookaside Buffer (TLB) to translate linear addresses to physical addresses. The data cache is configurable to be writeback or writethrough on a line by line basis and follows the MESI protocol. The data cache tags are triple ported to support two data transfers and an inquire cycle in the same clock. The code cache is an inherently write protected cache. The code cache tags are also triple ported to support snooping and split line accesses. Individual pages can be configured as cacheable or noncacheable by software or hardware. The caches can be enabled or disabled by software or hardware.

The Pentium processor (510\60, 567\66) has increased the data bus to 64-bits to improve the data transfer rate. Burst read and burst writeback cycles are supported by the Pentium processor (510\60, 567\66). In addition, bus cycle pipelining has been added to allow two bus cycles to be in progress simultaneously. The Pentium processor (510\60, 567\66) Memory Management Unit contains optional extensions to the architecture which allow 4 Mbyte page sizes.

The Pentium processor (510\60, 567\66) has added significant data integrity and error detection capability. Data parity checking is still supported on a byte by byte basis. Address parity checking, and internal parity checking features have been added along with a new exception, the machine check exception. In addition, the Pentium processor (510\60, 567\66) has implemented functional redundancy checking to provide maximum error detection of the processor and the interface to the processor. When functional redundancy checking is used, a second processor, the "checker" is used to execute in lock step with the "master" processor. The checker samples the master's outputs and compares those values with the values it computes internally, and asserts an error signal if a mismatch occurs.

As more and more functions are integrated on chip, the complexity of board level testing is increased. To address this, the Pentium processor (510\60, 567\66) has increased test and debug capability. Like many of the Intel486 CPUs, the Pentium processor (510\60, 567\66) implements IEEE Boundary Scan (Standard 1149.1). In addition, the Pentium processor (510\60, 567\66) has specified 4 breakpoint pins that correspond to each of the debug registers and externally indicate a breakpoint match. Execution tracing provides external indications when an instruction has completed execution in either of the two internal pipelines, or when a branch has been taken.

System management mode has been implemented along with some extensions to the SMM architecture. Enhancements to the Virtual 8086 mode have been made to increase performance by reducing the number of times it is necessary to trap to a virtual 8086 monitor.

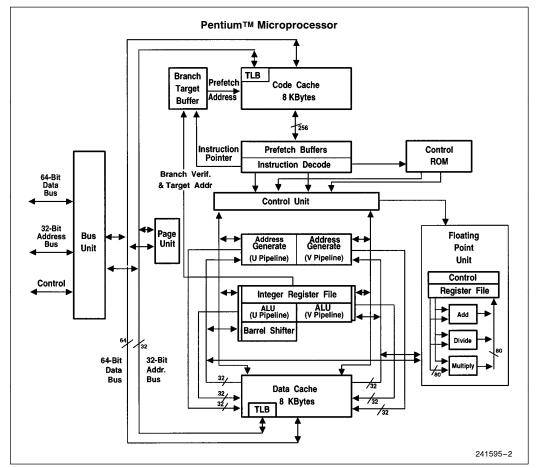

Figure 1-1 shows a block diagram of the Pentium processor (510\60, 567\66).

The block diagram shows the two instruction pipelines, the "u" pipe and the "v" pipe. The u-pipe can execute all integer and floating point instructions. The v-pipe can execute simple integer instructions and the FXCH floating point instructions.

Figure 1-1. Pentium™ Processor (510\60, 567\66) Block Diagram

#### **PENTIUM™ PROCESSOR (510\60, 567\66)**

The separate caches are shown, the code cache and data cache. The data cache has two ports, one for each of the two pipes (the tags are triple ported to allow simultaneous inquire cycles). The data cache has a dedicated Translation Lookaside Buffer (TLB) to translate linear addresses to the physical addresses used by the data cache.

The code cache, branch target buffer and prefetch buffers are responsible for getting raw instructions into the execution units of the Pentium processor (510\60, 567\66). Instructions are fetched from the code cache or from the external bus. Branch addresses are remembered by the branch target buffer. The code cache TLB translates linear addresses to physical addresses used by the code cache. The decode unit decodes the prefetched instructions so the Pentium processor (510\60, 567\66) can execute the instruction. The control ROM contains the microcode which controls the sequence of operations that must be performed to implement the Pentium processor (510\60, 567\66) architecture. The control ROM unit has direct control over both pipelines.

The Pentium processor (510\60, 567\66) contains a pipelined floating point unit that provides a significant floating point performance advantage over previous generations of the Pentium processor (510\60, 567\66).

The architectural features introduced in this chapter are more fully described in the *Pentium*<sup>TM</sup> *Processor* (510\60, 567\66) User's Manual.

### 2.0 PINOUT

### 2.1 Pinout and Pin Descriptions

2.1.1 Pentium™ PROCESSOR (510\60, 567\66) PINOUT

|     | 1          | 2         | 3            | 4            | 5         | 6         | 7         | 8         | 9         | 10       | 11        | 12        | 13        | 14_       | 15        | 16        | 17        | 18        | 19        | 20          | 21        |    |

|-----|------------|-----------|--------------|--------------|-----------|-----------|-----------|-----------|-----------|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-------------|-----------|----|

| ۹ ( |            | О<br>м/ю# | ежве         | ↓ ()<br>↓ () | O<br>Vcc  | ⊖<br>Vcc  | O<br>Vcc  | O<br>Vcc  | O<br>DP2  | )<br>D23 | ()<br>Vcc | ()<br>Vcc |           | O<br>Vcc  | O<br>Vcc  | O<br>Vcc  | O<br>Vcc  | Vcc       | O<br>DP5  | ()<br>D43   | ()<br>D45 | •  |

| в   | O<br>IV    | O<br>BP2  | О<br>ВРЗ     | ()<br>D6     | ()<br>Vss | ()<br>Vss | ()<br>Vss | O<br>Vss  | ()<br>D17 | 〇<br>D24 | ()<br>Vss | ()<br>Vss | ()<br>Vss | ⊖<br>Vss  | ⊖<br>Vss  | ()<br>Vss |           | O<br>VSS  | ()<br>D41 | ()<br>D47   | ()<br>D48 | E  |

| :   | ⊖<br>Vcc   |           | О<br>РМ1/ВР1 |              | O<br>DP1  | 〇<br>D18  | ()<br>D22 | ()<br>D25 | )<br>D29  | )<br>D31 | 〇<br>D26  | O<br>D9   | ()<br>D10 | ()<br>D12 | ()<br>D19 | ()<br>D21 | )<br>D33  | D36       | ()<br>D34 | ()<br>D50   | ()<br>D52 | c  |

| D   | ⊖<br>Vcc   |           |              | ()<br>D13    | )<br>D15  | 〇<br>D16  | )<br>D20  | O<br>DP3  | )<br>D27  | O<br>D32 | 0<br>D28  | )<br>D30  | ()<br>D14 | ⊖<br>D40  | )<br>D39  | 〇<br>D37  | )<br>D35  | O<br>DP4  | ()<br>D38 | ()<br>D42   | ()<br>D44 | 0  |

| E   | ⊖<br>Vcc   | )<br>Vss  |              | 0<br>D2      | 0<br>D11  |           |           |           |           |          |           |           |           |           |           |           |           | )<br>D46  | O<br>DP6  | )<br>D54    | O<br>DP7  | E  |

| F   | ⊖<br>Vcc   | )<br>Vss  | )<br>D3      | 0<br>D8      |           |           |           |           |           |          |           |           |           |           |           |           |           | )<br>D51  | ()<br>D49 | 0<br>D57    | ()<br>Vcc | F  |

| a   | ⊖<br>Vcc   | )<br>Vss  | 0<br>D5      | ()<br>D7     |           |           |           |           |           |          |           |           |           |           |           |           |           | )<br>D53  | )<br>D55  | ()<br>Vss   | ()<br>Vcc | G  |

| н   | ⊖<br>Vcc   | O<br>Vss  | FERR#        |              |           |           |           |           |           |          |           |           |           |           |           |           |           | )<br>D63  | ()<br>D59 | ()<br>Vss   | ()<br>D56 | F  |

| L   | O<br>Vss   | C<br>U    | O<br>KEN#    | CACHE        |           |           |           |           |           |          |           |           |           |           |           |           |           | 0<br>D58  | )<br>D62  | O<br>Vss    |           |    |

| ĸ   | )<br>Vss   | )<br>Vss  | O<br>NA#     | O<br>BOFF#   |           |           |           |           |           | _        |           |           |           |           |           |           |           | CLK       | 0<br>D61  | ()<br>Vss   |           | ۲  |

| L   |            |           |              |              | *         |           |           |           |           | To       | op Vi     | ew        |           |           |           |           |           |           | -         | O<br>Vss    |           | ı  |

| M   | O<br>Vss v |           | eads#        | О<br>НІТМ#   |           |           |           |           |           |          |           |           |           |           |           |           |           |           |           | ()<br># Vss |           | h  |

| N   | ⊖<br>Vcc   | ⊖<br>Vss  | ₩/R#         | O<br>NC      |           |           |           |           |           |          |           |           |           |           |           |           |           |           | O<br>NMI  | O<br>Vss    |           | •  |

| Р   | ⊖<br>Vcc   | O<br>Vss  |              | O<br>ADS#    |           |           |           |           |           |          |           |           |           |           |           |           |           | SMI#      | о<br>тмs  | O<br>Vss    | O<br>Vcc  | F  |

| ٩   | ⊖<br>Vcc   | )<br>Vss  |              | O<br>BE1#    |           |           |           |           |           |          |           |           |           |           |           | •         |           |           | O<br>NC   | O<br>Vss    | Vcc       | G  |

| R   | )<br>Vcc   | O<br>Vss  | о<br>рснк#   | О<br>scyc    |           |           |           |           |           |          |           |           |           |           |           |           |           | O<br>R/S# | NC        | U<br>Vss    | Vcc       | F  |

| s   | Vcc        | Vss       | -            | BE5#         | L         |           |           |           |           |          |           |           |           |           |           |           |           |           |           |             | ~         | \$ |

| т   |            | )<br>Vss  | визснк       | # TCKS       |           | # BE4     | # BT2     | O<br>BTO  | 0<br>A26  | 0<br>A19 | 0<br>A17  | O<br>A15  | 0<br>A13  | 0<br>A11  | ()<br>A9  |           | <b>A3</b> | ~         | ВТ        |             |           | 1  |

| U   | O<br>Vcc   |           |              | O<br>BE0#    | A20M#     | BE2#      | BE6#      | 0<br>A24  | 0<br>A22  | 0<br>A20 | ()<br>A18 | 0<br>A16  | 0<br>A14  | 0<br>A12  | ()<br>A10 | 0<br>A8   | 0<br>A6   | -         | A25       | A23         | A21       | ľ  |

|     | O<br>BE3#  | BREQ      | LOCK#        | D/C#         | HOLD      | A28       | O<br>Vss  | O<br>Vss  | O<br>Vss  | Vss      | O<br>Vss  | O<br>Vss  | O<br>Vss  | O<br>Vss  | O<br>Vss  | O<br>Vss  | Vs        |           | ()<br>A31 | ()<br>A29   | A27       | 1  |

| N   | O<br>BE7#  | HIT#      | арснк#       | PCD          |           |           |           | O<br>Vcc  | O<br>Vcc  | Vcc      | O<br>Vcc  | O<br>Vcc  | Vcc       | O<br>Vcc  | O<br>Vcc  |           |           | c Vcc     | 0<br>A4   | ВТЗ         | O<br>BT1  | V  |

|     | 1          | 2         | 3            | 4            | 5         | 6         | 7         | 8         | 9         | 10       | 11        | 12        | 13        | 14        | 15        | 16        | 17        | 18        | 19        | 20          | 21        |    |

Figure 2-1. Pentium™ Processor (510\60, 567\66) Pinout (Top View)

PRELIMINARY

|   | 21       | 20       | 19        | 18       | 17       | 16       | 15       | 14       | 13       | 12       | 11        | 10        | 9        | 8        | 7          | 6        | 5        | 4          | 3          | 2           | 1         |

|---|----------|----------|-----------|----------|----------|----------|----------|----------|----------|----------|-----------|-----------|----------|----------|------------|----------|----------|------------|------------|-------------|-----------|

| w | BT1      | ВТЗ      | 0<br>A4   | Vcc      | O<br>Vcc | Vcc      | Vcc      | Vcc      | Vcc      | Vcc      | Vcc       | Vcc       | Vcc      | Vcc      | Vcc        | Vcc      | A30      | PCD        | АРСНК#     | HIT#        | O<br>BE7# |

| v | 0<br>A27 | A29      | 0<br>A31  | O<br>Vss | O<br>Vss | O<br>Vss | O<br>Vss | O<br>Vss | O<br>Vss | Uss      | O<br>Vss  | O<br>Vss  | O<br>Vss | 0<br>Vss | O<br>Vss   | 0<br>A28 | HOLD     | D/C#       | LOCK#      | BREQ        | O<br>BE3# |

| υ | A21      | A23      | 0<br>A25  | 0<br>A5  | 0<br>A6  | ()<br>A8 | 0<br>A10 | A12      | 0<br>A14 | 0<br>A16 | 0<br>A18  | A20       | 0<br>A22 | A24      | BE6#       |          | A20M     |            | PRDY       | FLUSH#      |           |

| T | ğ        | INIT     | вт        | NĊ       | A3       | A7       | A9       | A11      | A13      | A15      | A17       | A19       | A26      | вто      | BT2        | BE4# S   | SMIAC    |            | BUSCHK#    | Vss         | Vcc       |

| s |          |          |           | TRST#    | 0        | 0        | 0        | 0        | 0        | 0        | 0         |           | $\cap$   | 0        | 0          | 0        | 0        | BE5#       | PWT        | Vss         | Vcc       |

| R | Vcc      | Vss      | NČ        | R∕Š#     |          |          |          |          |          |          |           |           |          |          |            |          |          | scyc       | PCHK#      | Vss         | Vcc       |

|   | Vcc      | Vss      | NC        | Vcc      |          |          |          |          |          |          |           |           |          |          |            |          |          | BE1#       | HĽDA       | Vss         | Vcc       |

| Q | Vcc      | Vss<br>O | TMS<br>() | SMI#     |          |          |          |          |          |          |           |           |          |          |            |          |          | ADS#       | AP<br>O    | Vss         | Vcc       |

| Р | 0        | 0        |           |          |          |          |          |          |          |          |           |           |          |          |            |          |          | NČ         | ₩/R#       | Vss         | Vcc       |

| N |          | Vss /    | 0         | 0        |          |          |          |          |          |          |           |           |          |          |            |          |          | 0          | 0          | 0           | 0         |

| м | O        | 0        | RCMC      | 0        |          |          |          |          |          |          |           |           |          |          |            |          |          | О НПМ#     |            | О<br>WB/WT# | O<br>Vas  |

| L |          | O<br>Vss | 0<br>D60  |          |          |          |          |          |          | Boti     | tom       | View      |          |          |            |          |          |            |            |             | O<br>Vss  |

| к | O<br>Vcc | O<br>Vss | 0<br>D61  |          |          |          |          |          |          |          |           |           |          |          |            |          |          | O<br>BOFF# | O<br>NA#   | O<br>Vss    | O<br>Vss  |

| J | O<br>Vcc | 0<br>V55 | 0<br>D62  | 0<br>D58 |          |          |          |          |          |          |           |           |          |          |            |          |          | CACHE#     | O<br>KEN#  |             | )<br>V55  |

| н | 0<br>D56 | O<br>Vss | 0<br>D59  | 0<br>D63 |          |          |          |          |          |          |           |           |          |          |            |          |          | O<br>DP0   | O<br>FERR# | O<br>Vss    | ⊖<br>V∝   |

| G | O<br>Vcc | O<br>Vss | 0<br>D55  | O<br>D53 |          |          |          |          |          |          |           |           |          |          |            |          |          | 0<br>D7    | 0<br>D5    | O<br>Vss    | ⊖<br>Vcc  |

| F |          | 0<br>D57 | 0<br>D49  | 0<br>D51 |          |          |          |          |          |          |           |           |          |          |            |          |          |            | 0<br>D3    | O<br>Vss    | Vcc       |

| E | DP7      | 0<br>D54 | O<br>DP6  | 0<br>D46 | <u>г</u> |          |          |          |          |          |           |           |          |          |            |          | 0<br>    | 0<br>D2    | O<br>D1    | O<br>Vss    | ⊖<br>Vcc  |

| D | 0<br>D44 | 0<br>D42 | D38       | O<br>DP4 | )<br>D35 | D37      | D39      | 0<br>D40 | 0<br>D14 | D30      | ()<br>D28 | ()<br>D32 | 0<br>D27 | O<br>DP3 | ()<br>D20  | O<br>D16 | 0<br>D15 | 0<br>D13   |            | ~           |           |

| с | D52      | 0<br>D50 | 0<br>D34  | 0<br>D36 | 0<br>D33 | 0<br>D21 | 0<br>D19 | 0<br>D12 | 0<br>D10 | )<br>D9  | 0<br>D26  | 0<br>D31  | 0<br>D29 | 0<br>D25 | 022<br>022 | 0<br>D18 | DP1      |            | PM1/BP1    | O<br>IERR#  | Vcc       |

| в | D48      | 0<br>D47 | 0<br>D41  | O<br>Vss | 0<br>V55 | 0<br>V55 | O<br>Vss | O<br>Vss | 0<br>V35 | O<br>Vss | O<br>Vss  | 0<br>D24  | 0<br>D17 | O<br>Vss | O<br>Vss   | O<br>Vss | 0<br>Vss | 0<br>D6    | O<br>BP3   | O<br>BP2    | 0<br>V    |

| A | D45      | 0<br>D43 | O<br>DP5  | O<br>Vcc |          |          | O<br>Vcc |          | Vcc      |          | Vcc       | 0<br>D23  | O<br>DP2 | Vcc      |            |          |          |            | EWBE#      | О<br>мло#   | INV       |

|   | 21       | 20       | 19        | 18       | 17       | 16       | 15       | 14       |          | 12       |           | 10        | 9        | 8        | 7          | 6        | 5        | 4          | 3          | 2           |           |

Figure 2-2. Pentium™ Processor (510\60, 567\66) Pinout (Bottom View)

| Tabl   | e 2-1. Pentiur | m™ Processor | (510\60, 56 | 7\66) Pin Cı | oss Reference | e Table by Pin N | lame     |

|--------|----------------|--------------|-------------|--------------|---------------|------------------|----------|

| Signal | Location       | Signal       | Location    | Signal       | Location      | Signal           | Location |

| A3     | T17            | BE2#         | U06         | D18          | C06           | D54              | E20      |

| A4     | W19            | BE3#         | V01         | D19          | C15           | D55              | G19      |

| A5     | U18            | BE4#         | T06         | D20          | D07           | D56              | H21      |

| A6     | U17            | BE5#         | S04         | D21          | C16           | D57              | F20      |

| A7     | T16            | BE6#         | U07         | D22          | C07           | D58              | J18      |

| A8     | U16            | BE7#         | W01         | D23          | A10           | D59              | H19      |

| A9     | T15            | BOFF#        | K04         | D24          | B10           | D60              | L19      |

| A10    | U15            | BP2          | B02         | D25          | C08           | D61              | K19      |

| A11    | T14            | BP3          | B03         | D26          | C11           | D62              | J19      |

| A12    | U14            | BRDY#        | L04         | D27          | D09           | D63              | H18      |

| A13    | T13            | BREQ         | V02         | D28          | D11           | D/C#             | V04      |

| A14    | U13            | BT0          | T08         | D29          | C09           | DP0              | H04      |

| A15    | T12            | BT1          | W21         | D30          | D12           | DP1              | C05      |

| A16    | U12            | BT2          | T07         | D31          | C10           | DP2              | A9       |

| A17    | T11            | BT3          | W20         | D32          | D10           | DP3              | D08      |

| A18    | U11            | BUSCHK#      | Т03         | D33          | C17           | DP4              | D18      |

| A19    | T10            | CACHE#       | J04         | D34          | C19           | DP5              | A19      |

| A20    | U10            | CLK          | K18         | D35          | D17           | DP6              | E19      |

| A21    | U21            | D0           | D03         | D36          | C18           | DP7              | E21      |

| A22    | U09            | D1           | E03         | D37          | D16           | EADS#            | M03      |

| A23    | U20            | D2           | E04         | D38          | D19           | EWBE#            | A03      |

| A24    | U08            | D3           | F03         | D39          | D15           | FERR#            | H03      |

| A25    | U19            | D4           | C04         | D40          | D14           | FLUSH#           | U02      |

| A26    | Т09            | D5           | G03         | D41          | B19           | FRCMC#           | M19      |

| A27    | V21            | D6           | B04         | D42          | D20           | HIT#             | W02      |

| A28    | V06            | D7           | G04         | D43          | A20           | HITM#            | M04      |

| A29    | V20            | D8           | F04         | D44          | D21           | HLDA             | Q03      |

| A30    | W05            | D9           | C12         | D45          | A21           | HOLD             | V05      |

| A31    | V19            | D10          | C13         | D46          | E18           | IBT              | T19      |

| A20M#  | U05            | D11          | E05         | D47          | B20           | IERR#            | C02      |

| ADS#   | P04            | D12          | C14         | D48          | B21           | IGNNE#           | S20      |

| AHOLD  | L02            | D13          | D04         | D49          | F19           | INIT             | T20      |

| AP     | P03            | D14          | D13         | D50          | C20           | INTR             | N18      |

| APCHK# | W03            | D15          | D05         | D51          | F18           | INV              | A01      |

| BE0#   | U04            | D16          | D06         | D52          | C21           | IU               | J02      |

| BE1#   | Q04            | D17          | B09         | D53          | G18           | IV               | B01      |

PRELIMINARY

#### **PENTIUM™ PROCESSOR (510\60, 567\66)**

| Signal  | Location |  | Signal  | Location |  | S |  |  |  |  |  |  |

|---------|----------|--|---------|----------|--|---|--|--|--|--|--|--|

| KEN#    | J03      |  | RESET   | L18      |  | Ν |  |  |  |  |  |  |

| LOCK#   | V03      |  | R/S#    | R18      |  |   |  |  |  |  |  |  |

| M/IO#   | A02      |  | SCYC    | R04      |  | V |  |  |  |  |  |  |

| NA#     | K03      |  | SMI#    | P18      |  |   |  |  |  |  |  |  |

| NMI     | N19      |  | SMIACT# | T05      |  |   |  |  |  |  |  |  |

| PCD     | W04      |  | ТСК     | T04      |  |   |  |  |  |  |  |  |

| PCHK#   | R03      |  | TDI     | T21      |  |   |  |  |  |  |  |  |

| PEN#    | M18      |  | TD0     | S21      |  |   |  |  |  |  |  |  |

| PM0/BP0 | D02      |  | TMS     | P19      |  |   |  |  |  |  |  |  |

| PM1/BP1 | C03      |  | TRST#   | S18      |  |   |  |  |  |  |  |  |

| PRDY    | U03      |  | WB/WT#  | M02      |  |   |  |  |  |  |  |  |

| PWT     | S03      |  | W/R#    | N03      |  |   |  |  |  |  |  |  |

|         |          |  |         |          |  |   |  |  |  |  |  |  |

Table 2-1. Pentium™ Processor (510\60, 567\66) Pin Cross Reference Table by Pin Name (Continued)

#### Location Signal Location ignal B05, B06, ١C L03, N04, Vss Q19, R19, B07, B08, S19, T18 B11, B12, B13, B14, A04, A05, /cc B15, B16, A06, A07, B17, B18, A08, A11, E02, F02, A12, A13, G02, G20, A14, A15, H02, H20, A16, A17, J01, J20, A18, C01, K01, K02, D01, E01, K20, L01, F01, F21, L20, M01, G01, G21, M20, N02, H01, J21 N20, P02, K21, L21, P20, Q02, M21, N01, Q20, R02, N21, P01, R20, S02, P21, Q01, T02, V07, Q18, Q21, V08, V09, R01, R21, V10, V11, S01, T01, V12, V13, U01, W06, V14, V15, W07, W08, V16, V17, W09, W10, V18 W11, W12, W13, W14, W15, W16, W17, W18

#### 2.2 Design Notes

For reliable operation, always connect unused inputs to an appropriate signal level. Unused active LOW inputs should be connected to  $V_{CC}$ . Unused active HIGH inputs should be connected to GND.

No Connect (NC) pins must remain unconnected. Connection of NC pins may result in component failure or incompatibility with processor steppings.

#### NOTE:

The No Connect pin located at L03 (BRDYC#) along with BUSCHK# are sampled by the Pentium processor (510\60, 567\66) at RESET to configure the I/O buffers of the processor for use with the 82496 Cache Controller/82491 Cache SRAM secondary cache as a chip set (refer to the 82496 Cache Controller/82491 Cache SRAM Data Book for Use with the Pentium<sup>TM</sup> Processor (510\60, 567\66) for further information).

#### 2.3 Quick Pin Reference

This section gives a brief functional description of each of the pins. For a detailed description, see the Hardware Interface chapter in the *Pentium<sup>TM</sup> Processor (510\60, 567\66) User's Manual*, Vol. 1. **Note that all input pins must meet their AC/DC specifications to guarantee proper functional behavior**. In this section, the pins are arranged in alphabetical order. The functional grouping of each pin is listed at the end of this chapter.

The # symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage. When a # symbol is not present after the signal name, the signal is active, or asserted at the high voltage level.

PRELIMINARY

| Table | 2-2  | Quick | Pin | Reference |

|-------|------|-------|-----|-----------|

| Iable | 2-2. | QUICK | гш  | nelelelle |

| Symbol                | Type* | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20M#                 | I     | When the <i>address bit 20 mask</i> pin is asserted, the Pentium™ Processor (510\60, 567\66) emulates the address wraparound at one Mbyte which occurs on the 8086. When A20M# is asserted, the Pentium processor (510\60, 567\66) masks physical address bit 20 (A20) before performing a lookup to the internal caches or driving a memory cycle on the bus. The effect of A20M# is undefined in protected mode. A20M# must be asserted only when the processor is in real mode.                                      |

| A31–A3                | I/O   | As outputs, the <i>address</i> lines of the processor along with the byte enables define the physical area of memory or I/O accessed. The external system drives the inquire address to the processor on A31–A5.                                                                                                                                                                                                                                                                                                        |

| ADS#                  | 0     | The <i>address status</i> indicates that a new valid bus cycle is currently being driven by the Pentium processor (510\60, 567\66).                                                                                                                                                                                                                                                                                                                                                                                     |

| AHOLD                 | I/O   | In response to the assertion of <i>address hold</i> , the Pentium processor (510\60, 567\66) will stop driving the address lines (A31–A3), and AP in the next clock. The rest of the bus will remain active so data can be returned or driven for previously issued bus cycles.                                                                                                                                                                                                                                         |

| АР                    | I/O   | Address parity is driven by the Pentium processor (510\60, 567\66) with even parity information on all Pentium processor (510\60, 567\66) generated cycles in the same clock that the address is driven. Even parity must be driven back to the Pentium processor (510\60, 567\66) during inquire cycles on this pin in the same clock as EADS# to ensure that the correct parity check status is indicated by the Pentium processor (510\60, 567\66).                                                                  |

| APCHK#                | 0     | The <i>address parity check</i> status pin is asserted two clocks after EADS # is sampled active if the Pentium processor (510\60, 567\66) has detected a parity error on the address bus during inquire cycles. APCHK # will remain active for one clock each time a parity error is detected.                                                                                                                                                                                                                         |

| BE7#-BE0#             | 0     | The <i>byte enable</i> pins are used to determine which bytes must be written to external memory, or which bytes were requested by the CPU for the current cycle. The byte enables are driven in the same clock as the address lines (A31–3).                                                                                                                                                                                                                                                                           |

| BOFF #                | 1     | The <i>backoff</i> input is used to abort all outstanding bus cycles that have not yet completed. In response to BOFF #, the Pentium processor (510\60, 567\66) will float all pins normally floated during bus hold in the next clock. The processor remains in bus hold until BOFF # is negated at which time the Pentium processor (510\60, 567\66) restarts the aborted bus cycle(s) in their entirety.                                                                                                             |

| BP[3:2]<br>PM/BP[1:0] | 0     | The <i>breakpoint</i> pins (BP3–0) correspond to the debug registers, DR3–DR0.<br>These pins externally indicate a breakpoint match when the debug registers<br>are programmed to test for breakpoint matches.<br>BP1 and BP0 are multiplexed with the Performance Monitoring pins (PM1 and<br>PM0). The PB1 and PB0 bits in the Debug Mode Control Register determine if<br>the pins are configured as breakpoint or performance monitoring pins. The pins<br>come out of reset configured for performance monitoring. |

| BRDY#                 | I     | The <i>burst ready</i> input indicates that the external system has presented valid data on the data pins in response to a read or that the external system has accepted the Pentium processor (510\60, 567\66) data in response to a write request. This signal is sampled in the T2, T12 and T2P bus states.                                                                                                                                                                                                          |

| Symbol  | Type* | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BREQ    | 0     | The <i>bus request</i> output indicates to the external system that the Pentium processor (510\60, 567\66) has internally generated a bus request. This signal is always driven whether or not the Pentium processor (510\60, 567\66) is driving its bus.                                                                                                                                                                                                                                                                     |

| BT3-BT0 | 0     | The <i>branch trace</i> outputs provide bits 2-0 of the branch target linear address (BT2-BT0) and the default operand size (BT3) during a branch trace message special cycle.                                                                                                                                                                                                                                                                                                                                                |

| BUSCHK# | I     | The <i>bus check</i> input allows the system to signal an unsuccessful completion of a bus cycle. If this pin is sampled active, the Pentium processor (510\60, 567\66) will latch the address and control signals in the machine check registers. If in addition, the MCE bit in CR4 is set, the Pentium processor (510\60, 567\66) will vector to the machine check exception.                                                                                                                                              |

| CACHE # | 0     | For Pentium processor (510\60, 567\66)-initiated cycles the <i>cache</i> pin indicates internal cacheability of the cycle (if a read), and indicates a burst writeback cycle (if a write). If this pin is driven inactive during a read cycle, Pentium processor (510\60, 567\66) will not cache the returned data, regardless of the state of the KEN $\#$ pin. This pin is also used to determine the cycle length (number of transfers in the cycle).                                                                      |

| CLK     | I     | The <i>clock</i> input provides the fundamental timing for the Pentium processor (510\60, 567\66). Its frequency is the internal operating frequency of the Pentium processor (510\60, 567\66) and requires TTL levels. All external timing parameters except TDI, TDO, TMS and TRST# are specified with respect to the rising edge of CLK.                                                                                                                                                                                   |

| D/C#    | 0     | The <i>Data/Code</i> output is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. D/C# distinguishes between data and code or special cycles.                                                                                                                                                                                                                                                                                                                 |

| D63-D0  | 1/0   | These are the 64 <i>data lines</i> for the processor. Lines D7-D0 define the least significant byte of the data bus; lines D63-D56 define the most significant byte of the data bus. When the CPU is driving the data lines, they are driven during the T2, T12, or T2P clocks for that cycle. During reads, the CPU samples the data bus when BRDY $\#$ is returned.                                                                                                                                                         |

| DP7-DP0 | Ι/Ο   | These are the <i>data parity</i> pins for the processor. There is one for each byte of the data bus. They are driven by the Pentium processor (510\60, 567\66) with even parity information on writes in the same clock as write data. Even parity information must be driven back to the Pentium processor (510\60, 567\66) on these pins in the same clock as the data to ensure that the correct parity check status is indicated by the Pentium processor (510\60, 567\66). DP7 applies to D63–D56, DP0 applies to D7–D0. |

| EADS#   | I     | This signal indicates that a <i>valid external address</i> has been driven onto the Pentium processor (510\60, 567\66) address pins to be used for an inquire cycle.                                                                                                                                                                                                                                                                                                                                                          |

| EWBE#   | I     | The <i>external write buffer empty</i> input, when inactive (high), indicates that a write cycle is pending in the external system. When the Pentium processor (510\60, 567\66) generates a write, and EWBE # is sampled inactive, the Pentium processor (510\60, 567\66) will hold off all subsequent writes to all E or M-state lines in the data cache until all write cycles have completed, as indicated by EWBE # being active.                                                                                         |

Table 2-2. Quick Pin Reference (Continued)

PRELIMINARY

| Table 2-2. | Quick | Pin | Reference    | (Continued) | ) |

|------------|-------|-----|--------------|-------------|---|

|            | Guion |     | increacine c | (Continuou) | , |

| Symbol | Type* | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FERR#  | 0     | The <i>floating point error</i> pin is driven active when an unmasked floating point error occurs. FERR# is similar to the ERROR# pin on the Intel387 <sup>™</sup> math coprocessor. FERR# is included for compatibility with systems using DOS type floating point error reporting.                                                                                                                                                                                                                                                |

| FLUSH# | I     | When asserted, the <i>cache flush</i> input forces the Pentium processor (510\60, 567\66) to writeback all modified lines in the data cache and invalidate its internal caches. A Flush Acknowledge special cycle will be generated by the Pentium processor (510\60, 567\66) indicating completion of the writeback and invalidation.<br>If FLUSH # is sampled low when RESET transitions from high to low, tristate test                                                                                                          |

|        |       | mode is entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FRCMC# |       | The <i>Functional Redundancy Checking Master/Checker</i> mode input is used to determine whether the Pentium processor (510\60, 567\66) is configured in master mode or checker mode. When configured as a master, the Pentium processor (510\60, 567\66) drives its output pins as required by the bus protocol. When configured as a checker, the Pentium processor (510\60, 567\66) tristates all outputs (except IERR # and TDO) and samples the output pins.                                                                   |

|        |       | The configuration as a master/checker is set after RESET and may not be changed other than by a subsequent RESET.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HIT#   | 0     | The <i>hit</i> indication is driven to reflect the outcome of an inquire cycle. If an inquire cycle hits a valid line in either the Pentium processor ( $510\60$ , $567\66$ ) data or instruction cache, this pin is asserted two clocks after EADS# is sampled asserted. If the inquire cycle misses Pentium processor ( $510\60$ , $567\66$ ) cache, this pin is negated two clocks after EADS#. This pin changes its value only as a result of an inquire cycle and retains its value between the cycles.                        |

| HITM#  | 0     | The <i>hit to a modified line</i> output is driven to reflect the outcome of an inquire cycle.<br>It is asserted after inquire cycles which resulted in a hit to a modified line in the data<br>cache. It is used to inhibit another bus master from accessing the data until the line<br>is completely written back.                                                                                                                                                                                                               |

| HLDA   | 0     | The <i>bus hold acknowledge</i> pin goes active in response to a hold request driven to the processor on the HOLD pin. It indicates that the Pentium processor (510\60, 567\66) has floated most of the output pins and relinquished the bus to another local bus master. When leaving bus hold, HLDA will be driven inactive and the Pentium processor (510\60, 567\66) will resume driving the bus. If the Pentium processor (510\60, 567\66) has bus cycle pending, it will be driven in the same clock that HLDA is deasserted. |

| HOLD   | I     | In response to the <i>bus hold request</i> , the Pentium processor (510\60, 567\66) will float most of its output and input/output pins and assert HLDA after completing all outstanding bus cycles. The Pentium processor (510\60, 567\66) will maintain its bus in this state until HOLD is deasserted. HOLD is not recognized during LOCK cycles. The Pentium processor (510\60, 567\66) will recognize HOLD during reset.                                                                                                       |

| IBT    | 0     | The <i>instruction branch taken</i> pin is driven active (high) for one clock to indicate that a branch was taken. This output is always driven by the Pentium processor (510\60, 567\66).                                                                                                                                                                                                                                                                                                                                          |

| <b>T</b> . I. I. A. A. | 0        |             |             |

|------------------------|----------|-------------|-------------|

| i apie 2-2.            | QUICK PI | n Reference | (Continued) |

| Symbol  | Type* | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IERR#   | 0     | The <i>internal error</i> pin is used to indicate two types of errors, internal parity errors<br>and functional redundancy errors. If a parity error occurs on a read from an internal<br>array, the Pentium processor ( $510\60$ , $567\66$ ) will assert the IERR# pin for one<br>clock and then shutdown. If the Pentium processor ( $510\60$ , $567\66$ ) is configured<br>as a checker and a mismatch occurs between the value sampled on the pins and<br>the corresponding value computed internally, the Pentium processor ( $510\60$ ,<br>$567\66$ ) will assert IERR# two clocks after the mismatched value is returned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IGNNE # |       | This is the <i>ignore numeric error</i> input. This pin has no effect when the NE bit in CR0 is set to 1. When the CR0.NE bit is 0, and the IGNNE # pin is asserted, the Pentium processor (510\60, 567\66) will ignore any pending unmasked numeric exception and continue executing floating point instructions for the entire duration that this pin is asserted. When the CR0.NE bit is 0, IGNNE # is not asserted, a pending unmasked numeric exception exists (SW.ES = 1), and the floating point instruction is one of FINIT, FCLEX, FSTENV, FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium processor (510\60, 567\66) will exception exists (SW.ES = 1), and the floating point instruction in spite of the pending exception. When the CR0.NE bit is 0, IGNNE # is not asserted, a pending unmasked numeric exception exists (SW.ES = 1), and the floating point instruction in spite of the pending exception exists (SW.ES = 1), and the floating point instruction is one other than FINIT, FCLEX, FSTENV, FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium processor (510\60, 567\66) will stop execution and wait for an external interrupt. |

| INIT    | I     | The Pentium processor (510\60, 567\66) <i>initialization</i> input pin forces the Pentium processor (510\60, 567\66) to begin execution in a known state. The processor state after INIT is the same as the state after RESET except that the internal caches, write buffers, and floating point registers retain the values they had prior to INIT. INIT may NOT be used in lieu of RESET after power-up.<br>If INIT is sampled high when RESET transitions from high to low the Pentium processor (510\60, 567\66) will perform built-in self test prior to the start of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTR    | I     | program execution.<br>An active <i>maskable interrupt</i> input indicates that an external interrupt has been<br>generated. If the IF bit in the EFLAGS register is set, the Pentium processor<br>(510\60, 567\66) will generate two locked interrupt acknowledge bus cycles and<br>vector to an interrupt handler after the current instruction execution is completed.<br>INTR must remain active until the first interrupt acknowledge cycle is generated to<br>assure that the interrupt is recognized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| INV     | I     | The <i>invalidation</i> input determines the final cache line state (S or I) in case of an inquire cycle hit. It is sampled together with the address for the inquire cycle in the clock EADS# is sampled active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IU      | 0     | The <i>u-pipe instruction complete</i> output is driven active (high) for 1 clock to indicate that an instruction in the u-pipeline has completed execution. This pin is always driven by the Pentium processor (510\60, 567\66).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IV      | 0     | The <i>v-pipe instruction complete</i> output is driven active (high) for one clock to indicate that an instruction in the v-pipeline has completed execution. This pin is always driven by the Pentium processor (510\60, 567\66).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| KEN#    | I     | The <i>cache enable</i> pin is used to determine whether the current cycle is cacheable<br>or not and is consequently used to determine cycle length. When the Pentium<br>processor (510\60, 567\66) generates a cycle that can be cached (CACHE #<br>asserted) and KEN # is active, the cycle will be transformed into a burst line fill<br>cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Symbol                | Type* | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCK#                 | 0     | The <i>bus lock</i> pin indicates that the current bus cycle is locked. The Pentium processor (510\60, 567\66) will not allow a bus hold when LOCK# is asserted (but AHOLD and BOFF# are allowed). LOCK# goes active in the first clock of the first locked bus cycle and goes inactive after the BRDY# is returned for the last locked bus cycle. LOCK# is guaranteed to be deasserted for at least one clock between back to back locked cycles.                                                                                                                                                    |

| M/IO#                 | 0     | The <i>Memory/Input-Output</i> is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS # signal is asserted. M/IO # distinguishes between memory and I/O cycles.                                                                                                                                                                                                                                                                                                                                                                                             |

| NA#                   | I     | An active <i>next address</i> input indicates that the external memory system is ready to accept a new bus cycle although all data transfers for the current cycle have not yet completed. The Pentium processor (510\60, 567\66) will drive out a pending cycle two clocks after NA # is asserted. The Pentium processor (510\60, 567\66) supports up to 2 outstanding bus cycles.                                                                                                                                                                                                                   |

| NMI                   | I     | The <i>non-maskable interrupt</i> request signal indicates that an external non-maskable interrupt has been generated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PCD                   | 0     | The <i>page cache disable</i> pin reflects the state of the PCD bit in CR3, the Page Directory Entry, or the Page Table Entry. The purpose of PCD is to provide an external cacheability indication on a page by page basis.                                                                                                                                                                                                                                                                                                                                                                          |

| PCHK#                 | 0     | The <i>parity check</i> output indicates the result of a parity check on a data read. It is driven with parity status two clocks after BRDY # is returned. PCHK # remains low one clock for each clock in which a parity error was detected. Parity is checked only for the bytes on which valid data is returned.                                                                                                                                                                                                                                                                                    |

| PEN#                  | I     | The <i>parity enable</i> input (along with CR4.MCE) determines whether a machine check exception will be taken as a result of a data parity error on a read cycle. If this pin is sampled active in the clock a data parity error is detected, the Pentium processor (510\60, 567\66) will latch the address and control signals of the cycle with the parity error in the machine check registers. If in addition the machine check enable bit in CR4 is set to "1", the Pentium processor (510\60, 567\66) will vector to the machine check exception before the beginning of the next instruction. |

| PM/BP[1:0]B<br>P[3:2] | 0     | These pins function as part of the Performance Monitoring feature.<br>The breakpoint pins BP[1:0] are multiplexed with the Performance Monitoring<br>pins PM[1:0]. The PB1 and PB0 bits in the Debug Mode Control Register<br>determine if the pins are configured as breakpoint or performance monitoring<br>pins. The pins come out of reset configured for performance monitoring.                                                                                                                                                                                                                 |

| PRDY                  | 0     | The PRDY output pin indicates that the processor has stopped normal execution in response to the R/S # pin going active, or Probe Mode being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PWT                   | 0     | The <i>page write through</i> pin reflects the state of the PWT bit in CR3, the Page Directory Entry, or the Page Table Entry. The PWT pin is used to provide an external writeback indication on a page by page basis.                                                                                                                                                                                                                                                                                                                                                                               |

| R/S#                  | I     | The R/S# input is an asynchronous, edge sensitive interrupt used to stop the normal execution of the processor and place it into an idle state. A high to low transition on the R/S# pin will interrupt the processor and cause it to stop execution at the next instruction boundary.                                                                                                                                                                                                                                                                                                                |

### intel

| Symbol  | Type* | Name and Function                                                                                                                                                                                                                                                                                                             |

|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET   | I     | <i>Reset</i> forces the Pentium processor (510\60, 567\66) to begin execution at a known state. All the Pentium processor (510\60, 567\66) internal caches will be invalidated upon the RESET. Modified lines in the data cache are not written back.                                                                         |

|         |       | FLUSH #, FRCMC # and INIT are sampled when RESET transitions from high to low to determine if tristate test mode or checker mode will be entered, or if BIST will be run.                                                                                                                                                     |

| SCYC    | 0     | The <i>split cycle</i> output is asserted during misaligned LOCKed transfers to indicate that more than two cycles will be locked together. This signal is defined for locked cycles only. It is undefined for cycles which are not locked.                                                                                   |

| SMI#    | I     | The system Management Interrupt causes a system management interrupt request to be latched internally. When the latched SMI # is recognized on an instruction boundary, the processor enters System Management Mode.                                                                                                          |

| SMIACT# | 0     | An active <i>system management interrupt active</i> output indicates that the processor is operating in System Management Mode (SMM).                                                                                                                                                                                         |

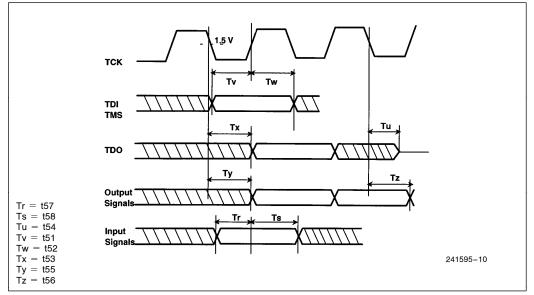

| ТСК     | I     | The <i>testability clock</i> input provides the clocking function for the Pentium processor (510\60, 567\66) boundary scan in accordance with the IEEE Boundary Scan interface (Standard 1149.1). It is used to clock state information and data into and out of the Pentium processor (510\60, 567\66) during boundary scan. |

| TDI     | I     | The <i>test data input</i> is a serial input for the test logic. TAP instructions and data are shifted into the Pentium processor (510\60, 567\66) on the TDI pin on the rising edge of TCK when the TAP controller is in an appropriate state.                                                                               |

| TDO     | 0     | The <i>test data output</i> is a serial output of the test logic. TAP instructions and data are shifted out of the Pentium processor (510\60, 567\66) on the TDO pin on the falling edge of TCK when the TAP controller is in an appropriate state.                                                                           |

| TMS     | I     | The value of the <i>test mode select</i> input signal sampled at the rising edge of TCK controls the sequence of TAP controller state changes.                                                                                                                                                                                |

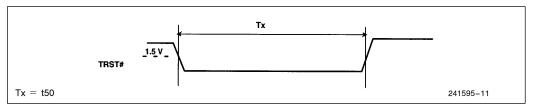

| TRST#   | I     | When asserted, the <i>test reset</i> input allows the TAP controller to be asynchronously initialized.                                                                                                                                                                                                                        |

| W/R#    | 0     | <i>Write/Read</i> is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. $W/R$ # distinguishes between write and read cycles.                                                                                                                                  |

| WB/WT#  | I     | The writeback/writethrough input allows a data cache line to be defined as write back or write through on a line by line basis. As a result, it determines whether a cache line is initially in the S or E state in the data cache.                                                                                           |

#### Table 2-2. Quick Pin Reference (Continued)

#### NOTE:

\*The pins are classified as Input or Output based on their function in Master Mode. See the Functional Redundancy Checking section in the "Error Detection" chapter of the *Pentium™ Processor (510\60, 567\66) User's Manual*, Vol. 1, for further information.

#### 2.4 Pin Reference Tables

| Table 2-3. Output Pins        |                 |                                            |  |  |

|-------------------------------|-----------------|--------------------------------------------|--|--|

| Name                          | Active<br>Level | When Floated                               |  |  |

| ADS#                          | LOW             | Bus Hold, BOFF #                           |  |  |

| APCHK#                        | LOW             |                                            |  |  |

| BE7#-BE0#                     | LOW             | Bus Hold, BOFF #                           |  |  |

| BREQ                          | HIGH            |                                            |  |  |

| BT3-BT0                       | n/a             |                                            |  |  |

| CACHE#                        | LOW             | Bus Hold, BOFF #                           |  |  |

| FERR#                         | LOW             |                                            |  |  |

| HIT#                          | LOW             |                                            |  |  |

| HITM#                         | LOW             |                                            |  |  |

| HLDA                          | HIGH            |                                            |  |  |

| IBT                           | HIGH            |                                            |  |  |