# 80C286/883

## High Performance Microprocessor with Memory Management and Protection

March 1997

## Features

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- Compatible with NMOS 80286/883

- Static CMOS Design for Low Power Operation

ICCSB = 5mA Maximum

- ICCOP = 185mA Maximum (80C286-10/883)

- ICCOP = 220mA Maximum (80C286-12/883)

- Large Address Space

- 16 Megabytes Physical

- 1 Gigabyte Virtual per Task

- Integrated Memory Management, Four-Level Memory Protection and Support for Virtual Memory and Operating Systems

- Two 80C86 Upward Compatible Operating Modes

80C286/883 Real Address Mode

- Protected Virtual Address Mode

- Compatible with 80287 Numeric Data Co-Processor

## Description

The Intersil 80C286/883 is a static CMOS version of the NMOS 80286 microprocessor. The 80C286/883 is an advanced, high-performance microprocessor with specially optimized capabilities for multiple user and multi-tasking systems. The 80C286/883 has built-in memory protection that supports operating system and task isolation as well as program and data privacy within tasks. The 80C286/883 includes memory management capabilities that map 230 (one gigabyte) of virtual address space per task into 2<sup>24</sup> bytes (16 megabytes) of physical memory.

The 80C286/883 is upwardly compatible with 80C86 and 80C88 software (the 80C286/883 instruction set is a superset of the 80C86/80C88 instruction set). Using the 80C286/ 883 real address mode, the 80C286/883 is object code compatible with existing 80C86 and 80C88 software. In protected virtual address mode, the 80C286/883 is source code compatible with 80C86 and 80C88 software but may require upgrading to use virtual address as supported by the 80C286/883's integrated memory management and protection mechanism. Both modes operate at full 80C286/883 performance and execute a superset of the 80C86 and 80C88 instructions.

The 80C286/883 provides special operations to support the efficient implementation and execution of operating systems. For example, one instruction can end execution of one task, save its state, switch to a new task, load its state, and start execution of the new task. The segment-not-present exception and restartable instructions.

## **Ordering Information**

| PACKAGE    | TEMP. RANGE     | 10MHz           | 12.5MHz         | 16MHz       | 20MHz       | 25MHz | PKG. NO. |

|------------|-----------------|-----------------|-----------------|-------------|-------------|-------|----------|

| 68 Pin PGA | 0°C to +70°C    | -               | CG80C286-12     | CG80C286-16 | CG80C286-20 | -     | G68.B    |

|            | -40°C to +85°C  | IG80C286-10     | IG80C286-12     | -           | -           | -     | G68.B    |

|            | -55°C to +125°C | MG80C286-10/883 | MG80C286-12/883 | -           | -           | -     | G68.B    |

|            |                 | 5962-9067801MXC | 5962-9067802MXC | -           | -           | -     | G68.B    |

#### **Absolute Maximum Ratings**

#### Thermal Information

| Supply Voltage+8.0V                                                                                                                                                 | Thermal Resistance (Typical) | θ <sub>JA</sub> | θ <sub>JC</sub> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------|-----------------|

| Input, Output or I/O Voltage AppliedGND -1.0V to V <sub>CC</sub> +1.0V                                                                                              | PGA Package                  | 35°C/W          | 6°C/W           |

| Storage Temperature Range    -65°C to +150°C      Junction Temperature    +175°C      Lead Temperature (Soldering 10s)    +300°C      ESD Classification    Class 1 |                              |                 |                 |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

#### **Operating Conditions**

| Operating Voltage Range +4.5V to +5.5V                     | Input RISE and FALL Time (From 0.8V to 2.0V |

|------------------------------------------------------------|---------------------------------------------|

| Operating Temperature Range55°C to +125°C                  | 80C286-10/883 10ns (Max)                    |

| System Clock (CLK) RISE Time (From 1.0V to 3.6V 8ns (Max)  | 80C286-12/883                               |

| System Clock (CLK) FALL Time (from 3.6V to 1.0V) 8ns (Max) |                                             |

#### TABLE 1. 80C286/883 D.C. ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

|                                                       |                   |                                                                                           | GROUP A        |                                            | LIN                  | <b>NITS</b>          |       |

|-------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------|----------------|--------------------------------------------|----------------------|----------------------|-------|

| PARAMETER                                             | SYMBOL            | CONDITIONS                                                                                | SUB-<br>GROUPS | TEMPERATURE                                | MIN                  | MAX                  | UNITS |

| Input LOW Voltage                                     | V <sub>IL</sub>   | $V_{CC} = 4.5V$                                                                           | 1, 2, 3        | $-55^{o}C \leq T_{A} \leq +125^{o}C$       | -0.5                 | 0.8                  | V     |

| Input HIGH Voltage                                    | V <sub>IH</sub>   | V <sub>CC</sub> = 5.5V                                                                    | 1, 2, 3        | $-55^oC \le T_A \le +125^oC$               | 2.0                  | V <sub>CC</sub> +0.5 | V     |

| CLK Input LOW Voltage                                 | V <sub>ILC</sub>  | V <sub>CC</sub> = 4.5V                                                                    | 1, 2, 3        | $-55^{o}C \leq T_{A} \leq +125^{o}C$       | -0.5                 | 1.0                  | V     |

| CLK Input HIGH Voltage                                | V <sub>IHC</sub>  | $V_{CC} = 5.5V$                                                                           | 1, 2, 3        | $-55^{o}C \leq T_{A} \leq +125^{o}C$       | 3.6                  | V <sub>CC</sub> +0.5 | V     |

| Output LOW Voltage                                    | V <sub>OL</sub>   | I <sub>OL</sub> = 2.0mA, V <sub>CC</sub> = 4.5V                                           | 1, 2, 3        | $-55^oC \le T_A \le +125^oC$               | -                    | 0.4                  | V     |

| Output HIGH Voltage                                   | V <sub>OH</sub>   | $I_{OH}$ = -2.0mA, $V_{CC}$ = 4.5V                                                        | 1, 2, 3        | $-55^{o}C \leq T_{A} \leq +125^{o}C$       | 3.0                  | -                    | V     |

|                                                       |                   | $I_{OH} = -100 \mu A, V_{CC} = 4.5 V$                                                     |                |                                            | V <sub>CC</sub> -0.4 | -                    | V     |

| Input Leakage Current                                 | lı<br>I           | $V_{IN} = GND \text{ or } V_{CC}, \\ V_{CC} = 5.5V, \\ Pins 29, 31, 57, 59, 61, \\ 63-64$ | 1, 2, 3        | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -10                  | 10                   | μA    |

| Input Sustaining Current<br>LOW                       | I <sub>BHL</sub>  | $V_{CC}$ = 4.5V and 5.5V,<br>$V_{IN}$ = 1.0V, Note 1                                      | 1, 2, 3        | $-55^{o}C \leq T_{A} \leq +125^{o}C$       | 38                   | 200                  | μA    |

| Input Sustaining Current<br>HIGH                      | I <sub>BHH</sub>  | V <sub>CC</sub> = 4.5V and 5.5V,<br>V <sub>IN</sub> = 3.0V, Note 2                        | 1, 2, 3        | $-55^{o}C \leq T_{A} \leq +125^{o}C$       | -50                  | -400                 | μΑ    |

| Input Sustaining Current<br>on BUSY and ERROR<br>Pins | I <sub>SH</sub>   | $V_{CC}$ = 4.5V and 5.5V<br>$V_{IN}$ = GND, Note 5                                        | 1, 2, 3        | $-55^{o}C \leq T_{A} \leq +125^{o}C$       | -30                  | -500                 | μA    |

| Output Leakage Current                                | Ι <sub>Ο</sub>    | $V_{O} = GND \text{ or } V_{CC}$<br>$V_{CC} = 5.5V,$<br>Pins 1, 7-8, 10-28, 32-34         | 1, 2, 3        | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ | -10                  | 10                   | μΑ    |

| Active Power Supply                                   | I <sub>CCOP</sub> | 80C286-10/883, Note 4                                                                     | 1, 2, 3        | $-55^{\circ}C \le T_A \le +125^{\circ}C$   | -                    | 185                  | mA    |

| Current                                               |                   | 80C286-12/883, Note 4                                                                     |                |                                            | -                    | 220                  | mA    |

| Standby Power<br>Supply Current                       | I <sub>CCSB</sub> | V <sub>CC</sub> = 5.5V, Note 3                                                            | 1, 2, 3        | $-55^oC \le T_A \le +125^oC$               | -                    | 5                    | mA    |

NOTES:

2.  $I_{BHL}$  should be measured after lowering V<sub>IN</sub> to GND and then raising to 1.0V on the following pins: 36-51, 66, 67.

3.  $I_{BHH}$  should be measured after raising  $V_{IN}$  to  $V_{CC}$  and then lowering to 3.0V on the following pins: 4-6, 36-51, 66-68.

4.  $I_{CCSB}$  should be tested with the clock stopped in phase two of the processor clock cycle.  $V_{IN} = V_{CC}$  or GND,  $V_{CC} = 5.5V$ , outputs unloaded.

5.  $I_{CCOP}$  measured at 10MHz for the 80C286-10/883 and 12.5MHz for the 80C286-12/883.  $V_{IN}$  = 2.4V or 0.4V,  $V_{CC}$  = 5.5V, outputs unloaded.

6.  $I_{SH}$  should be measured after raising  $V_{IN}$  to  $V_{CC}$  and then lowering to 0V on pins 53 and 54.

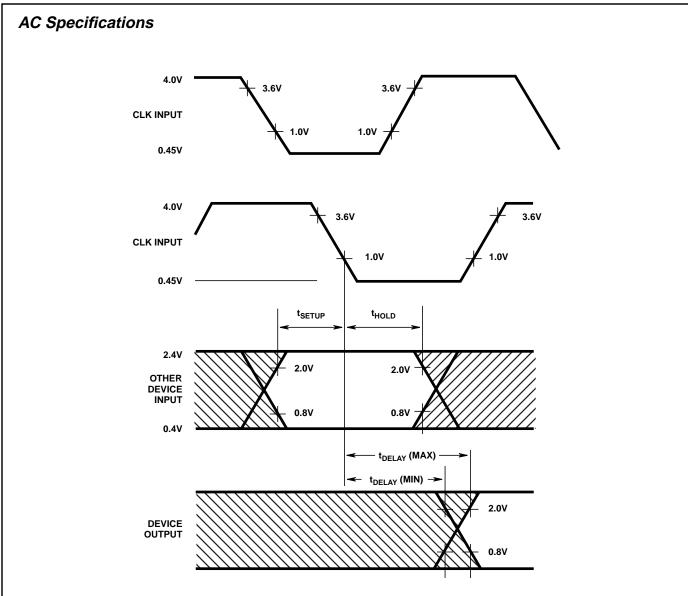

### TABLE 2. 80C286/883 AC ELECTRICAL PERFORMANCE SPECIFICATIONS

AC Timings are Referenced to 0.8V and 2.0V Points of the Signals as Illustrated in Datasheet Waveforms, Unless Otherwise Noted. Device Guaranteed and 100% Tested.

|                                               |        |                                                                                     |                      |                                                    |     | 80C28 | 36/883 |     |       |

|-----------------------------------------------|--------|-------------------------------------------------------------------------------------|----------------------|----------------------------------------------------|-----|-------|--------|-----|-------|

|                                               |        |                                                                                     |                      |                                                    | 10  | ЛНz   | 12.5   | MHz |       |

| PARAMETER                                     | SYMBOL | CONDITIONS                                                                          | GROUP A<br>SUBGROUPS | TEMPERATURE                                        | MIN | MAX   | MIN    | MAX | UNITS |

| System Clock<br>(CLK) Period                  | 1      | $V_{CC}$ = 4.5V and 5.5V                                                            | 9, 10, 11            | $-55^{o}C \leq T_{A} \leq +125^{o}C$               | 50  | -     | 40     | -   | ns    |

| System Clock<br>(CLK) Low Time                | 2      | V <sub>CC</sub> = 4.5V and 5.5V<br>at 1.0V                                          | 9, 10, 11            | $-55^{o}C \leq T_{A} \leq +125^{o}C$               | 12  | -     | 11     | -   | ns    |

| System Clock (CLK)<br>High Time               | 3      | V <sub>CC</sub> = 4.5V and 5.5V<br>at 3.6V                                          | 9, 10, 11            | $-55^{\circ}C \le T_A \le +125^{\circ}C$           | 16  | -     | 13     | -   | ns    |

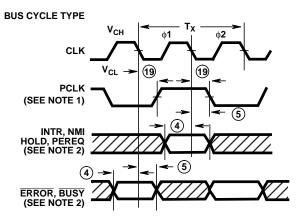

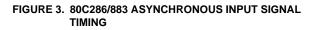

| Asynchronous Inputs<br>SETUP Time<br>(Note 1) | 4      | V <sub>CC</sub> = 4.5V<br>and 5.5V                                                  | 9, 10, 11            | $\text{-55}^{o}C \leq T_A \leq +125^{o}C$          | 20  | -     | 15     | -   | ns    |

| Asynchronous Inputs<br>HOLD Time<br>(Note 1)  | 5      | V <sub>CC</sub> = 4.5V<br>and 5.5V                                                  | 9, 10, 11            | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$         | 20  | -     | 15     | -   | ns    |

| RESET SETUP Time                              | 6      | V <sub>CC</sub> = 4.5V<br>and 5.5V                                                  | 9, 10, 11            | $-55^{\circ}C \le T_A \le +125^{\circ}C$           | 19  | -     | 10     | -   | ns    |

| RESET HOLD Time                               | 7      | V <sub>CC</sub> = 4.5V<br>and 5.5V                                                  | 9, 10, 11            | $-55^{\circ}C \le T_A \le +125^{\circ}C$           | 0   | -     | 0      | -   | ns    |

| Read Data<br>SETUP Time                       | 8      | V <sub>CC</sub> = 4.5V<br>and 5.5V                                                  | 9, 10, 11            | $-55^{\circ}C \le T_A \le +125^{\circ}C$           | 8   | -     | 5      | -   | ns    |

| Read Data<br>HOLD Time                        | 9      | V <sub>CC</sub> = 4.5V<br>and 5.5V                                                  | 9, 10, 11            | $-55^{\circ}C \le T_A \le +125^{\circ}C$           | 4   | -     | 4      | -   | ns    |

| READY SETUP Time                              | 10     | V <sub>CC</sub> = 4.5V<br>and 5.5V                                                  | 9, 10, 11            | $-55^{\circ}C \le T_A \le +125^{\circ}C$           | 26  | -     | 20     | -   | ns    |

| READY HOLD Time                               | 11     | V <sub>CC</sub> = 4.5V<br>and 5.5V                                                  | 9, 10, 11            | $-55^{o}C \leq T_{A} \leq +125^{o}C$               | 25  | -     | 20     | -   | ns    |

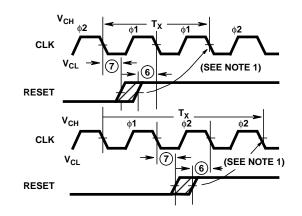

| Status/PEACK Active<br>Delay, (Note 4)        | 12A    | V <sub>CC</sub> = 4.5V and<br>5.5V, C <sub>L</sub> = 100pF<br>I <sub>L</sub> =  2mA | 9, 10, 11            | $\text{-55}^{o}C \leq T_A \leq +125^{o}C$          | 1   | 22    | 1      | 21  | ns    |

| Status/PEACK<br>Inactive Delay<br>(Note 3)    | 12B    | $V_{CC} = 4.5V$ and<br>5.5V, $C_{L} = 100pF$<br>$I_{L} =  2mA $                     | 9, 10, 11            | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$         | 1   | 30    | 1      | 24  | ns    |

| Address Valid<br>Delay (Note 2)               | 13     | V <sub>CC</sub> = 4.5V and<br>5.5V, C <sub>L</sub> = 100pF<br>I <sub>L</sub> =  2mA | 9, 10, 11            | $\text{-55}^{o}C \leq T_{A} \leq \text{+125}^{o}C$ | 1   | 35    | 1      | 32  | ns    |

| Write Data<br>Valid Delay, (Note 2)           | 14     | V <sub>CC</sub> = 4.5V and<br>5.5V, C <sub>L</sub> = 100pF<br>I <sub>L</sub> =  2mA | 9, 10, 11            | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$         | 0   | 40    | 0      | 31  | ns    |

#### TABLE 2. 80C286/883 AC ELECTRICAL PERFORMANCE SPECIFICATIONS (Continued)

AC Timings are Referenced to 0.8V and 2.0V Points of the Signals as Illustrated in Datasheet Waveforms, Unless Otherwise Noted. Device Guaranteed and 100% Tested.

|                              |        |                                                                         |           |                                      |     | 80C28 | 86/883 |     |       |

|------------------------------|--------|-------------------------------------------------------------------------|-----------|--------------------------------------|-----|-------|--------|-----|-------|

|                              |        |                                                                         | GROUP A   |                                      | 101 | /Hz   | 12.5   | MHz |       |

| PARAMETER                    | SYMBOL | CONDITIONS                                                              | SUBGROUPS | TEMPERATURE                          | MIN | MAX   | MIN    | MAX | UNITS |

| HLDA Valid Delay<br>(Note 5) | 15     | V <sub>CC</sub> = 4.5V and<br>5.5V, C <sub>L</sub> = 100pF<br>IL =  2mA | 9, 10, 11 | $-55^{o}C \leq T_{A} \leq +125^{o}C$ | 0   | 47    | 0      | 25  | ns    |

NOTES:

1. Asynchronous inputs are INTR, NMI, HOLD, PEREQ, ERROR, and BUSY. This specification is given only for testing purposes, to assure recognition at a specific CLK edge.

- 2. Delay from 1.0V on the CLK to 0.8V or 2.0V.

- 3. Delay from 1.0V on the CLK to 0.8V for Min (HOLD time) and to 2.0V for Max (inactive delay).

- 4. Delay from 1.0V on the CLK to 2.0V for Min (HOLD time) and to 0.8V for Max (active delay).

- 5. Delay from 1.0V on the CLK to 2.0V.

|  | TABLE 3. | 80C286/883 ELECTRICAL | PERFORMANCE SPECIFICATIONS | 3 |

|--|----------|-----------------------|----------------------------|---|

|--|----------|-----------------------|----------------------------|---|

|                                       |                  |                         |            |                                              | 80C |     | 36/883 |     |       |

|---------------------------------------|------------------|-------------------------|------------|----------------------------------------------|-----|-----|--------|-----|-------|

|                                       |                  |                         |            |                                              | 101 | ЛНz | 12.5   | MHz |       |

| PARAMETER                             | SYMBOL           | CONDITIONS              | NOTES      | TEMPERATURE                                  | MIN | MAX | MIN    | MAX | UNITS |

| CLK Input Capacitance                 | C <sub>CLK</sub> | FREQ = 1MHz             | 5          | T <sub>A</sub> = +25 <sup>o</sup> C          | -   | 10  | -      | 10  | pF    |

| Other Input Capacitance               | C <sub>IN</sub>  | FREQ = 1MH              | 5          | T <sub>A</sub> = +25°C                       | -   | 10  | -      | 10  | pF    |

| I/O Capacitance                       | C <sub>I/O</sub> | FREQ = 1MH              | 5          | T <sub>A</sub> = +25 <sup>o</sup> C          | -   | 10  | -      | 10  | pF    |

| Address/Status/Data<br>Float Delay    | 15               |                         | 1, 3, 4, 5 | $-55^{\circ}C \leq T_{A} \leq +125^{\circ}C$ | 0   | 47  | 0      | 32  | ns    |

| Address Valid to Status<br>SETUP Time | 19               | I <sub>L</sub> =  2.0mA | 1, 2, 5    | $-55^{o}C \leq T_{A} \leq +125^{o}C$         | 27  | -   | 20     | -   | ns    |

NOTES:

1. Output Load:  $C_L = 100 pF$ .

2. Delay measured from address either reaching 0.8V or 2.0V (valid) to status going active reaching 0.8V or status going inactive reaching 2.0V.

- 3. Delay from 1.0V on the CLK to Float (no current drive) condition.

- 4.  $I_L = -6mA$  (V<sub>OH</sub> to Float),  $I_L = 8mA$  (V<sub>OL</sub> to Float).

- 5. The parameters listed in Table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design and after major process and/or design changes.

| TABLE 4. | APPLICABLE | SUBGROUPS |

|----------|------------|-----------|

|----------|------------|-----------|

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |  |  |

|--------------------|--------------|-------------------------------|--|--|

| Initial Test       | 100%/5004    | -                             |  |  |

| Interim Test       | 100%/5004    | 1, 7, 9                       |  |  |

| PDA                | 100%         | 1                             |  |  |

| Final Test         | 100%         | 2, 3, 8A, 8B, 10, 11          |  |  |

| Group A            | -            | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |  |  |

| Group C & D        | Samples/5005 | 1, 7, 9                       |  |  |

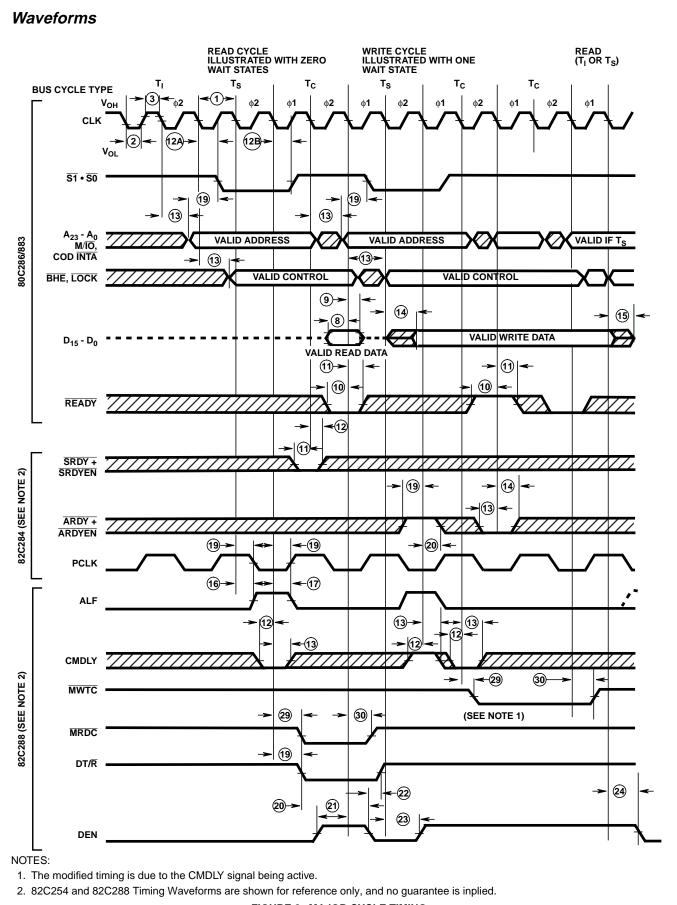

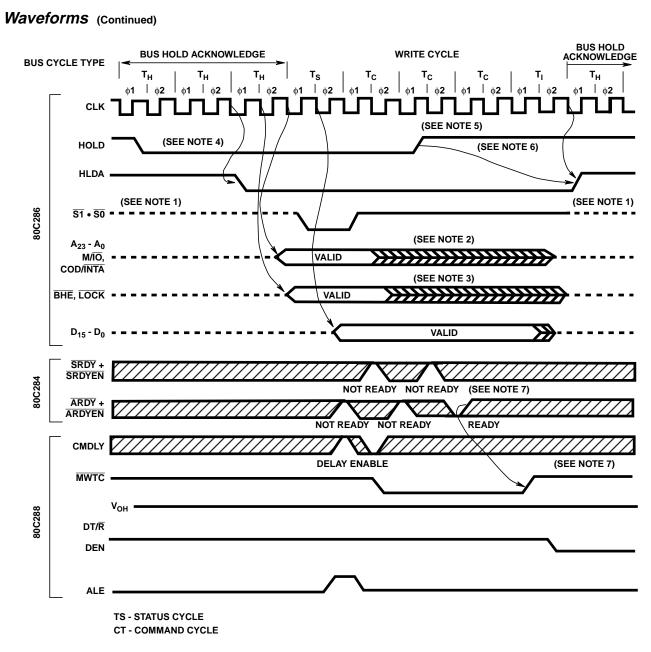

AC Electrical Specifications 82C284 and 82C288 Timing Specifications Are Given For Reference Only, And No Guarantee is Implied.

## 82C284 Timing

|                     |                        | 10MHz |     | 12.5MHz |     |      |                                                                         |

|---------------------|------------------------|-------|-----|---------|-----|------|-------------------------------------------------------------------------|

| SYMBOL              | PARAMETER              | MIN   | МАХ | MIN     | MAX | UNIT | TEST CONDITION                                                          |

| TIMING REQUIREMENTS |                        |       |     |         |     |      |                                                                         |

| 11                  | SRDY/SRDYEN Setup Time | 15    | -   | 15      | -   | ns   |                                                                         |

| 12                  | SRDY/SRDYEN Hold Time  | 2     | -   | 2       | -   | ns   |                                                                         |

| 13                  | ARDY/ARDYEN Setup Time | 5     | -   | 5       | -   | ns   | (Note 1)                                                                |

| 14                  | ARDY/ARDYEN Hold Time  | 30    | -   | 25      | -   | ns   | (Note 1)                                                                |

| TIMING RESPONSES    |                        |       |     |         |     |      | •                                                                       |

| 19                  | PCLK Delay             | 0     | 20  | 0       | 16  | ns   | C <sub>L</sub> = 75pF, I <sub>OL</sub> = 5mA,<br>I <sub>OH</sub> = -1mA |

NOTE:

1. These times are given for testing purposes to ensure a predetermined action.

## 82C288 Timing

|           |                                       | 10  | ИНz | 12.5 | MHz |      |                            |

|-----------|---------------------------------------|-----|-----|------|-----|------|----------------------------|

| SYMBOL    | PARAMETER                             | MIN | MAX | MIN  | MAX | UNIT | TEST CONDITION             |

| TIMING RE | QUIREMENTS                            |     |     |      |     |      |                            |

| 12        | CMDLY Setup Time                      | 15  | -   | 15   | -   | ns   |                            |

| 13        | CMDLY Hold Time                       | 1   | -   | 1    | -   | ns   |                            |

| TIMING RE | SPONSES                               |     |     |      |     |      | •                          |

| 16        | ALE Active Delay                      | 1   | 16  | 1    | 16  | ns   |                            |

| 17        | ALE Inactive Delay                    | -   | 19  | -    | 19  | ns   |                            |

| 19        | $DT/\overline{R}$ Read Active Delay   | -   | 23  | -    | 23  | ns   | C <sub>L</sub> = 150pF     |

| 20        | DEN Read Active Delay                 | 0   | 21  | 0    | 21  | ns   | I <sub>OL</sub> = 16mA Max |

| 21        | DEN Read Inactive Delay               | 3   | 23  | 3    | 21  | ns   | I <sub>OH</sub> = -1mA Max |

| 22        | $DT/\overline{R}$ Read Inactive Delay | 5   | 24  | 5    | 18  | ns   |                            |

| 23        | DEN Write Active Delay                | -   | 23  | -    | 23  | ns   |                            |

| 24        | DEN Write Inactive Delay              | 3   | 23  | 3    | 23  | ns   |                            |

| 29        | Command Active Delay from CLK         | 3   | 21  | 3    | 21  | ns   | C <sub>L</sub> = 300pF     |

| 30        | Command Inactive Delay from CLK       | 3   | 20  | 3    | 20  | ns   | I <sub>OL</sub> = 32mA Max |

NOTE:

1. For AC testing, input rise and fall times are driven at 1ns per volt.

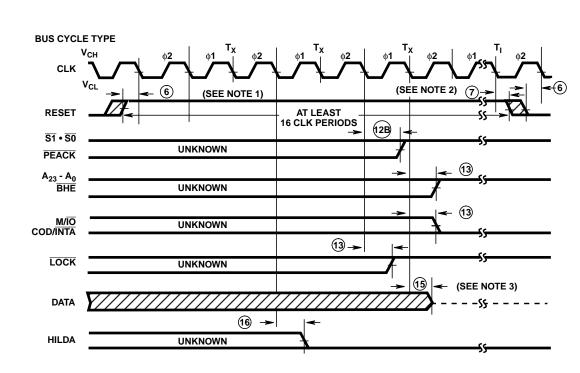

FIGURE 2. MAJOR CYCLE TIMING

## Waveforms (Continued)

#### NOTES:

- 1. PCLK indicates which processor cycle phase will occur on the next CLK. PCLK may not indicate the correct phase until the first cycle is performed.

- 2. These inputs are asynchronous. The setup and hold times shown assure recognition for testing purposes.

#### NOTE:

When RESET meets the setup time shown, the next CLK will start or repeat φ1 of a processor cycle.

#### FIGURE 4. 80C286/883 RESET INPUT TIMING AND SUBSE-QUENT PROCESSOR CYCLE PHASE

#### NOTES:

- 1. These signals may not be driven by the 80C286/883 during the time shown. The worst case in terms of latest float time is shown.

- 2. The data bus will be driven as shown if the last cycle before  $T_{\rm I}$  in the diagram was a write  $T_{\rm C}.$

- 3. The 80C286/883 puts its status pins in a high impedance logic one state during  $\rm T_{\rm H}.$

- 4. For HOLD request set up to HLDA, refer to Figure 8.

- 5.  $\overline{\text{BHE}}$  and  $\overline{\text{LOCK}}$  are driven at this time but will not become valid until  $\text{T}_{\text{S}}.$

- 6. The data bus will remain in a high impedance state if a read cycle is performed.

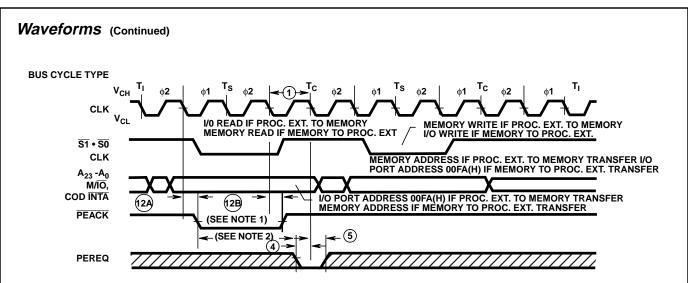

#### FIGURE 5. EXITING AND ENTERING HOLD

#### NOTES:

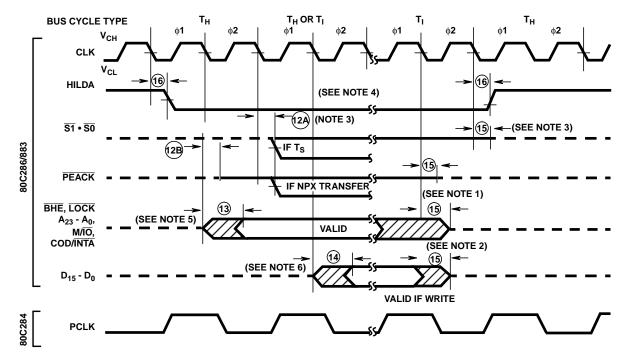

- 1. PEACK always goes active during the first bus operation of a processor extension data operand transfer sequence. The first bus operation will be either a memory read at operand address or I/O read at port address 00FA(H).

- 2. To prevent a second processor extension data operand transfer, the worst case maximum time (shown above) is 3 x (1 12A<sub>MAX</sub> (4)<sub>MIN</sub> The actual, configuration dependent, maximum time is: 3 x (1) 12A<sub>MAX</sub> (<sup>4)</sup><sub>MIN</sub> +N x 2 x (<sup>1</sup>). N is the number of extra T<sub>C</sub> states added to either the first or second bus operation of the processor extension data operand transfer sequence.

#### FIGURE 6. 80C286/883 PEREQ/PEACK TIMING FOR ONE TRANSFER ONLY

#### NOTES:

- 1. Setup time for RESET  $\uparrow$  may be violated with the consideration that  $\phi$ 1 of the processor clock may begin one system CLK period later.

- 2. Setup and hold times for RESET  $\downarrow$  must be met for proper operation, but RESET  $\downarrow$  may occur during  $\phi$ 1 or  $\phi$ 2.

- 3. The data bus is only guaranteed to be in a high impedance state at the time shown.

## FIGURE 7. INITIAL 80C286/883 PIN STATE DURING RESET

NOTES:

- 1. Status lines are held at a high impedance logic one by the 80C286 during a HOLD state.

- 2. Address, M/ $\overline{IO}$  and COD/ $\overline{INTA}$  may start floating during any T<sub>C</sub> depending on when internal 80C286 bus arbiter decides to release bus to external HOLD. The float starts in  $\phi$ 2 of T<sub>C</sub>.

- 3. BHE and LOCK may start floating after the end of any T<sub>C</sub> depending on when internal 80C286 bus arbiter decides to release bus to external HOLD. The float starts in  $\phi$ 1 of T<sub>C</sub>.

- 4. The minimum HOLD to HLDA time is shown. Maximum is one  $\rm T_{\rm H}$  longer.

- 5. The earliest HOLD time is shown. It will always allow a subsequent memory cycle if pending is shown.

- 6. The minimum HOLD to HLDA time is shown. Maximum is a function of the instruction, type of bus cycle and other machine state (i.e., Interrupts, Waits, Lock, etc.).

- 7. Asynchronous ready allows termination of the cycle. Synchronous ready does not signal ready in this example. Synchronous ready state is ignored after ready is signaled via the asynchronous input.

#### FIGURE 8. MULTIBUS WRITE TERMINATED BY ASYNCHRONOUS READY WITH BUS HOLD

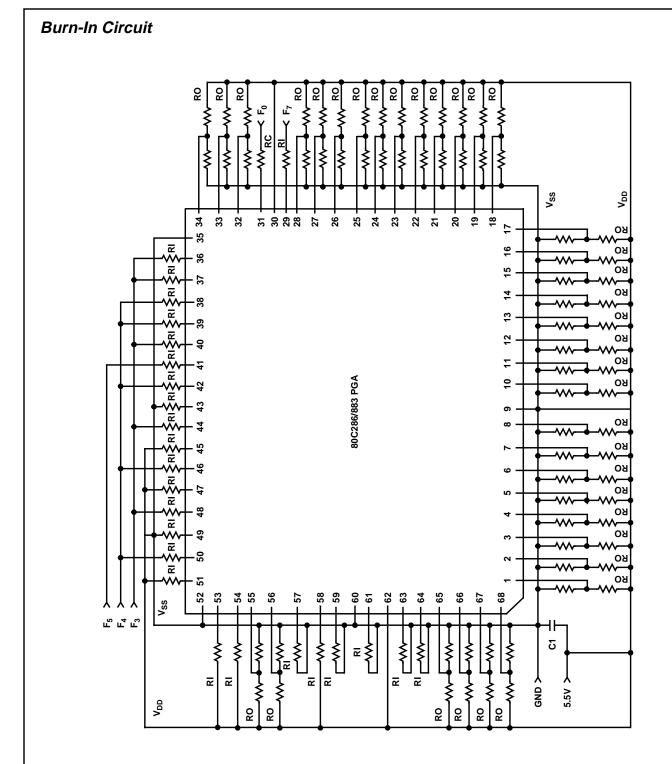

#### NOTES:

- 8. Supply Voltage:  $V_{DD}$  = 5.5V,  $V_{SS}$  = 0.0V.

- 9. Input Voltage Limits:  $V_{IL}$  (Maximum) = 0.8V,  $V_{IH}$  (Minimum) = 2.0V

- 10. Component Values: RC = 1k $\Omega$  ±5%, RI = 10k $\Omega$  ±5%, RO = Two Series 2.7k $\Omega$  ±5%

- 11. Capacitor Values: C1 = 0.1 Microfarads

- 12. Oven Type and Frequency Requirements: Wakefield Oven Board  $f_0 = 100$ kHz,  $f_3 = 12.5$ kHz,  $f_4 = 6.25$ kHz,  $f_5 = 3.125$ kHz,  $f_7 = 781.25$ Hz.

- 13. Special Requirements: (a) ELECTROSTATIC DISCHARGE SENSITIVE. Proper Precautions Must be Used When Handling Units. (b) All Power Supplies Must be at Zero Volts When the Boards are Inserted into the Ovens. (c) When Powering Up, the Inputs Must be Held Below the V<sub>DD</sub> Voltage. (d) If an Excessive Current is Indicated at Final Inspection, Check to See if a Part is Inserted Backwards or is Latched Up.

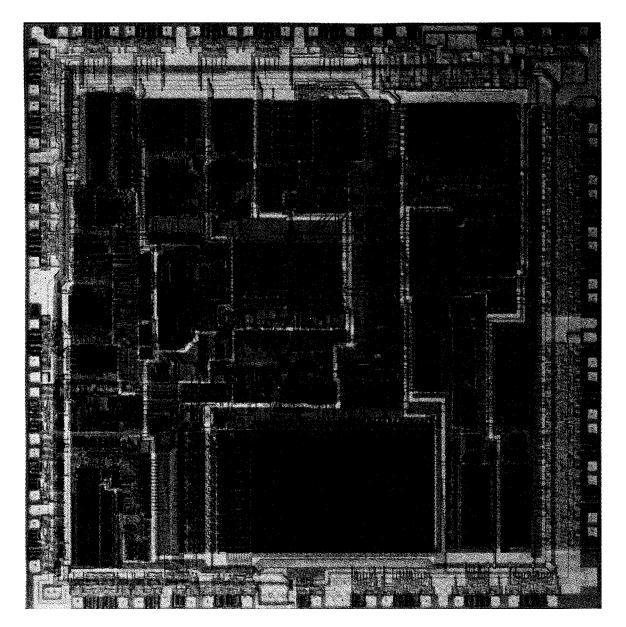

## **Die Characteristics**

## DIE DIMENSIONS:

286 x 283 x 19 ±1mils

## METALLIZATION:

Type: Si-Al Thickness: 8kÅ

## Metallization Mask Layout

GLASSIVATION: Type: Nitrox Thickness: 10kÅ

WORST CASE CURRENT DENSITY: 2 X 10<sup>5</sup>A/cm<sup>2</sup>

LEAD TEMPERATURE: (10s Soldering):  $\leq 300^{\circ}$ C

80C286/883

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com