# **IM6100 CMOS 12 Bit Microprocessor**

### **FEATURES**

- Silicon Gate Complementary MOS

- Fully Static 0 to 5.7 MHz

- Single Power Supply IM6100  $V_{CC} = 5$  volts IM6100A  $V_{CC} = 10$  volts

- Crystal Controlled On Chip Timing

- PDP®-8/e, Instruction Set Compatible

- Low Power Dissipation

- < 10mW @ 3.3 MHz @ 5 volts

- TTL Compatible at 5 volts

- Excellent Noise Immunity

- **Direct Memory Access (DMA)**

- Interrupt

### **GENERAL DESCRIPTION**

The IM6100 is a fixed word length, single word instruction, parallel transfer microprocessor using 12-bit, two's complement arithmetic which recognizes the instruction set of Digital Equipment Corporation's PDP-8/e minicomputer. The internal circuitry is completely static and designed to operate at any speed between DC and the maximum operating frequency. Two pins are available to allow for an external crystal, thereby eliminating the need for clock generators and level translators. The crystal can be removed and the processor clocked by an external clock generator. The device design is optimized to minimize the number of external components required for interfacing with standard memory and peripheral devices.

The IM6100 family includes IM6101 (Programmable Interfacing Element), IM6102 (Memory Extension/DMA Control-Jer/Interval Timer), IM6103 (Parallel Input-Output Port), IM6512 (64 x 12 RAM), IM6312 (1k x 12 ROM), and IM6402/03 (UART), all featuring ultra low power-high noise immunity CMOS characteristics. The entire family is supported by the 6910 Intercept II Microcomputer Development System.

PDP-8 is a registered trademark of Digital Electronics Corp.

8-33

### IM6100

# **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature   |                                |

|-------------------------|--------------------------------|

| Industrial IM6100       | 45°C to +85°C                  |

| Charage Temperature     | -65°C to +150°C                |

| Storage remperature     | 14 0V to ±11 0V                |

| Operating Voltage       | +4.0V to +11.0V                |

| Supply Voltage          | +12.0V                         |

| Voltage On Any Input or |                                |

| Output Pin              | -0.3V to V <sub>CC</sub> +0.3V |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures. extended periods may cause device failures.

### D.C. CHARACTERISTICS

TEST CONDITIONS: VCC = 5.0V  $\pm 10\%$ , TA = -40°C to +85°C

|           |        | DAGAMETER                    | CONDITIONS                              | MIN     | TYP | MAX      | UNITS       |

|-----------|--------|------------------------------|-----------------------------------------|---------|-----|----------|-------------|

|           | SYMBOL | PARAMETER                    | CONDITIONS                              | Vcc-2.0 |     |          | V           |

| 1         | ViH    | Input Voltage High           |                                         | VCC-2.0 |     | 0.8      | V           |

| 2         | VIL    | Input Voltage Low            |                                         |         |     |          | <del></del> |

| 3         | lin.   | Input Leakage                | GND ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> | -1.0    |     | 1.0      | μΑ          |

| <u> </u>  |        | Output Voltage High          | I <sub>OH</sub> = -0.2mA                | 2.4     |     | <u> </u> | V           |

| 4         | Vон    |                              | IoL = 2.0mA                             |         |     | 0.45     | l v         |

| 5         | Vol    | Output Voltage Low           |                                         | 10      |     | 1.0      | μΑ          |

| 6         | IOLK   | Output Leakage               | GND ≤ Vout ≤ Vcc                        | -1.0    |     |          |             |

| 7         | Icc    | Power Supply Current-Standby | V <sub>IN</sub> = GND or Vcc            |         |     | 800      | μΑ          |

| <u>'-</u> |        | Power Supply Current-Dynamic | $f_C = 2.5MHz$                          |         |     | 1.8      | mA_         |

| 8         | lcc    |                              | 10                                      |         | 7.0 | 8.0      | pF          |

| 9         | CIN    | Input Capacitance            |                                         |         |     | 10.0     | pF          |

| 10        | Co     | Output Capacitance           |                                         |         | 8.0 | 10.0     |             |

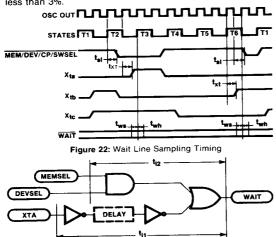

# A.C. CHARACTERISTICS (See Figure 2 and 22)

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $C_L = 50 pF$ ,  $T_A - 40^{\circ}C$  to  $+85^{\circ}C$ ,  $f_C = 2.5 MHz$

|    | SYMBOL             | PARAMETER                                                  | MIN | TYP          | MAX          | UNITS       |

|----|--------------------|------------------------------------------------------------|-----|--------------|--------------|-------------|

|    |                    | Operating Frequency                                        |     |              | 2.5          | MHz         |

| _1 | t <sub>op</sub>    |                                                            | 800 |              |              | ns          |

| 2  | ts                 | Major State Time                                           | 335 |              |              | ns          |

| 3  | t <sub>ixmar</sub> | LXMAR Pulse Width                                          | 120 |              | 1            | ns          |

| 4  | t <sub>as</sub>    | Address Setup Time : DX-LXMAR (4)                          | 175 | -            |              | ns          |

| 5  | <sup>t</sup> ah    | Address Hold Time: LXMAR (+)-DX                            | 1/3 | <del> </del> | 575          | ns          |

| 8  | t <sub>end</sub>   | Data Output Enable Time: DEVSEL (+)-DX                     |     |              |              | ns          |

| 6  | t <sub>al</sub>    | Access Time from LXMAR                                     |     |              | 650          |             |

| 7  | t <sub>en</sub>    | Output Enable Time (MEM, CP, DEVSEL)                       |     | L            | 400          | ns          |

| 9  | two                | Pulse Width (MEMSEL, CPSEL)                                | 320 | <u> </u>     |              | ns          |

| 10 | t <sub>wpd</sub>   | Pulse Width (DEVSEL)                                       | 320 |              |              | ns          |

| 11 | t <sub>ds</sub>    | Data Setup Time (DX- + MEMSEL/CPSEL)                       | 240 |              |              | ns          |

| 12 | t <sub>dh</sub>    | Data Hold Time (+ MEMSEL/CPSEL-DX)                         | 175 | L            |              | ns          |

| 13 | t <sub>dsd</sub>   | Data Setup Time (DX-+ DEVSEL)                              | 275 |              | <u> </u>     | ns          |

|    | tdhd               | Data Hold Time (* DEVSEL-DX)                               | 175 |              | L            | ns          |

| 14 | t <sub>sl</sub>    | Logic Delay to MEM/DEV/CP/SWSEL                            | 75  |              | 440          | ns          |

| 15 |                    | Logic Delay to LXMAR, XTA, XTB, XTC                        | 65  |              | 380          | ns          |

| 16 | t <sub>xt</sub>    | Logic Delay to DATAF, RUN, DMAGNT, INTGNT, LINK, IFETCH    |     | 1            | 475          | ns          |

| 17 | t <sub>st</sub>    | Logic Delay to DATAF, HON, DMAGNT, INTGITT, EINK, II ET OT | 0   | +            | +            | ns          |

| 18 | t <sub>rs</sub>    | Set up Time for CP/INT/DMAREQ                              | 300 | +            | <del>†</del> | ns          |

| 19 | t <sub>rh</sub>    | Hold Time for CP/INT/DMAREQ, RESET, RUN-HALT               |     | +            | +            | ns          |

| 20 | t <sub>rhp</sub>   | RUN-HALT Pulse Width                                       | 110 | +            | +            | <del></del> |

| 21 | tws                | Set up Time for Wait                                       | 100 | +            |              | ns          |

| 22 | t <sub>wh</sub>    | Hold Time for Wait                                         | 35  |              |              | ns          |

Note: For capacitance greater than 50pF, the AC parameters will have a delay factor of 0.5ns/pF.

INTERSIL

### IM6100

### IM6100A ABSOLUTE MAXIMUM RATINGS

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

### D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC}=10V~\pm5\%,~T_A=-40^{\circ}C~to~+85^{\circ}C$

|    | SYMBOL | PARAMETER                    | CONDITIONS                              | MIN                                              | TYP | MAX         | UNITS |

|----|--------|------------------------------|-----------------------------------------|--------------------------------------------------|-----|-------------|-------|

|    |        | Input Voltage High           |                                         | 70% Vcc                                          |     |             |       |

| 1  | ViH    |                              |                                         |                                                  |     | 20% Vcc     | V     |

| 2  | VIL    | Input Voltage Low            |                                         | <del> </del>                                     |     | 1.0         | μА    |

| 3  | . IIL  | Input Leakage                | GND ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> | -1.0                                             |     | 1.0         | μΑ    |

| 4  | Voн    | Output Voltage High          | $I_{OH} = 0.0 mA$                       | V <sub>CC</sub> -0.01                            |     | <del></del> | V     |

| 5  | VoL    | Output Voltage Low           | $I_{OL} = 0.0 \text{mA}$                |                                                  |     | GND +0.01   | V     |

| 6  | lork   | Output Leakage               | GND ≤ Vout ≤ Vcc                        | -1.0                                             |     | 1.0         | μΑ    |

| 7  | Icc    | Power Supply Current-Standby | V <sub>IN</sub> = GND or Vcc            |                                                  |     | 900         | μΑ    |

|    |        | Power Supply Current-Dynamic | f <sub>C</sub> = 5.71MHz                |                                                  |     | 4.0         | mA_   |

|    | lcc    |                              |                                         |                                                  | 7.0 | 8.0         | pF    |

| 9  | Cin    | Input Capacitance            |                                         | <del>                                     </del> | 8.0 | 10.0        | pF    |

| 10 | Co     | Output Capacitance           |                                         | <u> </u>                                         | 0.0 |             | P1    |

# A.C. CHARACTERISTICS (Ref: Figures 2 and 22)

TEST CONDITIONS:  $V_{CC}=10V\pm5\%$ ,  $C_L=50pF$ ,  $T_A=-40^{\circ}C$  to  $+85^{\circ}C$ ,  $f_C=5.71MHz$

|    | SYMBOL             | PARAMETER                                               | MIN | TYP          | MAX                                               | UNITS |

|----|--------------------|---------------------------------------------------------|-----|--------------|---------------------------------------------------|-------|

|    |                    | Operating Frequency                                     |     |              | 5.71                                              | MHz   |

| 1  | fop                |                                                         | 350 |              |                                                   | ns    |

| 2  | t <sub>s</sub>     | Major State Time                                        | 150 |              |                                                   | ns    |

| 3  | t <sub>lxmar</sub> | LXMAR Pulse Width                                       | 55  | i            |                                                   | ns    |

| 4  | t <sub>as</sub>    | Address Setup Time : DX-LXMAR (4)                       | 60  | <del> </del> | <del>                                      </del> | ns    |

| 5  | tah                | Address Hold Time : LXMAR (I)-DX                        |     | <del></del>  | 250                                               | ns    |

| 8  | tend               | Data Output Enable Time: DEVSEL (4)-DX                  |     | <del></del>  | 295                                               | ns    |

| 6  | tat                | Access Time from LXMAR                                  |     |              |                                                   |       |

| 7  | t <sub>en</sub>    | Output Enable Time (MEM, CP, DEVSEL)                    |     | L            | 185                                               | ns    |

| 9  | twp                | Pulse Width (MEMSEL, CPSEL)                             | 140 |              |                                                   | ns    |

| 10 | twpd               | Pulse Width (DEVSEL)                                    | 140 |              |                                                   | ns    |

| 11 | t <sub>ds</sub>    | Data Setup Time (DX- † MEMSEL/CPSEL)                    | 115 |              | <u> </u>                                          | ns    |

| 12 | t <sub>dh</sub>    | Data Hold Time ( † MEMSEL/CPSEL-DX)                     | 60  |              | ļ                                                 | ns    |

| 13 | t <sub>dsd</sub>   | Data Setup Time (DX- + DEVSEL)                          | 110 |              | <u> </u>                                          | ns    |

| 14 | t <sub>dhd</sub>   | Data Hold Time ( + DEVSEL-DX)                           | 60  | ļ            | <u> </u>                                          | ns    |

| 15 | t <sub>sl</sub>    | Logic Delay to MEM/DEV/CP/SWSEL                         | 35  |              | 180.                                              | ns    |

| 16 | t <sub>xt</sub>    | Logic Delay to LXMAR, XTA, XTB, XTC                     | 35  |              | 155                                               | ns    |

| 17 | t <sub>st</sub>    | Logic Delay to DATAF, RUN, DMAGNT, INTGNT, LINK, IFETCH |     |              | 190                                               | ns    |

| 18 | t <sub>rs</sub>    | Set up Time for CP/INT/DMAREQ                           | 0   |              |                                                   | ns    |

| 19 | t <sub>rh</sub>    | Hold Time for CP/INT/DMAREQ, RESET, RUN-HALT            | 125 |              |                                                   | ns    |

| 20 | t <sub>rhp</sub>   | RUN-HALT Pulse Width                                    | 45  |              |                                                   | ns    |

| 21 | tws                | Set up Time for Wait                                    | 45  |              | ļ                                                 | ns    |

| 22 | t <sub>wh</sub>    | Hold Time for Wait                                      | 15  |              | <u></u>                                           | ns    |

Note: For capacitance greater than 50pF, the AC parameters will have a delay factor of 0.5ns/pF.

8-35

IM6100 INTERSIL

# IM6100AM (Military) ABSOLUTE MAXIMUM RATINGS

Operating Temperature

Industrial IM6100AM -55°C to +125°C

Storage Temperature -65°C to +150°C

Operating Voltage +4.0V to +11.0V

Supply Voltage +12.0V

Voltage On Any Input or

Output Pin -0.3V to Vcc +0.3V

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

### D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 10V \pm 5\%$ ,  $T_A = -55$ °C to  $\pm 125$ °C

| - 1           | SYMBOL          | PARAMETER                    | CONDITIONS                               | MIN                                              | TYP | MAX                                    | UNITS    |

|---------------|-----------------|------------------------------|------------------------------------------|--------------------------------------------------|-----|----------------------------------------|----------|

| $\rightarrow$ |                 |                              |                                          | 70% Vcc                                          |     |                                        | V        |

| 1             | ViH             | Input Voltage High           |                                          | 7070 100                                         |     | 20% Vcc                                | V        |

| 2             | VIL             | Input Voltage Low            |                                          | <del>                                     </del> |     | 1.0                                    |          |

| 3             | T <sub>IL</sub> | Input Leakage                | GND ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>  | -1.0                                             |     | 1.0                                    | μA       |

| 4             | VoH             | Output Voltage High          | $I_{OH} = 0.0 \text{mA}$                 | V <sub>CC</sub> -0.01                            |     |                                        | <u>V</u> |

| 5             | Vol             | Output Voltage Low           | I <sub>OL</sub> = 0.0mA                  | l                                                |     | GND +0.01                              | V        |

| 6             | JOLK            | Output Leakage               | GNĐ ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub> | -1.0                                             |     | 1.0                                    | μA       |

| 7             | Icc             | Power Supply Current-Standby | V <sub>IN</sub> = GND or V <sub>CC</sub> |                                                  |     | 900                                    | μΑ       |

| 'n            | lcc             | Power Supply Current-Dynamic | f <sub>C</sub> = 5.0MHz                  |                                                  |     | 4.0                                    | mA       |

| ~             |                 | Input Capacitance            |                                          |                                                  | 7.0 | 8.0                                    | pF_      |

| 9             | Cin             |                              |                                          |                                                  | 8.0 | 10.0                                   | pF       |

| 10            | Co              | Output Capacitance           | <u> </u>                                 |                                                  | 5.0 | لـــــــــــــــــــــــــــــــــــــ |          |

### A.C. CHARACTERISTICS (Ref.: Figures 2 and 22)

TEST CONDITIONS: V<sub>CC</sub> = 10V  $\pm$  5%,  $\stackrel{-}{C_L}$  = 50pF, T<sub>A</sub> = -55°C to +125°C, f<sub>C</sub> = 5.0MHz

|     | SYMBOL             | PARAMETER                                               | MIN | TYP | MAX                                               | UNITS       |

|-----|--------------------|---------------------------------------------------------|-----|-----|---------------------------------------------------|-------------|

|     |                    | Operating Frequency                                     |     |     | 5.0                                               | MHz         |

| 1 . | †op                |                                                         | 400 |     |                                                   | ns          |

| 2   | t <sub>s</sub>     | Major State Time                                        | 170 | T   |                                                   | ns          |

| 3   | t <sub>lxmar</sub> | LXMAR Pulse Width                                       | 70  | +   |                                                   | ns          |

| 4   | tas                | Address Setup Time : DX-LMAR (4)                        | 70  | +   | <del>                                      </del> | ns          |

| 5   | t <sub>ah</sub>    | Address Hold Time : LXMAR (+)-DX                        | 70  |     | 290                                               | ns          |

| 8   | t <sub>end</sub>   | Data Output Enable Time: DEVSEL (+)-DX                  |     |     |                                                   | <del></del> |

| 6   | tai                | Access Time from LXMAR                                  |     |     | 340                                               | ns          |

| 7   | ten                | Output Enable Time (MEM, CP, DEVSEL)                    |     |     | 220                                               | ns          |

| 9   | twp                | Pulse Width (MEMSEL, CPSEL)                             | 160 |     | <u> </u>                                          | ns          |

| 10  | twpd               | Pulse Width (DEVSEL)                                    | 160 |     | ļ                                                 | ns          |

| 11  | t <sub>ds</sub>    | Data Setup Time (DX- + MEMSEL/CPSEL)                    | 140 |     |                                                   | ns          |

| 12  | tdh                | Data Hold Time († MEMSEL/CPSEL-DX)                      | 70  |     |                                                   | ns          |

| 13  | t <sub>dsd</sub>   | Data Setup Time (DX- + DEVSEL)                          | 140 |     |                                                   | ns          |

| 14  | tdhd               | Data Hold Time ( + DEVSEL-DX)                           | 70_ |     |                                                   | ns          |

| 15  | t <sub>sl</sub>    | Logic Delay to MEM/DEV/CP/SWSEL                         | 35  |     | 210                                               | ns          |

| 16  | t <sub>xt</sub>    | Logic Delay to LXMAR, XTA, XTB, XTC                     | 35  |     | 170                                               | ns          |

| 17  | tst                | Logic Delay to DATAF, RUN, DMAGNT, INTGNT, LINK, IFETCH |     |     | 210                                               | ns          |

| 18  | t <sub>rs</sub>    | Set up Time for CP/INT/DMAREQ                           | 0   |     |                                                   | ns          |

| 19  | t <sub>rh</sub>    | Hold Time for CP/INT/DMAREQ, RESET, RUN-HALT            | 140 |     |                                                   | ns          |

| 20  | t <sub>rhp</sub>   | RUN-HALT Pulse Width                                    | 50  |     | <u> </u>                                          | ns          |

| 21  | tws                | Set up Time for Wait                                    | 50  |     |                                                   | ns          |

| 22  | t <sub>wh</sub>    | Hold Time for Wait                                      | 20  |     |                                                   | ns          |

Note: For capacitance of greater than 50pF, the AC parameters will have a delay factor of 0.5ns/pF.

INTERSIL

### **IM6100**

### IM6100-1

### **ABSOLUTE MAXIMUM RATINGS**

Operating Temperature

-40°C to +85°C

Industrial IM6100-11

-40°C to +85°C

Storage Temperature

-65°C to +150°C

Operating Voltage

+4.0V to +11.0V

Supply Voltage

+12.0V

Voltage On Any Input or

-0.3V to Vcc +0.3V

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

### D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC}$  = 5.0V ±10%,  $T_A$  = -40° C to +85° C

|    | SYMBOL          | PARAMETER                    | CONDITIONS                               | MIN      | TYP | MAX  | UNITS |

|----|-----------------|------------------------------|------------------------------------------|----------|-----|------|-------|

| 1  | ViH             | Input Voltage High           |                                          | Vcc -2.0 |     |      | V     |

| 2  | VtL             | Input Voltage Low            |                                          |          |     | 8.0  | V     |

| 3  | lı <sub>L</sub> | Input Leakage                | GND ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>  | -1.0     |     | 1.0  | μА    |

| 4  | Vон             | Output Voltage High          | I <sub>OH</sub> = −0.2mA                 | 2.4      |     |      | V     |

| 5  | Vol             | Output Voltage Low           | $I_{OL} = 2.0 \text{mA}$                 |          | Ī   | 0.45 | V     |

| 6  | IOLK            | Output Leakage               | GND ≤ Vout ≤ Vcc                         | -1.0     |     | 1.0  | μА    |

| 7  | lcc             | Power Supply Current-Standby | V <sub>IN</sub> = GND or V <sub>CC</sub> |          |     | 800  | μА    |

| 8  | Icc             | Power Supply Current-Dynamic | $f_C = 3.33MHz$                          |          |     | 2.0  | mA    |

| 9  | Cin             | Input Capacitance            |                                          |          | 7.0 | 8.0  | pF    |

| 10 | Co              | Output Capacitance           |                                          |          | 8.0 | 10.0 | pF    |

### A.C. CHARACTERISTICS (Ref. Fig. 2 and 22)

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $C_L = 50 pF$ ,  $T_A = -40 ^{\circ} C$  to  $+85 ^{\circ} C$ ,  $f_C = 3.33 MHz$

| 1  | SYMBOL             | PARAMETER                                               | MIN | TYP      | MAX  | UNITS |

|----|--------------------|---------------------------------------------------------|-----|----------|------|-------|

| 1  | f <sub>op</sub>    | Operating Frequency                                     |     |          | 3.33 | MHz   |

| 2  | t <sub>s</sub>     | Major State Time                                        | 600 |          |      | ns    |

| 3  | t <sub>lxmar</sub> | LXMAR Pulse Width                                       | 260 | Ĭ        |      | пѕ    |

| 4  | tas                | Address Setup Time: DX-LXMAR (+)                        | 85  |          |      | ns    |

| 5  | tah                | Address Hold Time : LXMAR (♣)-DX                        | 125 |          |      | ns    |

| 8  | t <sub>end</sub>   | Data Output Enable Time: DEVSEL (+)-DX                  |     |          | 470  | ns    |

| 6  | tal                | Access Time from LXMAR                                  |     |          | 520  | ns    |

| 7  | t <sub>en</sub>    | Output Enable Time (MEM, CP, DEVSEL)                    |     |          | 300  | ns    |

| 9  | twp                | Pulse Width (MEMSEL, CPSEL)                             | 235 |          |      | ns    |

| 10 | twpd               | Pulse Width (DEVSEL)                                    | 235 |          |      | ns    |

| 11 | t <sub>ds</sub>    | Data Setup Time (DX-1 MEMSEL/CPSEL)                     | 135 |          |      | ns    |

| 12 | t <sub>dh</sub>    | Data Hold Time (* MEMSEL/CPSEL-DX)                      | 125 |          |      | ns    |

| 13 | t <sub>dsd</sub>   | Data Setup Time (DX-† DEVSEL)                           | 225 |          |      | ns    |

| 14 | t <sub>dhd</sub>   | Data Hold Time († DEVSEL-DX)                            | 125 | <u> </u> |      | ns    |

| 15 | t <sub>si</sub>    | Logic Delay to MEM/DEV/CP/SWSEL                         | 75  |          | 380  | ns    |

| 16 | t <sub>xt</sub>    | Logic Delay to LXMAR, XTA, XTB, XTC                     | 65  |          | 270  | ns    |

| 17 | t <sub>st</sub>    | Logic Delay to DATAF, RUN, DMAGNT, INTGNT, LINK, IFETCH |     |          | 340  | ns    |

| 18 | t <sub>rs</sub>    | Set up Time for CP/INT/DMAREQ                           | 0   |          |      | ns    |

| 19 | t <sub>rh</sub>    | Hold Time for CP/INT/DMAREQ, RESET, RUN-HALT            | 200 |          |      | ns    |

| 20 | t <sub>rhp</sub>   | RUN-HALT Pulse Width                                    | 80  |          |      | ns    |

| 21 | t <sub>ws</sub>    | Set up Time for Wait                                    | 100 |          |      | ns    |

| 22 | t <sub>wh</sub>    | Hold Time for Wait                                      | 20  |          |      | ns    |

$\textbf{Note:} \ \ \text{For capacitance greater than 50pF, the AC parameters will have a delay factor of 0.5ns/pF.}$

### IM6100

### IM6100-1M (Military) ABSOLUTE MAXIMUM RATINGS

| Operating Temperature                               |

|-----------------------------------------------------|

| Industrial IM6100-1M55°C to +125°C                  |

| Storage Temperature65°C to +150°C                   |

| Operating Voltage +4.0V to +11.0V                   |

| Supply Voltage+12.0V                                |

| Supply Voltage                                      |

| Voltage On Any Input or Outout Pin0.3V to Vcc +0.3V |

| Output Pin 0.5 to vec                               |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

# D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC}$  = 5V  $\pm$  10%,  $T_A$  = -55°C to +125°C

|    | SYMBOL | PARAMETER                    | CONDITIONS                               | MIN      | TYP | MAX  | UNITS    |

|----|--------|------------------------------|------------------------------------------|----------|-----|------|----------|

|    |        |                              |                                          | Vcc -2.0 | ,   |      | V        |

| 1  | ViH    | Input Voltage High           |                                          |          |     | 0.8  | V        |

| 2  | VIL    | Input Voltage Low            |                                          |          |     | 1.0  | μА       |

| 3  | lı.    | Input Leakage                | GND ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>  | -1.0     |     | 1.0  | μ^       |

| 4  | Vон    | Output Voltage High          | $i_{OH} = -0.2mA$                        | 2.4      |     |      | V        |

|    | Vol    | Output Voltage Low           | $I_{OL} = 2.0 \text{mA}$                 |          |     | 0.45 | <u> </u> |

| 6  | IOLK   | Output Leakage               | GND ≤ Vout ≤ Vcc                         | -1.0     |     | 1.0  | μΑ       |

|    |        |                              | V <sub>IN</sub> = GND or V <sub>CC</sub> |          |     | 800  | μΑ       |

| 7  | Icc    | Power Supply Current-Standby |                                          |          |     | 2.0  | mA       |

| 8  | loc    | Power Supply Current-Dynamic | $f_C = 2.5MHz$                           |          |     |      |          |

| 9  | Cin    | Input Capacitance            |                                          |          | 7.0 | 8.0  | pF       |

| 10 | Co     | Output Capacitance           |                                          |          | 8.0 | 10.0 | pF       |

# A.C. CHARACTERISTICS (Ref. Fig. 2 and 22)

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $C_L = 50pF$ ,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $f_C = 2.5MHz$

|  | 5 | 3 | ) |  |

|--|---|---|---|--|

|  | _ |   |   |  |

|     | SYMBOL             | PARAMETER                                               | MIN | TYP                                              | MAX         | UNITS |

|-----|--------------------|---------------------------------------------------------|-----|--------------------------------------------------|-------------|-------|

|     |                    |                                                         |     |                                                  | 2.5         | MHz   |

| 1   | † <sub>op</sub>    | Operating Frequency                                     | 800 |                                                  |             | ns    |

| 2   | t <sub>s</sub>     | Major State Time                                        | 355 |                                                  |             | ns    |

| 3 _ | t <sub>lxmar</sub> | LXMAR Pulse Width                                       | 200 |                                                  |             | ns    |

| 4   | tas                | Address Setup Time : DX-LXMAR (*)                       |     | +                                                | <del></del> | ns    |

| 5   | tah                | Address Hold Time: LXMAR (+)-DX                         | 175 | +                                                | 655         | ns    |

| 8   | tend               | Data Output Enable Time: DEVSEL (+)-DX                  |     | +                                                |             |       |

| 6   | tal                | Access Time from LXMAR                                  |     | <del> </del>                                     | 745         | ns    |

| 7   | t <sub>en</sub>    | Output Enable Time (MEM, CP, DEVSEL)                    |     | <del></del>                                      | 470         | ns_   |

| 9   | twp                | Pulse Width (MEMSEL, CPSEL)                             | 330 |                                                  |             | ns    |

| 10  | t <sub>wpd</sub>   | Pulse Width (DEVSEL)                                    | 330 |                                                  |             | ns    |

| 11  | t <sub>ds</sub>    | Data Setup Time (DX- + MEMSEL/CPSEL)                    | 250 |                                                  | <u> </u>    | ns    |

| 12  | t <sub>dh</sub>    | Data Hold Time ( MEMSEL/CPSEL-DX)                       | 170 |                                                  | <u> </u>    | ns    |

| 13  | t <sub>dsd</sub>   | Data Setup Time (DX- + DEVSEL)                          | 350 |                                                  |             | ns    |

| 14  | t <sub>dhd</sub>   | Data Hold Time ( † DEVSEL-DX)                           | 170 |                                                  |             | ns    |

|     | t <sub>sl</sub>    | Logic Delay to MEM/DEV/CP/SWSEL                         | 75  |                                                  | 420         | _ns   |

| 15  | t <sub>xt</sub>    | Logic Delay to LXMAR, XTA, XTB, XTC                     | 65  |                                                  | 300         | ns    |

| 16  |                    | Logic Delay to DATAF, RUN, DMAGNT, INTGNT, LINK, IFETCH |     |                                                  | 375         | ns    |

| 17  | t <sub>st</sub>    | Set up Time for CP/INT/DMAREQ                           | 0   |                                                  |             | ns    |

| 18  | t <sub>rs</sub>    | Set up Time for CP/INT/DMAREQ                           | 220 | <del>                                     </del> | <b>†</b>    | ns    |

| 19  | t <sub>rh</sub>    | Hold Time for CP/INT/DMAREQ, RESET, RUN-HALT            | 90  |                                                  |             | ns    |

| 20  | t <sub>rhp</sub>   | RUN-HALT Pulse Width                                    | 110 | +-                                               | <b>+</b>    | ns    |

| 21  | tws                | Set up Time for Wait                                    | +   |                                                  | +           | ns    |

| 22  | twh                | Hold Time for Wait                                      | 20  | _1                                               |             | l lis |

Note: For capacitance of greater than 50pF, the AC parameters all have delay factor of 0.5ns/pF.

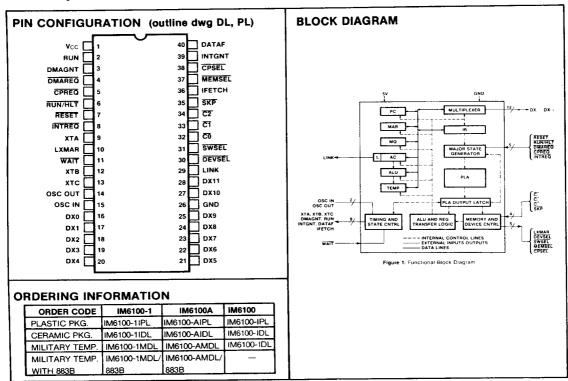

Figure 1: Functional Block Diagram

### **FUNCTIONAL PIN DESCRIPTIONS**

| PIN | SYMBOL          | DESCRIPTION                                                                                                                                                                                   |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Vcc             | Supply voltage.                                                                                                                                                                               |

| 2   | RUN             | The signal indicates the runstate of the CPU and may be used to power down the external circuitry                                                                                             |

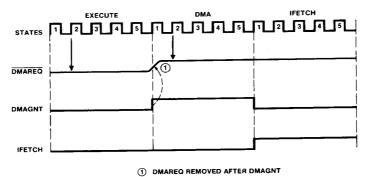

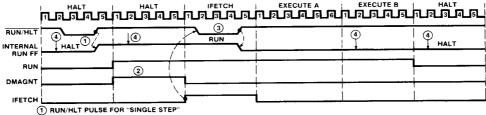

| 3   | DMAGNT          | Direct Memory Access Grant—DX lines are three-state.                                                                                                                                          |

| 4   | DMAREQ          | Direct Memory Access Request—DMA is<br>granted at the end of the current instruction.<br>Upon DMA grant, the CPU suspends<br>program execution until the DMAREQ line is<br>released.          |

| 5   | CPREQ           | Control Panel Request—a dedicated inter-<br>rupt which bypasses the normal device inter-<br>rupt request structure.                                                                           |

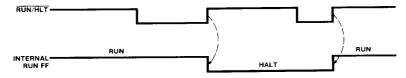

| 6   | RUN/HLT         | Pulsing the Run/Halt line causes the CPU to alternately run and halt by changing the state of the internal RUN/HLT flip flop.                                                                 |

| 7   | RESET           | Clears the AC and loads 7777 <sub>8</sub> into the PC.<br>CPU is halted.                                                                                                                      |

| 8   | INTREQ          | Peripheral device interrupt request.                                                                                                                                                          |

| 9   | XTA             | External coded minor cycle timing—signifies input transfers to the IM6100.                                                                                                                    |

| 10  | LXMAR           | The Load External Memory Address<br>Register is used to store memory and<br>peripheral addresses externally.                                                                                  |

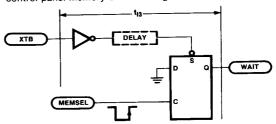

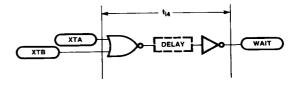

| 11  | WAIT            | Indicates that peripherals or external memory is not ready to transfer data. The CPU state gets extended as long as WAIT is active. The CPU is in the lowest power state with clocks running. |

| 12  | хтв             | External coded minor cycle timing—signifies output transfers from the IM6100.                                                                                                                 |

| 13  | XTC             | External coded minor cycle timing—used in conjunction with the Select Lines to specify read or write operations.                                                                              |

| 14  | OSC OUT         | Crystal input to generate the internal timing (also external clock input).                                                                                                                    |

| 15  | OSC IN          | See Pin 14—OSC OUT (also external clock ground)                                                                                                                                               |

| 16  | DX <sub>0</sub> | DataX—multiplexed data in, data out and address lines.                                                                                                                                        |

| 17  | DX <sub>1</sub> | See Pin 16—DX <sub>0</sub> .                                                                                                                                                                  |

| PIN      | SYMBOL                | DESCRIPTION                                                                        |

|----------|-----------------------|------------------------------------------------------------------------------------|

| 18       | DX <sub>2</sub>       | See Pin 16—DX <sub>0</sub> .                                                       |

| 19       | DX <sub>3</sub>       | See Pin 16—DX <sub>0</sub> .                                                       |

| 20       | DX <sub>4</sub>       | See Pin 16-DX <sub>0</sub> .                                                       |

| 21       | DX <sub>5</sub>       | See Pin 16—DX <sub>0</sub> .                                                       |

| 22       | DX <sub>6</sub>       | See Pin 16—DX <sub>0</sub> .                                                       |

| 23       | DX <sub>7</sub>       | See Pin 16—DX <sub>0</sub> .                                                       |

| 24       | DX8                   | See Pin 16—DX <sub>0</sub> .                                                       |

| 25       | DX <sub>9</sub>       | See Pin 16—DX <sub>0</sub> .                                                       |

| 26       | GND                   | Ground                                                                             |

| 27       | DX <sub>10</sub>      | See Pin 16DX <sub>0</sub> .                                                        |

| 28       | DX <sub>11</sub>      | See Pin 16DX <sub>0</sub> .                                                        |

| 29       | LINK                  | Indicates state of link flip flop.                                                 |

| 30       | DEVSEL                | Device Select for I/O transfers.                                                   |

| 31       | SWSEL                 | Switch Register Select for the OR THE SWITCH REGISTER INSTRUCTION (OSR).           |

|          |                       | OSR is a Group 2 Operate Instruction which                                         |

|          |                       | reads a 12 bit external switch register and                                        |

| 1        |                       | OR's it with the contents of the AC.                                               |

| 32       | <del>C</del> ₀        | Control line inputs from the peripheral                                            |

|          | <del>_</del>          | device during an I/O transfer (Table VI).<br>See Pin 32—Co.                        |

| 33<br>34 | <u>C1</u>             | See Pin 32—Co.                                                                     |

| 35       | C <sub>2</sub><br>SKP | Skips the next sequential instruction if active                                    |

| 35       | SKP                   | during an I/O instruction.                                                         |

| 36       | IFETCH                | Instruction Fetch Cycle                                                            |

| 37       | MEMSEL                | Memory Select for memory transfers.                                                |

| 38       | CPSEL                 | The Control Panel Memory Select becomes                                            |

| l        |                       | active, instead of the MEMSEL, for control panel routines. Signal may be used to   |

| l        | !                     | distinguish between control panel and main                                         |

|          |                       | memories.                                                                          |

| 39       | INTGNT                | Peripheral device Interrupt Grant.                                                 |

| 40       | DATAF                 | Data Field pin indicates the execute phase of                                      |

| 1        | t                     | indirectly addressed AND, TAD, ISZ and DCA instructions so that the data transfers |

|          | ļ.                    | are controlled by the Data Field, DF, and not                                      |

| 1        | [                     | the Instruction Field, IF, if Extended Memory                                      |

| 1        |                       | Control hardware is used to extend the addressing space from 4K to 32K words.      |

| Į.       | 1                     | addressing space from 4K to 32K words.                                             |

| 1        | 1                     | 1                                                                                  |

8-39

### **MEMORY ORGANIZATION**

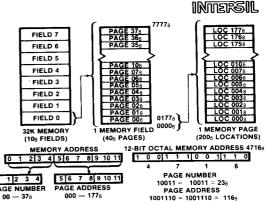

The IM6100 has a basic addressing capacity of 4096 12-bit words which may be extended by Extended Memory Control hardware to 32K. The memory system is organized in 4096 word blocks, called MEMORY FIELDS. The first 4096 words of memory are in Field 0; if a full 32K of memory is installed, the uppermost Memory Field will be numbered 7. In any given Memory Field every location has a unique 4 digit octal (12 bit binary) address, 0000<sub>8</sub> to 7777<sub>8</sub> (00001<sub>0</sub> to 40951<sub>0</sub>). Each Memory Field is subdivided into 32 PAGES of 128 words each. Memory Pages are numbered sequentially from Page 00<sub>8</sub>, containing addresses 0000-0177<sub>8</sub>, to Page 37<sub>8</sub>, containing addresses 7600<sub>8</sub>-7777<sub>8</sub>. The first 5 bits of a 12-bit MEMORY ADDRESS denote the PAGE NUMBER and the low order 7 bits specify the PAGE ADDRESS of the memory location within the given Page.

During an instruction fetch cycle, the IM6100 fetches the instruction pointed to by the PC, the contents of the PC are transferred to the MAR, and the PC is incremented by 1. The PC now contains the address of the 'next' sequential instruction and the MAR contains the address of the 'current' instruction which must be fetched from memory. Bits 0-4 of the MAR identify the CURRENT PAGE, that is, the Page from which instructions are currently being fetched, and bits 5-11 of the MAR identify the location within the Current Page. (PAGE ZERO (0), by definition, denotes the first 128 words of memory, 00008-01778.)

Memory Organization

### **INSTRUCTION SET**

The IM6100 instructions are 12-bit words stored in memory. The IM6100 makes no distinction between instructions and data; it can manipulate instructions as stored variables or execute data as instructions when it is programmed to do so. There are three general classes of IM6100 instructions. They are referred to as Memory Reference Instruction (MRI), Operate Instruction (OPR) and Input/Output Transfer Instruction (IOT).

The notations used in the following instruction tables are defined in Table I below:

**TABLE 1.** Notation Definitions

- ( ) denotes the contents of the register or location within parenthesis. (EA) is read as "... the contents of the Effective Address."

- (i)) denotes the contents of the location pointed to by the contents of the location within the double parenthesis.

((PA)) is read as "... the contents of the location pointed to by the contents of the Pointer Address."

- 3. denotes "... is replaced by ..."

- 4 denotes the interchange operation.

- 5. A denotes logical AND operation.

- 6. v denotes logical OR operation.

- 7. EA denotes the Effective Address for Direct Addressing.

- 8. PA denotes the Pointer Address for Indirect Addressing. PA can be any address on the CURRENT PAGE or PA can be any address (0000<sub>8</sub>) through (0177<sub>8</sub>) on PAGE ZERO other than the addresses (0010<sub>8</sub>) through (0017<sub>8</sub>) which are reserved for autoindexing.

- PAIX denotes the Pointer Address for autoindexing. It can be any address (0010<sub>8</sub>) through (0017<sub>8</sub>).

- I represents bit 3; the Indirect Addressing Bit, of the instruction.

- 11. EA, PA, or PAIX is specified by bit 4 through bit 11 of the memory reference instruction.

- 12. PC denotes the Program Counter.

- 13. SR denotes the Switch Register.

- 14. (AC)n denotes the nth bit of the AC contents.

- 15. DEV denotes a specific peripheral device and "dddddd" denotes the device address code. CMND is the command issued to the device during an I/O operation and "eee" is its three bit code.

IM6100 INTERSIL

### **ARCHITECTURE**

The IM6100 has 6 twelve bit registers, a programmable logic array, an arithmetic and logic unit and associated gating and timing circuitry. A block diagram of the IM6100 is shown in Figure 1.

#### **ACCUMULATOR (AC)**

The AC is a 12-bit register in which arithmetic and logical operations are performed. Data words may be transferred from memory to the AC or transferred from the AC into memory. Arithmetic and logical operations involve one or two operands, one held in the AC and the other fetched from the memory. The result of the operation is left in the AC which may be cleared, complemented, tested, incremented or rotated under program control. The AC also serves as an input-output register, as all programmed data transfers pass through the AC.

#### LINK (L)

The Link is a 1-bit flip-flop that serves as a high-order extension of the AC. It is used as a carry flip-flop for 2's complement arithmetic. A carry out of the accumulator complements the Link. Link can be cleared, set, complemented and tested under program control and rotated as part of the AC.

### MQ REGISTER (MQ)

The MQ is a 12-bit temporary register which is program accessible. The contents of AC may be transferred to the MQ for temporary storage, or MQ can be OR'ed with the AC and the result stored in the AC. The contents of the AC and the MQ may also be exchanged.

### MEMORY ADDRESS REGISTER (MAR)

While accessing memory, the 12-bit MAR register contains the address of the memory location that is currently selected for reading or writing. The MAR is also used as an internal register for microprogram control during data transfers to and from memory and peripherals.

### PROGRAM COUNTER (PC)

The 12-bit PC contains the address of the memory location from which the next instruction is fetched. During an instruction fetch, the PC is transferred to MAR and the PC is then incremented by 1. When there is a branch to another address in memory, the branch address is set into the PC. Branching normally takes place under program control, however, during an input-output operation, a device may specify a branch address. A skip (SKP) instruction increments the PC by 1, thus causing the next instruction to be skipped. The SKP instruction may be unconditional, or conditional on the state of the AC or the Link. During an input-output operation, a device can also cause the next sequential instruction to be skipped. Interrupts force the PC to 0000. Reset forces the PC to 77778.

#### ARITHMETIC AND LOGICAL UNIT (ALU)

The ALU performs both arithmetic and logical operations, –two's complement binary addition, AND, OR and complement. The ALU can perform a single position shift either to the left or to the right; a double rotate is implemented in two single bit shifts. The ALU can also shift by 3 positions to implement a byte swap in two steps. The AC is always one of the inputs to the ALU, however, under internal microprogram control, AC may be gated off and all one's or all zero's gated in. The second input may be any one of the other registers under internal microprogram control.

### **TEMPORARY REGISTER (TEMP)**

The 12-bit TEMP register latches the result of an ALU operation, before it is sent to the destination register, to avoid race conditions. The TEMP is also used as an internal register for microprogram control.

### INSTRUCTION REGISTER (IR)

During an instruction fetch, the 12-bit IR is loaded with the instruction that is to be executed by the CPU. The IR specifies the initial step of the microprogram sequence for each instruction, and is also used as an internal register to store temporary data for microprogram control.

### **MULTIPLEXER (DX)**

The 12-bit Input/Output Multiplexer handles data, address and instruction transfers into and out of the CPU, and to or from the main memory and peripheral devices on a time-multiplexed basis.

# MAJOR STATE GENERATOR AND THE PROGRAMMED LOGIC ARRAY (PLA)

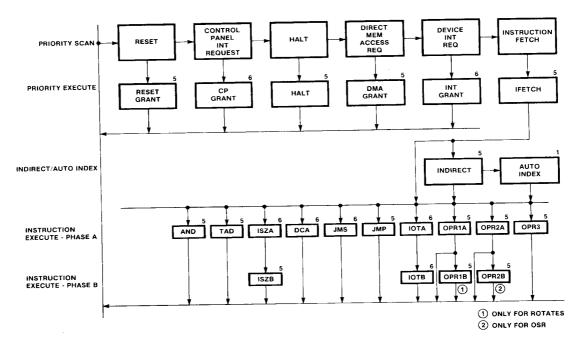

During an instruction fetch the instruction to be executed is loaded into the IR. The PLA is then used for the correct sequencing of the CPU for the appropriate instruction. After an instruction is completely sequenced, the major state generator scans the internal priority network, which decides whether the machine is going to fetch the next instruction in sequence, or service one of the external request lines.

# 8

### PLA OUTPUT LATCH

The PLA Output Latch permits the PLA to be pipelined; it fetches the next control sequence while the CPU is executing the current sequence.

# MEMORY AND DEVICE CONTROL, ALU AND REG TRANSFER LOGIC

The Memory and Device Control Unit provides external control signals to communicate with peripheral devices (DEVSEL), switch register (SWSEL), memory (MEMSEL) and/or control panel memory (CPSEL). During I/O instructions this unit also modifies the PLA outputs depending on the states of the four device control lines (SKP, C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>). The ALU and Register Transfer Logic provides the control signals for the internal register transfers and ALU operation.

# ARCHITECTURE (CONTINUED)

# TIMING AND STATE CONTROL

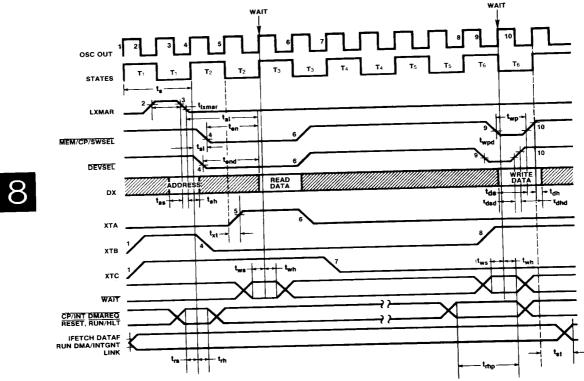

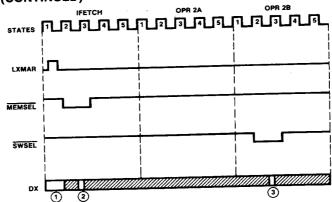

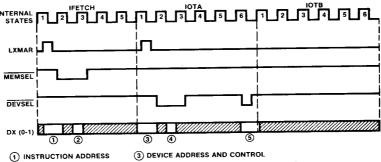

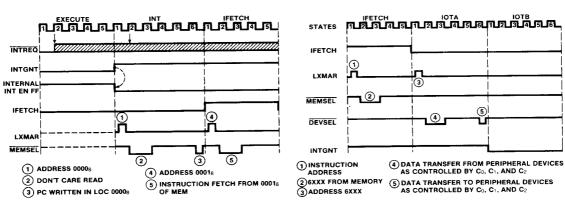

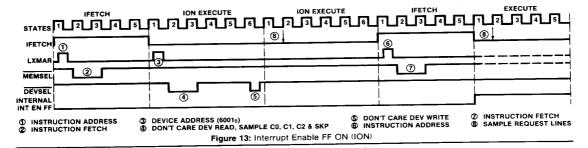

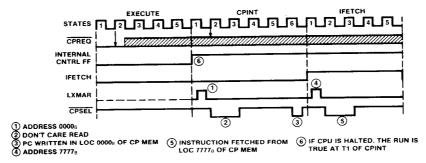

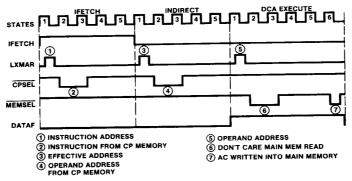

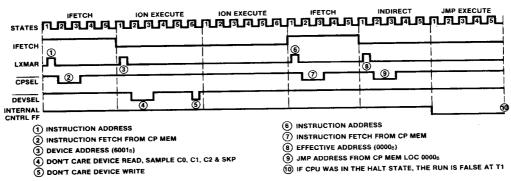

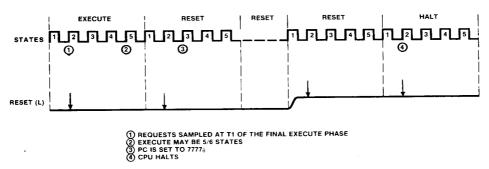

The IM6100 internally generates all the timing and state signals. A crystal is used to control the CPU operating frequency, which is divided by two by the CPU. With a 4MHz crystal, the internal states will be of 500nsec duration. The major timing states are described in Figure 2.

For memory reference instructions, a 12-bit address is sent on the DX lines. The Load External Memory Address Register, LXMAR, is used to clock an external register to store the address information externally, if required. When executing an Input-Output I/O instruction, the instruction being executed is sent on the DX lines to be stored externally. The external address register then contains the device address and control information. The LXMAR pulse occurs only if a valid address is present on the DX lines.

Various CPU request lines are priority sampled if the next cycle is an Instruction Fetch cycle. Current state of the CPU is available externally.

Memory/Peripheral data is read for an input trans- $T_2$ fer (READ). WAIT controls the transfer duration. If WAIT is active during input transfers, the CPU waits in the T2 state. The wait duration is an integral multiple of the crystal frequency - 250nsec for 4MHz.

For memory reference instructions, the Memory Select, MEMSEL, line is active. For I/O instructions the Device Select, DEVSEL, line is active. Control lines, therefore, distinguish the contents of the external register as memory or device address.

External device sense lines,  $C_0$ ,  $C_1$ ,  $C_2$ , and SKP, are sampled if the instruction being executed is an I/O

Control Panel Memory Select, CPSEL, and Switch Register Select, SWSEL, become active low for data transfers between the IM6100 and Control Panel Memory and the Switch Register, respectively.

T<sub>3</sub>,T<sub>4</sub>,T<sub>5</sub> ALU operation and internal register transfers.

This state is entered for an output transfer (WRITE). The address is defined during  $T_1$ . WAIT controls the time for which the Write data must be maintained.

Figure 2: IM6100 AC Timing Diagram

8-42

INNERSIL **IM6100**

### **INSTRUCTION SET**

### MEMORY REFERENCE INSTRUCTION (MRI)

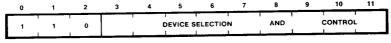

The Memory Reference Instructions operate on the contents of a memory location or use the contents of a memory location to operate on the AC or the PC. The first 3 bits of a Memory Reference Instruction specify the operation code, or OPCODE, and the low order 9 bits, the OPERAND address, as shown in Figure 3.

Figure 3: Memory Reference Instruction Format

Bits 5 through 11, the PAGE ADDRESS, identify the location of the OPERAND on a given page, but they do not identify the page itself. The page is specified by bit 4, called the CURRENT PAGE OR PAGE 0 BIT. If bit 4 is a 0, the page address is interpreted as a location on Page 0. If bit 4 is a 1, the page address specified is interpreted to be on the Current Page.

For example, if bits 5 through 11 represent 1238 and bit 4 is a 0, the location referenced is the absolute address 01238 However, if bit 4 is a 1 and the current instruction is in a memory location whose absolute address is 46108 the page address 1238 designates the absolute address 47238, as shown below.

46108 = 100 110 001 000 = PAGE 10 011 = PAGE 238 4610<sub>8</sub> = 100 110 001 000 = PAGE 10 011 - PAGE 238 Location 4610<sub>8</sub> is in PAGE 23<sub>8</sub>. Location 123<sub>8</sub> in PAGE 23<sub>8</sub>. CURRENT PAGE, will be: 10 011<sub>1</sub>1 010 011<sub>1</sub> = 100 111 010 011 = 4723<sub>8</sub> PAGE ADDRESS 123<sub>8</sub> PAGE NUMBER 23<sub>8</sub>

By this method, 256 locations may be directly addressed, 128 on PAGE 0 and 128 on the CURRENT PAGE. Other locations are addressed indirectly by setting bit 3. An INDIRECT ADDRESS (pointer address) identifies the location that contains the desired address (effective address). To address a location that is not directly addressable, not in PAGE 0 or in the CURRENT PAGE, the absolute address of the desired location is stored in one of the 256 directly addressable locations (pointer address). Upon execution, the MRI will operate on the contents of the location identified by the address contained in the pointer location.

It should be noted that locations 00108-00178 in PAGE 0 are AUTOINDEXED. If these locations are addressed indirectly, the contents are incremented by 1 and restored before they are used as the operand address. These locations may, therefore, be used for indexing applications.

Table II lists the mnemonics for the six memory reference instructions, their OPCODEs, the operations they perform and the number of states required for execution.

It should be noted that the data is represented in Two's Complement Integer notation. In this system, the negative of a number is formed by complementing each bit in the data word and adding "1" to the complemented number. The sign is indicated by the most significant bit. In the 12-bit word used by the IM6100, when bit 0 is a "0", it denotes a positive number and when bit 0 is a "1", it denotes a negative number. The maximum single precision number ranges for this system are 37778 (+2047) and 40008 (-2048).

Table II

| MNEMONIC   | OP CODE | ĪΑ | STATES | OPERATION                                                                                                                                                                                                                                                                                              |

|------------|---------|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AND EA     | 08      | 0  | 10     | LOGICAL AND DIRECT Operation IAC: — AC: N.EA Description Contents of the EA are logically AND ed with the contents of the AC and the result is stored in AC.                                                                                                                                           |

| AND I PA   |         | 1  | 15     | LOGICAL AND INDIRECT (PA ≠ 0010-0017 <sub>8</sub> ) Operation: (AC ← AC A (PA).                                                                                                                                                                                                                        |

| AND PAIX   |         | 1  | 16     | LOGICAL AND AUTOINDEX (PAIX = 0010-00178) Operation: PA: — PA: + 1, AC: — AC: A «PA:                                                                                                                                                                                                                   |

| TAD EA     | 18      | 0  | 10     | BINARY ADD DIRECT Operation AC+=-RGI + EA Description. Contents of the EA are ADDed with the contents of the AC and the result is stored in the AC, carry out complements the LINK If AC is initially cleared, this instruction acts as LOAD from Memory.                                              |

| TAD I PA   | ļ       | 1  | 15     | BINARY ADD INDIRECT (PA ≠ 0010-0017 <sub>8</sub> ) Operation AC ← AC+ «PA)                                                                                                                                                                                                                             |

| TAD I PAIX |         | 1  | 16     | BINARY ADD AUTOINDEX (PAIX = 0010-00178) Operation (PA) + PA) + 1, AC; -AC; + (PA)                                                                                                                                                                                                                     |

| ISZ EA     | 28      | 0  | 16     | INCREMENT AND SKIP IF ZERO DIRECT Operation EA — EA + I, II EA = 0000; PC — PC + 1 Description. Contents of the EA are incremented by 1 and restored. If the result is zero, the next sequential instruction is support.                                                                               |

| ISZ I PA   |         | 1  | 21     | INCREMENT AND SKIP IF ZERO INDIRECT (PA ≠ 0010-00178) Operation, iPA() ← iPA() + 1, if i(PA) = 00008, PC ← PC + 1                                                                                                                                                                                      |

| ISZ I PAIX |         | 1  | 22     | INCREMENT AND SKIP IF ZERO AUTOINDEX (PAIX = 0010-0017g) Operation (PA: + PA: + 1, *PA: + *PA: + 1, *PA: + 0000g, PC + PC + 1                                                                                                                                                                          |

| DCA EA     | 38      | 0  | 11     | DEPOSIT AND CLEAR THE ACCUMULATOR DIRECT Operation "EA → → ACI, "ACI → → 00008 Description: The conferts of the AC are stored in EA and the AC is cleared.                                                                                                                                             |

| DCA I PA   |         | 1  | 16     | DEPOSIT AND CLEAR THE ACCUMULATOR INDIRECT (PA ≠ 0010-00178)                                                                                                                                                                                                                                           |

| DCA I PAIX |         | 1  | 17     | DEPOSIT AND CLEAR THE ACCUMULATOR AUTOINDEX (PAIX = 0010-00178)  Operation PA + 1 PA + 1 PA + ACC AC + 00006                                                                                                                                                                                           |

| JMS EA     | 48      | 0  | 11     | JUMP TO SUBROUTINE DIRECT  Operation The contents of the PC are stored in the EA. The PC is incremented by 1 immediately after every instruction letch. The contents of the EA now point to the next sequential instruction following the JMS return address. The next instruction is taken from EA+1. |

| JMS I PA   |         | 1  | 16     | JUMP TO SUBROUTINE INDIRECT (PA ≠ 0010-0017 <sub>8</sub> ) Operation (PA) ← PC, (PC) ← PA) + 1                                                                                                                                                                                                         |

| JMS I PAIX |         | 1  | 17     | JUMP TO SUBROUTINE AUTOINDEX (PAIX = 0010-00178) Operation (PAI — PAI+1), (PAI — PC, (PC) — PAI+1                                                                                                                                                                                                      |

| JMP EA     | 58      | 0  | 10     | JUMP DIRECT Operation IPC — EA Description: The next instruction is taken from the EA                                                                                                                                                                                                                  |

| JMP I PA   |         | 1  | 15     | JUMP INDIRECT (PA ≠ 0010-0017 <sub>8</sub> ) Operation (PC) 1PA                                                                                                                                                                                                                                        |

| JMP I PAIX |         | 1  | 16     | JUMP AUTOINDEX (PAIX = 0010-0017 <sub>8</sub> ) Operation -PAI+1, -PCI                                                                                                                                                                                                                                 |

# INSTRUCTION SET (CONTINUED)

### **OPERATE INSTRUCTIONS**

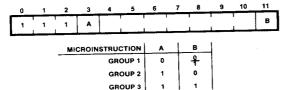

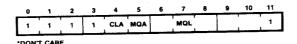

The Operate Instructions, which have an OPCODE of 78 (111), consist of 3 groups of microinstructions. Group 1, which is identified by the presence of the 0 in bit 3, is used to perform logical operations on the contents of the accumulator and link. Group 2, which is identified by the presence of a 1 in bit 3 and a 0 in bit 11, is used primarily to test the contents of the Accumulator and/or Link and then conditionally skip the next sequential instruction. Group 3 has a 1 in bit 3 and a 1 in bit 11 and performs logical operations on the contents of the AC and MQ.

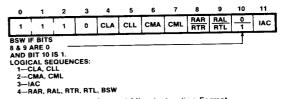

The basic OPR instruction format is shown in Figure 4.

Figure 4: Basic OPR Instruction Format

Operate microinstructions from any group may be microprogrammed with other operate microinstructions of the same group providing the instruction codes do not conflict. The actual code for a microprogrammed combination of two, or more, microinstructions is the bitwise logical OR of the octal codes for the individual microinstructions. When more than one operation is microprogrammed into a single instruction, the operations are performed in a prescribed sequence, with logical sequence number 1 performed first,

logical sequence number 2 performed second, logical sequence number 3 performed third and so on. Two operations with the same logical sequence number, within a given group of microinstructions, are performed simultaneously.

### **GROUP MICROINSTRUCTIONS**

Figure 5 shows the instruction format of a group 1 microinstruction. Any one of bits 4 to 11 may be set, loaded with a binary 1, to indicate a specific group 1 microinstruction. If more than one of these bits is set, the instruction is a microprogrammed combination of group 1 microinstructions, which will be executed according to the logical sequence shown in Figure 5.

Figure 5: Group 1 Microinstruction Format

Table III lists commonly used group 1 microinstructions, their assigned mnemonics, octal code, logical sequence, the number of states, and the operation they perform. The same format is followed in Table IV and V which lists group 2 and 3 microinstructions, respectively.

Table III: Group 1 Operate Microinstructions

|     | MNEMONIC | OCTAL<br>CODE | LOGICAL<br>SEQUENCE | NUMBER<br>OF<br>STATES | OPERATION                                                                                                                                                                                                                                  |

|-----|----------|---------------|---------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t   | NOP      | 7000          | 1                   | 10                     | NO OPERATION—This instruction causes a 10 state delay in program execution, without affecting the state of<br>the IM6100. It may be used for timing synchronization or as a convenient means of deleting an instruction from a<br>program. |

| 1   | IAC      | 7001          | 3                   | 10                     | INCREMENT ACCUMULATOR—The content of the AC is incremented by one (1) and carry out                                                                                                                                                        |

| ١   | RAL      | 7004          | 4                   | 15                     | ROTATE ACCUMULATOR LEFT—The contents of the AC and L are rotated one binary position to the left. AC ion is shifted to L and L is shifted to AC (11).                                                                                      |

| l   | RTL      | 7006          | 4                   | 15                     | ROTATE TWO LEFT—The contents of the AC and L are rotated two binary positions to the left. AC (1) is shifted to L and L is shifted to AC (10).                                                                                             |

| l   | RAR      | 7010          | 4                   | 15                     | ROTATE ACCUMULATOR RIGHT—The content of the AC and Lare rotated one binary position to the right. AC (13) is shifted to L and L is shifted to AC (0).                                                                                      |

| ١   | RTR      | 7012          | 4                   | 15                     | ROTATE TWO RIGHT—The contents of the AC and Lare rotated two binary positions to the right. AC (10) is shifted to L and L is shifted to AC (1).                                                                                            |

| ١   | BSW      | 7002          | 4                   | 15                     | BYTE SWAP—The right six (6) bits of the AC are exchanged or SWAPPED with the left six bits. AC (0) is swapped with AC (6). AC (1) with AC (7), etc. L is not affected.                                                                     |

| ı   | CML      | 7020          | 2                   | 10                     | COMPLEMENT LINK—The content of the link is complemented.                                                                                                                                                                                   |

| l   | CMA      | 7040          | 2                   | 10                     | COMPLEMENT ACCUMULATOR—The content of each bit of the AC is complemented having the effect of replacing the content of the AC with its one's complement.                                                                                   |

| ۱   | CIA      | 7041          | 2,3                 | 10                     | COMPLEMENT AND INCREMENT ACCUMULATOR—The content of the AC is replaced with its two's complement. Carry out complements the LINK.                                                                                                          |

| 1   | CLL      | 7100          | 1 1                 | 10                     | CLEAR LINK—The link is loaded with a binary 0.                                                                                                                                                                                             |

| 1   | CLL BAL  | 7104          | 1,4                 | 15                     | CLEAR LINK—ROTATE ACCUMULATOR LEFT.                                                                                                                                                                                                        |

| ı   | CLL RTL  | 7106          | 1,4                 | 15                     | CLEAR LINK—ROTATE TWO LEFT.                                                                                                                                                                                                                |

| ١   | CLL BAR  | 7110          | 1,4                 | 15                     | CLEAR LINK—ROTATE ACCUMULATOR RIGHT.                                                                                                                                                                                                       |

| 1   | CLL RTR  | 7112          | 1,4                 | 15                     | CLEAR LINK—ROTATE TWO RIGHT.                                                                                                                                                                                                               |

| ١   | STL      | 7120          | 1,2                 | 10                     | SET THE LINK—The LINK is loaded with a binary 1 corresponding with a microprogrammed combination of CLL and CML.                                                                                                                           |

| -1  | CLA      | 7200          | 1                   | 10                     | CLEAR ACCUMULATOR—The accumulator is loaded with binary 0's.                                                                                                                                                                               |

| ١   | CLA IAC  | 7201          | 1,3                 | 10                     | CLEAR ACCUMULATOR—INCREMENT ACCUMULATOR.                                                                                                                                                                                                   |

| ١   | GLT      | 7204          | 1,4                 | 15                     | GET THE LINK—The AC is cleared; the content of L is shifted into AC (11), a 0 is shifted into L. This is a micro-programmed combination of CLA and RAL.                                                                                    |

| - 1 | CLA CLL  | 7300          | 1                   | 10                     | CLEAR ACCUMULATOR—CLEAR LINK.                                                                                                                                                                                                              |

|     | STA      | 7240          | 1,2                 | 10                     | SET THE ACCUMULATOR—Each bit of the AC is set to 1 corresponding to a microprogrammed combination of CLA and CMA.                                                                                                                          |

INTERSIL

## IM6100

### **INSTRUCTION SET (CONTINUED)**

### **GROUP 2 MICROINSTRUCTIONS**

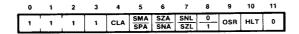

Figure 6 shows the instruction format of group 2 microinstructions. Bits 4-10 may be set to indicate a specific group 2 microinstruction. If more than one of bits 4-7 or 9-10 is set, the instruction is a microprogrammed combination of group 2 microinstructions, which will be executed according to the logical sequence shown in Figure 6.

Skip microinstructions may be microprogrammed with CLA,

OSR, or HLT microinstructions. When two or more skip microinstructions are microprogrammed into a single instruction, the resulting condition on which the decision will be based is the logical OR of the individual conditions when bit 8 is 0, or, when bit 8 is 1, the decision will be based on the logical AND.