# SINGLE-CHIP 8-BIT MICROCONTROLLER

# GENERAL DESCRIPTION

The MAB80XXH family of single-chip 8-bit microcontrollers is fabricated in NMOS. Three interchangeable (pin compatible) versions are available:

- MAB8048H: 1 K bytes mask-programmed ROM, 64 bytes RAM

- MAB8035HL: ROM-less version of the MAB8048H

- MAB8049H: 2 K bytes mask-programmed ROM, 128 bytes RAM

- MAB8039HL: ROM-less version of the MAB8049H

- MAB8050H: 4 K bytes mask-programmed ROM, 256 bytes RAM

- MAB8040HL: ROM-less version of the MAB8050H

These microcontrollers are designed to be efficient control processors as well as arithmetic processors. Their instruction set allows the user to directly set and reset individual I/O lines as well as test individual bits within the accumulator. A large variety of branch and table look-up instructions enable efficient implementation of standard logic functions. Code efficiency is high; over 70% of the instructions are single byte; all others are two byte.

An on-chip 8-bit counter is provided, which can count either machine cycles (+32) or external events. The counter can be used to generate an interrupt to the processor.

Program and data memories plus input/output capabilities can be expanded using standard TTL compatible memories and logic. For more detailed information see the 8048 family specification.

# Features

- 8-bit CPU, ROM, RAM and I/O

- 8-bit counter/timer

- On-chip oscillator and clock driver circuits

- Single-level interrupts: external and counter/timer

- 17 internal registers: accumulator, 16 addressable registers

- Over 90 instructions: 70% single byte

- All instructions 1 or 2 cycles

- Easily expandable memory and 27 I/O lines

- TTL compatible inputs and outputs

- Single 5 V supply

Standard and extended temperature ranges (see Table 5): MAB80XX: 0 to +70 °C

| MAF80XX:  | -40 to +85 °C  |

|-----------|----------------|

| MAF80AXX: | -40 to +110 °C |

## Applications

- Peripheral interfaces and controllers

- Test and measuring instruments

- Sequencers

# PACKAGE OUTLINES

All versions: with type no, suffix P (see Table 5): 40-lead DIL; plastic (SOT-129), MAB8035/8048/8039/8049H/HLWP

- Modems and data enciphering

- Environmental control systems

- Audio/video systems

: 44-lead PLCC; plastic leaded chip-carrier

(SOT187AA).

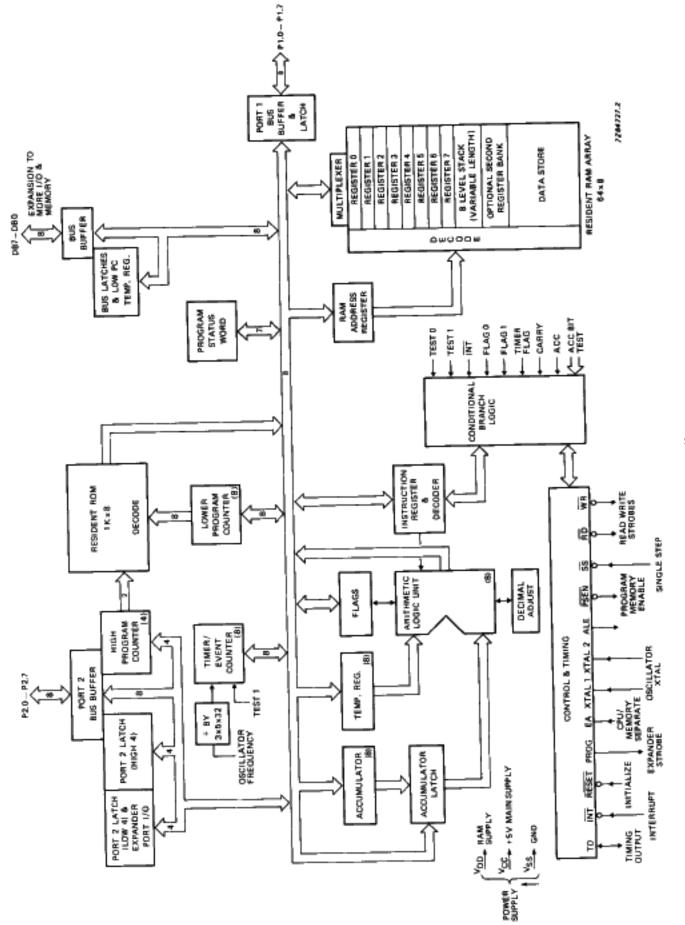

Fig. 1 Block diagram.

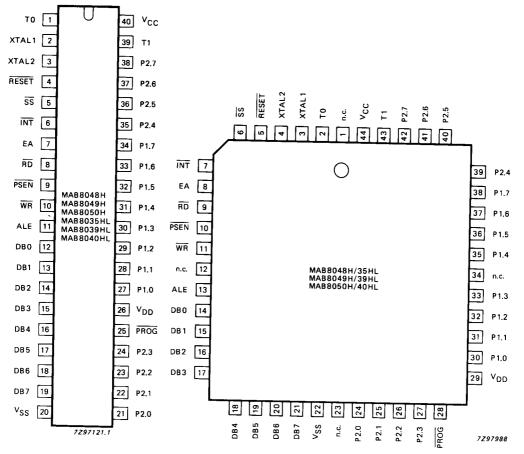

Fig. 2a Pinning diagram; for pin designation see next page.

Fig. 2b Pinning diagram for MAB80XXHWP; for pin designation see next page.

# Product type numbering European and USA cross-reference scheme

Type numbering reference Type numbering equivalent used mainly in Europe reference used mainly in USA MAB8039HLP/HLWP SCN8039HCB N40/A44 MAF8039HLP/HLWP SCN8039HAB N40/A44 MAB8049HP/HWP SCN8049HCB N40/A44 MAF8049HP/HWP SCN8049HAB N40/A44 MAB8040HLP/HLWP SCN8040HCB N40/A44 MAF8050HP/HWP SCN8050HCB N40/A44

| PINNING |                  |                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12–19   | DB0DB7           | <b>Data Bus:</b> true bidirectional I/O port which can be written or read using the $\overline{RD}$ and $\overline{WR}$ strobes. This port can also be used as an 8-bit latch. It contains the 8 low order address bits during an external memory access and receives the addressed instruction under control of PSEN. This multiplexed address/data port also contains the address and data during external RAM accesses. |

| 27–34   | P1.0-P1.7        | Port 1: 8-bit quasi-bidirectional I/O port (note 1).                                                                                                                                                                                                                                                                                                                                                                       |

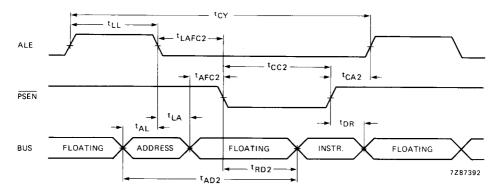

| 21-24   | P2.0P2.7         | Port 2: 8-bit quasi-bidirectional I/O port (note 1).                                                                                                                                                                                                                                                                                                                                                                       |

| 35–38   |                  | P2.0—P2.3 contains the 4 higher order address bits during an external program memory access and provides a 4-bit bus for 8243 I/O expanders.                                                                                                                                                                                                                                                                               |

| 25      | PROG             | Output strobe: active LOW for 8243 I/O expanders.                                                                                                                                                                                                                                                                                                                                                                          |

| 1       | то               | <b>Test 0:</b> input pin which can be tested by the JTO and JNTO instructions.<br><b>Clock:</b> TO can be configured as a clock output using the ENTO CLK instruction.                                                                                                                                                                                                                                                     |

| 39      | Τ1               | Test 1: input pin which can be tested using the JT1 and JTN1 instructions.<br>T1 can be configured as the timer/counter input using the STRT CNT<br>instruction.                                                                                                                                                                                                                                                           |

| 6       | ĪNT              | Interrrupt: interrupt input pin which can initiate an interrupt if the external interrupt is enabled.<br>Can also be tested using the JNI instruction. Interrupt is disabled during and after RESET.                                                                                                                                                                                                                       |

| 4       | RESET            | <b>Reset:</b> active LOW input used to initialize the microcontroller.<br>During program verification, the address is latched by a $0-$ to $-1$ transition on <b>RESET</b> and the data at the addressed location is output on BUS (note 2).                                                                                                                                                                               |

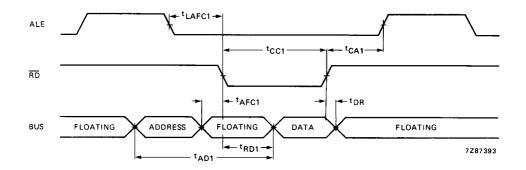

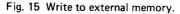

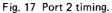

| 11      | ALE              | Address latch enable: occurs each cycle and is useful as a clock output.<br>During an external program or data memory access, ALE is used to<br>latch the address information multiplexed on the DB0 to DB7 outputs.                                                                                                                                                                                                       |

| 8       | RD               | Read BUS: active LOW strobe used to gate data on to BUS lines when<br>reading from an external source.                                                                                                                                                                                                                                                                                                                     |

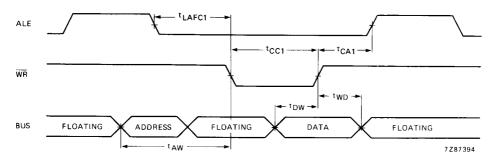

| 10      | WR               | Write BUS: active LOW strobe used to write data from BUS lines to an external designation.                                                                                                                                                                                                                                                                                                                                 |

| 7       | EA               | External access input: when HIGH, all instruction fetches are from external memory.                                                                                                                                                                                                                                                                                                                                        |

| 9       | PSEN             | <b>Program store enable:</b> active LOW strobe that occurs only during a fetch from external memory.                                                                                                                                                                                                                                                                                                                       |

| 5       | SS               | Single step: active LOW input used with ALE to cause the microcontroller to execute a single instruction.                                                                                                                                                                                                                                                                                                                  |

| 2<br>3  | XTAL 1<br>XTAL 2 | Crystal inputs: inputs for a crystal, LC-network or an external timing signal to determine the internal oscillator frequency (note 2).                                                                                                                                                                                                                                                                                     |

| 20      | V <sub>SS</sub>  | Ground: circuit earth potential.                                                                                                                                                                                                                                                                                                                                                                                           |

| 40      | Vcc              | Power supply: + 5 V main power supply pin.                                                                                                                                                                                                                                                                                                                                                                                 |

| 26      | VDD              | Power supply: + 5 V RAM standby power supply; low power                                                                                                                                                                                                                                                                                                                                                                    |

#### Notes

- 1. Each port line can be individually configured as an input or an output. A line is designated as an input by first writing a logic 1 to the line. RESET sets all port lines to logic 1.

- 2. Non-standard TTL VIH-

#### FUNCTIONAL DESCRIPTION

The following sections provide a detailed functional description of the MAB80XXH microcontroller as shown in Fig. 1. The generic term "MAB80XXH" is used to refer collectively to the MAB8048H/35HL, MAB8049H/39HL and MAB8050H/40HL.

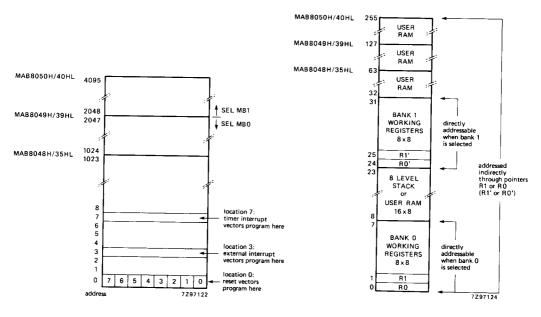

#### Program memory (see Fig. 3)

The on-chip program memory consists of 1024, 2048 or 4096 bytes of mask programmed ROM (MAB8048H/49H/50H); the MAB8035HL/39HL/40HL versions do not have on-chip program memory. The total addressing capability is 4096 bytes.

The program memory address space is divided into two 2048-byte banks MB0 and MB1. These two 2048 byte banks are each divided into 8 pages of 256 bytes for conditional branches. There are three locations in program memory of special interest. These are:

- Location 0 contains the first instruction to be executed after a RESET

- Location 3 contains the first instruction of an external interrupt routine

- Location 7 contains the first instruction of a timer/counter interrupt routine

Fig. 3 Program memory map.

Fig. 4 Data memory map.

## FUNCTIONAL DESCRIPTION (continued)

### Data memory (see Fig. 4)

The on-chip data memory consists of a 64, 128 or 256 byte RAM. All locations are indirectly addressable using two RAM pointer registers R0, R1 or R0', R1'. The first 8 RAM locations (0 to 7) are designated as working register bank 0 and are directly addressable. By selecting register bank 1, RAM locations 24 to 31 become the working registers. RAM locations 8 to 23 are designated as the stack. Two bytes are used per CALL allowing up to 8 levels of subroutine nesting. An extra 256 bytes of RAM may be added and addressed directly using the MOVX instructions. If more RAM is required, I/O port lines may be used to select additional (256 byte) banks of external memory.

## Program counter and stack

The program counter (PC) is a 12-bit counter/register that points to the location from which the next instruction is to be fetched. When EA is logic 0 the PC can address locations 0 to 1023 (8048H), 2047 (8049H) or 4095 (8050H) of internal program memory. At the 1 K (8048H), 2 K (8049H) boundary, an automatic switch-over to external memory occurs. When EA is logic 1 all fetches are from external program memory. The total address space is 4 K bytes. An interrupt or subroutine CALL causes the contents of the program counter to be stored in one of the 8 register pairs of the program counter stack. A 3-bit stack pointer which is part of the program status word (PSW) points to the relevant register pair. Data RAM locations 8 to 23 are available as stack registers and are used to store the program counter and 4 bits of the PSW register. The stack pointer, when initialized to 000, points to RAM locations 8 and 9. The first subroutine jump or interrupt results in the program counter contents being transferred to locations 8 an 9 of the RAM array. The stack pointer is then incremented by one to point to locations 10 and 11. Nesting of subroutines within subroutines can continue up to 8 times without overflowing the stack. If overflow does occur the deepest address stored (locations 8 and 9) will be overwritten and lost since the stack pointer overflows from 111 to 000. It also underflows from 000 to 111. The end of a subroutine, which is signalled by a return instruction (RET or RETR), causes the stack pointer to be decremented and the contents of the appropriate register pair to be transferred to the program counter.

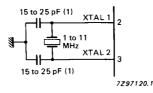

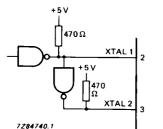

## Oscillator and clock (see Figs 5, 6 and 7)

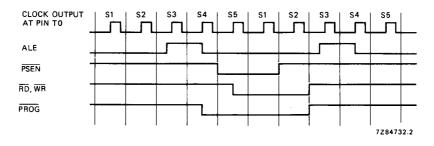

The MAB80XXH has on-chip oscillator and clock driver circuitry. A crystal, LC-network or external timing signal (pulse generator) determines the oscillator frequency. The output of the oscillator is divided-by-three and is available at T0 (pin 1) by executing the ENTO CLK instruction. This clock signal (CLK) is divided-by-five to define a machine (instruction) cycle. It is available at ALE (pin 11).

(1) Including crystal-socket stray capacities.

Fig. 5 Crystal oscillator mode. Crystal series impedance should be < 75  $\Omega$  at 6 MHz and < 180  $\Omega$  at 3,6 MHz. When using a ceramic oscillator both capacitors should be 30 pF.

.

Fig. 6 External clock source. Both XTAL 1 and XTAL 2 should be driven. Resistors to  $V_{CC}$  (+ 5 V) are required to ensure  $V_{IH} = 3,8$  V if TTL circuitry is used. The minimum HIGH and LOW times are 45%.

|                            | f ≈ · C' | $=\frac{C+3C_{pp}}{2}$ | L<br>(µH) | C<br>(pF) | nom. f<br>(MHz) |

|----------------------------|----------|------------------------|-----------|-----------|-----------------|

| LC XTAL2<br>3<br>7284738.1 | 1~2π√LC′ | 2                      | 45<br>120 | 20<br>20  | 5,2<br>3,2      |

Fig. 7 LC oscillator. Each capacitor should be  $\approx$  20 pF including stray capacitance  $C_{pp}\approx$  5 to 10 pF (pin-to-pin capacitance).

#### Timer/event counter

An internal counter is available which can count either external events or machine cycles (÷32). The machine cycles are divided-by-32 before they are applied to the input of the 8-bit counter. External events are applied directly to the input of the counter. The maximum clock rate is one third of the machine cycle frequency. The minimum positive duty cycle that can be detected is 0,2 times the cycle period. The counter can be configured to generate an interrupt to the processor when it overflows.

#### Interrupt

An interrupt may be generated by:

- An external input INT (pin 6) or

- A timer/counter overflow, when enabled.

In either event, the processor completes execution of the present instruction and then calls the interrupt service routine.

At the end of the interrupt service routine, a RETR instruction restores the machine to the state it was in prior to the interrupt. The external interrupt has priority over the timer/counter interrupt.

#### Input/output

The MAB80XXH has 27 I/O lines arranged as three 8-bit ports and 3 'test' inputs that can alter program sequences when tested by conditional jump instructions.

Each port line can be individually configured as an input or output.

#### FUNCTIONAL DESCRIPTION (continued)

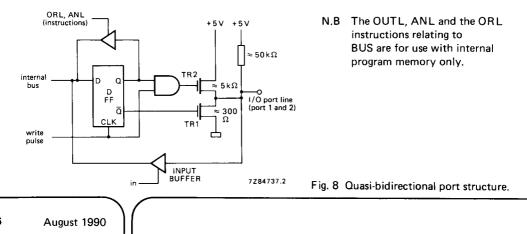

Ports 1 and 2 are both 8-bits wide and have identical characteristics. Data written to these ports is latched and remains unchanged until rewritten. In the input mode, these ports are non-latching; inputs must be present until read by an input instruction. Inputs are fully TTL compatible and outputs will drive one standard TTL load.

Ports 1 and 2 are called quasi-bidirectional because they are not high impedance when configured as inputs. Each line is pulled up to + 5 V through a resistor ( $\approx 50 \Omega$ ). This pull-up provides sufficient source current for a TTL HIGH level, yet can be pulled LOW by a standard TTL gate, thus allowing the pin to be used both as an input and an output. To provide fast switching times during a logic 0 - to - 1 transition, transistor TR 2 is switched on for one fifth of a machine cycle when a logic 1 is written to the line. When a logic 0 is written, transistor TR 1 overcomes the pull-up and provides TTL current sinking capability. Since the pull-down transistor is low impedance, a logic 1 must first be written to any line which is to used as an input. RESET initializes all lines to the high impedance logic 1 state. This structure allows input and output on the same pin. Individual port lines can be read and written using the ANL and ORL instructions.

#### BUS (DB0-DB7)

BUS is a true bidirectional 8-bit port with associated input and output strobes. The BUS port can operate in three different modes: as a latched I/O port, as a bidirectional bus port, or in an expanded system as a program memory address output port. If the bidirectional feature is not needed, BUS can serve as either a statically latched output port or non-latching input port. Input and output lines on this port cannot be mixed. The BUS port lines are either active HIGH, active LOW, or high impedance (floating).

As a static port, data is written and latched using the OUTL instruction and input using the INS in instruction. The INS and OUTL instructions generate pulses on the corresponding  $\overline{RD}$  and  $\overline{WR}$  output strobe lines; however, in the static port mode they are generally not used. As a bidirectional port, the MOVX instructions are used to read and write the port. A write to the port generates a pulse on the  $\overline{WR}$  output line and output data is valid at the trailing edge of  $\overline{WR}$ . A read of the port generates a pulse on the  $\overline{RD}$  output line and input data must be valid at the trailing edge of  $\overline{RD}$ .

The latched mode (INS, OUTL) is intended for use in the single-chip configuration, where BUS is not being used as an expanded port. OUTL and MOVX instructions can be mixed if required. However, when using a MOVX instruction a previously latched output will be lost and BUS will be left in the high impedance state. INS does not put the BUS in a high impedance state. Therefore, in order to read an external byte (and not the previously latched value) using an INS instruction, it is necessary to precede INS with a MOVX instruction.

OUTL should never be used in a system with external program memory, since latching BUS may cause the next instruction to be incorrectly fetched.

### Test (T0, T1) and INT

These three pins serve as inputs and may be tested by the conditional jump instruction. They allow inputs to cause program branches without the necessity of loading an input port into the accumulator.

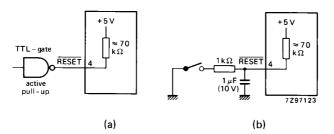

#### RESET (see Fig. 9)

This active LOW input is used to initialize the microcontroller.

This Schmitt-trigger input has an internal pull-up resistor which, in combination with an external 1  $\mu$ F capacitor, provides an internal reset pulse of sufficient duration to reset all circuitry. If the reset pulse is generated externally, the reset pin must be held at ground (0,45 V) for at least 10 ms after the power supply is within tolerance. Only 5 machine cycles (12,5  $\mu$ s at 6 MHz) are required if power is already on and the oscillator has stabilized.

Fig. 9 An external reset is shown in (a) and power-on reset in (b).

#### Single step (SS)

This active LOW input when used in combination with ALE will cause the microcontroller to execute a single instruction, then wait until  $\overline{SS}$  is reactivated.

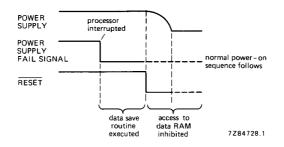

#### Power-down mode (see Fig. 10)

In the MAB80XXH, power can be removed from all but the data RAM array, for low power standby operation. In the power-down mode the contents of the data RAM can be maintained while drawing typically 10% to 15% of the normal operating supply voltage. V<sub>CC</sub> serves as the +5 V supply pin for the bulk of the circuitry, while the V<sub>DD</sub> pin supplies only the RAM array. In normal operation, both pins are at +5 V. In the standby mode, V<sub>CC</sub> is at ground and only V<sub>DD</sub> is maintained at +5 V. Applying RESET to the microcontroller through the reset pin inhibits any access to the RAM and ensures that the RAM cannot be inadvertently altered as power is removed from V<sub>CC</sub>.

Fig. 10 Power down sequence.

2-37

#### FUNCTIONAL DESCRIPTION (continued)

#### Instruction set (see Tables 1, 2, 3 and 4)

The MAB80XXH instruction set consists of over 90 one and two-byte instructions. Program code efficiency is high because:

- Working registers and program variables are stored in RAM locations 0 to 127, which require only a single byte to address

- Program memory is divided into pages of 256 bytes, which means that branch destination addresses require only one byte

The instruction set performs logical, arithmetic and test operations on bytes. It also manipulates and tests bits. A set of MOVE instructions operate indirectly on either RAM or ROM, which permits efficient access of pointers and data tables. The indirect jump instruction performs a multi-way branch (up to 256) on the contents of the accumulator to addresses stored in a look-up table. The 'decrement register and jump if not zero' instruction saves a byte each time it is used as opposed to using separate increment and test instructions. The on-chip counter provides the facility for external events or time to be counted by hardware which does not interfere with the main program. The MAB80XXH can either test the counter (under program control) or cause its overflow to generate an interrupt. These features are essential for real-time applications.

| Aaccumulatoraddrprogram memory addressBbbit designation (b = 07)RBSregister bank selectCcarry (bit CY)CNTevent counterDmnemonic for 4-bit digit (nibble)data8-bit number or expressionIinterruptMBmemory bankMBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by↔is exchanged with       | symbol | definition description              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------|

| Bbbit designation (b = 07)RBSregister bank selectCcarry (bit CY)CNTevent counterDmnemonic for 4-bit digit (nibble)data8-bit number or expressionIinterruptMBmemory bankMBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#immediate data prefix@indirect address prefix(X)contents of location addressed by X←is replaced by                                                           | A      | accumulator                         |

| RBSregister bank selectCcarry (bit CY)CNTevent counterDmnemonic for 4-bit digit (nibble)data8-bit number or expressionIinterruptMBmemory bankMBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                         | addr   |                                     |

| Ccarry (bit CY)CNTevent counterDmnemonic for 4-bit digit (nibble)data8-bit number or expressionIinterruptMBmemory bankMBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                | Bb     | bit designation (b = $0-7$ )        |

| CNTevent counterDmnemonic for 4-bit digit (nibble)data8-bit number or expressionIinterruptMBmemory bankMBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                               | RBS    | register bank select                |

| Dmnemonic for 4-bit digit (nibble)data8-bit number or expressionIinterruptMBmemory bankMBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                               | С      | carry (bit CY)                      |

| data8-bit number or expressionIinterruptMBmemory bankMBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                 | CNT    | event counter                       |

| IinterruptMBmemory bankMBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                                               | D      | mnemonic for 4-bit digit (nibble)   |

| MBmemory bankMBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                                                         | data   | 8-bit number or expression          |

| MBFFmemory bank flip-flopPmnemonic for 'in-page' operationPCprogram counterPpport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                                                                      | 1      | interrupt                           |

| P       mnemonic for 'in-page' operation         PC       program counter         Pp       port designation (p = 0, 1, 2)         PSW       program status word         RB       register bank         Rr       register designation (r = 0-7)         Sn       serial I/O register         SP       stack pointer         T       timer         TF       timer flag         TO       test 0 input         T1       test 1 input         #       immediate data prefix         @       indirect address prefix         (X)       contents of X         ((X))       contents of location addressed by X | MB     | memory bank                         |

| PCprogram counterPpport designation $(p = 0, 1, 2)$ PSWprogram status wordRBregister bankRrregister designation $(r = 0-7)$ Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#indirect address prefix(X)contents of X((X))contents of location addressed by X $\leftarrow$ is replaced by                                                                                                                                                                                                                                                                             | MBFF   |                                     |

| Ppport designation (p = 0, 1, 2)PSWprogram status wordRBregister bankRrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagTOtest 0 inputT1test 1 input#immediate data prefix@indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                                                                                                                           | Р      | mnemonic for 'in-page' operation    |

| PSW     program status word       RB     register bank       Rr     register designation (r = 0-7)       Sn     serial I/O register       SP     stack pointer       T     timer       TF     timer flag       TO     test 0 input       T1     test 1 input       #     immediate data prefix       @     indirect address prefix       (X)     contents of X       ((X))     contents of location addressed by X       ←     is replaced by                                                                                                                                                          | PC     | program counter                     |

| RB     register bank       Rr     register designation (r = 07)       Sn     serial I/O register       SP     stack pointer       T     timer       TF     timer flag       TO     test 0 input       T1     test 1 input       #     immediate data prefix       @     indirect address prefix       (X)     contents of X       ((X))     contents of location addressed by X       ←     is replaced by                                                                                                                                                                                             | Рр     | port designation ( $p = 0, 1, 2$ )  |

| Rrregister designation (r = 0-7)Snserial I/O registerSPstack pointerTtimerTFtimer flagT0test 0 inputT1test 1 input#immediate data prefix@indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                                                                                                                                                                                                | PSW    | program status word                 |

| Sn     serial I/O register       SP     stack pointer       T     timer       TF     timer flag       T0     test 0 input       T1     test 1 input       #     immediate data prefix       @     indirect address prefix       (X)     contents of X       ((X))     contents of location addressed by X       ←     is replaced by                                                                                                                                                                                                                                                                   | RB     |                                     |

| SP       stack pointer         T       timer         TF       timer flag         TO       test 0 input         T1       test 1 input         #       immediate data prefix         @       indirect address prefix         (X)       contents of X         ((X))       contents of location addressed by X         ←       is replaced by                                                                                                                                                                                                                                                              | Rr     | register designation ( $r = 0-7$ )  |

| TtimerTFtimer flagTOtest 0 inputT1test 1 input#immediate data prefix@indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                                                                                                                                                                                                                                                                    | Sn     | serial I/O register                 |

| TFtimer flagT0test 0 inputT1test 1 input#immediate data prefix@indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                                                                                                                                                                                                                                                                          | SP     | stack pointer                       |

| T0test 0 inputT1test 1 input#immediate data prefix@indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                                                                                                                                                                                                                                                                                      | т      | timer                               |

| T1test 1 input#immediate data prefix@indirect address prefix(X)contents of X((X))contents of location addressed by X←is replaced by                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TF     | timer flag                          |

| <ul> <li># immediate data prefix</li> <li>@ indirect address prefix</li> <li>(X) contents of X</li> <li>((X)) contents of location addressed by X</li> <li>← is replaced by</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 | т0     | test 0 input                        |

| <ul> <li>@ indirect address prefix</li> <li>(X) contents of X</li> <li>((X)) contents of location addressed by X</li> <li>← is replaced by</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | T1     | test 1 input                        |

| <ul> <li>(X) contents of X</li> <li>((X)) contents of location addressed by X</li> <li>← is replaced by</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | #      | immediate data prefix               |

| ((X)) contents of location addressed by X<br>← is replaced by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -      |                                     |

| ← is replaced by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (X)    |                                     |

| , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ((X))  | contents of location addressed by X |

| ↔ is exchanged with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ←      | is replaced by                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ↔      | is exchanged with                   |

Table 1 Symbols and definitions used in Table 2.

| Instruction set |  |

|-----------------|--|

| Table 2         |  |

| notes            | -                          | <del>~~</del>                        | -                       | -                                    | -                                                | -                                 | . <del>.</del>    | <u> </u>                                   | <del></del>                 |                 |                                        |                            |                  |                                          |                             |                  |                  |                 |                    |                                                                               |

|------------------|----------------------------|--------------------------------------|-------------------------|--------------------------------------|--------------------------------------------------|-----------------------------------|-------------------|--------------------------------------------|-----------------------------|-----------------|----------------------------------------|----------------------------|------------------|------------------------------------------|-----------------------------|------------------|------------------|-----------------|--------------------|-------------------------------------------------------------------------------|

|                  | r = 0–7                    |                                      |                         | r = 0–7                              |                                                  |                                   | r = 0–7           |                                            |                             | r = 07          |                                        |                            | r = 07           |                                          |                             |                  |                  |                 |                    | n = 0—6                                                                       |

| function         | (A)←(A) + (Rr)             | (A)+(A) + ((R0))<br>(A)+(A) + ((R1)) | (A)←(A) + data          | (A)++(A) + (Rr) + (C)                | (A)+(A) + ((R0)) + (C)<br>(A)+(A) + ((R1)) + (C) | (A)←(A) + data + (C)              | (A)+-(A) AND (Rr) | (A)++(A) AND ((R0))<br>(A)++(A) AND ((R1)) | (A)←(A) AND data            | (A)←(A) OR (Rr) | (A)←(A) OR ((R0))<br>(A)←(A) OR ((R1)) | (A)←(A) OR data            | (A)←(A) XOR (Rr) | (A)←(A) XOR ((R0))<br>(A)←(A) XOR ((R1)) | (A)←(A) XOR data            | (A)←(A) + 1      | (A)+(A) − 1      | (A)≁0           | (A)←NOT(A)         | (A <sub>n</sub> + 1)←(A <sub>n</sub> )<br>(A <sub>0</sub> )←(A <sub>7</sub> ) |

| description      | Add register contents to A | Add RAM data, addressed by Rr, to A  | Add immediate data to A | Add carry and register contents to A | Add carry and RAM data, addresses by Rr, to A    | Add carry and immediate data to A | AND' Rr with A    | 'AND' RAM data, addressed by Rr, with A    | 'AND' immediate data with A | 'OR' Rr with A  | 'OR' RAM data, addressed by Rr, with A | 'OR' immediate data with A | 'XOR' Rr with A  | 'XOR' RAM, addressed by Rr, with A       | 'XOR' immediate data with A | increment A by 1 | decrement A by 1 | clear A to zero | one's complement A | rotate A left                                                                 |

| bytes/<br>cycles | 1/1                        | 1/1                                  | 2/2                     | 1/1                                  | 1/1                                              | 2/2                               | 1/1               | 1/1                                        | 2/2                         | 1/1             | 1/1                                    | 2/2                        | 1/1              | 1/1                                      | 2/2                         | 1/1              | 1/1              | 1/1             | 1/1                | 1/1                                                                           |

| opcode<br>(hex.) | 6*                         | 60<br>61                             | 03 data                 | 7*                                   | 70<br>71                                         | 13 data                           | <u>ئ</u>          | 50<br>51                                   | 53 data                     | 4*              | 40<br>41                               | 43 data                    | *0               | 00<br>10                                 | D3 data                     | 17               | 07               | 27              | 37                 | E7                                                                            |

| mnemonic         | ADD A, Rr                  | ADD A, @Rr                           | ADD A, #data            | ADDC A, Rr                           | ADDC A, @Rr                                      | ADDC A, #data                     | ANL A, Rr         | ANL A, @Rr                                 | ANL A, #data                | ORL A, Rr       | ORL A, @Rr                             | ORL A, #data               | XRL A, Rr        | XRL A, @Rr                               | XRL A, #data                | INC A            | DEC A            | CLR A           | CPL A              | RL A                                                                          |

|                  |                            |                                      |                         |                                      |                                                  |                                   |                   | ย                                          | οτν                         | חר⊳             | าพักอะ                                 | DΑ                         |                  |                                          |                             |                  |                  |                 |                    |                                                                               |

August 1990

2-3<del>9</del>

| notes            | 2                                                                                      |                                                               | 2                                                                            | 2                |                   |                             |                                      |                          |                                       |                                                           |                           |                                                     |                                       |                                                                |                                                          | _                                | с                                |                                                     |                          |

|------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------|------------------|-------------------|-----------------------------|--------------------------------------|--------------------------|---------------------------------------|-----------------------------------------------------------|---------------------------|-----------------------------------------------------|---------------------------------------|----------------------------------------------------------------|----------------------------------------------------------|----------------------------------|----------------------------------|-----------------------------------------------------|--------------------------|

|                  | 9—0 = u                                                                                | n = 0—6                                                       | n = 06                                                                       |                  |                   | r = 0–7                     |                                      |                          | r = 0–7                               |                                                           | r = 07                    |                                                     | r = 0–7                               |                                                                |                                                          |                                  |                                  |                                                     | in page 3                |

| function         | (A <sub>n</sub> + 1)←(A <sub>n</sub> )<br>(A <sub>n</sub> )←(C), (C)←(A <sub>7</sub> ) | $(A_{n}) \leftarrow (A_{n} + 1)$ $(A_{7}) \leftarrow (A_{0})$ | $(A_n) \leftarrow (A_n + 1)$<br>$(A_7) \leftarrow (C), (C) \leftarrow (A_0)$ |                  | (A4-7)↔(A0-3)     | (A)←(Rr)                    | (A)←((R0))<br>(A)←((R1))             | (A)←data                 | (Rr)←(A)                              | ((R0))←(A)<br>((R1))←(A)                                  | (Rr)←data                 | ((R0))←data<br>((R1))←data                          | (A)↔(Rr)                              | (A)↔((R0))<br>(A)↔((R1))                                       | (A0_3)↔((R00_3))<br>(A0_3)↔((R10_3))                     | (A)→(PSW)                        | (PSW)→(A)                        | ((V))→(V)                                           | ((A)→(A))                |

| description      | rotate A left through carry                                                            | rotate A right                                                | rotate A right through carry                                                 | decimal adjust A | swap nibbles of A | move register contents to A | move RAM data, addressed by Rr, to A | move immediate data to A | move accumulator contents to register | move accumulator contents to RAM location addressed by Rr | move immediate data to Rr | move immediate data to RAM location addressed by Rr | exchange accumulator contents with Rr | exchange accumulator contents with<br>RAM data addressed by Rr | exchange lower nibbles of A and RAM data addressed by Rr | move PSW contents to accumulator | move accumulator contents to PSW | move indirectly addressed data in current page to A | move data in page 3 to A |

| bytes/<br>cycles | 1/1                                                                                    | 1/1                                                           | 1/1                                                                          | 1/1              | 1/1               | 1/1                         | 1/1                                  | 2/2                      | 1/1                                   | 1/1                                                       | 2/2                       | 2/2                                                 | 1/1                                   | 1/1                                                            | 1/1                                                      | 1/1                              | 1/1                              | 1/2                                                 | 1/2                      |

| opcode<br>(hex.) | F7                                                                                     | 77                                                            | 67                                                                           | 57               | 47                | *                           | F0<br>F1                             | 23 data                  | *A                                    | A0<br>A1                                                  | B* data                   | B0 data<br>B1 data                                  | 2*                                    | 20<br>21                                                       | 30<br>31                                                 | c7                               | D7                               | A3                                                  | E3                       |

| mnemonic         | RLC A                                                                                  | RR A                                                          | RRC A                                                                        | DA A             | SWAP A            | MOV A, Rr                   | MOV A, @Rr                           | MOV A, #data             | MOV Rr, A                             | MOV @Rr, A                                                | MOV Rr, #data             | MOV @rR, #data                                      | XCH A, Rr                             | XCH A, @Rr                                                     | XCHD A, @Rr                                              | MOV A, PSW                       | MOV PSW, A                       | MOVP A, @A                                          | MOVP3 A,@A               |

|                  | (cont.)                                                                                | яот∧                                                          | /ากพก                                                                        | าวว              | A                 |                             |                                      |                          |                                       |                                                           | S3/                       | OM A                                                | ΤA                                    |                                                                |                                                          |                                  |                                  |                                                     |                          |

2-40

August 1990

|                                                    |                                                       | 2               | 2                    |                         |                                      |                   |                         |                                      |                                         |                             | -                                 |                               |                                     |                                      |                                              |                                    |                                    |                                     |                                  |                                           |                                      |                                     |                                      |                                      | 4                                       |

|----------------------------------------------------|-------------------------------------------------------|-----------------|----------------------|-------------------------|--------------------------------------|-------------------|-------------------------|--------------------------------------|-----------------------------------------|-----------------------------|-----------------------------------|-------------------------------|-------------------------------------|--------------------------------------|----------------------------------------------|------------------------------------|------------------------------------|-------------------------------------|----------------------------------|-------------------------------------------|--------------------------------------|-------------------------------------|--------------------------------------|--------------------------------------|-----------------------------------------|

| r = 0–1                                            | r = 0–1                                               |                 |                      | r = 07                  |                                      |                   | r = 0–7                 |                                      |                                         |                             | r = 0–7                           |                               |                                     |                                      |                                              | b = 0–7                            |                                    |                                     |                                  |                                           |                                      |                                     |                                      |                                      |                                         |

| (A)←((R))                                          | ((R))+(A)                                             | (C)+0           | (C)←NOT(C)           | (Rr)↔(Rr) + 1           | ((R0))←((R0)) + 1                    | ((R1))+((R1)) + 1 | (Rr)←(Rr) –1            | (PC8-10)←addr8-10                    | (PC0_7)←addr0_7<br>  (PC11 12)←MBFF 0_1 | (PC <sub>0−7</sub> )+((A))  | (Rr)←(Rr) -1                      | if (Rr) not zero (PC0_7)←addr | if F0 = 1: (PC <sub>07</sub> )←addr | if F1 = 1: (PC <sub>0−7</sub> )←addr | if <u>INT</u> = 0: (PC <sub>0−7</sub> )←addr | if b = 1: (PC <sub>07</sub> )←addr | if C = 1: (PC <sub>07</sub> )←addr | if C = 0: (PC <sub>07</sub> )+-addr | if A = 0: $(PC_{0-7})^{+-}$ addr | if A $\neq 0$ : (PC <sub>0-7</sub> )+addr | if T0 = 1: (PC <sub>0-7</sub> )←addr | if T0 = 0: (PC <sub>07</sub> )←addr | if T1 = 1: (PC <sub>0-7</sub> )←addr | if T1 = 0: (PC <sub>0-7</sub> )←addr | if TF = 1: $(PC_{0-7}) \leftarrow addr$ |

| move indirect the contents of external memory to A | move indirect the contents of A to<br>external memory | clear carry bit | complement carry bit | increment register by 1 | increment RAM data, addressed by Rr, | by 1              | decrement register by 1 | unconditional jump within a 2 K bank |                                         | indirect jump within a page | decrement Rr by 1 and jump if not | zero to addr                  | jump to addr if F0 = 1              | jump to addr if $F1 = 1$             | jump to addr if $INT = 0$                    | jump to addr if Acc. bit $b = 1$   | jump to addr if $C = 1$            | jump to addr if $C = 0$             | jump to addr if $A = 0$          | jump to addr if A is NOT zero             | jump to addr if $TO = 1$             | jump to addr if $T0 = 0$            | jump to addr if $T1 = 1$             | jump to addr if $T1 = 0$             | jump to addr if Timer Flag = 1          |

| 1/2                                                | 1/2                                                   | 1/1             | 1/1                  | 1/1                     | 1/1                                  |                   | 1/1                     | 2/2                                  |                                         | 1/2                         | 2/2                               |                               | 2/2                                 | 2/2                                  | 2/2                                          | 2/2                                | 2/2                                | 2/2                                 | 2/2                              | 2/2                                       | 2/2                                  | 2/2                                 | 2/2                                  | 2/2                                  | 2/2                                     |

| 80<br>81                                           | 90<br>91                                              | 97              | A7                   | *                       | 10                                   | 11                | ť                       | • 4 address 2/2                      |                                         | B3                          | E* address 2/2                    |                               | B6 address                          | 76 address                           | 86 address                                   | ▲ 2 address                        | F6 address                         | E6 address                          | C6 address                       | 96 address                                | 36 address                           | 26 address                          | 56 address                           | 46 address                           | 16 address                              |

| MOVX A,@Rr                                         | MOVX @Rr,A                                            | CLR C           | CPL C                | INC Rr                  | INC @Rr                              |                   | DEC Rr                  | JMP addr                             |                                         | JMPP @A                     | DJNZ Rr, addr                     |                               | JF0 addr                            | JF1 addr                             | JNI addr                                     | JBb addr                           | JC addr                            | JNC addr                            | JZ addr                          | JNZ addr                                  | JT0 addr                             | JNT0 addr                           | JT1 addr                             | JNT1 addr                            | JTF addr                                |

| ·                                                  |                                                       | SD              | 4.1∃                 | 8                       | этs                                  | 19                | 38                      |                                      |                                         |                             |                                   |                               |                                     |                                      | нэ                                           | NA §                               | BF                                 |                                     |                                  | _                                         |                                      |                                     |                                      |                                      |                                         |

| notes            |                                                  |                                                     |                     |             |                          |                                      |                                       |                           |                            | ß                      | ß                      |                              |                              |                             | 9                         |                                       |                    | 9                            | 9                                                        |

|------------------|--------------------------------------------------|-----------------------------------------------------|---------------------|-------------|--------------------------|--------------------------------------|---------------------------------------|---------------------------|----------------------------|------------------------|------------------------|------------------------------|------------------------------|-----------------------------|---------------------------|---------------------------------------|--------------------|------------------------------|----------------------------------------------------------|

| function         | (A)←(T)                                          | {T)←(A)                                             |                     |             |                          |                                      |                                       |                           |                            | (RBS)←0                | (RBS)←1                | (MBFF0)←0, (MBFF1)←0         | (MBFF0)←1, (MBFF1)←0         |                             | ((SP))←(PC), (PSW4, 6, 7) | $(PC_{8-1})^{\leftarrow} = ddr_{8-1}$ | (PC11-12)←MBFF 0-1 | (SP)←(SP) - 1<br>(PC)←((SP)) | (SP)←(SP) −1<br>(PSW4, 6, 7) + (PC)←((SP))               |

| description      | move timer/event counter contents to accumulator | move accumulator contents to<br>timer/event counter | start event counter | start timer | stop timer/event counter | enable timer/event counter interrupt | disable timer/event counter interrupt | enable external interrupt | disable external interrupt | select register bank 0 | select register bank 1 | select program memory bank 0 | select program memory bank 1 | enable clock output onto TO | jump to subroutine        |                                       |                    | return from subroutine       | return from interrupt and restore<br>bits 4, 6, 7 of PSW |

| bytes/<br>cycles | 1/1                                              | 1/1                                                 | 1/1                 | 1/1         | 1/1                      | 1/1                                  | 1/1                                   | 1/1                       | 1/1                        | 1/1                    | 1/1                    | 1/1                          | 1/1                          | 1/1                         | 2/2                       |                                       |                    | 1/2                          | 1/2                                                      |

| opcode<br>(hex.) | 42                                               | 62                                                  | 45                  | 55          | 65                       | 25                                   | 35                                    | 05                        | 15                         | C5                     | D5                     | E5                           | F5                           | 75                          | ▲ 4 address               |                                       |                    | 83                           | 93                                                       |

| mnemonic         |                                                  |                                                     |                     |             |                          | EN TCNTI                             | DIS TCNTI                             | ENI                       | DISI                       |                        | SEL RB1                | SEL MBO                      | SEL MB1                      | ENTO CLK                    | CALL addr                 |                                       |                    | RET                          | RETR                                                     |

|                  | ЯЭТІ                                             | сопи                                                | ΤN                  | ΞΛE         | 3/8                      | эМ                                   | ι1                                    |                           |                            | 101                    | ΗTV                    | 100                          |                              |                             |                           | INE                                   | no                 | ษยกร                         |                                                          |

August 1990 2-42

|         | OUTL BUS,A                                                                                       | 02                                                                              | 1/2    | output accumulator to BUS                                                                                                                                                                                                                      | (BUS)←A                                  |                                                                |                 |

|---------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------|-----------------|

|         | IN A,Pp                                                                                          | 60 Q                                                                            | 1/2    | input port p data to accumulator                                                                                                                                                                                                               | (A)←(P1)<br>(A)←(P2)                     | p = 1–2                                                        | 7               |

|         | INS A, BUS                                                                                       | 80                                                                              | 1/2    | input strobed BUS data into accumulator                                                                                                                                                                                                        | (A)→(BUS)                                |                                                                |                 |

|         | OUTL Pp,A                                                                                        | 39<br>3A                                                                        | 1/2    | output accumulator data to port p                                                                                                                                                                                                              | (P1)←(A)<br>(P2)←(A)                     | p = 12                                                         |                 |

|         | ANL BUS, # data                                                                                  | 98                                                                              | 2/2    | logical AND immediate data with BUS                                                                                                                                                                                                            | (BUS)←(BUS) AND data                     |                                                                |                 |

|         | ANL Pp, # data                                                                                   | 66<br>96                                                                        | 2/2    | AND port p data with immediate data                                                                                                                                                                                                            | (P1)←(P1) AND data<br>(P2)←(P2) AND data | p = 12                                                         |                 |

| L       | ORL Pp, # data                                                                                   | 89<br>8A                                                                        | 2/2    | OR port p data with immediate data                                                                                                                                                                                                             | (P1)←(P1) OR data<br>(P2)←(P2) OR data   | p = 1–2                                                        |                 |

| .Nd     | ORL BUS, # data                                                                                  | 88                                                                              | 2/2    | logical OR immediate data with BUS                                                                                                                                                                                                             | (BUS)←(BUS) OR data                      |                                                                |                 |

| TUO\TU9 | MOVD A,Pp                                                                                        | 00 80<br>0 80                                                                   | 1/2    | move contents of designated port $(4-7)$ to A                                                                                                                                                                                                  | (A0_3)←(Pp)<br>(A4_7)←0                  | p = 4-7                                                        |                 |

| JI      | MOVD Pp,A                                                                                        | ar<br>ar<br>ar<br>ar<br>ar<br>ar<br>ar<br>ar<br>ar<br>ar<br>ar<br>ar<br>ar<br>a | 1/1    | move contents of A to designated port (4–7)                                                                                                                                                                                                    | (Pp)←(A <sub>0</sub> 3)                  | p = 4–7                                                        |                 |