# Rabbit 3000<sup>®</sup> Microprocessor

## Designer's Handbook

019-0112 • 030607-B

This manual (or an even more up-to-date revision) is available for free download at the Rabbit website: www.rabbitsemiconductor.com

## Rabbit $3000^{ ext{(R)}}$ Microprocessor Designer's Handbook

Part Number 019-0112 • 030607-B • Printed in U.S.A.

©2003 Rabbit Semiconductor • All rights reserved.

Rabbit Semiconductor reserves the right to make changes and improvements to its products without providing notice.

#### **Trademarks**

Dynamic  $C^{\textcircled{8}}$  is a registered trademark of Z-World  $Z80/Z180^{^{TM}}$  is a trademark of Zilog, Inc.

#### **Rabbit Semiconductor**

2932 Spafford Street Davis, California 95616-6800 USA

Telephone: (530) 757-8400 Facsimile: (530) 757-8402

Web site: http://www.rabbitsemiconductor.com

## **Table of Contents**

| Chapter 1. | Introduction                                             | 1  |

|------------|----------------------------------------------------------|----|

| 1.1        | Summary of Design Conventions                            | 1  |

| Chapter 2. | Rabbit Hardware Design Overview                          | 3  |

|            | Design Conventions                                       |    |

|            | Rabbit Programming Connector                             |    |

|            | Memory Chips                                             |    |

| 2.2        | Oscillator Crystals                                      |    |

|            | Operating Voltages                                       |    |

|            | Power Consumption                                        |    |

|            | Through-Hole Technology                                  |    |

|            | Moisture Sensitivity                                     |    |

| Chapter 3. | Core Design and Components                               | 7  |

| 3.1        | Clocks                                                   | 7  |

| 3.2        | Floating Inputs.                                         | 8  |

| 3.3        | Basic Memory Design                                      |    |

|            | Memory Access Time                                       |    |

| 2.4        | Interfacing External I/O with Rabbit 3000 Designs        |    |

|            | PC Board Layout and Memory Line Permutation              |    |

| 3.5        | PC Board Layout and Electromagnetic Interference         |    |

|            |                                                          |    |

| _          | How Dynamic C Cold Boots the Target System               |    |

| 4.1        | How the Cold Boot Mode Works In Detail                   | 12 |

| 4.2        | Program Loading Process Overview                         |    |

|            | Program Loading Process Details                          | 13 |

| Chapter 5. | Rabbit Memory Organization                               | 15 |

| 5.1        | Physical Memory                                          |    |

|            | Flash Memory                                             |    |

|            | SRAM                                                     |    |

| 5.2        | Basic Memory Configuration                               |    |

| 3.2        | Definition of Terms.                                     |    |

|            | The Base (or Root) Segment                               |    |

|            | Types of Code Best-Suited for the Base Segment           |    |

|            | The Data Segment                                         |    |

|            | The Stack Segment                                        |    |

|            | The Extended Memory Segment                              |    |

| 5.3        | Separate I&D Space                                       |    |

|            | Enable Separate I&D SpaceI&D Space Mappings in Dynamic C |    |

|            | Compiling to RAM                                         |    |

|            | Compiling to Flash                                       |    |

|            | Writing a Flash Driver                                   |    |

|            | Customizing Interrupts                                   |    |

|            | Method #1                                                |    |

| ~ 4        | Method #2                                                |    |

| 5.4        | How The Compiler Compiles to Memory                      |    |

|            |                                                          |    |

|               | Paged Access in Extended Memory                                                               | 28       |

|---------------|-----------------------------------------------------------------------------------------------|----------|

| 5.5           | Memory Planning                                                                               | 29       |

|               | Flash                                                                                         |          |

|               | Static RAM                                                                                    | 29       |

| 5.6           | Making a RAM-Only Board                                                                       | 30       |

|               | Hardware Changes                                                                              | 30       |

|               | Software Changes                                                                              | 30       |

| Chapter 6.    | The Rabbit BIOS                                                                               | 31       |

| 6.1           | Startup Conditions Set by the BIOS                                                            | 32       |

| 6.2           | BIOS Flowchart                                                                                | 33       |

| 6.3           | Internally-Defined Macros.                                                                    | 34       |

|               | Modifying the BIOS                                                                            |          |

|               | Advanced Options                                                                              |          |

| 6.5           | Origin Directives Used by the Compiler                                                        | 37       |

|               | Origin Directive Syntax                                                                       |          |

|               | Origin Directive Semantics                                                                    | 38       |

|               | Defining a Memory Region                                                                      | 38       |

|               | Action Qualifiers                                                                             |          |

|               | I&D Qualifiers                                                                                |          |

|               | Follow Qualifiers                                                                             |          |

|               | Origin Directive Examples Origin Directives in Program Code                                   |          |

| -             | The System Identification and User Blocks  System ID Block Details  Definition of SysIDBlock. | 42       |

|               | Reading the System ID Block                                                                   |          |

|               | Determining the Existence of the System ID Block                                              |          |

|               | Writing the System ID Block                                                                   |          |

| 7.2           | User Block Details                                                                            |          |

|               | Boot Block Issues                                                                             |          |

|               | Reserved Flash Space                                                                          |          |

|               | Reading the User Block                                                                        |          |

| <b>Cl</b> . 0 | Writing the User Block                                                                        |          |

|               | BIOS Support for Program Cloning                                                              |          |

|               | Overview of Cloning                                                                           |          |

| 8.2           | Creating a Clone                                                                              |          |

|               | Steps to Enable and Set Up Cloning                                                            |          |

|               | Steps to Perform Cloning                                                                      |          |

|               | LED Patterns                                                                                  |          |

| 8.3           | Cloning Questions                                                                             |          |

|               | MAC Address                                                                                   |          |

|               | Different Flash Types                                                                         |          |

|               | Different Memory Sizes                                                                        | 55<br>55 |

|               | LIANTED RACIFICATIONS                                                                         | ~ ~      |

| Chapter 9. Low-Power Design and Support                       | 57 |

|---------------------------------------------------------------|----|

| 9.1 Details of the Rabbit 3000 Low-Power Features             | 58 |

| Special Chip Select Features                                  |    |

| Reducing Operating Voltage                                    |    |

| Preferred Crystal Configuration                               |    |

| 9.2 To Further Decrease Power Consumption                     | 60 |

| What To Do When There is Nothing To Do                        | 60 |

| Sleepy Mode                                                   | 60 |

| External 32 kHz Oscillator                                    | 61 |

| Conformal Coating of 32.768 kHz Oscillator Circuit            | 61 |

| Software Support for Sleepy Mode                              | 61 |

| Baud Rates in Sleepy Mode                                     | 62 |

| Debugging in Sleepy Mode                                      | 62 |

| Chapter 10. Supported Flash Memories                          | 63 |

| 10.1 Supporting Other Flash Devices                           | 63 |

| 10.2 Writing Your Own Flash Driver                            | 64 |

| Required Information for Flash Memory                         |    |

| Flash Driver Functions                                        | 65 |

| Chapter 11. Troubleshooting Tips for New Rabbit-Based Systems | 67 |

| 11.1 Initial Checks                                           | 67 |

| 11.2 Diagnostic Tests.                                        | 67 |

| Program to Transmit Diagnostic Tests                          | 67 |

| Diagnostic Test #1: Toggle the Status Pin                     |    |

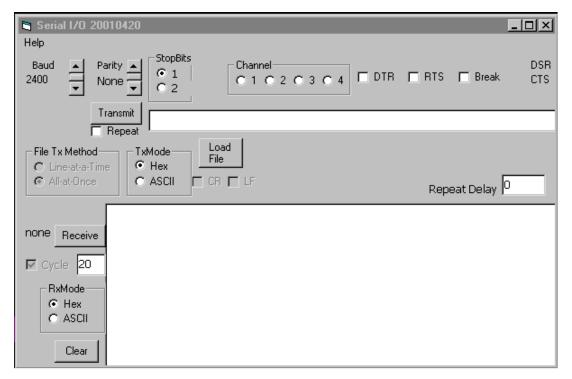

| Using serialIO.exe                                            | 69 |

| Diagnostic Test #2                                            | 70 |

| Appendix A.Supported Rabbit 3000 Baud Rates                   | 73 |

| Notice to Users                                               | 75 |

| Inday                                                         | 77 |

|                                                               |    |

## 1. Introduction

This manual is intended for the engineer designing a system using the Rabbit 3000 microprocessor and Z-World's Dynamic C development environment. It explains how to develop a system that is based on the Rabbit 3000 and can be programmed with Dynamic C.

With Rabbit 3000 microprocessors and Dynamic C, many traditional tools and concepts are obsolete. Complicated and fragile in-circuit emulators are unnecessary. EPROM burners are not needed. Rabbit 3000 microprocessors and Dynamic C work together without elaborate hardware aids, provided that the designer observes certain design conventions.

For all topics covered in this manual, further information is available in the *Rabbit 3000 Microprocessor User's Manual*.

## 1.1 Summary of Design Conventions

- Include a programming connector.

- Connect a static RAM having at least 128 KB to the Rabbit 3000 using /CS1, /OE1 and /WE1.

- Connect a flash memory that is on the approved list and has at least 128 KB of storage to the Rabbit 3000 using /CS0, /OE0 and /WE0.

- Install a crystal oscillator with a frequency of 32.768 kHz to drive the battery-backable clock. (Battery-backing is optional, but the clock is used in the cold boot sequence to generate a known baud rate of 2400 bps.)

- Install a crystal or oscillator for the main processor clock that is a multiple of 614.4 kHz, or better, a multiple of 1.8432 MHz.

- Do not use pin PB1 in your design if cloning is to be used.

- Be sure unused inputs are not floating.

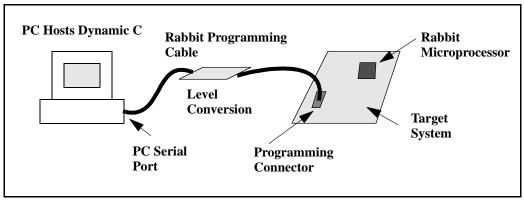

As shown in Figure 1, the Rabbit programming cable connects a PC serial port to the programming connector of the target system. Dynamic C or the Rabbit Field Utility (RFU) runs as an application on the PC, and can cold boot the Rabbit 3000 based target system with no pre-existing program installed in the target. A USB to RS232 converter may also be used instead of a PC serial port. Rabbit 3000 based targets may also be programmed and debugged remotely over a local network or even the Internet using a RabbitLink card.

Figure 1.1 The Rabbit 3000 Microprocessor and Dynamic C

Dynamic C programming uses serial port A for software development. However, it is possible for the user's application to also use serial port A, with the restriction that debugging is not available.

## 2. Rabbit Hardware Design Overview

Because of the glueless nature of the external interfaces, especially the memory interface, it is easy to design hardware in a Rabbit 3000-based system. More details on hardware design are given in the *Rabbit 3000 Microprocessor User's Manual*.

## 2.1 Design Conventions

- Include a standard Rabbit programming cable. The standard 10-pin programming connector provides a connection to serial port A and allows the PC to reset and cold boot the target system.

- Connect a static RAM having at least 128 KB to the processor using /CS1, /OE1 and /WE1.

It is useful if the PC board footprint can also accommodate a RAM large enough to hold all the code anticipated. Although code residing in some flash memory can be debugged, debugging and program download is faster to RAM.

- Connect a flash memory that is on the approved list and has at least 128 KB of storage to the processor using /CS0, /OE0 and /WE0. Non-approved memories can be used, but it may be necessary to modify the BIOS. Some systems designed to have their program reloaded by an external agent on each powerup may not need any flash memory.

- Install a crystal oscillator with a frequency of 32.768 kHz to drive the battery-backable real-time clock (RTC), the watchdog timer (WDT) and the Periodic Interrupt.

- Install a crystal or oscillator for the main processor clock that is a multiple of 614.4 kHz, or better, a multiple of 1.8432 MHz. These preferred clock frequencies make possible the generation of sensible baud rates. Common crystal frequencies to use are 7.3728 MHz, 11.0592 MHz, 14.7456 MHz, 18.432 MHz, 22.1184 MHz, 25.8048 MHz or double these frequencies.

- Digital I/O line PB1 should not be used in the design if cloning is to be used. PB1 should be pulled up with 50K or so pull up resistor if cloning is used. (See "BIOS Support for Program Cloning" on page 53 for more information on cloning.)

### 2.1.1 Rabbit Programming Connector

The user may be concerned that the requirement for a programming connector places added cost overhead on the design. The overhead is very small—less than \$0.25 for components and board space that could be eliminated if the programming connector were not made a part of the system.

The programming connector can also be used for a variety of other purposes, including user applications. A device attached to the programming connector has complete control over the system because it can perform a hardware reset and load new software. If this degree of control is not desired for a particular situation, then certain pins can be left unconnected in the connecting cable, limiting the functionality of the connector to serial communications. Z-World develops products and software that assume the presence of the programming connector.

### 2.1.2 Memory Chips

Most systems have one static RAM chip and one or two flash memory chips, but more memory chips can be used when appropriate. Static RAM chips are available in 32K x 8, 64K x 8, 128K x 8, 256K x 8 and 512K x 8 sizes. They are all available in 3 V versions. Suggested flash memory chips between 128K x 8 and 512K x 8 are given in <u>Chapter 10</u>, Flash Memories.

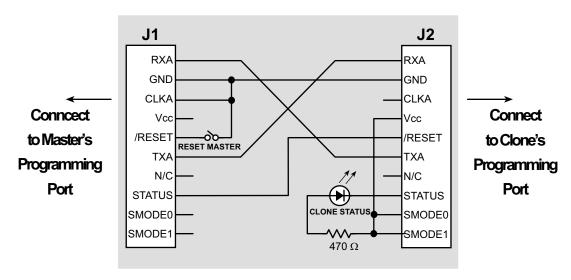

Dynamic C and a PC are not necessary for the production programming of flash memory since the flash memory can be copied from one controller to another by *cloning*. This is done by connecting the system to be programmed to the same type of system that is already programmed. This connection is made with the Rabbit Cloning Board. The Cloning Board connects to the programming ports of both systems. A push of a button starts the transfer of the program and an LED displays the progress of the transfer.

Please visit <a href="http://www.zworld.com/store/index.html">http://www.zworld.com/store/index.html</a> to purchase the Rabbit Cloning Board.

#### 2.1.3 Oscillator Crystals

Generally, a system will have two oscillator crystals:

- A 32.768 kHz crystal oscillator to drive the battery-backable timer,

- A crystal that has a frequency that is a multiple of 614.4 kHz or a multiple of 1.8432 MHz.

Typical values are 1.8432, 3.6864, 7.3728, 11.0592, 14.7456, 18.432, 25.8048, and 29.4912 MHz.

These crystal frequencies (except 614.4 kHz and 1.8432 MHz) allow generation of standard baud rates up to at least 115,200 bps. The clock frequency can be doubled by an on-chip clock doubler, but the doubler should not be used to achieve frequencies higher than about 54 MHz on a 3.3 V system. A quartz crystal should be used for the 32.768 kHz oscillator. For the main oscillator, a ceramic resonator that is accurate to 0.5% will usually be adequate and less expensive than a quartz crystal.

## 2.2 Operating Voltages

The operating voltage in Rabbit 3000 based systems will usually be 3.3 V  $\pm 10\%$ , but voltages in the range of 1.8 V to 2.7 V are also possible. The maximum computation per watt is obtained in the range of 3.0 V to 3.6 V. The highest clock speed requires 3.3 V. The maximum clock speed with a 3.3 V supply is 54 MHz (26.7264 x 2), but it will usually be convenient to use a 14.7456 MHz crystal, doubling the frequency to 29.4912 MHz. Good computational performance, but not the absolute maximum, can be implemented for a 3.3 V system by using an 11.0592 crystal and doubling the frequency to 22.1184 MHz. Such a system will operate with 70 ns memories. A 29.4912 MHz system will require memories with 55 ns access time. A table of timing specification is in the *Rabbit 3000 Microprocessor User's Manual*.

## 2.3 Power Consumption

The following mechanisms are important for determining the current consumption of the Rabbit 3000 while it is operating.

- **1.** A current proportional to voltage and clock frequency that results from the charging of internal and external capacitances. At 3.3 V (see 2 below) approximately 57% of the current is due to charging and 43% to crossover current.

- 2. Current is proportional to clock frequency and to  $V_C = V(0.5 \text{ x V} 0.7)$ . This is the cross-over current that results from a brief short circuit when both the P and N transistors of a CMOS buffer are turned on at the same time. This component drops as the voltage drops relative to the other component, and becomes negligible at 1.4 V.

- 3. The current consumed by the built-in main oscillator when it is turned on. This current is proportional to  $V_C$  above, and is equal to 1 mA at 3.3 V.

- **4.** The current drawn by the logic that is driven at the oscillator (crystal) frequency. This is considered distinctly because it varies with the crystal frequency, but is not reduced when the clock frequency is divided. This current becomes zero if the main oscillator is turned off. This current is 2.5 mA at 3.3 V when the crystal frequency is 14.7 MHz. This current is divided between capacitive and crossover components in the same manner as the currents in (1) and (2) above.

All of the above components can be combined in the following formula:

$$I_{\text{TOTAL}} = 0.32 \times V \times f + 0.23 \times Vc \times f + 0.30 \times Vc + 0.029 \times V \times fc + 0.025 \times Vc \times fc$$

where,

$$V_{C} = V \times (0.5 \times V - 0.7)$$

$$f_{C} = \text{frequency of crystal oscillator}$$

$$f = \text{clock frequency in MHz}$$

## 2.4 Through-Hole Technology

Most design advice given for the Rabbit 3000 assumes the use of surface-mount technology. However, it is possible to use the older through hole technology and develop a Rabbit 3000 system. One can use Z-World's Rabbit 3000-based Core Module, a small circuit board with a complete Rabbit 3000 core that includes memory and oscillators. Another possibility is to solder the Rabbit 3000 processors by hand to the circuit board. This is not difficult and is satisfactory for low production volumes if the right technique is used.

## 2.5 Moisture Sensitivity

Surface-mount processing of plastic packaged components such as Rabbit microprocessors typically involves subjecting the package body to high temperatures and various chemicals such as solder fluxes and cleaning fluids during solder wave and reflow operations. The plastic molding compounds used for IC packaging (encapsulation) is hygroscopic, that is, it readily absorbs moisture. The amount of moisture absorbed by the package is proportional to the storage environment and the amount of time the package is exposed to the humidity in the environment. During the solder reflow process, the package is heated rapidly, and any moisture present in the package will vaporize rapidly, generating excessive internal pressures to various interfaces in the package. The vapors escaping from the package may cause cracks or delamination of the package. These cracks can propagate through the package or along the lead frame, thus exposing the die to ionic contaminants and increasing the potential for circuit failures. The damage to the package may or may not be visible to the naked eye. This condition is common to all plastic surface-mount components and is not unique to Rabbit microprocessors.

Rabbit microprocessors are shipped to customers in moisture-barrier bags with enough desiccant to maintain their contents below 20% relative humidity for up to 12 months from the date of seal. A reversible Humidity Indicator Card is enclosed to monitor the internal humidity level. The loaded bag is then sealed under a partial vacuum. The caution label (IPC/JEDEC J-STD-020, LEVEL 3) included with each bag outlines storage, handling, and bake requirements.

The requirements outlined on the label only apply to components that will be exposed to SMT processing. This means that completed board-level products that will not be subjected to the solder reflow processing do not have to be baked or sealed in special moisture barrier bags.

## 3. Core Design and Components

Core designs can be developed around the Rabbit 3000 microprocessor. A core design includes memory, the microprocessor, oscillator crystals, the Rabbit 3000 standard programming port, and in some cases, a power controller and power supply. Although modern designs usually use at least four-layer printed circuit boards, two-sided boards are a viable option with the Rabbit 3000, especially if the clock speed is not high and the design is intended to operate at 2.5 V or 3.3 V—factors that reduce edge speed and electromagnetic radiation.

Schematics illustrating the use of the Rabbit 3000 microprocessor are available at:

www.rabbitsemiconductor.com

#### 3.1 Clocks

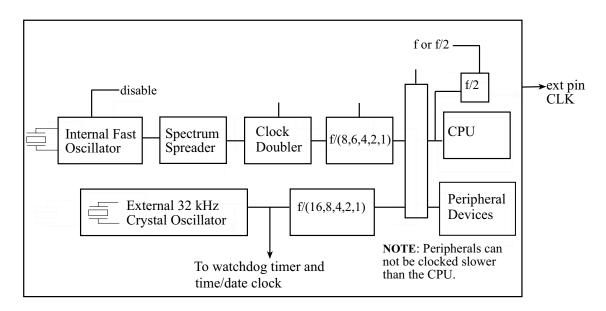

The Rabbit 3000 has a built-in oscillator for the fast clock and an input pin for the 32.768 kHz clock. The fast clock drives the Rabbit 3000 CPU and peripheral clocks, whereas the 32.768 kHz clock is used for the battery backable clock (aka, the real-time clock), the watchdog timer, the periodic interrupt timer and the asynchronous cold boot function.

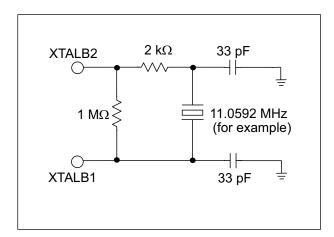

Figure 3-1 Main Oscillator Circuit

The 32.768 kHz oscillator is slow to start oscillating after power-on. For this reason, a wait loop in the BIOS waits until this oscillator is oscillating regularly before continuing the startup procedure. The startup delay may be as much as 5 seconds, but will usually be about 200 ms. Crystals with low series resistance (  $R < 35 \ k\Omega$ ) will start faster.

For more information on the 32.768 kHz oscillator please see Technical Note 235, "External 32.768 kHz Oscillator Circuits." This document is available on our website:

www.rabbitsemiconductor.com.

## 3.2 Floating Inputs

Floating inputs or inputs that are not solidly either high or low can draw current because both N and P FETs can turn on at the same time. To avoid excessive power consumption, floating inputs should not be included in a design (except that some inputs may float briefly during power-on sequencing). Most unused inputs on the Rabbit 3000 can be made into outputs by proper software initialization to remove the floating property. Pull-up resistors will be needed on a few inputs that cannot be programmed as outputs. An alternative to a pull-up resistor is to tie an unused output to the unused inputs. If pull-up (or pull-down) resistors are required, they should be made as large as possible if the circuit in question has a substantial part of its duty cycle with current flowing through the resistor.

## 3.3 Basic Memory Design

Normally /CS0 and /OE0 and /WE0 should be connected to a flash memory that holds the startup code that executes at address zero. When the processor exits reset with (SMODE1, SMODE0) set to (0,0), it will attempt to start executing instructions at the start of the memory connected to /CS0, /OE0, and /WE0.

For Dynamic C to work out of the box, the basic RAM memory must be connected to /CS1, /OE1, and /WE1.

/CS1 has a special property that makes it the preferred chip select for battery-backed RAM. The BIOS defined macro, CS1\_ALWAYS\_ON, may be redefined in the BIOS to 1which will set a bit in the MMIDR register that forces /CS1 to stay enabled (low). This capability can be used to counter a problem encountered when the chip select line is passed through a device that is used to place the chip in standby by raising /CS1 when the power is switched over to battery backup. The battery switchover device typically has a propagation delay that may be 20 ns or more. This is enough to require the insertion of wait states for RAM access in some cases. By forcing /CS1 low, the propagation delay is not a factor because the RAM will always be selected and will be controlled by /OE1 and /WE1. If this is done, the RAM will consume more power while not battery-backed than it would if it were run with dynamic chip select and a wait state. If this special feature is used to speed up access time for battery backed RAM then no other memory chips should be connected to OE1 and WE1.

Table 3.1 Typical Interface between the Rabbit 3000 and Memory

| Primary Flash       | SRAM                | Secondary Flash     |

|---------------------|---------------------|---------------------|

| /CS0, /OE0 and /WE0 | /CS1, /OE1 and /WE1 | /CS2, /OE0 and /WE0 |

### 3.3.1 Memory Access Time

Memory access time depends on the clock speed and the capacitive loading of the address and data lines. Wait states can be specified by programming to accommodate slow memories for a given clock speed. Wait states should be avoided with memory that holds programs because there is a significant slowing of the execution speed. Wait states are far more important in the instruction memory than in the data memory since the great majority of accesses are instruction fetches. Going from 0 to 1 wait states is about the same as reducing the clock speed by 30%. Going from 0 to 2 wait states is worth approximately a 45% reduction in clock speed. A table of memory access times required for various clock speeds is given in the *Rabbit 3000 Microprocessor User's Manual*.

### 3.3.2 Interfacing External I/O with Rabbit 3000 Designs

The Rabbit 3000 provides on-chip facilities for glueless interfacing to many types of external I/O peripherals. The processor provides a common I/O read and I/O write strobe in addition to eight user configurable I/O strobes that can be used as read, write, read/write, or chip select signals. The Rabbit 3000 also provides the option of enabling a completely separate bus for I/O accesses. The Auxiliary I/O Bus, which uses many of the same pins used by Parallel Port A and the Slave Port, provides 8 data lines and 6 address lines that are active only during I/O operations. By connecting I/O devices to the auxiliary bus, the fast memory bus is relieved of capacitive loading that would otherwise slow down memory accesses. For core modules based on the Rabbit 3000, fewer pins are required to exit the core module since the slave port and the I/O bus can share the same pins and the memory bus no longer needs to exit the module to provide I/O capability.

As far as external I/O timing is concerned, the Rabbit 3000 provides:

- half a clock cycle of address and chip select hold time for I/O write operations, and

- zero clock cycles of address and chip select hold times for I/O read operations.

This is true if an I/O device is interfaced to the common memory and I/O bus. However, if an I/O peripheral is interfaced to the Auxiliary I/O bus, address hold time is no longer an issue as the address does not change until the next external I/O operation. For more information on I/O timing please refer to the *Rabbit 3000*<sup>®</sup> *Microprocessor User's Manual*.

Some I/O peripherals such as LCD controllers and Compact Flash devices require address and chip select hold times for both read and write operations. If the peripheral is interfaced to the Auxiliary I/O bus, address hold time is not an issue. If chip select hold time is required, an unused auxiliary I/O address line can be used to generate the chip select. In situations where I/O peripherals are interfaced to the common memory and I/O bus, address and chip select hold times can be extended under software control or with minor hardware changes. Please refer to Technical Note 227, "Interfacing External I/O with Rabbit 2000/3000 Designs" for additional information. This document is available online:

http://www.rabbitsemiconductor.com/docs/app tech notes.shtml

## 3.4 PC Board Layout and Memory Line Permutation

In order to use the PC board real estate efficiently, it is recommended that the address and data lines to memory be permuted to minimize the use of PC board resources. By permuting the lines, the need to have lines cross over each other on the PC board is reduced, saving feed-through's and space.

For static RAM, address and data lines can be permuted freely, meaning that the address lines from the processor can be connected in any order to the address lines of the RAM, and the same applies for the data lines. For example, if the RAM has 15 address lines and 8 data lines, it makes no difference if A15 from the processor connects to A8 on the RAM and vice versa. Similarly D8 on the processor could connect to D3 on the RAM. The only restriction is that all 8 processor data lines must connect to the 8 RAM data lines. If several different types of RAM can be accommodated in the same PC board footprint, then the upper address lines that are unused if a smaller RAM is installed must be kept in order. For example, if the same footprint can accept either a 128K x 8 RAM with 17 address lines or a 512K x 8 RAM with 19 address lines, then address lines A18 and A19 can be interchanged with each other, but not exchanged with A0–A17.

Permuting lines does make a difference with flash memory and must be avoided in practical systems.

## 3.5 PC Board Layout and Electromagnetic Interference

Most design failures are related to the layout of the PC board. A good layout results when the effects of electromagnetic interference (EMI) are considered. For detailed information regarding this subject please see Technical Note 221, "PC Board Layout Suggestion for the Rabbit 3000 Microprocessor." This document is available at:

http://www.rabbitsemiconductor.com/docs/app\_tech\_notes.shtml

#### 3.5.1 Rabbit 3000 Low EMI Features

The Rabbit 3000 has powerful built-in features to minimize EMI. They are noted here. For details please see *The Rabbit 3000 Microprocessor User's Manual*.

- Separate power pins exist for core and I/O rings.

- The I/O bus can be separate from the memory bus.

- The external processor bus cycles are not all the same length.

- The external processor bus does not require running the clock around the PCB.

- The clock spectrum spreader option modulates the clock frequency.

- Some gated internal clocks are enabled only when needed.

- An internal clock doubler allows the external crystal oscillator to operate at 1/2 frequency.

## 4. How Dynamic C Cold Boots the Target System

Dynamic C assumes that target controller boards using the Rabbit 3000 CPU have no pre-installed firmware. It takes advantage of the Rabbit 3000's bootstrap (cold boot) mode, which allows memory and I/O writes to take place over the programming port.

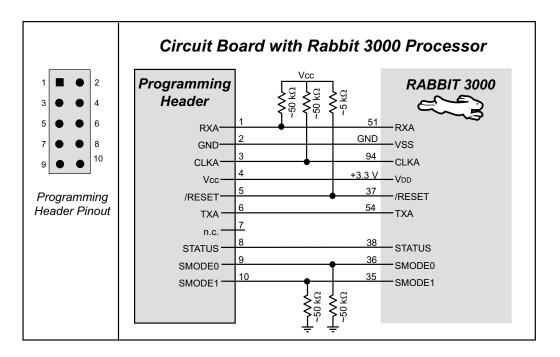

Figure 4-1 Rabbit Programming Port

The Rabbit programming cable is a smart cable with an active circuit board in its middle. The circuit board converts RS-232 voltage levels used by the PC serial port to CMOS voltage levels used by the Rabbit 3000. The level converter is powered from the power supply voltage present on the Rabbit 3000 programming connector. Plugging the programming cable into the Rabbit programming connector results in pulling the Rabbit 3000 SMODE0 and SMODE1 (startup mode) lines high. This causes the Rabbit 3000 to enter the cold boot mode after reset.

When the programming cable connects a PC serial port to the target controller board, the PC running Dynamic C is connected to the Rabbit 3000 as shown in the table below.

Table 4-1 Programming Port Connections

| PC Serial Port Signal | Rabbit 3000 Signal              |

|-----------------------|---------------------------------|

| DTR (output)          | /RESET (input, reset system)    |

| DSR (input)           | STATUS (general purpose output) |

| TX (serial output)    | RXA (serial input, port A)      |

| RX (serial input)     | TXA (serial output, port A)     |

When Dynamic C cold boots the Rabbit 3000-based target system it assumes that no program is already installed on the target. The flash memory on the target system may be blank or it may contain any data. The cold boot capability permits the use of soldered-in flash memory on the target. Soldered-in memory eliminates sockets, boot blocks and PROM programming devices.

#### 4.1 How the Cold Boot Mode Works In Detail

Cold boot works by receiving triplets of bytes that consist of a high address byte followed by a low address byte, followed by a data byte, and writing the data byte to either memory or I/O space. Cold boot mode is entered by having one or both of the SMODE pins pulled high when the Rabbit is reset. The pin settings determine the source of the incoming triplets:

```

SMODE1 = 0, SMODE0 = 1 cold boot from slave port.

SMODE1 = 1, SMODE0 = 0 cold boot from clocked serial port A.

SMODE1 = 1, SMODE0 = 1 cold boot from asynchronous serial port A at 2400 bps.

SMODE1 = 0, SMODE0 = 0 start normal execution at address zero.

```

The SMODE pins can be used as general input pins once the cold boot is complete.

On entering cold boot mode, the microprocessor starts executing a 12-byte program contained in an internal ROM. The program contains the following code.

```

; origin zero

00 ld l,n

; n=0c0h for serial port A

; n=020h for parallel (slave port)

; get address most significant byte

02

ioi ld d,(hl)

ioi ld e,(hl)

; get least significant byte

06 ioi ld a, (hl)

; get data

; if the high bit of the MSB of the address is 1

8 0

ioi or nop

; (i.e., d[7] == 1) then ioi, else nop

09

ld (de),A

; store in memory or I/O

10

jr 0

; jump back to zero

; note wait states inserted at bytes 3, 5 and 7 waiting

; for serial port or parallel port ready

```

The function of the boot ROM program depends on the settings of the pins SMODE0 and SMODE1 and on whether the high bit of the high address byte (first byte of a received triplet) that is loaded to register D is set. If bit 7 of the high address byte is set, then the data byte (last byte of the triplet) is written to I/O space when received. If the bit is clear, then the data byte gets written to memory. Boot mode is terminated by storing 80h to I/O register 24h, which causes an instruction fetch to begin at address zero.

Wait states are automatically inserted during the fetching of bytes 3, 5 and 7 to wait for the serial or parallel port ready. The wait states continue indefinitely until the serial port is ready. This will cause the processor to be in the middle of an instruction fetch until the next character is ready. While the processor is in this state the chip select, but not the output enable, will be enabled if the memory mapping registers are such as to normally enable the chip select for the boot ROM address. The chip select will stay low for extended periods while the processor is waiting for the serial or parallel port data to be ready.

## 4.2 Program Loading Process Overview

On start up, Dynamic C first uses the PC's DTR line on the serial port to assert the Rabbit 3000 RESET line and put the processor in cold boot mode. Next, Dynamic C uses a four stage process to load a user program:

- 1. Load an initial loader (cold loader) to RAM via triplets sent at 2400 baud from the PC to a target in cold boot mode.

- 2. Run the initial loader and load a secondary loader (pilot BIOS) to RAM at 57600 baud.

- **3.** Run the secondary loader and load the BIOS and user program to flash after compiling them to a file, optionally negotiating with the Pilot BIOS to increase the baud rate to 115200 or higher so the loading can happen quickly.

- **4.** Run the BIOS. Then run and debug the user program at the baud rate selected in Dynamic C.

**NOTE:** Step 4 is combined with step 3 when using 4 K (or greater) sector flash.

#### 4.2.1 Program Loading Process Details

When Dynamic C starts, the following sequence of events takes place:

- 1. The serial port is opened with the DTR line high, closed, then reopened with the DTR line low at 2400 baud. This pulses the reset line on the target low (the programming cable inverts the DTR line) and prepares the PC to send triplets.

- 2. A group of triplets defined in the file COLDLOAD. BIN consisting of 2 address bytes and a data byte are sent to the target. The first few bytes sent are sent to I/O addresses to set up the MMU and MIU and do system initialization. The MMU is set up so that RAM is mapped to 0x00000, and flash is mapped to 0x80000.

- **3.** The remaining triplets place a small initial loader program at memory location 0x00000. The last triplet sent is 0x80, 0x24, 0x80, which tells the CPU to ignore the SMODE pins and start running code at address 0x00000.

- **4.** The initial loader measures the crystal speed to determine what divisor is needed to set a baud rate of 19200. The divisor is stored at address 0x3F02 for later use by the BIOS, and the programming port is set to 57600 baud.

- **5.** The PC now bumps the baud rate on the serial port being used to 57600 baud.

- **6.** The initial loader then reads 7 bytes from the serial port. First a 2-byte length field: the number of bytes in the secondary loader, followed by a 4-byte address field: the physical address to place the secondary loader. The 7th byte is a checksum (simple summation) of the previous 6 bytes. Whether or not the checksum matched, it is echoed back as an acknowledgement.

- 7. The data segment is then mapped to the given physical location, using the DATASEG register. The data segment boundary will also be set to 0x6000, so the secondary loader will always be located at the same place in logical space, regardless of where it physically resides.

- **8.** The initial loader finally enters a loop where it receives the specified number of bytes that compose the secondary loader program (pilot.bin sent by the PC) and writes those bytes starting at 0x6000 (logical). The first byte sent this way MUST be 0xCC, as an indicator to the initial loader. This byte will be stored as 0x00 (nop), instead of 0xCC. A 2-byte checksum will be sent after the secondary loader has been received, using the 8-bit Fletcher Algorithm (see RFC1145 for details), such that the load can be verified. After all of the bytes are received, and the checksum has been sent, program execution jumps to 0x6000.

- **9.** The secondary loader does a wrap-around test to determine how much RAM is available, reads the flash ID, the CPU ID, and initializes the flash-write routines. This information is made available for transmittal to Dynamic C when requested.

- **10.** The secondary loader now enters a finite state machine (FSM) that is used to implement the Dynamic C/Target Communications protocol. Dynamic C requests the CPU ID, flash information, RAM size, and 19200 baud rate divisor to define internally defined constants and macros. At this stage, the compiler can request the baud rate be increased to a higher value. The secondary loader is now ready to load a BIOS and user program.

- 11. Dynamic C now compiles the BIOS and user programs. Both are compiled to a file, then the file is loaded to the target using the Pilot BIOS' FSM. After the loading is complete, Dynamic C, using the Pilot BIOS' FSM, tells the Pilot BIOS to map flash to 0x00000, map RAM to 0x80000, and start program execution at 0x00000, thereby running the compiled BIOS.

- **12.** If the Pilot BIOS detects a RAM compile or small-sector flash that uses sector-write mode, Dynamic C uses a slightly different loading procedure. The BIOS will be compiled as normal, and loaded using the Pilot BIOS. After the BIOS is loaded, Dynamic C will tell the Pilot BIOS to start it, and the rest of the program will be loaded through the compiled BIOS.

- 13. Once the compiled BIOS starts up, it runs some initialization code. This includes setting up the serial port for the debug baud rate (set in the Communications Options dialog box prior to Dynamic C v. 8. For later versions of Dynamic C, go to the Communications tab in Options | Project Options), setting up serial interrupts and starting the BIOS FSM. Dynamic C sets a breakpoint at the beginning of main() and runs the program up to the breakpoint. The board has been programmed, and Dynamic C is now in debug mode.

- **14.** If the programming cable is removed and the target board is reset, the user's program will start running automatically because the BIOS will check the SMODE pins to determine whether to run the user application or enter the debug kernel.

## 5. Rabbit Memory Organization

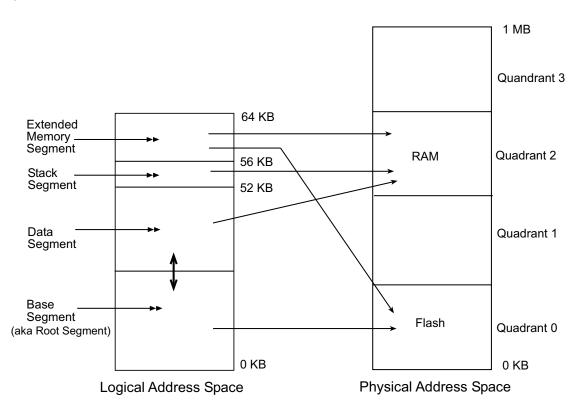

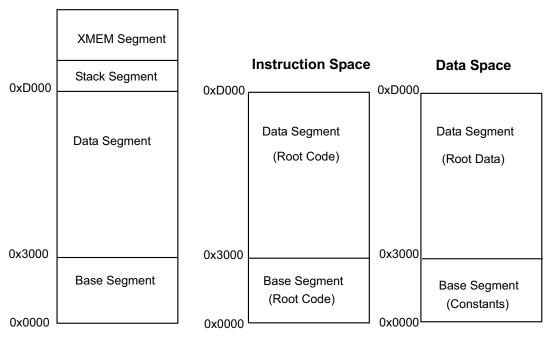

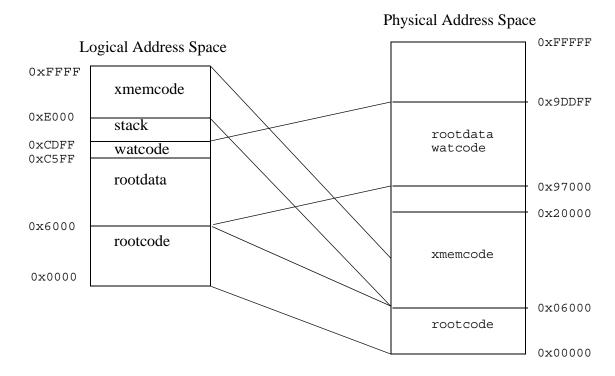

The Rabbit 3000 architecture is derived from the original Z80 microprocessor. The original Z80 instruction set used 16-bit addresses to address a 64 KB memory space. All code and data had to fit in this 64 KB space. To expand the available memory space, the Rabbit 3000 adopts a scheme similar to that used by the Z180. The 64 KB space is divided into segments and the Rabbit's Memory Mapping Unit (MMU) maps each segment to a block in a larger memory. The larger memory is 1 megabyte. The segments are effectively windows to the larger memory. The view from the window can be adjusted so that the window looks at different blocks in the larger memory. Figure 5-1 on page 16 shows the memory mapping schematically.

Please see Technical Note 202, "Rabbit Memory Management in a Nutshell," for more details on how memory mapping works. This document is available at:

http://www.rabbitsemiconductor.com/docs/app tech notes.shtml

## 5.1 Physical Memory

The Rabbit 3000 has a 1 MB physical memory space. In special circumstances more than 1 MB of memory can be installed and accessed using auxiliary memory mapping schemes. Typical Rabbit 3000 systems have two types of physical memory: flash memory and static RAM memory.

## 5.1.1 Flash Memory

Flash memory in a Rabbit 3000-based system may be small-sector or large-sector type. Small-sector memory typically has sectors of 128 to 4096 bytes. Individual sectors may be separately erased and written. In large-sector memory the sectors are often 16 KB to 64 KB or more. Large-sector memory is less expensive and has faster access time. The best solution will usually be to lay out a design to accept several different types of flash memory, including the flexible small-sector memories and the fast large-sector memories.

Flash memory follows a write-once-in-a-while and read-frequently model. Depending on the particular type of flash used, the flash memory may wear out after it has been written approximately 10,000 to 100,000 times.

#### 5.1.2 SRAM

Static RAM memory may or may not be battery-backed. If it is battery-backed it retains its data when power is off. Static RAM chips typically used for Rabbit systems are 128 KB, 256 KB, or 512 KB.

When the memory is battery-backed, power is supplied at 2 V to 3 V from a backup battery. While preserving memory contents with battery power, the shutdown circuitry must keep the chip select line high.

### 5.1.3 Basic Memory Configuration

A basic Rabbit system typically has two static memory chips: one flash memory chip and one RAM chip. Additional static memory chips may be added. If an application requires storing a lot of data in flash memory, it is recommended that another flash memory chip be added, creating a system with 3 memory chips—2 flash memory chips and one RAM chip.

Trying to use a single flash memory chip to store both the user's program and live data that must be frequently changed can create software problems. When data are written to a small-sector flash memory, the memory becomes inoperative during the 5 to 20 ms that it takes to write a sector. If the same memory chip is used to hold data and the program, then the execution of code must cease during this write time. The 5-20 ms is timed out by a small routine executing from root RAM while system interrupts are disabled, effectively freezing the system for 5-20 ms. The 5-20 ms lockup period can seriously affect real-time operation.

## **5.2 Memory Segments**

From the point of view of a Dynamic C programmer, there are a number of different uses of memory. Each memory use occupies a different segment in the logical 16-bit address space. The four segments are shown here:

Figure 5-1 Typical Memory Map of 16-bit Addressing Space

This figure shows that the Rabbit 3000 does not have a "flat" memory space. The advantage of the Rabbit 3000's memory organization is that the use of 16-bit addresses and pointers is retained, ensuring that the code is compact and executes quickly.

**NOTE:** The relative size of the base and data segments can be adjusted by increasing or decreasing the BIOS macro DATAORG in increments of 0x1000.

#### 5.2.1 Definition of Terms

The following definitions clarify some of the terms that will be encountered in this chapter.

**Extended Code**: Instructions located in the extended memory segment.

**Extended Constants**: C constants located in the extended memory segment. They are mixed together with the extended code.

Extended Memory: Logical addresses above 0xDFFF.

**Extended RAM**: RAM not used for root variables or stack. Extended memory in RAM may be used for large buffers to save root RAM space. The function xalloc() allocates space in extended RAM memory.

**Root Code**: Instructions located in the base segment.

**Root Constants**: C constants, such as quoted strings, initialized variables or data tables, that are located in the base segment.

**Root Memory**: Logical addresses below 0xE000. Please note that root memory is not the same as the root segment. The root segment is contained in root memory, as are the data and stack segments. The root segment is also known as the base segment.

**Root Variables**: C variables, including structures and arrays that are not initialized to a fixed value, are located in the data segment.

## 5.2.2 The Base (or Root) Segment

The base segment has a typical size of 24 KB. The larger the base segment, the smaller the data segment and vice-versa. Base segment address zero is always mapped to 20-bit address zero. Usually the base segment is mapped to flash memory since root code and root constants do not change except when the system is reprogrammed. It may be mapped to RAM for debugging, or to take advantage of the faster access time offered by RAM.

The base segment holds a mixture of code and constants. C functions or assembly language programs that are compiled to the base segment are interspersed with data constants. Data constants are inserted between blocks of code. Data constants defined inside a C function are put before the end of the code belonging to the function. Data constants defined outside of C functions are stored as encountered in the source code.

Except in small programs, the bulk of the code is executed using the extended memory (xmem) segment. Code operates at the same speed whether addressed through the base segment or the xmem segment. It just takes a few cycles longer to call xmem functions and return from them.

### 5.2.2.1 Types of Code Best-Suited for the Base Segment

- Short subroutines of about 20 instructions or less that are called frequently will use significantly less execution time if placed in root memory because of the faster calling linkage for 16-bit versus 20-bit addresses. For a call and return, 20 clocks are used compared to 32 clocks.

- **Interrupt routines.** Interrupt vectors use 16-bit addressing so the entry to an interrupt routine must be in the base segment.

- **The BIOS core.** The initialization code of the BIOS must be at the start of the base segment.

- A function that modifies the XPC must always be run in root memory.

### 5.2.3 The Data Segment

The data segment has a typical size of 28 KB, starting at 24 KB and ending at 52 KB (0xD000). The data segment is mapped to RAM and contains C variables. Data allocation starts at or near the top and proceeds in a downward direction. It is also possible to place executable code in the data segment if it is copied from flash to the data segment. This can be desirable for code that is self modifying, code to implement debugging aids or code that controls write to the flash memory and cannot execute from flash. In some cases RAM may require fewer wait states so code executes faster if copied to RAM.

#### 5.2.4 The Stack Segment

Usually the stack segment is from logical address 0xD000 to 0xDFFF. It is always mapped to RAM and holds the system stack. Multiple stacks may be implemented by defining several stacks in the 4 KB space or by remapping the 4 KB space to different locations in physical RAM memory, or by using both approaches. Multiple stack allocation is handled by  $\mu C/OS-II$  internally.

For example, if 16 stacks of 1 KB length are needed then 4 stacks can be placed in each 4 KB mapping and 4 different mappings for the window can be used.

#### 5.2.5 The Extended Memory Segment

This 8 KB segment from logical address 0xE000 to 0xFFFF is used to execute extended code and it is also used by routines that manipulate data located in extended memory. While executing code the mapping is shifted by 4 KB each time the code passes the 60 KB point. Up to a MB of code can be efficiently executed by moving the mapping of the 8 KB window using special instructions (long call, long jump and long return) that are designed for this purpose. This uses up only 8 KB of the 16-bit addressing space.

The xmem segment can map to any 4 KB page of the 1MB physical address space. For example if XPC is set to 0xF2, then the 16-bit address 0xE000 maps to the physical address 0x00000.

Please see Technical Note 202, "Rabbit Memory Management in a Nutshell," for more details on how memory mapping works. This document is available at:

http://www.rabbitsemiconductor.com/docs/app tech notes.shtml

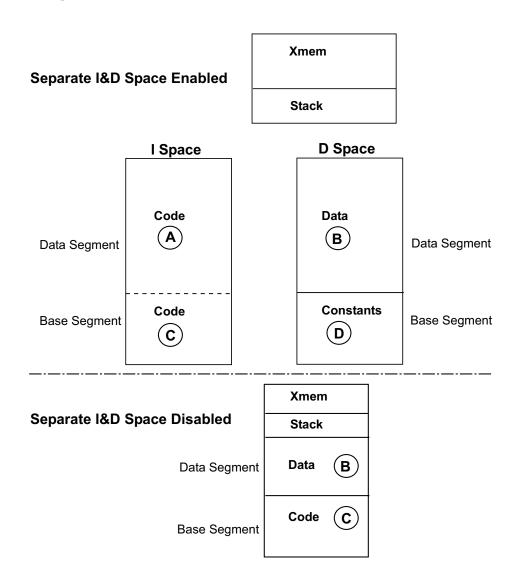

## 5.3 Separate I&D Space

Separate instruction and data space is a hardware memory management scheme that uses address line inversion to double the amount of logical address space in the base and data segments. In other words, this doubles the amount of root code and root data available for an application program.

Without separate I&D space, recall that in a typical memory map of the 16-bit address space, the base segment holds a mixture of code and constants and is mapped to flash; the data segment holds C variables and is mapped to RAM. With separate I&D space, code and data no longer have to divide this space because they share logical addresses by inverting address lines depending on whether the CPU is fetching instructions or data.

The following diagram shows the logical address space when separate I&D space is enabled and SEGSIZE =  $0 \times D3$ . The boundary at  $0 \times 3000$  is determined by the macro DATAORG in the BIOS. The boundary may be changed, however, care must be taken. To change the boundary, enter the macro name and a new boundary value in the "Defines" dialog box, which is accessed via Dynamic C's Options | Compiler dialog box prior to version 8. With later versions of Dynamic C, go to the Defines tab in Options | Project Options.

16-bit Logical Address Space

**NOTE:** This diagram illustrates how I&D space works; the actual values used in the BIOS may differ from those shown here.

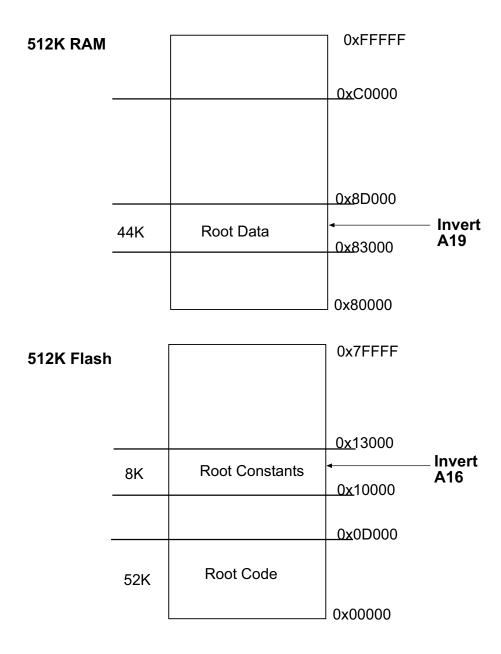

I&D logical addresses map to physical addresses by inverting address lines A16, A19 or both. The MMU Instruction/Data Register (MMIDR) determines which lines are inverted. Please see the *Rabbit 3000 Microprocessor User's Manual* for more information about the MMIDR.

The following diagram shows the physical address space when separate I&D space is enabled, SEGSIZE = 0xD3 and code is compiled to flash.

The inversion of A16 causes the root constants in the data space to be addressed in the next higher 64 KB block of the flash. The inversion of A19 causes the root data in the data space to be addressed in RAM (0x80000), starting at 0x83000 as directed by the lower nibble of SEGSIZE.

There are some new restrictions when using separate I&D space.

- Interrupt vectors that are modifiable at runtime have 80 clock cycles added to the execution time of the interrupt. The default case for system defined interrupt vectors is nonmodifiable. Nonmodifiable means that the interrupt vector is set at compile time and may not be changed unless the application is recompiled.

- You can not reference code as data or data as code in logical memory below the stack. When using separate I&D space, the processor makes a distinction between fetching an instruction from memory and fetching data from memory.

- There are some changes in the flash driver that are handled internally. The changes are only of concern if you are writing your own flash driver.

Embedded applications that do not need more code or data space need not make any changes for separate I&D space. By default, Dynamic C compiles without I&D space enabled.

#### 5.3.1 Enable Separate I&D Space

To use separate I&D space, open the Options | Compiler dialog box (for Dynamic C versions prior to version 8) and check the enable separate I&D space option. For later versions of Dynamic C the same option is accessible on the Compiler tab of the Options | Project Options dialog. The Dynamic C command line compiler equivalent is -id+ (enable I&D space) and -id- (disable I&D space). Please see the *Dynamic C User's Manual* for more information about the command line compiler.

The BIOS and the compiler take care of all the details so the user does not need to understand them. However, if you want to change the way an interrupt vector is handled or you need to write a flash driver, the rest of this chapter provides you with the necessary information.

### 5.3.2 I&D Space Mappings in Dynamic C

The next two subsections show the default MMU settings that Dynamic C uses when separate I&D space is enabled.

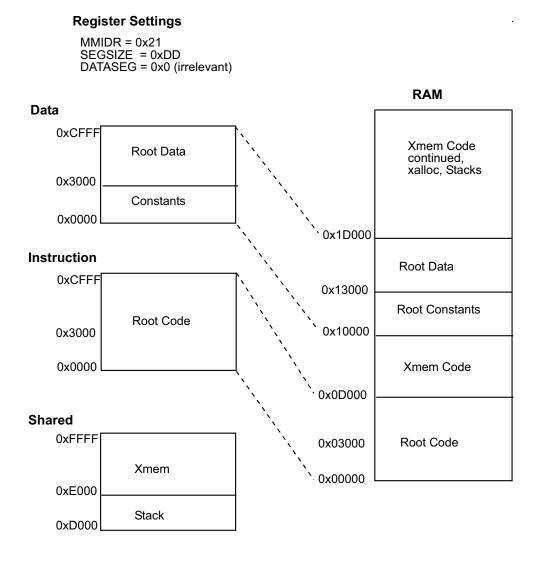

## 5.3.2.1 Compiling to RAM

For RAM compiles, all banks (quadrants) are mapped to RAM. For 512 KB memories, the lower 256 KB would be mapped to banks 0 and 2. The higher 256 KB are mapped to banks 1 and 3. In this configuration, A16 is inverted to provide access to the constants and data in the next 64 KB area. The standard configuration is to set the SEGSIZE register to 0xDD so that the base segment occupies the entire 52 KB region up to the stack segment. Note that this configuration causes the DATASEG register to be irrelevant.

The BIOS sets the MMIDR to 0x21. Bit 5 of this register enables the instruction/data split and bit 0 causes the inversion of A16 for data addresses.

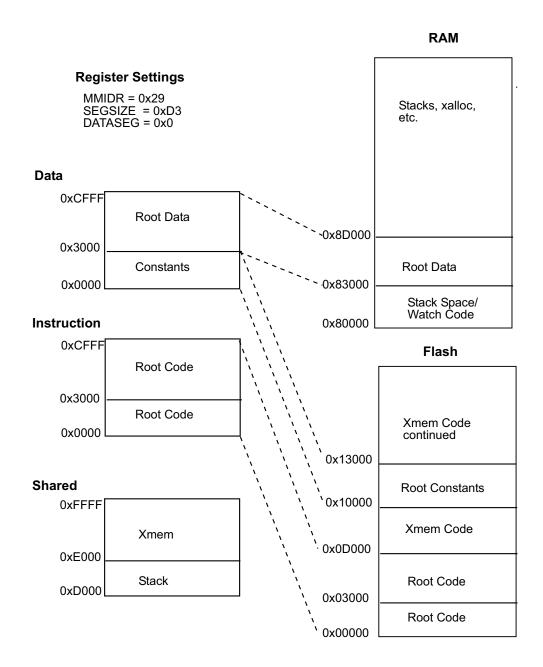

## 5.3.2.2 Compiling to Flash

For flash compiles, flash memory is mapped to banks 0 and 1 (address range 0x00000 to 0x7FFFF). RAM is mapped to banks 2 and 3 (address range 0x80000 to 0xFFFFF).

The BIOS sets the MMIDR to 0x29 to enable the I&D space for flash compilation. Bit 5 of this register enables the I&D split, bit 0 enables inversion of A16 for the data space base segment (i.e., the logical address space for constants) and bit 3 enables inversion of A19 for the data space data segment (i.e., the logical address space for root data).

### 5.3.3 Writing a Flash Driver

If you are writing your own flash driver, please read Section 10.2, "Writing Your Own Flash Driver," starting on page 64. When using separate I&D space there are several additional things to consider:

- The flash driver must run in RAM so that any flash location can be written.

- The flash driver cannot run in the xmem window for two reasons. First, the driver uses the xmem window. Second, it would require the use of "load physical" instructions (1dp) which always write 2 bytes and a flash unlock sequence requires 1-byte writes.

- Separate I&D space must be disabled while the flash driver is running due to the reasons stated above.

- While the flash driver is running you lose access to most of the application code and to all of its constants.

The following figure illustrates what happens to the access of an application's code and data when separate I&D space is disabled to run the flash driver.

## **5.3.4 Customizing Interrupts**

There are two methods to set the handling of an interrupt vector. The one you select depends on the needs of your application. Most of the ISRs set up by the BIOS are fast and nonmodifiable by default. Modifiable interrupts are slower because 80 clocks are added to their execution time.

Here is a list of the defined interrupt vector names and the corresponding ISRs:

Table 5-1 Interrupt Vector and ISR Names

| Interrupt Vector Name    | ISR Name                                                       | Default Condition      |  |

|--------------------------|----------------------------------------------------------------|------------------------|--|

| periodic_intvec          | periodic_isr                                                   | Fast and nonmodifiable |  |

| rst10_intvec             | User defined name                                              | User defined           |  |

| rst18_intvec             | These interrupt vectors and their ISRs should never be altered |                        |  |

| rst20_intvec             | by the user because they are reserved for the debug kernel.    |                        |  |

| rst28_intvec             |                                                                |                        |  |

| rst38_intvec             | User defined name                                              | User defined           |  |

| slave_intvec             | slave_isr                                                      | Fast and nonmodifiable |  |

| timera_intvec            | User defined name                                              | User defined           |  |

| timerb_intvec            | User defined name                                              | User defined           |  |

| a                        | DevMateSerialISR                                               | Fast and nonmodifiable |  |

| sera_intvec <sup>a</sup> | spa_isr                                                        | User defined           |  |

| serb_intvec              | spb_isr                                                        | User defined           |  |

| serc_intvec              | spc_isr                                                        |                        |  |

| serd_intvec              | spd_isr                                                        |                        |  |

| sere_intvec              | spe_isr                                                        |                        |  |

| serf_intvec              | spf_isr                                                        |                        |  |

| inputcap_intvec          | User defined name                                              |                        |  |

| quad_intvec              | qd_isr                                                         |                        |  |

| ext0_intvec              | User defined name                                              |                        |  |

| ext1_intvec              | User defined name                                              |                        |  |

a. Please note that this ISR shares the same interrupt vector as DevMateSerialISR. Using spa\_isr precludes Dynamic C from communicating with the target.

### 5.3.4.1 Method #1

To make an ISR fast and nonmodifiable, use the keyword interrupt vector. The syntax is:

```

interrupt vector <INT VECTOR NAME> <ISR NAME>

```

INT\_VECTOR\_NAME is an interrupt vector name, either user-defined or from Table 5-1. ISR\_NAME is the name of the interrupt service routine, either user-defined or from Table 5-1. The interrupt vectors for user-defined ISRs are fast and nonmodifiable when interrupt\_vector is used during setup.

In an application, use as follows:

```

// Set up an Interrupt Service Routine for Timer B

#asm

timerb_isr::

; ISR code

...

ret

#endasm

main() {

// Variables

...

// Set up ISR

interrupt_vector timerb_intvec timerb_isr; // Compile time set up

// Code

...

}

```

Notice that the interrupt vector is set up at compile time. This will override any run-time set up done by the function SetVectIntern(). Therefore, this function and the interrupt\_vector keyword are mutually exclusive. In other words, if you use both, the interrupt vector handling will be determined by interrupt\_vector and not by SetVectIntern(). Additionally, if interrupt\_vector is used multiple times for the same interrupt vector, the last one encountered by the compiler will override all previous ones.

For more information on SetVectIntern(), please see the  $Dynamic\ C\ Function\ Reference\ Manual$  or use the Function Lookup feature from Dynamic C's Help menu.

The keyword interrupt\_vector is syntactic sugar for using the origin directives and assembly code. The line:

```

interrupt vector timerb intvec timerb isr;

```

is equivalent to the following:

```

#rcodorg timerb_intvec apply

#asm

jp timerb_isr

#endasm

#rcodorg rootcode resume

```

### 5.3.4.2 Method #2

If you want the ISR to be modifiable, you have to set it up as follows:

```

#rcodorg <INT_VEC_NAME> apply

#asm

INTVEC_RELAY_SETUP(intvec_relay + <INTERRUPT_OFFSET>)

#endasm

#rcodeorg rootcode resume

```

<INTERRUPT\_OFFSET> is one of the following:

| EXTO_OFS     | SERA_OFS            |

|--------------|---------------------|

| EXT1_OFS     | SERB_OFS            |

| INPUTCAP_OFS | SERC_OFS            |

| PERIODIC_OFS | SERD_OFS            |

| QUAD_OFS     | SERE_OFS            |

| RST10_OFS    | SERF_OFS            |

| RST18_OFS    | ${\tt SLAVE\_OFS}$  |

| RST20_OFS    | ${\tt TIMERA\_OFS}$ |

| RST28_OFS    | TIMERB_OFS          |

| RST38_OFS    |                     |

|              |                     |

These are defined in sysio.lib.

## **5.4 How The Compiler Compiles to Memory**

The compiler generates code for root code, root constants, extended code and extended constants. It allocates space for data variables, but, except for constants, does not generate data to be stored in memory. Any initialization of RAM variables must be accomplished by code since the compiler is not present when the program starts in the field. (Please see #GLOBAL\_INIT in the *Dynamic C User's Manual.*)

Static variables are not zeroed out by default. Starting with Dynamic C version 7.30, the BIOS macro ZERO\_OUT\_STATIC\_DATA may be set to 1, which will zero out static variables on board power-up or reset only. Zeroing out static variables is not compatible with the use of protected variables because they will be zeroed out along with the rest of the static data.

#### 5.4.1 Placement of Code in Memory

Code may be placed in either extended memory or root memory. Functions execute at the same speed, but calls to functions in root memory are slightly more efficient than calls to functions in extended memory.

In all but the smallest programs, most of the code is compiled to extended memory. Since root constants share the memory space needed for root code (when separate I&D space is disabled), as the memory needed for root constants increases, the amount of code that can be stored in root memory decreases, and code must be moved to extended memory.

Please see the *Dynamic C User's Manual* regarding the compiler directive #memmap for more information about controlling the placement of code in memory.

#### **5.4.2 Paged Access in Extended Memory**

The code in extended memory executes in the 8 KB window from E000 to FFFF. This 8 KB window uses paged access. Instructions that use 16-bit addressing can jump within the page and also outside of the page to the remainder of the 64 KB logical space. Special instructions, particularly lcall, ljp, and lret, are used to access code outside of the 8 KB window. When one of these transfer-of-control instructions is executed, both the address and the view through the 8 KB window change, allowing transfer to any instruction in the 1MB physical memory space. The 8-bit XPC register controls which of two consecutive 4 KB pages the 8 KB window aligns with (there are 256 pages). The 16-bit PC controls the address of the instruction, usually in the region E000 to FFFF. The advantage of paged access is that most instructions continue to use 16-bit addressing. Only when a page change is needed does a 20-bit transfer of control need to be made.

As the compiler compiles code in the extended code window, it checks at opportune times to see if the code has passed the midpoint of the window or F000. When the code passes F000, the compiler slides the window down by 4 KB so that the code at F000+x becomes resident at E000+x. This automatic paging results in the code being divided into segments that are typically 4 KB long, but which can be very short or as long as 8 KB. Transfer of control within each segment can be accomplished by 16-bit addressing. Between segments, 20-bit addressing is required.

## 5.5 Memory Planning

The design conventions for the memory configuration of a Rabbit 3000-based system specify both flash and SRAM. However, you can design a board using RAM only. Details for doing so are discussed in section 5.6.

Table 5-2 Typical Interface Between the Rabbit 3000 and Memory

| Primary Flash       | SRAM                | Secondary Flash     |

|---------------------|---------------------|---------------------|

| /CS0, /OE0 and /WE0 | /CS1, /OE1 and /WE1 | /CS2, /OE0 and /WE0 |

#### 5.5.1 Flash

Code is typically stored in flash memory, so the size of the code must be anticipated. Usually code size up to 512 KB is handled by one or two flash memory chips. If you are writing a program from scratch, remember that 512 KB of code is equivalent to 25,000 to 50,000 C statements, and such a large program can take years to write.

Static data tables can be conveniently placed in the same space using the xdata and xstring declarations supported by Dynamic C, so the amount of space needed for static data can be added to the amount of space needed for code.

#### 5.5.2 Static RAM

C programs vary in how much RAM will be required. Many programs can subsist on 32 KB of RAM. However, having more RAM is necessary for debugging. Since debugging and program testing generally operate more powerfully and faster when sufficient RAM is available to hold the program and data, most Z-World controllers based on the Rabbit 3000 use a dual footprint for RAM that can accommodate either a 32K x 8, which is in a 28-pin package, or a 128K x 8 or 512K x 8, which is in a 32-pin package. The base RAM is interfaced to /CS1 and /WE1, and /OE1.

RAM is required for the following items:

- **Root Variables**—maximum of 40-44 KB, and about 4 KB more if separate I&D space is enabled.

- **Stack Pages**—rarely more than 20 KB.

- **Debugging**—as a convenience on prototype units, 512 KB is usually enough to accommodate programs. It is not necessary to debug in RAM, but may be desirable.

- **Extended Memory**—such as data logging applications or communications applications. The amount needed depends on application.

29

## 5.6 Making a RAM-Only Board

Some Rabbit 3000 customers are designing boards that have a single RAM chip and no flash memory. Although this is not recommended, it may be safe as long as the board has a continuous power supply and is set up to be field-programmable via the Rabbit 3000 bootstrap mode.

For example, a Rabbit 3000 board in a noncritical system such as a lawn sprinkler system may be monitored from a remote location via the Internet or Ethernet, where the remote monitor has the ability to reload the application program to the board. One way to achieve field programmability is with the RabbitLink Network Gateway.

There are certain hardware and software changes that are required to make this work. If you are using Dynamic C version 7.25, you will need to contact our Technical Support department if you wish to design a RAM-only board

#### 5.6.1 Hardware Changes

Ordinarily, /CS0, /OE0 and /WE0 of the Rabbit 3000 processor are connected to a flash chip, and /CS1, /OE1 and /WE1are connected to RAM. However, if only RAM is to be used, /CS0, /OE0 and /WE0 must be connected to the RAM. This is because on power up or reset, the Rabbit 3000 will begin fetching instructions from whatever is hooked to /CS0, /OE0 and /WE0.

#### 5.6.2 Software Changes

In order to program a RAM-only board from Dynamic C or the Rabbit Field Utility (RFU), several changes are needed.

- Set the macro RAMONLYBIOS to 1 in RabbitBios.c.

- When Dynamic C or the RFU first start, they put the Rabbit 3000-based target board in bootstrap mode where it awaits data sent via "triplets." These programs then send triplets that map the lowest quadrant of physical memory to /CS1, /OE1 and /WE1 in order to load a primary loader to RAM. The first set of triplets loaded to the target is contained in a file called coldload.bin. This is the primary loader.

- A different coldload.bin is required to map the lowest memory quadrant to /CS0, /OE0 and /WE0. The image file for this program is \BIOS\RAMONLYCOLDLOAD.BIN. To use it, rename COLDLOAD.BIN to COLDLOAD.BAK, and rename RAMONLYCOLDLOAD.BIN to COLDLOAD.BIN. (Later versions of Dynamic C may have a GUI method of choosing the cold loader.)

- The primary loader loads a secondary loader, pilot.bin. A different pilot BIOS is needed: RAMonlypilot.bin. Rename pilot.bin to pilot.bak and rename RAMonlypilot.bin to pilot.bin.

The secondary loader loads the Rabbit BIOS to RAM (from the application program image file in the case of the RFU, by compiling the BIOS straight to the target in the case of Dynamic C).

## 6. The Rabbit BIOS

When Dynamic C compiles a user's program to a target board, the BIOS (Basic Input-Output System) is compiled first, as an integral part of the user's program. The BIOS is a separate program file that contains the code needed to interface with Dynamic C. Normally, it also contains a software interface to the user's particular hardware. Certain drivers in the Dynamic C libraries require BIOS routines to perform tasks that are hardware-dependent.

#### The BIOS also:

- Takes care of microprocessor system initialization, such as the setup of memory.

- Provides the communications services required by Dynamic C for downloading code and performing debugging services such as setting breakpoints or examining data variables.

- Provides flash drivers.

A single, general-purpose BIOS is supplied with Dynamic C for the Rabbit 3000. This BIOS allows Dynamic C to boot up on any Rabbit-based system that follows the basic design rules needed to support Dynamic C. The BIOS requires both a flash memory and a 32 KB or larger RAM, or just a 128 KB RAM, for it to be possible to compile and run Dynamic C programs. If the user uses a flash memory from the list of flash memories that are already supported by the BIOS, the task will be simplified. A list of supported flash devices is listed in Technical Note 226, available online at:

http://www.rabbitsemiconductor.com/docs/app tech notes.shtml

If the flash device is not already supported, the user will have to write a driver to perform the write operation on the flash memory. This is not difficult provided that a system with 128 KB of RAM and the flash memory to be used are available for testing.

An existing BIOS can be used as a skeleton BIOS to create a new BIOS. Frequently it will only be necessary to change #define statements at the beginning of the BIOS. In this case it is unnecessary for the user to understand or work out the details of the memory setup and other processor initialization.

## 6.1 Startup Conditions Set by the BIOS

The BIOS sets up initial values for the following registers by means of code and declarations.

- The four memory bank control registers —MBOCR, MB1CR, MB2CR, and MB3CR—are 8-bit registers, each associated with one quadrant of the 1M memory space. Each register determines which memory chip will be mapped into its quadrant, how many wait states will be used for accessing that memory chip, and whether the memory chip will be write protected.

- The STACKSEG register is an 8-bit register that determines the location of the stack segment in the 1M memory.

- The DATASEG register is an 8-bit register that determines the location of the data segment in the 1M memory, normally the location of the data variable space.

- The SEGSIZE register is an 8-bit register holding two 4-bit values. Together the values determine the relative size of the base segment, data segment and stack segment in the 64 KB root space.

- The MMIDR register is an 8-bit register used to control separate I&D space and to force /CS1 to be always enabled or not. Having /CS1 always enabled reduces access time if /CS1 is routed through an external battery backup device and the propagation delay through the external device may slow the transition of /CS1 during memory cycles.

- The SP register is the system stack pointer. It is frequently changed by the user's code. The BIOS sets up an initial value.

In addition, a number of origin declarations are made in the BIOS to tell the Dynamic C compiler where to place different types of code and data. The compiler maintains a number of assembly counters to place or allocate root code, extended code, data constants, data variables, and extended data variables. Each of these counters has a starting location and a block size.

For more information about the MMU and MIU registers please see the *Rabbit 3000 Microprocessor User's Manual*.

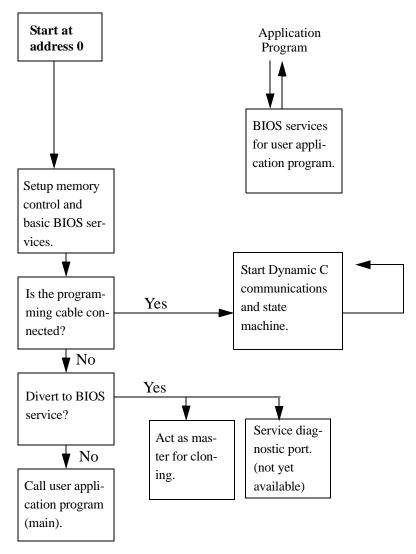

## 6.2 BIOS Flowchart

The following flowchart summarizes the functionality of the BIOS:

Figure 6-1 BIOS Flowchart

**NOTE:** If the programming cable is connected at power-up, the Rabbit will never get to the BIOS.