# iDragon SCX501 Programming Manual

Release A

May 9, 2000

**RiSE Technology Company**

Information provided is believed to be accurate and reliable. However, RiSE Technology assumes no responsibility for the consequences of use of such information nor for any infringements of patents or other rights of third parties which may result from its use. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied.

# **1 TABLE OF CONTENTS**

| 1 TABLE OF CONTENTS                                           |

|---------------------------------------------------------------|

| 2 LIST OF TABLES                                              |

| 3 LIST OF FIGURES                                             |

| 4. INTRODUCTIO                                                |

| 5. HOW TO USE THIS MANUAL                                     |

| 5.1 INTRODUCTION                                              |

| 5.2 SPECIFIC NOTES                                            |

| 5.3 ISSUING NOTES                                             |

| 6 LIST OF REGISTERS                                           |

| 7. SDRAM Controller                                           |

| 7.1 INTRODUCTION                                              |

| 7.2 MEMORY CONTROLLER                                         |

| 7.3 MEMORY ADDRESS MAP                                        |

| 7.4 IO ADDRESS MAP                                            |

| 7.5 CACHE RELATED REGISTERS                                   |

| 7.6 ADDRESS DECODE RELATED REGISTERS                          |

| 7.7 HOST SDRAM CONTROLLER REGISTERS                           |

| 7.8 SDRAM CONTROLER REGISTER ACCESS                           |

| 7.9 MEMORY CLOCK REGISTERS                                    |

| 7.10 SDRAM INTERFACE                                          |

| 7.11 SDRAM ARBITRATION:                                       |

| 8. PCI CONTROLLERS                                            |

| 8.1 INTRODUCTION                                              |

| 8.2 METHOD FOR ACCESSING THE PCI CONFIGURATION REGISTERS      |

| 8.3 CONFIGURATION ADDRESS REGISTER IO CF8H (CONFIG_ADDRESS)47 |

| 8.4 CONFIGURATION DATA REGISTER IO CFCH (CONFIG_DATA)         |

# TABLE OF CONTENTS

|    | 8.5   | THE NORTH BRIDGE CONFIGURATION REGISTERS               |

|----|-------|--------------------------------------------------------|

|    | 8.6   | THE SOUTH BRIDGE                                       |

|    | 8.7   | SOUTH BRIDGE PCI FUNCTION 0<br>CONFIGURATION REGISTERS |

|    | 8.8   | SOUTH BRIDGE PCI FUNCTION 1 CONFIGURATION REGISTERS    |

| 9. | ISA I | NTERFACE                                               |

|    | 9.1   | INTRODUCTION                                           |

|    | 9.2   | PCI / ISA CYCLES                                       |

|    | 9.3   | XBUS READ AND WRITE                                    |

|    | 9.4   | FAST CPU RESET AND FAST GATE A20                       |

|    | 9.5   | ISA STANDARD REGISTERS                                 |

|    | 9.6   | ISA CONFIGURATION REGISTERS                            |

| 10 | . IDE | CONTROLLER                                             |

|    | 10.1  | .INTRODUCTION                                          |

|    | 10.2  | PRD TABLE ENTRY                                        |

|    | 10.3  | B.IDE BUS MASTER REGISTERS                             |

|    | 10.4  | BUS MASTER IDE REGISTER DESCRIPTION                    |

|    | 10.5  | BUS MASTER IDE COMMAND REGISTER                        |

|    | 10.6  | OPERATION                                              |

|    | 10.7  | Z.DATA SYNCHRONIZATION 85                              |

|    | 10.8  | ERROR CONDITIONS                                       |

|    | 10.9  | 9.PCI SPECIFICS                                        |

| 11 | . VG  | A CONTROLLER                                           |

|    | 11.1  | INTRODUCTION                                           |

|    | 11.2  | VGA CONTROLLER                                         |

|    | 11.3  | VGA REGISTERS                                          |

|    | 11.4  | GENERAL VGA REGISTERS                                  |

|    | 11.5  | VGA SEQUENCER REGISTERS                                |

|    | 11.6 GRAPHICS CONTROLLER REGISTERS      |

|----|-----------------------------------------|

|    | 11.7 ATTRIBUTE CONTROLLER REGISTERS     |

|    | 11.8 CRT CONTROLLER REGISTERS           |

|    | 11.9 VGA EXTENDED REGISTERS             |

|    | 11.10ADDITIONAL MODES                   |

|    | 11.11INTERLACED MONITOR SUPPORT         |

|    | 11.12RAMDAC REGISTERS                   |

|    | 11.13DCLK CONTROL REGISTERS             |

| 12 | . GRAPHICS ENGINE                       |

|    | 12.1 INTRODUCTION                       |

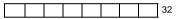

|    | 12.2 MEMORY ADDRESS SPACE               |

|    | 12.3 DUMB FRAME BUFFER ACCESS           |

|    | 12.4 ADDRESSING                         |

|    | 12.5 VGA OPERAND SOURCES                |

|    | 12.6 VGA OPERAND FRAME BUFFER ADDRESSES |

|    | 12.7 DRAWING ENGINE REGISTERS           |

|    | 12.8 REGISTER ACCESS                    |

|    | 12.9 REGISTER SPECIFICATION             |

|    | 12.10GE OPERATIONS                      |

|    | 12.11CURSOR SUPPORT                     |

|    | 12.12GRAPHICS CLOCK REGISTERS           |

| 13 | VIDEO CONTROLLER                        |

|    | 13.1 INTRODUCTION                       |

|    | 13.2 VIDEO INPUT PORT (VIP) OVERVIEW    |

|    | 13.3 DIGITAL VIDEO INPUT FORMATS        |

|    | 13.4 VIP SPECIFICATIONS NOT SUPPORTED   |

|    | 13.5 VIDEO INPUT MODULE ADDRESS SPACE   |

|    | 13.6 VIP VIDEO INPUT PORT REGISTERS     |

# TABLE OF CONTENTS

|    | 13.7 VIDEO OUTPUT PORT                                   | 149  |

|----|----------------------------------------------------------|------|

|    | 13.8 VIDEO OUTPUT PORT REGISTER ACCESS                   | 158  |

|    | 13.9 VIDEO OUTPUT PORT REGISTERS                         | 159  |

|    | 13.10VIDEO OUTPUT PORT REGISTER CONTENTS AND DESCRIPTION | 160  |

|    | 13.11VIDEO PIPELINE REGISTERS                            | 169  |

| 14 | LOCAL BUS INTERFACE                                      | 175  |

|    | 14.1 INTRODUCTION                                        | 175  |

|    | 14.2 LOCAL BUS REGISTERS                                 | 175  |

|    | 14.3 LOCAL BUS ADDRESS DECODE REGISTERS                  | 176  |

|    | 14.4 LOCAL BUS TIMING REGISTERS                          | .176 |

|    | 14.5 LOCAL BUS CONTROL REGISTER                          | 177  |

|    | 14.6 CHIP SELECT MEMORY MAP                              | 178  |

| 1  | . POWER MANAGEMENT                                       | 181  |

|    | 15.1 INTRODUCTION                                        | 181  |

|    | 15.2 POWER MANAGEMENT REGISTERS                          | 182  |

RISE

# 2 LIST OF TABLES

| CPU Registers located in the ST 486 Manual                           | . 26 |

|----------------------------------------------------------------------|------|

| Supported Memory Configs                                             | . 27 |

| IO map space                                                         | .31  |

| PCI configuration address space                                      |      |

| MCLK Control Register Address 22 Index 40h, 41h                      |      |

| Standard Memory DIMM Pinout                                          | .43  |

| Address Mapping                                                      | .43  |

| Register CF8h                                                        | .47  |

| Register CFCh                                                        | .47  |

| North Bridge Reset Values                                            |      |

| Function 0 (ISA bridge) Configuration Space Register Reset Values    | .52  |

| Function 1 (IDE Bridge) PCI Configuration Space Reister reset values | .54  |

| Recovery R/W Signal Time                                             | . 57 |

| Active R/W Signal Time                                               | . 57 |

| Address Setup Time                                                   | . 57 |

| Prefetch encoding                                                    | .58  |

| PIO R/W Signal Recovery Time                                         |      |

| PIO R/W Signal Active Time                                           |      |

| Address Setup Time Encoding                                          |      |

| Prefetch IDE Controller Encoding                                     |      |

| PIO R/W Recovery Time                                                |      |

| PIO Active Time Encoding                                             |      |

| IDE Controller Prefetch Encoding                                     |      |

| PIO R/W Signal Recovery Time                                         |      |

| PIO R/W Signal Active Time                                           |      |

| Address Setup Time Encoding                                          |      |

| IDE Controller Prefetch encoding                                     |      |

| DMA 1 Registers                                                      |      |

| Interrupt Controller 1 registers                                     |      |

| Interval Timer registers                                             |      |

| Interrupt Controller 2 registers                                     |      |

| DMA Controller 2 registers                                           |      |

| DMA Page registers                                                   | . 74 |

| CPU Deturbo Encoding                                                 |      |

| Routing Control A# encoding                                          |      |

| Routing Control B# encoding                                          |      |

| Routing Control C# encoding                                          |      |

| Routing Control D# encoding                                          |      |

| IPC Wait state encoding                                              |      |

| DMA 16-Bit Wait State encoding                                       |      |

| DMA 8-Bit Wait State encoding                                        |      |

| VMI Routing Control encoding                                         | .70  |

| Video Encoding Formats                                               |      |

| Video Input Module Address Space                                     |      |

| Video Output Port Register/Bit Mapping                               |      |

| Register_21_22_23                                                    | 166  |

| Register_31_32_33                                                    | 167  |

| Register_31_32_35                                                    |      |

| Negistel_07_00_01_00                                                 |      |

| tegister_39-40              |

|-----------------------------|

| register_42                 |

| Register 43                 |

| ctivity detection           |

| Suspend timer encoding      |

| tandby timer encoding       |

| lousekeeping timer encoding |

| eripheral timeout encoding  |

| 0oze timeout encoding       |

| MU encoding                 |

| TPCL# modulation encoding   |

| 0/S/S State encoding        |

RISE

# **3 LIST OF FIGURES**

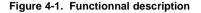

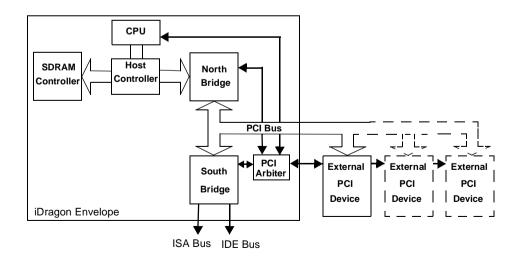

| Functionnal description                           | 11  |

|---------------------------------------------------|-----|

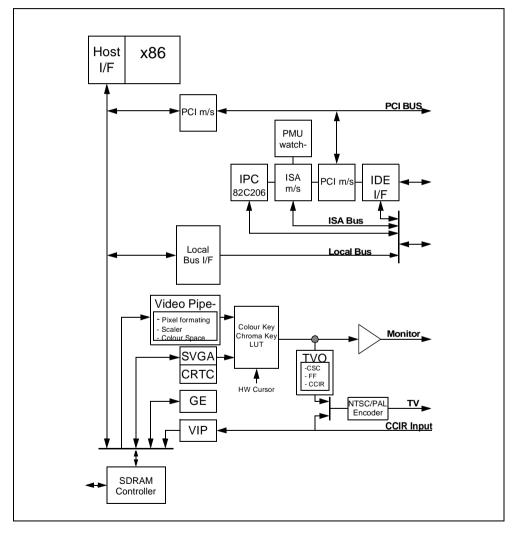

| One memory Bank with eight chips (8-Bit)          | 41  |

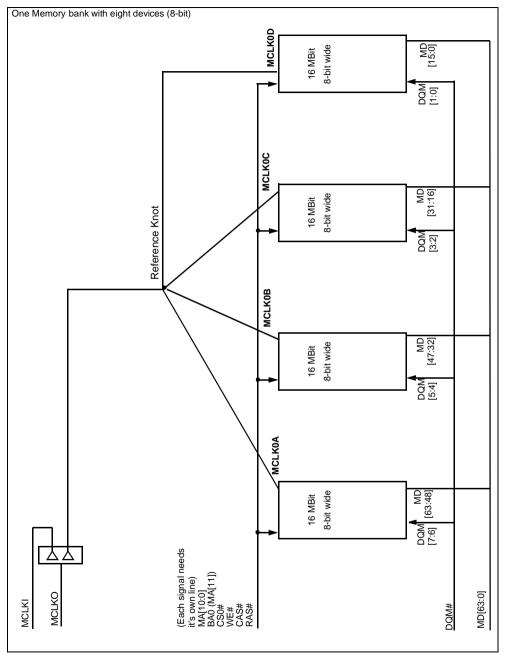

| Two memory banks with eight chips on each (8-Bit) | 42  |

| PCI Layout                                        | 45  |

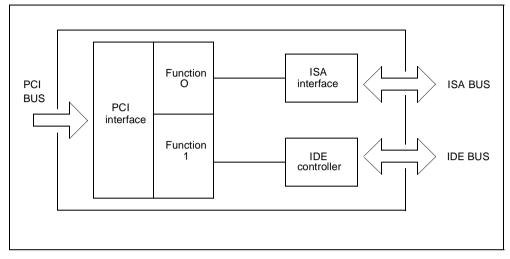

| South bridge layout                               | 51  |

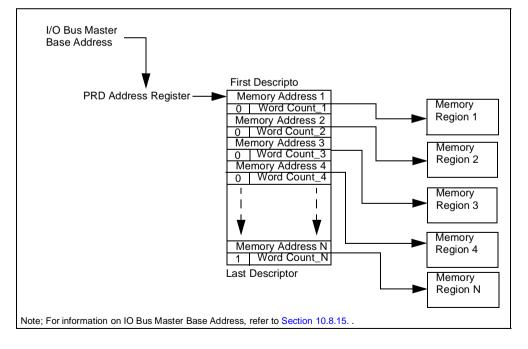

| PRD Table Entry Example                           | 82  |

| GE memory Map                                     | 117 |

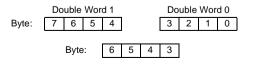

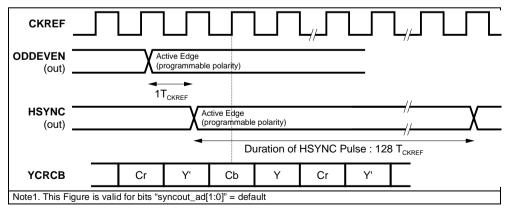

| Horizontal Blanking Interval and Active Timings   | 150 |

| ODDEVEN, VSYNC and HSYNC Waveforms                | 151 |

| Master Mode Sync Signals                          | 151 |

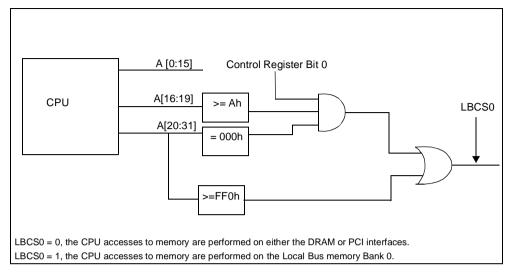

| Local Bus Address Mapping Diagram                 |     |

| Memory Bank 0 Access Logic                        | 180 |

Release A

RiSE<sup>™</sup> and iDragon <sup>™</sup> are trademark of RiSE<sup>™</sup> Technology. All other trademarks are properties of respective owners. This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change with out notice.

# 4. INTRODUCTION

This programming manual details the register sets for the iDragon SCX501 Device. The manual is split into chapters each dedicated to a function.

This documents contains all the information required to program and configure the iDragon SCX501.

In order to use this manual to the full, you may want to make reference to the STPC and X86 core Datasheets.

RISE<sup>™</sup> and iDragon<sup>™</sup> are trademark of RiSE<sup>™</sup> Technology. All other trademarks are properties of respective owners. This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change with out notice.

Release A

RiSE™ and iDragon ™ are trademark of RiSE™ Technology. All other trademarks are properties of respective owners. This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change with out notice.

# 5. HOW TO USE THIS MANUAL

#### 5.1 INTRODUCTION

This manual provides full technical documentation for the iDragondevice. It is recommended that the reader is familiar with the x86 series processors and PC compatible architectures before reading this document. Many terms are related directly to the PC architecture.

The manual itself is split into chapters. These chapters hold the information for a particular functional block of the device. For example, the chapter titled "Memory Access" gives the memory map of the iDragondevice, the memory architecture and interface to the external DRAM modules.

#### **5.2 SPECIFIC NOTES**

#### 5.2.1 RESERVED BITS

Write mode 1 is a subset of Write Mode 0. No CPU-supplied write data is used. The read data latched from a previous read operation is written. The bit mask is disabled. The map-masks are implemented as they are for Write Mode 0.

Many bits in the register descriptions are noted as reserved. These bits are not internally connected, physically not present or are used for testing purposes. In all cases these bits should be set to a '0' when writing to a register with reserved bits. When reading from a register with reserved bits, these specific bits should be masked from the data value before action is taken on the data.

Any functionality found by setting the reserved bits to levels other than '0' cannot and will not be guaranteed on future revisions of the circuit design. Thus it is not recommended to use the bits marked as reserved in any way different from noted above.

#### 5.2.2 SIGNAL ACTIVE STATE

The pound symbol (#) following a signal name indicates that when the signal is in its active (asserted) state, the signal is at a logic low level. When the "#" is not present at the end of a signal name, the logic high level represents the active state.

#### **5.2.3 HEXADECIMAL NOTATION**

In this manual Hexadecimal (Hex) numbers (numbers to the base 16: [0-9,A-F]) are denoted by the postfix 'h'.

For example a memory address 783A hexadeci mal will be written 783Ah.

#### **5.2.4 ENDIAN**

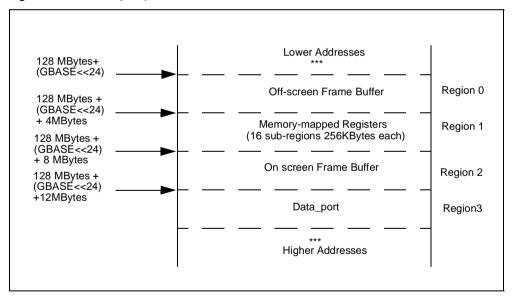

In common with the x86 architecture, values in memory are little-endian, that is the lower part of the memory contains the least significant Byte.

For an 8-bit value

13/193

#### **5.3 ISSUING NOTES**

There are three levels identified; Advanced data, Preliminary data and Full production release.

Each level is identified in a specific way as follows.

| Document<br>Identification | Status                 | Definition                                                                                                                                                       | Release Identification |

|----------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| ADVANCED DATA              | In design              | This document based on the product specification.<br>The information may be updated without notice.<br>Large changes may still occur.                            | Release A, Release B   |

| PRELIMINARY<br>DATA        | Pre-production<br>Data | This document contains preliminary data and may<br>be updated without notice in order to improve the<br>product features.                                        | Issue 0.X.             |

| FULL<br>PRODUCTION<br>DATA | Production Data        | This is the finalized document and all test plans are<br>completed. The information may be updated with-<br>out notice in order to improve the product features. | Issue 1.X.             |

This chapter lists all the registers accessable by external software.

| Section    | Register Name                      | Mnemonic           | Purpose       | Address   | Access type |

|------------|------------------------------------|--------------------|---------------|-----------|-------------|

| 3.         | Power on strap Registers           |                    |               | 0022h     |             |

| 3.1.1      | Strap register 0                   | Strap0             | Configuration | 0023h     | Index 04Ah  |

| 3.1.2      | Strap register 1                   | Strap1             | Configuration |           | Index 04Bh  |

| 3.1.3      | Strap register 2                   | Strap2             | Configuration |           | Index 04Ch  |

| 3.1.4      | HCLK Strap register                | HCLK_Strap         | Configuration |           | Index 05Fh  |

|            | 1                                  |                    |               | 1         |             |

| 7.5        | Cache related registers            |                    |               | 0022h     |             |

| 7.5.1      | Cache Architecture Register 0      | Cash_arc0          | Configuration | 0023h     | Index 020h  |

| 7.5.2      | Cache Architecture Register 1      | Cash_arc1          | Configuration |           | Index 021h  |

| 7.5.3      | Cache Architecture Register 2      | Cash_arc2          | Configuration |           | Index 022h  |

|            |                                    |                    |               |           |             |

| 7.6        | Address decode related registers   |                    |               | 0022h     |             |

| 7.6.1      | Memory Hole Control Register       | Mem_hole           | Configuration | 0023h     | Index 024h  |

| 7.6.2      | Shadow Control Register 0          | Shadow_cont0       | Configuration |           | Index 025h  |

| 7.6.3      | Shadow Control Register 1          | Shadow_cont1       | Configuration |           | Index 026h  |

| 7.6.4      | Shadow Control Register 2          | Shadow_cont2       | Configuration |           | Index 027h  |

| 7.6.5      | Shadow Control Register 3          | Shadow_cont3       | Configuration |           | Index 028h  |

| 7.6.6      | VGA Decode Register                | VGA_dec            | Configuration |           | Index 029h  |

|            |                                    | -                  |               |           |             |

| 7.7        | Host SDRAM controller registers    |                    |               | 0022h     |             |

| 7.7.1      | SDRAM Bank 0 Register              | SDRAM_bank0        | Configuration | 0023h     | Index 030h  |

| 7.7.2      | SDRAM Bank 1 Register              | SDRAM_bank1        | Configuration |           | Index 031h  |

| 7.7.3      | SDRAM Bank 2 Register              | SDRAM_bank2        | Configuration |           | Index 032h  |

| 7.7.4      | SDRAM Bank 3 Register              | SDRAM_bank3        | Configuration |           | Index 033h  |

| 7.7.5      | Memory Bank Width Register         | Mem_width          | Configuration |           | Index 034h  |

| 7.7.6      | Graphics Memory Size Register      | Graph_mem          | Configuration |           | Index 036h  |

| 7.7.7      | Presents Detect Register           | Pres_dect          | Configuration |           | Index 097h  |

|            |                                    | T                  |               | I         |             |

| 7.         | Memory Interface                   |                    | 0             | GBase+4C6 |             |

| 7.8.1      | Register 1                         | MEM_REG1           | Configuration |           | 000h        |

| 7.8.2      | Register 2                         | MEM_REG2           | Configuration |           | 004h        |

| 7.9        | MCLK Control Registers             | 1                  |               | 22h       |             |

| .9<br>.9.1 | MCLK Control Register 0            | MCLK00             |               | 23h       | Index 0x40h |

| .9.2       | MCLK Control Register 1            | MCLK01             |               |           | Index 0x41h |

|            |                                    |                    |               |           |             |

| 10.5.      | North Bridge Config Registers      |                    |               |           |             |

| 10.2       | Configuration Address Register     | Config_<br>address | Ю             | 0xCF8h    |             |

| 10.3.      | Configuration Data Register        |                    |               | 0xCFC -   |             |

| 10.4.      |                                    | Config_data        | IO            | CFFh      |             |

|            | North Bridge Vendor Identification | NB_Vend_ID         | PCI Config    |           | Index 0x0h  |

| 10.5.1.    | Register                           |                    | 5             |           |             |

| Section | Register Name                                          | Mnemonic            | Purpose        | Address | Access type |

|---------|--------------------------------------------------------|---------------------|----------------|---------|-------------|

| 10.5.2. | North Bridge Device Identification<br>Register         | NB_Device_ID        | PCI Config     |         | Index 0x2h  |

| 10.5.3. | North Bridge PCI Command Regis-<br>ter                 | NB_Command          | PCI Config     |         | Index 0x4h  |

| 10.5.4. | North Bridge PCI Status Register                       | NB_Status           | PCI Config     |         | Index 0x6h  |

| 10.5.5. | North Bridge PCI Revision Id Reg-                      | NB_Rev_ID           | PCI Config     |         | Index 0x8h  |

| 10.5.6. | North Bridge Device Class Code<br>Register             | NB_Class_<br>Code   | PCI Config     |         | Index 0x9h  |

| 10.5.7. | North Bridge Header Type Register                      | NB_HEAD             | PCI Config     |         | Index 0x0Eh |

| 10.5.8. | North Bridge Control Register                          | NB_Control          | PCI Config     |         | Index 0x50h |

| 10.5.9. | North Bridge PCI Error Status Reg-<br>ister            | NB_Error_<br>Status | PCI Config     |         | Index 0x54h |

|         |                                                        |                     |                |         |             |

| 10.7.   | South Bridge PCI Function 0<br>Configuration Registers |                     |                | 0xCF8h  |             |

| 10.7.1. | South BridgeVendor Identification<br>Register          | SB_Vend_ID0         | PCI config F#0 | 0xCFCh  | Index 0x0h  |

| 10.7.2. | South Bridge Device Identification<br>Register         | SB_Device_<br>ID0   | PCI Config F#0 |         | Index 0x2h  |

| 10.7.3. | South Bridge PCI Command Reg-<br>ister                 | SB_<br>Command0     | PCI Config F#0 |         | Index 0x4h  |

| 10.7.4. | South Bridge PCI Status Register                       | SB_Status0          | PCI Config F#0 |         | Index 0x6h  |

| 10.7.5. | South Bridge PCI Revision Id Reg-<br>ister             | SB_Rev_ID0          | PCI Config F#0 |         | Index 0x8h  |

| 10.7.6. | South Bridge Device Class Code<br>Register             | SB_Class_<br>Code0  | PCI Config F#0 |         | Index 0x9h  |

| 10.7.7. | South Bridge Header Type Regis-<br>ter                 | SB_Header0          | PCI Config F#0 |         | Index 0xEh  |

| 10.7.8. | South Bridge Miscellaneous Regis-<br>ter               | SB_Misc0            |                |         | Index 040h  |

|         | ·                                                      |                     |                |         |             |

| 10.8.   | South Bridge PCI Function 1<br>Configuration Registers |                     |                | 0xCF8h  |             |

| 10.8.1. | South Bridge Vendor Identification<br>Register         | SB_Vend_ID1         | PCI config F#1 | 0xCFCh  | Index 0x0h  |

| 10.8.2. | South Bridge Device Identification Register            | SB_Device_<br>ID1   | PCI Config F#1 |         | Index 0x2h  |

| 10.8.3. | South Bridge PCI Command Reg-<br>ister                 | SB_<br>Command1     | PCI Config F#1 |         | Index 0x4h  |

| 10.8.4. | South Bridge PCI Status Register                       | SB_Status1          | PCI Config F#1 |         | Index 0x6h  |

| 10.8.5. | South Bridge Revision ID Register                      | SB_Rev_ID1          | PCI Config F#1 |         | Index 0x8h  |

| 10.8.6. | South Bridge Programming Inter-<br>face Register       | Prog_Interf         | PCI Config F#1 |         | Index 0x9h  |

| 10.8.7. | South Bridge Sub-Class Code<br>Register                | Sub_Class           | PCI Config F#1 |         | Index 0xAh  |

| 10.8.8. | South Bridge Base-Class code<br>Register               | Base_Class          | PCI Config F#1 |         | Index 0xBh  |

| 10.8.9. | South Bridge Latency Timer control<br>Register         | Latency_Timer       | PCI Config F#1 |         | Index 0xDh  |

| Section  | Register Name                                      | Mnemonic            | Purpose        | Address | Access type |

|----------|----------------------------------------------------|---------------------|----------------|---------|-------------|

| 10.8.10. | South Bridge Header Type Regis-<br>ter             | Header_Time         | PCI Config F#1 |         | Index 0xEh  |

| 10.8.11. | South Bridge Base Address 0 Reg-<br>ister          | Base0               | PCI Config F#1 |         | Index 0x10h |

| 10.8.12. | South Bridge Base Address 1 Reg-<br>ister          | Base1               | PCI Config F#1 |         | Index 0x14h |

| 10.8.13. | South Bridge Base Address 2 Reg-<br>ister          | Base2               | PCI Config F#1 |         | Index 0x18h |

| 10.8.14. | South Bridge Base Address 3 Reg-<br>ister          | Base3               | PCI Config F#1 |         | Index 0x1Ch |

| 10.8.15. | South Bridge Base Address 4 Reg-<br>ister          | Base4               | PCI Config F#1 |         | Index 0x20h |

| 10.8.16. | South Bridge Primary IDE Timing Register           | Prime_IDE_<br>Time  | PCI Config F#1 |         | Index 0x40h |

| 10.8.17. | South Bridge Secondary IDE Tim-<br>ing Register    | Second_IDE_<br>Time | PCI Config F#1 |         | Index 0x44h |

| 10.8.18. | South Bridge Miscellaneous Regis-<br>ter           | SB_Misc1            | PCI Config F#1 |         | Index 0x48h |

|          |                                                    |                     |                |         |             |

| 9.5      | ISA standard Registers                             |                     |                |         |             |

| 9.5.1    | DMA 1 Controller Registers                         | DMA_1               | IO             | 0000h   |             |

| 9.5.1    | DMA 1 Channel 0 Base and Cur-<br>rent Count        | DMA1_CBC0           | IO             | 0001h   |             |

| 9.5.1    | DMA 1 Channel 1 Base and Cur-<br>rent Address      | DMA1_CBA1           | IO             | 0002h   |             |

| 9.5.1    | DMA 1 Channel 1 Base and Cur-<br>rent Count        | DMA1_CBC1           | IO             | 0003h   |             |

| 9.5.1    | DMA 1 Channel 2 Base and Cur-<br>rent Address      | DMA1_CBA2           | IO             | 0004h   |             |

| 9.5.1    | DMA 1 Channel 2 Base and Cur-<br>rent Count        | DMA1_CBC2           | IO             | 0005    |             |

| 9.5.1    | DMA 1 Channel 3 Base and Cur-<br>rent Address      | DMA1_CBA3           | IO             | 0006h   |             |

| 9.5.1    | DMA 1 Channel 3 Base and Cur-<br>rent Count        | DMA1_CBC3           | IO             | 0007h   |             |

| 9.5.1    | DMA 1 Read Status / Write Com-<br>mand Register    | DMA1_RSWC           | IO             | 0008h   |             |

| 9.5.1    | DMA 1 Request Register                             | DMA1_RR             | 10             | 0009h   |             |

| 9.5.1    | DMA 1 Read Command / Write<br>Single Mask Register | DMA1_RCWS<br>M      | IO             | 000Ah   |             |

| 9.5.1    | DMA 1 Mode Register                                | DMA1_Mode           | IO             | 000Bh   |             |

| 9.5.1    | DMA 1 Set / Clear Byte Pointer Flip                | DMA1_SCBPF<br>F     | IO             | 000Ch   |             |

| 9.5.1    | DMA 1 Read Temp Register / Mas<br>ter Clear        | DMA1_RTMC           | IO             | 000Dh   |             |

| 9.5.1    | DMA 1 Clear Mask / Clear All<br>Request            | DMA1_CMCA<br>R      | IO             | 000Eh   |             |

| 9.5.1    | DMA 1 Read / Write all Mask Reg-<br>ister Bits     | DMA1_RWMB           | IO             | 000Fh   |             |

| 9.5.2    | Interrupt Controller 1 Registers                   | IC_1                | IO             | 0020h   |             |

| Section | Register Name                       | Mnemonic           | Purpose | Address | Access type |

|---------|-------------------------------------|--------------------|---------|---------|-------------|

| 9.5.3   | Interval Timer Registers            | IT_1               | IO      | 0040h   |             |

|         | Interval Timer Register Counter 0   | IT_0               | Ю       | 0040h   |             |

| 9.5.3   | Count                               | 11_0               | 10      | 004011  |             |

|         | Interval Timer Register Counter 1   | IT 1               | ю       | 0041h   |             |

| 9.5.3   | Count                               | 11_1               | 10      | 004111  |             |

|         | Interval Timer Register Counter 2   | IT 2               | 10      | 0042h   |             |

| 9.5.3   | Count                               | 11_2               | 10      | 004211  |             |

| 9.5.3   | Command Mode Register               | IT_3               | IO      | 0043h   |             |

| 9.5.4   | Port B Register                     | Port _B            | 10      | 0061h   |             |

| 9.5.5   | Port 60h Register                   | Port_60            | 10      | 0060h   |             |

| 9.5.5   | Port 64h Register                   | Port_64            | 10      | 0064h   |             |

| 9.5.6   | Port 70 Register                    | Port_70            | 10      | 0070h   |             |

| 9.5.7   | Interrupt Controller 2 Registers    | IC_2               | 10      | 00A0h   |             |

| 9.5.8   | DMA Controller 2 Registers          | DMA_Cont2          | 10      |         |             |

|         | DMA 2 Channel 0 Base and Cur-       |                    | 10      | 00001   |             |

| 9.5.8   | rent Address                        | DMA2_CBA0          | IO      | 00C0h   |             |

|         | DMA2 Channel 0 Base and Current     | DMA2 CBC0          | IO      | 00C2h   |             |

| 9.5.8   | Count                               | DMA2_CBC0          | 10      | 00C2n   |             |

|         | DMA 2 Channel 1 Base and Cur-       |                    | 10      |         |             |

| 9.5.8   | rent Address                        | DMA2_CBA1          | IO      | 00C4h   |             |

|         | DMA 2 Channel 1 Base and Cur-       |                    | 10      | 00001   |             |

| 9.5.8   | rent Count                          | DMA2_CBC1          | IO      | 00C6h   |             |

|         | DMA 2 Channel 2 Base and Cur-       |                    | 10      | 00001   |             |

| 9.5.8   | rent Address                        | DMA2_CBA2          | IO      | 00C8h   |             |

| 0.010   | DMA 2 Channel 2 Base and Cur-       | <b>D</b> 1110 0D00 | 10      | 000.01  |             |

| 9.5.8   | rent Count                          | DMA2_CBC2          | IO      | 00CAh   |             |

|         | DMA 2 Channel 3 Base and Cur-       |                    | 10      |         |             |

| 9.5.8   | rent Address                        | DMA2_CBA3          | IO      | 00CCh   |             |

|         | DMA 2 Channel 3 Base and Cur-       | D1440.0D00         | 10      | 00051   |             |

| 9.5.8   | rent Count                          | DMA2_CBC3          | IO      | 00CEh   |             |

|         | DMA 2 Read Status / Write Com-      |                    | Ю       | 00D0h   |             |

| 9.5.8   | mand Register                       | DMA2_RSWC          | 10      | UUDUN   |             |

| 9.5.8   | DMA 2 Request Register              | DMA2_RR            | IO      | 00D2h   |             |

|         | DMA 2 Read Command / Write          | DMA2_RCWS          | 10      | 000 41  |             |

| 9.5.8   | Single Mask Register                | М                  | IO      | 00D4h   |             |

| 9.5.8   | DMA 2 Mode Register                 | DMA2_Mode          | IO      | 00D6h   |             |

|         | DMA 2 Set / Clear Byte Pointer Flip | DMA2_SCBPF         | 10      | 00D0h   |             |

| 9.5.8   | - Flop                              | F                  | IO      | 00D8h   |             |

|         | DMA 2 Read Temporary / Master       | DIMA DTMO          | 10      | 000041  |             |

| 9.5.8   | Clear                               | DMA2_RTMC          | IO      | 00DAh   |             |

|         | DMA 2 Clear Mask / Clear All        | DMA2_CMCA          | 10      | 0000    |             |

| 9.5.8   | Requests Register                   | R                  | IO      | 00DCh   |             |

|         | DMA 2 Read / Write all Mask Reg-    | DMA2_RWMR          | 10      | 00DEh   |             |

| 9.5.8   | ister Bits                          | В                  | 10      | UUDEN   |             |

| 9.5.9   | DMA Page Registers                  | DMA_Page           | 10      |         |             |

|         | DMA Page Registers Port 80h         | Dart 00            | 10      | 0000    |             |

| 9.5.9   | (reserved)                          | Port_80            | IO      | 0080h   |             |

| 9.5.9   | DMA Page Register Channel 2         | DMA_PRC2           | IO      | 0081h   |             |

| 9.5.9   | DMA Page Register Channel 3         | DMA_PRC3           | IO      | 0082h   |             |

| 9.5.9   | DMA Page Register Channel 1         | DMA_PRC1           | IO      | 0082h   |             |

| Section          | Register Name                         | Mnemonic          | Purpose       | Address | Access type |

|------------------|---------------------------------------|-------------------|---------------|---------|-------------|

| 9.5.9            | DMA Page Register Port 84h            | Port_84           | 10            | 0084h   | (Reserved)  |

| 9.5.9            | DMA Page Register Port 85h            | Port_85           | Ю             | 0085h   | (Reserved)  |

| 9.5.9            | DMA Page Register Port 86h            | Port_86           | Ю             | 0086h   | (Reserved)  |

| 9.5.9            | DMA Page Register Channel 0           | DMA_PRC0          | 10            | 0087h   |             |

| 9.5.9            | DMA Page Register Port 87h            | Port_87           | 10            | 0088h   |             |

| 9.5.9            | DMA Page Register Channel 6           | DMA_PRC6          | 10            | 0089h   |             |

| 9.5.9            | DMA Page Register Channel 7           | DMA_PRC7          | IO            | 008Ah   |             |

| 9.5.9            | DMA Page Register Channel 5           | DMA_PRC5          | IO            | 008Bh   |             |

| 9.5.9            | DMA Page Register Port 8Bh            | Port_8B           | 10            | 008Ch   | (Reserved)  |

| 9.5.9            | DMA Page Register Port 8Ch            | Port_8C           | 10            | 008Dh   | (Reserved)  |

| 9.5.9            | DMA Page Register Port 8Dh            | Port_8D           | 10            | 008Eh   | (Reserved)  |

| 9.5.9            | DMA Page Register Port 8Eh            | Port_8E           | 10            | 008Fh   | (Reserved)  |

| 0.0.0            |                                       |                   |               | I       | × /         |

| 9.6              | ISA Configuration Registers           | [ ]               |               | 0022h   |             |

| 9.6.1            | Miscellaneous Control Register 0      | Misc_Cont0        | Configuration | 0023h   | Index 050h  |

| 9.6.2            | Miscellaneous Control Register 1      | Misc Cont1        | Configuration | -       | Index 051h  |

| 9.6.3            | PIRQA Routing control Register 0      | PAR Cont0         | Configuration |         | Index 052h  |

| 9.6.4            | PIRQB Routing control Register 0      | PBR Cont0         | Configuration |         | Index 053h  |

| 9.6.6            | PIRQC Routing control Register 0      | PCR Cont0         | Configuration |         | Index 054h  |

| 9.6.7            | PIRQD Routing control Register 0      | PDR Cont0         | Configuration |         | Index 055h  |

| 9.0.7            | Interrupt Level Control Register 0    | IRQ_Lev_Cont      |               |         |             |

| 9.6.8            | Interrupt Level Control Register 0    | 0                 | Configuration |         | Index 056h  |

| 9.6.9            | Interrupt Level Control Register 1    | IRQ_Lev_Cont<br>1 | Configuration |         | Index 057h  |

| 9.6.10           | IPC Configuration Register            | IPC_Conf          | Configuration |         | Index 001h  |

| 9.6.11           | VMI IRQ Routing Control Register      | VIR_Cont          | Configuration |         | Index 058h  |

| 9.6.12           | ISA Syncronizer Bypass Register       | ISA_Sync          | Configuration |         | Index 059h  |

|                  |                                       |                   |               |         |             |

| 11.3             | VGA registers                         |                   |               |         |             |

| 11.4             | General Registers                     |                   |               |         |             |

| 11.4.1           | Motherboard Enable Register           | MBEN              |               | 0x094h  |             |

| 11.4.2           | Add-in VGA Enable Register            | ADDEN             |               | 0x46E8h |             |

|                  | Video Subsystem Enable 1 Regis-       | VSE1              |               | 0x102h  |             |

| 11.4.3           | ter                                   | VOLI              |               | 0x10211 |             |

|                  | Video Subsystem Enable 2 Regis-       | VSE2              |               | 0x3C3h  |             |

| 11.4.4           | ter                                   | VOLZ              |               |         |             |

|                  | Miscellaneous Output Register         | MISC              |               | 0x3CC/  |             |

| 11.4.5           |                                       |                   |               | 0x3C2h  |             |

| 11.4.6           | Input Status Register #0              | INP0              |               | 0x3C2h  |             |

| 11.4.7           | Input Status Register #1              | INP1              |               | 0x3XAh  |             |

| 11.5             | Sequencer Registers                   |                   |               |         |             |

| 11.5.1           | Sequencer Index Register              | SRX               |               | 0x03C4h |             |

| 11.5.2           | Sequencer Reset Register              | SR0               |               | 0x03C5h | Index 000h  |

|                  | Sequencer Clocking Mode Regis-        | SR1               |               |         | Index 001h  |

| 11.5.3           | ter                                   | JK I              |               |         | Index 00111 |

| 11.5.4           | Sequencer Plane Mask Register         | SR2               |               |         | Index 002h  |

| 14 E E           | Sequencer Character Map Regis-        | SR3               |               |         | Index 003h  |

| 11.5.5           | ter<br>Soguencer Memory Mode Register | SP4               |               |         | Index 001b  |

| 11.5.5<br>11.5.6 | ter<br>Sequencer Memory Mode Register | SR4               |               |         | Index 004   |

| Section            | Register Name                                                       | Mnemonic   | Purpose    | Address | Access type |

|--------------------|---------------------------------------------------------------------|------------|------------|---------|-------------|

|                    | Extended Register Lock/Unlock                                       | SR6        |            |         | Index 006h  |

| 11.5.7             | Register                                                            | GILO       |            |         |             |

| 11.6               | Graphics Controller Registers                                       |            |            |         |             |

| 11.6.1             | Graphics Controller Index Register                                  | GRX        |            | 0x03CEh |             |

| 11.6.2             | Graphics Set/Reset Register                                         | GR0        |            | 0x03CFh | Index 000h  |

| 11.6.3             | Graphics Enable Set/Reset Regis-<br>ter                             | GR1        |            |         | Index 001h  |

| 11.6.4             | Graphics Color Compare Register                                     | GR2        |            |         | Index 002h  |

| 11.6.5             | Raster Op/Rotate Count Register                                     | GR3        |            |         | Index 003h  |

|                    | Graphics Read Map Select Regis-                                     | GR4        |            |         | Index 004h  |

| 11.6.6             | ter                                                                 | 0.5.5      |            |         |             |

| 11.6.7             | Graphics Mode Register                                              | GR5        |            |         | Index 005h  |

| 11.6.8             | Graphics Miscellaneous Register                                     | GR6        |            |         | Index 006h  |

| 11.6.9             | Graphics Color Don't Care Register                                  | GR7        |            |         | Index 007h  |

| 11.6.10            | Graphics Bit Mask Register                                          | GR8        |            |         | Index 008h  |

| 11.7               | Attribute Controller Registers                                      |            |            |         |             |

| 11.7.1             | Attribute Controller Index Register                                 | ARX        |            | 0x3C0h  |             |

|                    | Attribute Palette Registers                                         | AR0 - ARF  |            | 0x3C1/  |             |

| 11.7.2             | _                                                                   |            |            | 0x3C0h  |             |

|                    | Attribute Ctrl Mode Register                                        | AR10       |            | 0x3C1/  |             |

| 11.7.3             |                                                                     | ,          |            | 0x3C0h  |             |

|                    | Attribute Ctrl Overscan Color Reg-                                  | AR11       |            | 0x3C1/  |             |

| 11.7.4             | ister                                                               |            |            | 0x3C0h  |             |

|                    | Attribute Color Plane Enable Reg-                                   | AR12       |            | 0x3C1/  |             |

| 11.7.5             | ister                                                               | ,          |            | 0x3C0h  |             |

|                    | Attribute Horz Pixel Panning Regis-                                 | AR13       |            | 0x3C1/  |             |

| 11.7.6             | ter                                                                 | 7.1.10     |            | 0x3C0h  |             |

|                    | Attribute Color Select Register                                     | AR14       |            | 0x3C1/  |             |

| 11.7.7             |                                                                     |            |            | 0x3C0h  |             |

|                    |                                                                     |            |            |         |             |

| 11.8               | CRT Controller Registers                                            |            |            |         |             |

| 11.8.1             | Index Register                                                      | CRX        | see Note 1 | 0x3X4h  |             |

| 11.8.2             | Horizontal Total Register                                           | CR0        | see Note 1 | 0x3X5h  | Index 000h  |

| 11.8.3             | Horiz display End Register                                          | CR1        |            |         | Index 001h  |

| 11.8.4             | Horiz Blanking Start Register                                       | CR2        |            |         | Index 002h  |

| 11.8.5             | Horiz Blanking End Register                                         | CR3        |            |         | Index 003h  |

| 11.8.6             | Horiz Retrace Start Register                                        | CR4        |            |         | Index 004h  |

| 11.8.7             | Horizontal Retrace end Register                                     | CR5        |            |         | Index 005h  |

| 11.8.8             | Vertical Total Register                                             | CR6        |            |         | Index 006h  |

| 11.8.9             | Overflow Register                                                   | CR7        |            |         | Index 007h  |

|                    | Screen A Preset Row Scan Regis-                                     | CR8        |            |         | Index 008h  |

| 11.8.10            | ter                                                                 |            |            |         | INGEX UUUII |

| 11.8.11            | Character Cell Height Register                                      | CR9        |            |         | Index 009h  |

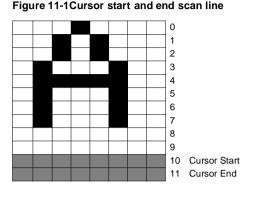

| 11.8.12            | Cursor Start Register                                               | CRA        |            |         | Index 00Ah  |

| 11.8.13            | Cursor End Register                                                 | CRB        |            | 1       | Index 00Bh  |

| 11.8.14            | Start Address High Register                                         | CRC        |            |         | Index 00Ch  |

| 11.8.15            | Start Address Low Register                                          | CRD        |            | 1       | Index 00Dh  |

| 11.0.10            |                                                                     |            |            | +       |             |

|                    |                                                                     | CRE        |            |         | Index 00Eh  |

| 11.8.16<br>11.8.17 | Text Cursor Offset High Register<br>Text Cursor Offset Low Register | CRE<br>CRF |            |         | Index 00Eh  |

| Section | Register Name                       | Mnemonic     | Purpose    | Address  | Access type |

|---------|-------------------------------------|--------------|------------|----------|-------------|

| 11.8.19 | Vertical Retrace End Register       | CR11         |            |          | Index 011h  |

| 11.8.20 | Vertical Display End Register       | CR12         |            |          | Index 012h  |

| 11.8.21 | Offset Register                     | CR13         |            |          | Index 013h  |

| 11.8.22 | Underline Location Register         | CR14         |            |          | Index 014h  |

| 11.8.23 | Vertical Blanking Start reg         | CR15         |            |          | Index 015h  |

| 11.8.24 | Vertical Blanking End Register      | CR16         |            |          | Index 016h  |

| 11.8.25 | Mode Register                       | CR17         |            |          | Index 017h  |

| 11.8.26 | Line Compare Register               | CR18         |            |          | Index 018h  |

| 11.8.27 | Graphics Control Data               | CR22         |            |          | Index 019h  |

| 11.8.28 | Attribute Address Flipflop          | CR24         |            |          | Index 020h  |

| 11.8.29 | Attribute Index Readback            | CR26         |            |          | Index 021h  |

| 11.0.29 | Attribute index Readback            | 01120        |            |          | Index 62 m  |

| 11.9    | VGA Extended Registers              |              | see Note 1 | 0x3X4h   |             |

| 11.9    | Repaint Control Register 0          | CR19         | see Note 1 | 0x3X5h   | Index 019h  |

| 11.9.1  | Repaint Control Register 0          | CR1A         |            | 0,0,1011 | Index 01Ah  |

|         | Repaint Control Register 2          | CR1B         |            |          | Index 017th |

| 11.9.3  | Repaint Control Register 2          | CR1D<br>CR1C |            |          | Index 01Dh  |

| 11.9.4  |                                     | CR1D         |            |          | Index 01Dh  |

| 11.9.5  | Page Register 0                     | CR1D<br>CR1E |            |          | Index 01Eh  |

| 11.9.6  | Page Register 1                     | CRIE         |            |          | Index UTEN  |

|         | Graphics Extended Enable Regis-     | CR1F         |            |          | Index 01Fh  |

| 11.9.7  | ter                                 |              |            |          |             |

|         | Graphics Extended GBASE Regis-      | CR20         |            |          | Index 020h  |

| 11.9.8  | ter                                 |              |            |          |             |

|         | Graphics Extended Aperture Reg-     | CR21         |            |          | Index 021h  |

| 11.9.9  | ister                               | 00.05        |            |          |             |

| 11.9.10 | Repaint Control Register 4          | CR25         |            |          | Index 025h  |

| 11.9.11 | Repaint Control Register 5          | CR27         |            |          | Index 027h  |

| 11.9.12 | Palette Control Register            | CR28         |            |          | Index 028h  |

| 11.9.13 | Cursor Height Register              | CR29         |            |          | Index 029h  |

| 11.9.14 | Cursor Color 0 Register A           | CR2A         |            |          | Index 02Ah  |

| 11.9.15 | Cursor Color 0 Register B           | CR2B         |            |          | Index 02Bh  |

| 11.9.16 | Cursor Color 0 Register C           | CR2C         |            |          | Index 02Ch  |

| 11.9.17 | Cursor Color 1 Register A           | CR2D         |            |          | Index 02Dh  |

| 11.9.18 | Cursor Color 1 Register B           | CR2E         |            |          | Index 02Eh  |

| 11.9.19 | Cursor Color 1 Register C           | CR2F         |            |          | Index 02Fh  |

|         | Graphics Cursor Address Register    | CR30         |            |          | Index 030h  |

| 11.9.20 | 0                                   | CK30         |            |          | Index 03011 |

|         | Graphics Cursor Address Register    | CP21         |            |          | Index 031h  |

| 11.9.21 | 1                                   | CR31         |            |          | index 031h  |

|         | Graphics Cursor Address Register    | 0000         |            |          | Inday: 000h |

| 11.9.22 | 2                                   | CR32         |            |          | Index 032h  |

| 11.9.23 | –<br>Urgent Start Register          | CR33         |            |          | Index 033h  |

|         | Displayed Frame Y Offset 0 Regis-   | 0504         |            | 1 1      | lada. 00.4  |

| 11.9.24 | ter                                 | CR34         |            |          | Index 034h  |

|         | Displayed Frame Y Offset 1 Regis-   | 05.27        |            |          | 1 1 227     |

| 11.9.25 | ter                                 | CR35         |            |          | Index 035h  |

| 11.9.26 | Interlace Half Field Start Register | CR39         |            |          | Index 039h  |

| 11.9.27 | Implementation Number Register      | CR3A         |            | +        | Index 03Ah  |

|         | Graphics Version Register           | CR3B         |            |          | Index 03Bh  |

| 11.9.28 | SDRAM Timing Parameter Register     | CR3B<br>CR3C |            |          | Index 03Ch  |

| 11.9.29 | Survivi Timing Parameter Register   | 0130         |            |          | ITUER USOIT |

| Section                       | Register Name                        | Mnemonic         | Purpose                  | Address    | Access type                |

|-------------------------------|--------------------------------------|------------------|--------------------------|------------|----------------------------|

| 11.9.30                       | SDRAM Arbitration control Register 0 | CR3D             |                          |            | Index 03Dh                 |

| 11.9.31                       | Miscellaneous Test Register          | CR3E             |                          |            | Index 03Eh                 |

| 11.9.32                       | DDC Control Register                 | CR3F             |                          |            | Index 03Fh                 |

| 11.9.33                       | TV Interface Control Register        | CR40             |                          |            | Index 040h                 |

| 11.3.55                       | TV Horizontal Active Video Start A   |                  |                          |            |                            |

| 11.9.34                       | Register                             | CR41             |                          |            | Index 041h                 |

| 11.0.04                       | TV Horizontal Active Video Start B   |                  |                          |            |                            |

| 11.9.35                       | Register                             | CR42             |                          |            | Index 042h                 |

| 11.9.36                       | TV Horizontal Sync End A Register    | CR43             |                          |            | Index 043h                 |

| 11.9.37                       | TV Horizontal Sync End B Register    | CR44             |                          |            | Index 044h                 |

| 11.3.57                       | TV Honzontal Oyne End D Register     |                  |                          |            | index of fin               |

| 11.12                         | RAMDAC registers                     |                  |                          | I          |                            |

| 11.12                         | Palette Pixel Mask Register          | Pixel Mask       |                          | 0x3C6h     |                            |

| 11.12.1                       | Palette Read index Register          | Read index       |                          | 0x3C7h     |                            |

|                               | Palette State Register               | Palette_State    |                          | 0x3C7h     |                            |

| 11.12.3                       | Palette Write Index Register         | Write index      |                          | 0x3C8h     |                            |

| 11.12.4                       |                                      | Palette data     |                          | 0x3C9h     |                            |

| 11.12.5                       | Palette Data Register                | Falelle_uala     |                          | 0x3C911    |                            |

| 11.12                         | DCI // Control Deistars              |                  |                          | 22h        |                            |

| 11.13                         | DCLK Control Rgisters                |                  | DCI Config               | 22h<br>23h | Index 0x10h                |

| 11.13.1                       | DCLK Control Register 00             | DCLK00<br>DCLK01 | PCI Config<br>PCI Config | Z3N        | Index 0x42h<br>Index 0x43h |

| 11.13.2                       | DCLK Control Register 01             |                  | 0                        |            |                            |

| 11.13.3                       | DCLK Control Register 10             | DCKL10           | PCI Config               |            | Index 0x44h                |

| 11.13.4                       | DCLK Control Register 11             | DCLK11           | PCI Config               |            | Index 0x45h                |

| 11.13.5                       | DCLK Control Register 20             | DCLK20           | PCI Config               |            | Index 0x46h                |

| 11.13.6                       | DCLK Control Register 21             | DCLK21           | PCI Config               |            | Index 0x47h                |

| 11.13.7                       | DCLK Control Register 30             | DCLK30           | PCI Config               |            | Index 0x48h                |

| 11.13.8                       | DCLK Control Register 31             | DCLK31           | PCI Config               |            | Index 0x49h                |

|                               |                                      |                  |                          |            |                            |

| 12.5                          | VGA Operand Source                   |                  |                          |            |                            |

| 12.9.1                        | Back Ground Color Register           | Background       |                          | 8400000h   | Index 0x004h               |

| 12.9.2                        | Cursor Coordinate Register           | Cursor_XY        |                          |            | Index 0x11Ch               |

| 12.9.3                        | Top of Data FIFO Register            | Data_Port        |                          |            | Index 0x804h               |

|                               | Destination Operand Base Address     | Dst base         |                          |            | Index 0x018h               |

| 12.9.4                        | Register                             | _                |                          |            |                            |

| 12.9.5                        | Destination Pitch Register           | Dst_pitch        |                          |            | Index 0x028h               |

|                               | Destination Operand Coordinate       | Dst XY           |                          | 8410000h   |                            |

| 12.9.6                        | Register                             | -                |                          |            |                            |

| 12.9.7                        | Foreground Color Register            | Foreground       |                          | 8400000h   | Index 0x034h               |

| 12.9.8                        | Height Register                      | Height           |                          |            | Index 0x048h               |

|                               | Pattern Base Address Operand         | Pattern          |                          |            | Index 0x058h               |

| 12.9.9                        | Register                             |                  |                          |            |                            |

| 12.9.10                       | Pixel Depth Operand Register         | Pixel_depth      |                          |            | Index 0x07Ch               |

| 12.9.11                       | Raster Operation Register            | ROP              |                          |            | Index 0x08Ch               |

|                               | Source Base Address Operand          | Src base         |                          |            | Index 0x098h               |

| 12.9.12                       | Register                             | SIC_Dase         |                          |            | ILLEY OVOSOIL              |

| 12.9.13                       | Source Pitch Operand Register        | Src_pitch        |                          |            | Index 0x0ACh               |

| 12.9.14                       | Source Coordinate Register           | Src_XY           |                          |            | Index 0x0BDh               |

| 12.3.14                       |                                      |                  |                          | 1          | Index 0x908                |

|                               | Status Register                      | Status           |                          |            | muex 0x906                 |

| 12.9.14<br>12.9.15<br>12.9.16 | Status Register<br>Width Register    | Status<br>Width  |                          |            | Index 0x908                |

| Section  | Register Name                               | Mnemonic     | Purpose    | Address           | Access type |

|----------|---------------------------------------------|--------------|------------|-------------------|-------------|

|          | SRC Transparency Compare Reg-               | SRC_         |            |                   | Index 0xECh |

| 12.9.18  | ister                                       | transparency |            |                   | mack ove on |

|          | DST Transparency Compare Reg-               | DST_         |            |                   | Index 0xFCh |

| 12.9.19  | ister                                       | transparency |            |                   |             |

|          |                                             |              |            |                   |             |

| 13.6     | Video Input Port Registers                  |              |            | 0.5               |             |

| 13.6.1   | Frame Buffer Address Readback<br>Register   | Fb1_adr      |            | GBase<br>+600000h | Index 0x00h |

| 13.6.2   | Video Input Port Configuration<br>Register  | Vin_cfg      |            |                   | Index 0x04h |

| 13.6.3   | Video Input Port Status Register            | Vin_stat     |            |                   | Index 0x08h |

| 13.6.4   | Video Input Buffer Addr 0                   | Vin_ad0      |            |                   | Index 0x0Ch |

| 13.6.5   | Video Input Buffer Addr 1                   | Vin_ad1      |            |                   | Index 0x10h |

| 13.6.6   | Video Input Desination Pitch                | Vin_dp       |            |                   | Index 0x14h |

| 13.6.7   | External Timing Generator 1                 | Vtg_ext1     |            |                   | Index 0x28h |

| 13.6.8   | External Timing Generator 2                 | Vtg_ext2     |            |                   | Index 0x2Ch |

| 13.6.9   | Horizontal Timing Generator                 | Vtg_ht       |            |                   | Index 0x30h |

| 13.6.10  | Video Timing Generator                      | Vtg_vg       |            |                   | Index 0x34h |

|          |                                             | 0-0          |            | 1                 |             |

| 13.10    | Video Output Port Register                  |              |            | GBase+4CA         | 000h        |

| 13.10.1  | Register_0.Configuration0                   | Config0      |            |                   | Index 000h  |

| 13.10.2  | Register_1.Configuration1                   | Config1      |            |                   | Index 001h  |

| 13.10.3  | Register_2.Configuration2                   | Config2      |            |                   | Index 002h  |

| 13.10.4  | Register_3.Configuration3                   | Config3      |            |                   | Index 003h  |

| 13.10.5  | Register_4.Configuration4                   | Config4      |            |                   | Index 004h  |

| 13.10.6  | Register_5.Configuration5                   | Config5      |            |                   | Index 005h  |

| 13.10.7  | Register_6.Configuration6                   | Config6      |            |                   | Index 006h  |

| 13.10.9  | Register_9.Status                           | Stat9        |            |                   | Index 009h  |

| 13.10.10 | Register_10.Increment_dfs                   | Incr_10      |            |                   | Index 010h  |

| 13.10.10 | Register_11.Increment_dfs                   | Incr_11      |            |                   | Index 011h  |

| 13.10.10 | Register_12.Increment_dfs                   | Incr_12      |            |                   | Index 012h  |

| 13.10.11 | Register_13.Phase_dfs                       | Phase_13     |            |                   | Index 013h  |

| 13.10.11 | Register 14.Phase dfs                       | Phase_14     |            |                   | Index 014h  |

| 13.10.18 | Register_21:line_reg=ltarg[8:1]             | Reg21        |            |                   | Index 021h  |

| 13.10.18 | Register_22:line_reg=ltarg[0] and Iref[8:2] | Reg22        |            |                   | Index 022h  |

| 13.10.18 | Register_23:line_reg=Iref[1:0]              | Reg23        |            | 1 1               | Index 023h  |

| 13.10.19 | Register_31.cgms_bit [1:4]                  | Reg31        |            |                   | Index 031h  |

| 13.10.19 | Register_32.cgms_bit [5:12]                 | Reg32        |            | 1                 | Index 032h  |

| 13.10.19 | Register_33.cgms_bit [13:20]                | Reg33        |            | 1 1               | Index 033h  |

| 13.10.13 | Register 39.cccf1                           | Reg39        |            | 1                 | Index 039h  |

| 13.10.21 | Register_40.cccf1                           | Reg40        |            |                   | Index 040h  |

| 13.10.21 | Register_41.cccf2                           | Reg41        |            | 1                 | Index 041h  |

| 13.10.22 | Register_42.cccf2                           | Reg42        |            |                   | Index 042h  |

| 13.10.22 | Register_43.cclif1                          | Reg43        |            |                   | Index 043h  |

| 10.10.23 |                                             |              |            |                   |             |

| 13.11    | Video Pipeline Registers                    |              |            |                   |             |

| 13.11.1  | Source Specification Registers              |              | see Note 2 | X600000h          |             |

| 10.11.1  | Video Source Base Register                  | Video_Src_   |            |                   |             |

|          |                                             | Base         |            | 1                 | Index 0x0h  |

| Section   | Register Name                                        | Mnemonic               | Purpose       | Address | Access type |

|-----------|------------------------------------------------------|------------------------|---------------|---------|-------------|

| 13.11.1.2 | Video Source Pitch Register                          | Video_Src_<br>Pitch    |               |         | Index 0x4h  |

| 13.11.1.3 | Video Source Dimension Register                      | Video_Src_<br>dim      |               |         | Index 0x8h  |

| 13.11.1.4 | CRTC Burst Length Register                           | CRTC_Burst_<br>Length  |               |         | Index 0xCh  |

| 13.11.1.5 | Video Burst Length Register                          | Video_Burst_<br>Length |               |         | Index 0x10h |

| 13.11.2   | Destination Specification Registers                  |                        |               |         |             |

| 13.11.2.1 | Video Destination Register                           | Video_Dst_XY           |               |         | Index 0x14h |

| 13.11.2.2 | Video Destination Dimension Reg-<br>ister            | Video_Dst_<br>dim      |               |         | Index 0x18h |

| 13.11.3   | Filter Control Register                              |                        |               |         |             |

| 13.11.3.1 | Horizontal Scaling and Decimation Register           | Horiz_Scale            |               |         | Index 0x20h |

| 13.11.3.2 | Vertical Control and Decimation<br>Register          | Vert_Scale             |               |         | Index 0x28h |

| 13.11.3.3 | Color Space Converter Specifica-<br>tion Register    | Color_Con_<br>Spec     |               |         | Index 0x2Ch |

| 13.11.4   | Video and Graphics mixing control<br>Registers       |                        |               |         |             |

| 13.11.4.1 |                                                      | Mix_Mode               |               |         | Index 0x30h |

| 13.11.4.2 |                                                      | Color_Key              |               |         | Index 0x34h |

| 13.11.4.3 |                                                      | Chroma_Key_<br>Low     |               |         | Index 0x38h |

| 13.11.4.4 | Chroma Key High Register                             | Chroma_Key_<br>High    |               |         | Index 0x3Ch |

| 13.11.4.5 | Status Register                                      | Filter_Status          |               |         | Index 0x40h |

| 14.2      | Local Bus Registers                                  |                        | 16 bit access | 22h     |             |

| 14.3      | Local Bus Address Decode Registers                   |                        |               | 23h     |             |

| 14.3.1    | I/O Slot Base Register 0                             | IOAREG0                |               | -       | Index 0x00h |

| 14.3.1    | I/O Slot Base Register 1                             | IOAREG1                |               |         | Index 0x01h |

| 14.3.1    | I/O Slot Base Register 2                             | IOAREG2                |               |         | Index 0x02h |

| 14.3.1    | I/O Slot Base Register 3                             | IOAREG3                |               |         | Index 0x03h |

| 14.3.2    | I/O Slot Mask Register 0                             | IOMREG0                |               |         | Index 0x04h |

| 14.3.2    | I/O Slot Mask Register 1                             | IOMREG1                |               |         | Index 0x05h |

| 14.4      | Local Bus Timing Registers                           |                        |               |         |             |

| 14.4      | Memory Timing Template 0                             | TIMEBANK0              |               |         | Index 0x06h |

| 14.4.1    | Memory Timing Template 0<br>Memory Timing Template 1 | TIMEBANKU<br>TIMEBANK1 |               |         | Index 0x00h |

| 14.4.1    | I/O Timing Template 0                                | TIMEBAINK I            |               |         | Index 0x08h |

| 14.4.2    | I/O Timing Template 0                                | TIMEIO0                |               |         | Index 0x00h |

| 14.4.2    | I/O Timing Template 1                                | TIMEIO1                |               |         | Index 0x03h |

| 14.4.2    | I/O Timing Template 3                                | TIMEIO2                |               |         | Index 0x0Bh |

|           |                                                      |                        |               |         |             |

| 14.5.1    | Local Bus Control Register                           | 0.01/75 0.             |               |         | Index 0x00t |

| 14.5.1    | Control Register                                     | CONTROL                |               |         | Index 0x0Ch |

| 14.5.2    | I/O Width Register                                   | IOWIDTH                |               | l       | Index 0x0Dh |

| Section   | Register Name                                                                                                     | Mnemonic             | Purpose       | Address | Access type |

|-----------|-------------------------------------------------------------------------------------------------------------------|----------------------|---------------|---------|-------------|

|           |                                                                                                                   |                      |               |         |             |

| 15.2      | Power Management Controller Re                                                                                    | egisters:            |               | 0022h   |             |

| 15.2.1    | Timer Register 0                                                                                                  | Timer0               | Configuration | 0023h   | Index 060h  |

| 15.2.2    | Timer Register 1                                                                                                  | Timer1               | Configuration |         | Index 061h  |

| 15.2.3    | Timer Register 2                                                                                                  | Timer2               | Configuration |         | Index 08dh  |

| 15.2.4    | System Activity Enable Register 0                                                                                 | Sys_activ_en0        | Configuration |         | Index 062h  |

| 15.2.5    | System Activity Enable Register 1                                                                                 | Sys_activ_en1        | Configuration |         | Index 063h  |

| 15.2.6    | System Activity Enable Register 2                                                                                 | Sys_activ_en2        | Configuration |         | Index 064h  |