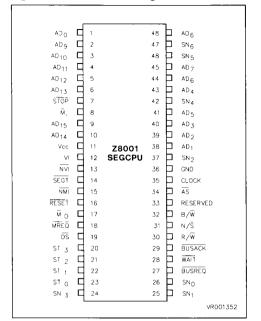

# Z8001 SEGCPU Z8002 CPU

# CENTRAL PROCESSING UNIT

- Regular, easy-to-use architecture.

- Instruction set more powerful than many minicomputers.

- Directly addresses 8M bytes.

- Eight user-selectable addressing modes.

- Seven data types that range from bits to 32-bit long words and word strings.

- System and Normal operating modes.

- Separate code, data and stack spaces.

- Sophisticated interrupt structure.

- Resource-sharing capabilities for multiprocessing systems.

- Multi-programming support.

- Strong compiler support.

- Memory management and protection provided by Z8010 Memory Management Unit.

- 32-bit operations, including signed multiply and divide.

- Z-BUS compatible.

- 4.6 and 10MHz clock rate.

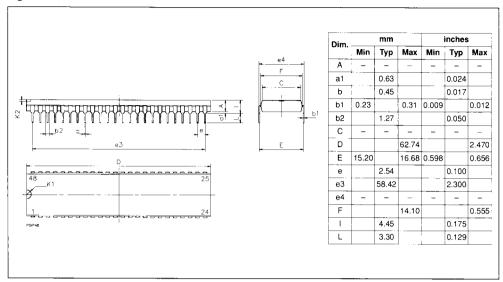

# PDIP48 (Ordering information at the end of the datasheet)

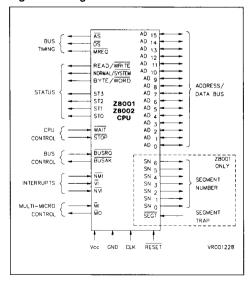

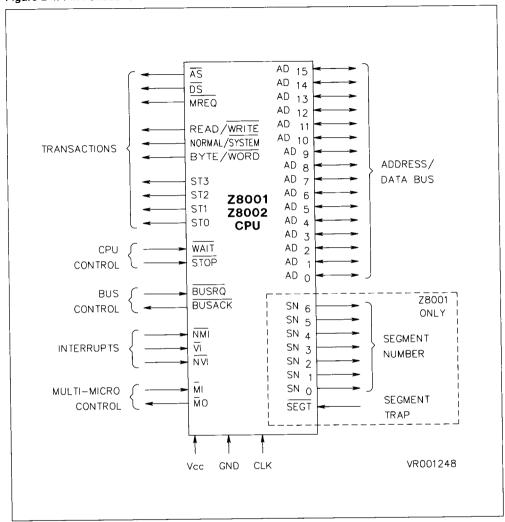

## Figure 1-1. Logic Function

## **GENERAL DESCRIPTION**

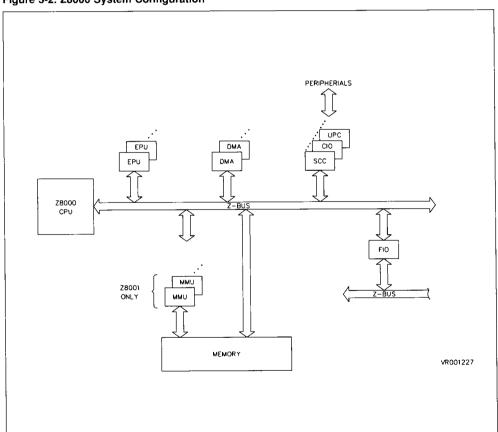

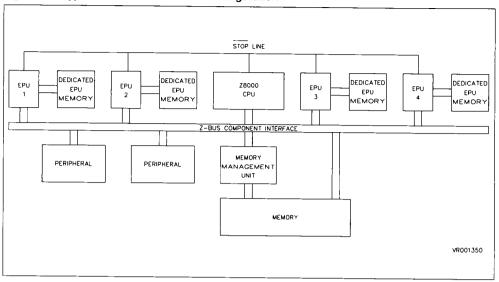

The Z8000 microprocessor has been designed to accommodate a wide range of applications, from the relatively simple to the large and complex. The Z8000 CPU is offered in two versions: the Z8001 and Z8002. Each CPU comes with an entire family of support components: a memory management unit, a DMA controller, serial and parallel I/O controllers and extended processing units - all compatible with the Z-BUS\*. Together with other Z8005 Family components, the advanced CPU architecture provides in an LSI microprocessor design the flexibility and sophisticated features usually associated with mini- or mainframe computers.

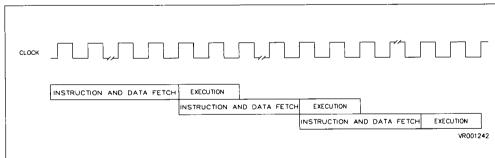

The major architectural features of the Z8000 CPU that enhance throughput and processing power are a general purpose register file, system and normal modes of operation, multiple addressing spaces, a powerful instruction set, numerous addressing modes, multiple stacks, sophisticated interrupt structure, a rich set of data types, separate I/O

## **GENERAL DESCRIPTION** (Continued)

address spaces and, for the Z8001, a large address space and segmented memory addressing. Each of these features is treated in detail in the next section.

These architectural features combine to produce a powerful, versatile microprocessor. The benefits that result from these features are code density, compiler efficiency, support for typical operating system operations, and complex data structures. These topics are treated in this chapter.

The CPU has been designed so that a powerful memory management system can be used to improve the utilization of the main memory and provide protection capabilities for the system. This is discussed in this chapter. Although memory management is an optional capability - the Z8000 CPU is an extremely sophisticated processor without memory management - the CPU has explicit features to facilitate integrating an external memory management device into a Z8000 system configuration.

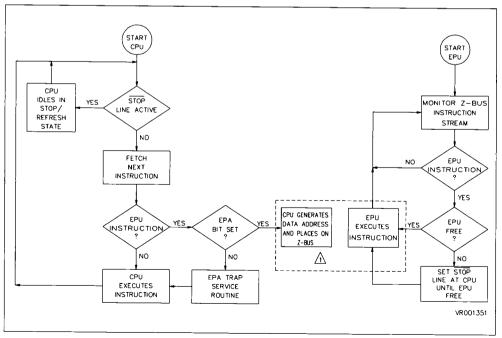

Finally, care has been taken to provide a very general mechanism for extending the basic instruction set through the use of external devices (called Extended Processing Units - EPUs). In general, an EPU is dedicated to performing complex and timeconsuming tasks so as to unburden the CPU. Typical tasks for specialized EPUs include floating-point arithmetic, data base search and maintenance operations, network interfaces, and many others. This topic is treated in this chapter.

#### Architecture

The architectural resources of the Z8000 CPU include sixteen 16-bit general-purpose registers, seven data types ranging from bits to 32-bit long words and byte strings, eight user-selectable addressing modes, and an instruction set more powerful than that of most mini-computers. The 110 distinct instruction types combine with the various data types and addressing modes to form a rich set of 414 instructions. Moreover, the set exhibits a high degree of regularity: more than 90% of the instructions can use. Any of five main addressing modes, with 8-bit byte, 16-bit word, and 32-bit long-word data types.

The CPU generates status signals indicating the nature of the bus transaction that is being attempted; these can be used to implement sophisticated systems with multiple address spaces memory areas dedicated to specific uses. The CPU also has two operating modes, system and normal, which can be used to separate operating system functions from normal application processes. I/O

operations have been separated from memory accesses, further enchancing the capability and integrity of Z8000-based systems, and a sophisticated interrupt structure facilitates the efficient operation of peripheral I/O devices. Moreover, the Extended Processing Unit (EPU) capability of the Z8000 allows the CPU to unload many time-consuming tasks onto external devices.

Special features of the Z8000 have been introduced to facilitate the implementation of multiple processor systems. In addition, the Z8001 CPU has a large, segmented addressing capability that greatly extends the applicability of microprocessors to large system applications.

**General-Purpose Register File.** The heart of the Z8000 CPU architecture is a file of sixteen 16-bit general-purpose registers. These general-purpose registers give the Z8000 its power and flexibility and add to its regular instruction structure.

General-purpose registers can be used as accumulators, memory pointers or index registers. Their major advantage is that the particular use to which they are put can vary during the course of a program as the needs of the program change. Thus, the general-purpose register file avoids the critical bottlenecks of an implied or dedicated register architecture, which must save and restore the contents of dedicated registers when more registers of a particular type are needed than are supplied by the processor.

The Z8000 CPU register file can be addressed in several ways: as 16 byte registers (occupying one half of the file) or as 16 word registers or, by using the register pairing mechanism, as eight long-word (32-bit) registers or a four quadruple-word (64-bit) registers. Because of this register flexibility, it is not necessary (for example) for a Z8000 user to dedicate a 32-bit register to hold a byte of data. Registers can be used efficiently in the Z8000.

Instruction Set. A powerful instruction set is one of the distinguishing characteristics of the Z8000. The instruction set is one measure of the flexibility and versatility of a computer. Having a given operation implemented in hardware saves memory and improves speed. In addition, completeness of the operations available on a particular data type is frequently more important than additional, esoteric instructions, which are unlikely to affect performance significantly. The Z8000 CPU provides a full complement of arithmetic, logical, branch, I/O, shift, rotate, and string instructions. In addition, special instructions have been included to facilitate multiprocessing, multiple processor configurations,

and typical high level language and operating system functions. The general philosophy of the instruction set is two-operand register-memory operations, which include as a special subset register-register operations. However, to improve code density, a few memory-memory operations are used for string manipulation. The two-address format reflects the most frequently occuring operations (such as  $A \leftarrow A + B$ ). Also, having one of the operands in a rapidly accessible general-purpose register facilitates the use of intermediate results generated during a calculation.

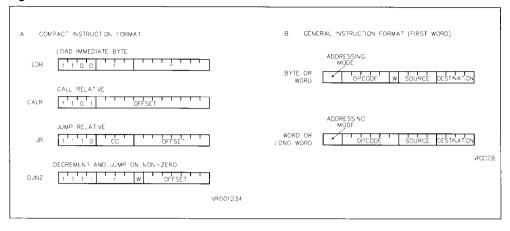

The majority of operations deal with byte, word, or long-word operands, thereby providing a high degree of regularity. Also included in the instruction set are compact, one-word instructions for the most frequently used operations, such as branching short distances in a program.

The instruction set contains some notable additions to the standard repertoire of earlier microprocessors. The Load and Exchange group of instructions has been expanded to support operating system functions and conversion of existing microprocessor programs. The usual arithmetic instructions can now deal with higher-precision operands, while hardware multiply and divide instructions have also been added. The Bit Man-

ipulation instructions can use calculated values to specify the bit position within a byte or word as well as to specify the position statically in the instruction. The Rotate and Shift instructions are considerably more flexible than those in previous microprocessors. The String instructions are useful in translating between different character codes. Multiple-processor configurations are supported by special instructions.

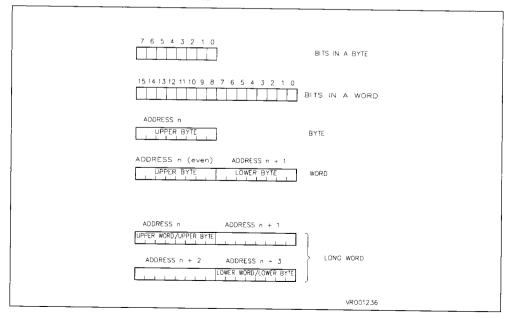

Data Types. Many data types are supported by the Z8000 architecture. A data type is supported when it has a hardware representation and instructions which directly apply to it. New data types can always be simulated in terms of basic data types. but hardware support provides faster and more convenient operations. The basic data type is the byte, which is also the basic addressable element. The architecture also supports the following data types: words (16 bits), long words (32 bits), byte strings, and word strings. In addition, bits are fully supported and addressed by number within a byte or word. BCD digits are supported and represented as two 4-bit digits in a byte. Arrays are supported by the Indexed addressing mode (in Chapter AD-DRESSING MODES), Stacks are supported by the instruction set and by an external device (the Memory Management Unit Z8010 MMU) available with the Z8001

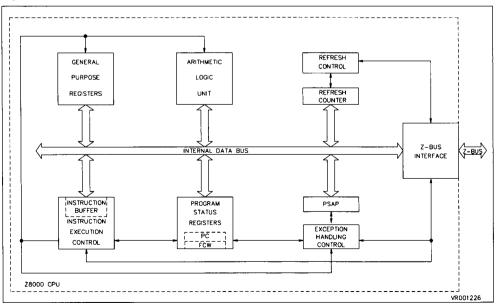

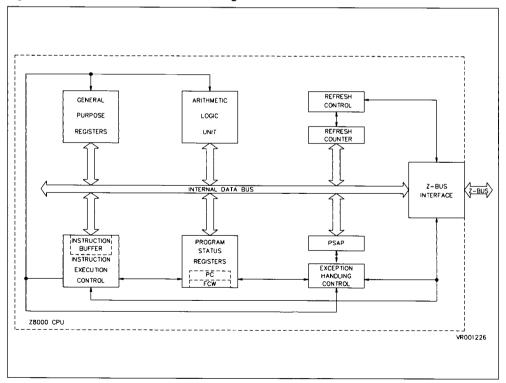

Figure 1-2. Z8000 CPU Functional Block Diagram

## Architecture (Continued)

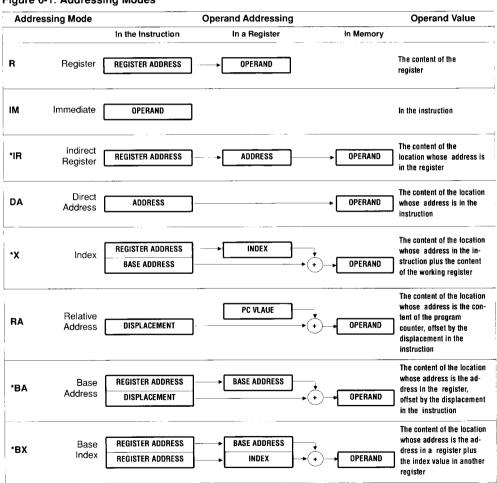

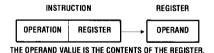

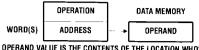

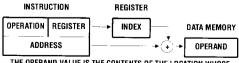

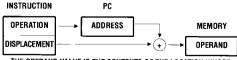

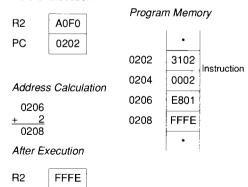

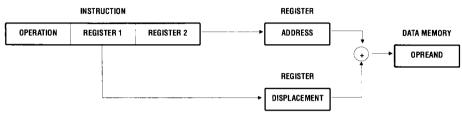

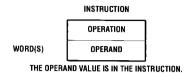

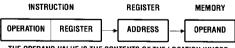

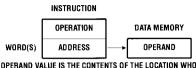

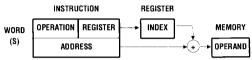

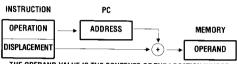

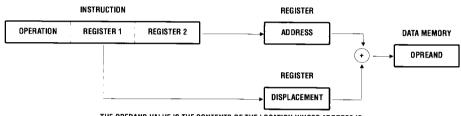

Addressing Modes. The addressing mode, which is the way an operand is specified in an instruction. determines how an address is generated. The Z8000 CPU offers eight addressing modes. Together with the large number of instructions and data types, they improve the processing power of the CPU. The addressing modes are Register, Immediate, Indirect Register, Direct Address, Index, Relative Address, Base Address, and Base Index. Several other addressing modes are implied by specific instructions, including autoincrement. The first five modes listed above are basic addressing modes that are used most frequently and apply to most instructions having more than one addressing mode. (In the Z8002, Base Address and Index modes are identical, and in the Z8001. Base Addressing capabilites can be simulated with all instructions, using Based Addressing or the Memory Management Unit and the Direct or Indexed Addressing mode.)

Multiple Memory Address Spaces. The Z8000 CPU facilitates the use of multiple address spaces. When the Z8000 CPU generates an address, it also outputs signals indicating the particular internal activity which led to the memory request : instruction fetch, operand reference, or stack reference. This information can be used in two ways: to increase the memory space available to the processor (for example, by putting programs in one space and data in another); or to protect portions of the memory and allow only certain types of accesses (for example, by allowing only instruction fetches from an area designated to contain proprietary software). The Memory Management Unit (MMU) has been designed to provide precisely these kinds of protection features by using the CPU-generated status information.

System/Normal Mode of Operation. The Z8000 CPU can run in either system mode or normal mode. In system mode, all of the instructions can be executed and all of the CPU registers can be accessed. This mode is intented for use by programs performing operating system functions. In normal mode, some instructions may not be executed (e.g., I/O operations), and the control registers of the CPU are inaccessible. In general, this mode of operation is intended for use by application programs. This separation of CPU resources promotes the integrity of the system, since programs operating in normal mode cannot access those aspects of the CPU which deal with time dependent or system-interface events.

Programs executing in normal mode which have errors can always reproduce those errors for debugging purposes simply by re-executing the program with its original data. Programs using facilities available only in system mode may have errors due to timing considerations (e.g. based upon the frequency of disk requests and disk arm-position) that are harder to debug because these errors are not easily reproduced. Thus, the preferred method of program development is to partition the task into a portion which can be performed without those resources accessible only in system mode (which will usually be the bulk of the task) and a portion requiring system mode resources. The classic example of this partitioning comes from current minicomputer and mainframe systems: the operating system runs in system mode and the individual users write their programs to run in normal mode.

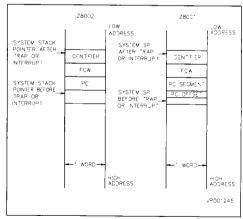

To further support the system/normal mode dichotomy, there are two copies of the stack pointer -one for a system mode stack and another for a normal mode stack. These two stacks facilitate the task switching involved when interrupts or traps occur. To insure that the normal stack is free of system information, the information saved on the occurrence of interrupts or traps is always pushed on to the system stack before the new program status is loaded.

Separate I/O Address Spaces. The Z8000 Architecture distinguishes between memory and I/O spaces and thus requires specific I/O instructions. This architectural separation allows better protection and has more potential for extension. The use of separate I/O spaces also conserves the limited Z8002 data memory space. There are in fact two separate I/O address spaces : standard I/O and special I/O. The main advantage of these two spaces is to provide for two types of peripheral support chips -standard I/O peripheral and special I/O peripherals- devices such as the Z8010 Memory Management Unit that do not respond to standard I/O commands, but do respond to special I/O commands. A second advantage of these two spaces is that they allow 8-bit peripherals to attach to the low-order eight bits (standard I/O) or to the high-order eight bits (special I/O) of the processor Address/Data bus.

The increased speed requirements of future microprocessors are likely to be achieved by tailoring memory and I/O references to their respective, characteristic reference patterns and by using simultaneous I/O and memory referencing. These future possibilities require an architectural separation today. Memory-mapped I/O is still possible, but loss of protection and lack of expandability are severe problems.

Interrupt Structure. The sophisticated interrupt structure of the Z8000 allows the processor to continue performing useful work while waiting for peripheral events to occur. The elimination of periodic polling and idling loops (typically used to determine when a device is ready to transmit data) increases the throughput of the system. The CPU supports three types of interrupts. A non-maskable interrupt represents a catastrophic event which requires immediate handling to preserve system integrity. In addition, there are two types of maskable interrupts: non-vectored interrupts and vectored interrupts. The latter provides an automatic call to separate interrupt processing routines for each peripheral, depending on the vector presented by the peripheral to the Z8000.

The Z8000 has implemented a priority system for handling interrupts. Vectored interrupts have higher priority than non-vectored interrupts. This priority scheme allows the efficient control of many peripheral devices in a Z8000 system.

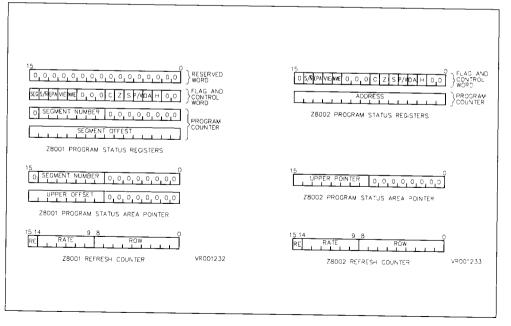

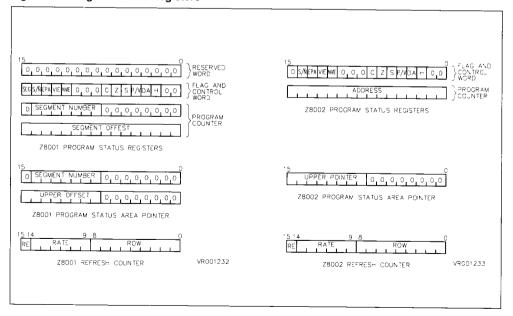

An interrupt causes information relating to the currently executing program (program status) to be saved on a special system stack with a code describing the reason for the switch. This allows recursive task switches to occur while leaving the normal stack undisturbed by system information. The program state to handle the interrupt (new program status) is loaded from a special area in memory, the program status area, designated by a pointer resident in the CPU.

The use of the stack and of a pointer to the program status area is a specific choice made to allow architectural compatibility if new interrupts or traps are added to the architecture.

**Multi-Processing.** The increase in microprocessor computing power that the Z8000 represents makes simple the design of distributed processing systems having many low-cost microprocessors running dedicated processes.

The Z8000 provides some basic mechanisms that allow the sharing of address spaces among different microprocessors. Large segmented address spaces and the support for external memory management make this possible. Also, a resource request bus is provided which, in conjunction with software, provides the exclusive use of shared critical resources. These mechanisms, and new peripherals such as the Z8038 FIO, have been designed to allow easy asynchronous communication between different CPUs.

Large Address Space for the Z8001. For many applications, a basic address space of 64K bytes is insufficient. A large address space increases the range of applications of a system by permitting large, complex programs and data sets to reside in memory rather than be partitioned and swapped into a small memory as needed. A large address space greatly simplifies program and data management. In addition, large address spaces and memories reduce the need for minimizing program size and permit the use of higher level languages. The segmented version of the Z8000 generates 23-bit addresses, for a basic address space of 8 megabytes (8M or 8.388, 608 bytes).

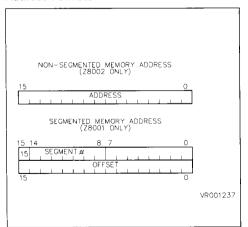

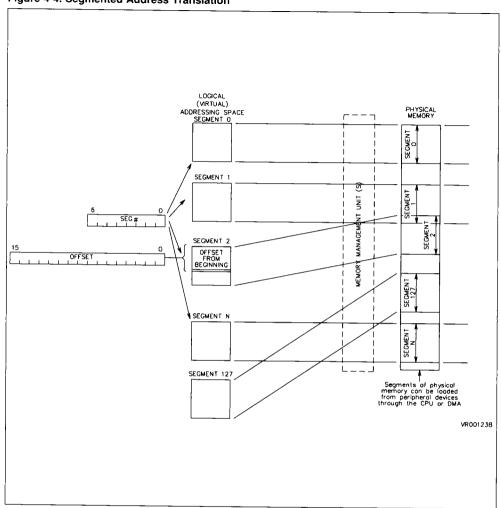

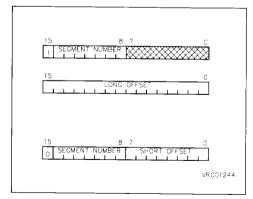

Seamented Addressing of the Z8001. The seamented version of the Z8000 CPU divides its 23-bit addresses into a 7-bit segment number and a 16-bit seament offset. The seament number serves as a logical name of a segment; it is not altered by the effective address calculation (by indexing, for example). This corresponds to the way memory is typically used by a program -one portion of the memory is set aside to hold instructions, another for data. In a segmented address space, the instructions could reside in one segment (or several different modules in different segments), and each data set could reside in a separate segment. One advantage of segmentation is that it speeds up address calculation and relocation. Thus, segmentation allows the use of slower memories than linear addressing schemes allow. In addition, segments provide a convenient way of partitioning memory so that each partition is given particular access attributes (for example, read-only). The Z8000 approach to segmentation (simultaneous access to a large number of segments) is necessary if all the advantages of segmentation are to be realized. A system capable of directly accessing only, say, four segments would lack the needed flexibility and would be constrained by address space limitations.

Memory Management. Memory management consists primarily of dynamic relocation, protection, and sharing of memory. It offers the following advantages: providing a logical structure to the memory space that is independent of the actual physical location of data, protecting the user from inadvertent mistakes such as attempting to execute data, preventing unauthorized access to memory resources or data, and protecting the operating system from disruption by the users.

## Architecture (Continued)

The addresses manipulated by the programmer, used by instructions, and output by the segmented Z8000 CPU are called logical addresses. The external memory management system takes the logical addresses and transforms them into physical addresses required for accessing the memory. This address transformation process is called relocation, which makes user software independent of the physical memory. Thus, the user is freed from specifying where information is actually located in the physical memory.

The segmented Z8000 CPU supports memory management both with segmented addressing and with program-status information. A segmented addressing space allows individual segments to be treated differently.

Program status information generated by the CPU permits an external memory management device to monitor the intended use of each memory access. Thus, illegal types of access can be suppressed and memory segments protected from unintended or unwanted modes of use. For example, system tables could be protected from direct user access. This added protection capability becomes more important as microprocessors are applied to large, complex tasks.

## Benefits of the Architecture

The features of the Z8000 Architecture combine to provide several significant benefits: improvements in code density, compiler efficiency, operating system support, and support for high level data structures.

Code Density. Code density affects both processor speed and memory utilization. Code compaction saves memory space -an especially important factor in smaller systems- and improves processor speed by reducing the number of instruction words that must be fetched and decoded. The Z8000 offers several advantages with respect to code density. The most frequently used instructions are encoded in single-word formats. Fewer instructions are needed to accomplish a given task and a consistent and regular architecture further reduces the number of instructions required.

Code density is achieved in part by the use of special "short" formats for certain instructions which are shown by statistical analysis to be most frequently used by assemblers. A "short offset" mechanism has also been provided to allow a 2-word segmented address to be reduced to a

single word; this format may be used by assemblers and compilers.

The largest reduction in program size and increase in speed results from the consistent and regular structure of the architecture and from the more powerful instruction set -factors that substantially reduce the number of instructions required for a task. The architecture is more regular relative to preceding microprocessors because its registers, address modes, and data types can be used in a more orderly fashion. Any general-purpose register except R0 can be specified as an accumulator, index register, or base register. With a few exceptions, all basic addressing modes can be used with all instructions, as can the various data types.

General-purpose registers do not have to be changed as often as registers dedicated to a specific purpose. This reduces program size, since frequent load and store operations are not required.

Compiler Efficiency. For microprocessor users. the transition from assembly language to high-level languages allows greater freedom from architectural dependency and improves ease of programming. However, rather than adapt the architecture to a particular high-level language, the Z8000 was designed as a general-purpose microprocessor. (Tailoring a processor for efficiency in one language often leads to inefficiency in unrelated languages). For the Z8000, language support has been provided through the inclusion of features designed to minimize typical compilation and code-generation problems. Among these features is the regularity of the Z8000 addressing modes and data types. Access to parameters and local variables on the procedure stack is supported by the "Index With Short Offset" addressing mode, as well as the Base Address and Base Index addressing modes. In addition, address arithmetic is aided by the Increment and Decrement instructions.

Testing of data, logical evaluation, initialization, and comparison of data are made possible by the instructions Test, Test Condition Codes, Load Immediate Into Memory, and Compare Immediate With Memory. Since compilers and assemblers frequently manipulate character strings, the instructions Translate, Translate And Test, Block Compare, and Compare String all result in dramatic speed improvements over software simulations of these important tasks. In addition, any register except R0 can be used as a stack pointer by the Push and Pop instructions.

**Operating System Support.** Interrupt and task-switching features are included to improve operating system implementations. The memory-management and compiler-support features are also quite important.

The interrupt structure has three levels: non-mask-able, non-vectored, and vectored. When an interrupt occurs, the program status is saved on the stack with an indication of the reason for this state-switching before a new program status is loaded from a special area of memory. The program status consists of the flag register, the control bits, and the program counter. The reason for the occurence is encoded in a vector that is read from the system bus and saved on the stack. In the case of a vectored interrupt, the vector also determines a jump table address that points to the interrupt processing routine.

The inclusion of system and normal modes improves operating system organization. In the system mode, all operations are allowed; in the normal mode, certain system instructions are prohibited. The System Call instruction allows a controlled switch of mode, and the implementation of traps enforces these restrictions.

Traps result in the same type of program status-saving as interrupts: in both cases, the information saved is pushed on to a system stack that keeps the normal stack undisturbed. The Load Multiple instruction allows the contents of registers to be saved efficiently in memory or on the stack. Running programs can cause program status changes under direct software control with the Load Program Status instruction.

Finally, exclusion and serialization can be achieved with the "atomic" Test And Set instruction that synchronizes asynchronous cooperating processes.

Support for Many Types of Data Structures. A data structure is a logical organization of primitive elements (byte, word, etc.) whose format and access conventions are well-defined. Common data structures include arrays, lists, stacks, and strings. Since data structures are high-level constructs frequently used in programming, processor performance is significantly enchanced if the CPU provides mechanisms for efficiently manipulating them. The Z8000 offers such mechanisms.

In many applications, one of the most frequently encountered data structures is the array. Arrays are

supported in the Z8000 by the index and the Base Index addressing mode and by segmented addressing. The Base Index addressing mode allows the use of pointers into an array (i.e., offsets from the array's starting address). Segmented addressing allows an array to be assigned to one segment, which can be referenced simply by segment number.

Lists occur more frequently than arrays in business applications and in general data processing. Lists are supported by Indirect Register and Base Address addressing modes. The Base Index addressing mode is also useful for more complex lists.

Stacks are used in all applications for nesting of routines, block structured languages, and interrupt handling. Stacks are supported by the Push and Pop instructions, and multiple stacks may be implemented based on the general-purpose registers of the Z8000. In addition, two hardware stack pointers are used to assign separate stacks to system and normal operating modes, thereby further supporting the separation of system and normal operating environments discussed earlier.

Byte and word strings are supported by the Translate and Translate And Test instructions. Decimal strings use the Decimal Adjust instruction to do decimal arithmetic on strings of BCD data, packed two characters per byte. The Rotate Digit instructions also manipulate 4-bit data.

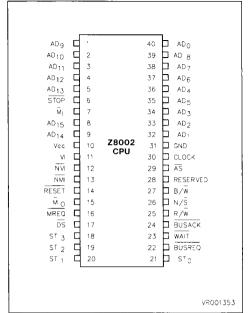

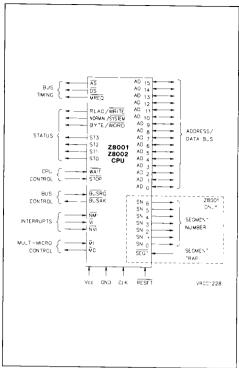

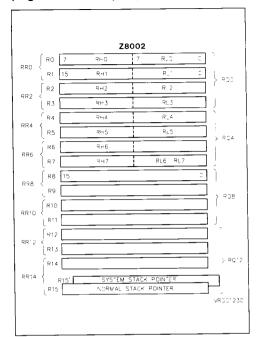

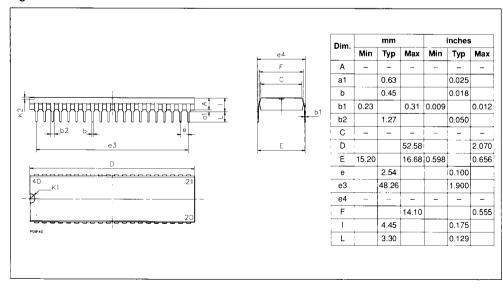

Two CPU Versions: Z8001 and Z8002. The Z8000 CPU is offered in two versions: the Z8001 48-pin segmented CPU and the Z8002 40-pin non-segmented CPU. The main difference between the two is addressing range. The Z8001 can directly address 8M bytes of memory; the Z8002 directly addresses 64K bytes. The Z8001 has a non-segmented mode of operation which permits it to execute programs written for the Z8002.

Not all applications require the large address space of the Z8001; for these applications the Z8002 is recommended. Moreover, many multiple-processor systems can be implemented with one Z8001 and severals Z8002s, instead of exclusively using Z8001s. Since the same assembler generates code for both CPUs, users can buy only the power they require without having to worry about software incompatibility between processors.

## **Extended Instruction Facility**

The Z8000 architecture has a mechanism for extending the basic instruction set through the use of external devices. Special opcodes have been set aside to implement this features. When the CPU encouters an instruction with these opcodes in its instruction stream, it will perform any indicated address calculation and data transfer; otherwise, it will treat the "extended instruction" as being executed by the external device. Fields have been set aside in these extended instructions which can be interpreted by external devices (Extended Processing Units -EPUs) as opcodes. Thus, by using appropriate EPUs, the instruction set of the Z8000 can be extended to include specialized instructions.

In general, an APU is dedicated to performing complex and time-consuming tasks in order to unburden the CPU. Typical tasks suitable for specialized EPUs include floating-point arithmetic, data base search and maintenance operations, network interfaces, graphics support operations -a complete list would include most areas of computing.

## Summary

The architectural sophistication of the Z8000 microprocessor is on a level comparable with that of the minicomputer. Features such as large address spaces, multiple memory spaces, segmented addresses, and support for multiple processors are beyond the capabilities of the traditional microprocessor. The benefits of this architecture code density, compiler support, and operating system support- greatly enhance the power and versatility of the CPU. The CPU features that support an external memory management system also enhance the CPU's applicability to large system environments.

## Register organization

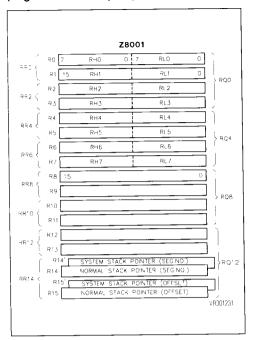

The Z800 CPU is a register-oriented machine that offers sixteen 16-bit general-purpose registers and a set of special system registers. All general-purpose registers can be used as accumulators and all but one as index registers or memory pointers.

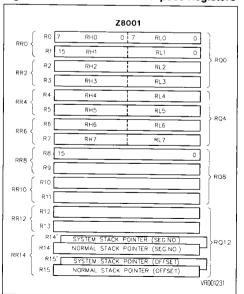

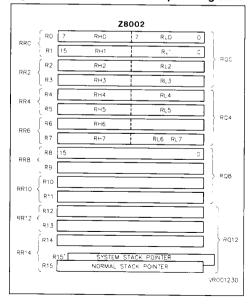

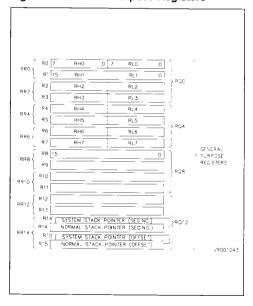

Register flexibility is created by grouping and overlapping multiple registers (Figure 1-3a and 1-3b). For byte operations, the first eight 16-bit registers (R0...R7) are treated as sixteen 8-bit registers (RL0, RH0,..., RL7, RH7). The sixteen 16-bit registers are grouped in pairs (RR0 ... RR14) to form 32-bit long-word registers. Similarly, the register set is grouped in quadruples (RQ0 ... RQ12) to form 64-bit registers.

Figure 1-3a. Z8001 General-Purpose Registers

Figure 1-3b. Z8002 General-Purpose Registers

# **Instruction Set Summary**

The Z8000 provides the following types of instructions:

- Load and Exchange.

- Arithmetic.

- Logical.

- Program Control.

- Bit Manipulation.

- Rotate and Shift.

- Block Transfer and String Manipulation.

- Input/Output.

- CPU Control.

# Load and Exchange

|                  |          |                           |                           | (             | Clock C  | ycles <sup>(1)</sup> |          |              |                                                                               |

|------------------|----------|---------------------------|---------------------------|---------------|----------|----------------------|----------|--------------|-------------------------------------------------------------------------------|

| Mnemonics        | Operands | Addr.<br>Modes            | W                         | ord, By       | rte      | Lor                  | ng Woi   | rd           | Operation                                                                     |

|                  |          |                           | NS                        | SS            | SL       | NS                   | SS       | SL           |                                                                               |

| CLR<br>CLRB      | dst      | R<br>IR<br>DA<br>X        | 7<br>8<br>11<br>12        | 12<br>12      | 14<br>15 |                      |          |              | Clear<br>dst ← 0                                                              |

| EX<br>EXB        | R,src    | R<br>IR<br>DA<br>X        | 6<br>12<br>15<br>16       | 16<br>16      | 18<br>19 |                      |          |              | Exchange<br>R ↔ src                                                           |

| LD<br>LDB<br>LDL | R,src    | R<br>IM<br>IM<br>IR<br>DA | 3<br>7<br>5<br>7<br>9     | (byte         | only)    | 5<br>11<br>11<br>12  | - 13     | -<br>-<br>15 | Load into Register<br>R ← src                                                 |

|                  |          | X<br>BA<br>BX             | 10<br>14<br>14            | 10            | 13       | 13<br>17<br>17       | 13       | 16           |                                                                               |

| LD<br>LDB<br>LDL | dst,R    | IR<br>DA<br>X<br>BA<br>BX | 8<br>11<br>12<br>14<br>14 | 12<br>12<br>- | 14<br>15 | 11<br>14<br>15<br>17 | 15<br>15 | 17<br>18     |                                                                               |

| LD<br>LDB        | dst,IM   | IR<br>DA<br>X             | 11<br>14<br>15            | 15<br>15      | 17<br>18 |                      |          |              | Load Immediate into Memory<br>dst ← IM                                        |

| LDA              | R,src    | DA<br>X<br>BA<br>BX       | 12<br>13<br>15<br>15      | 13<br>13<br>- | 15<br>16 |                      |          |              | <b>Load Address</b> R ← source address                                        |

| LDAR             | R,src    | RA                        | 15                        | -             | -        |                      |          |              | Load Address Relative<br>R ← source address                                   |

| LDK              | R,src    | IM                        | 5                         | -             | -        |                      |          |              | <b>Load Constant</b> R ← n (n = 0 15)                                         |

| LDM              | R,src,n  | IR<br>DA<br>X             | 11<br>14<br>15            | 15<br>15      | 17<br>18 | <br>                 | 3n       |              | Load Multipe R ← src (n consecutive words) (n = 1 16)                         |

| LDM              | dst,R,n  | IR<br>DA<br>X             | 11<br>14<br>15            | 15<br>15      |          | <br>                 | 3n       |              | Load Multiple (Store Multiple)<br>dst ← R (n consecutive words)<br>(n = 1 16) |

# Load and Exchange (Continued)

|                     | Operands | Operands Addr Modes -    |                           | C             | Clock C            | ycles <sup>(1</sup>  |          |          |                                                                      |

|---------------------|----------|--------------------------|---------------------------|---------------|--------------------|----------------------|----------|----------|----------------------------------------------------------------------|

| Mnemonics           |          |                          | Word, Byte                |               |                    | Long Word            |          |          | Operation                                                            |

|                     |          |                          | NS                        | SS            | SL                 | NS                   | SS       | SL       | -                                                                    |

| LDR<br>LDRB<br>LDRL | R,src    | RA                       | 14                        | -             | -                  | 17                   | -        | -        | Load Relative<br>R ← src<br>(range - 32768 + 32767)                  |

| LDR<br>LDRB<br>LDRL | dst,R    | RA                       | 14                        | -             | -                  | 17                   | -        | -        | Load Relative (Store Relative)<br>dst ← R<br>(range - 32768 + 32767) |

| POP<br>POPL         | dst,IR   | R<br>IR<br>DA<br>X       | 8<br>12<br>16<br>16       | -<br>16<br>16 | 18<br>19           | 12<br>19<br>23<br>23 | 23<br>23 | 25<br>26 | Pop<br>dst ← IR<br>Autoincrement contents of R                       |

| PUSH<br>PUSHL       | IR,src   | R<br>IM<br>IR<br>DA<br>X | 9<br>12<br>13<br>14<br>14 | 14            | -<br>-<br>16<br>17 | 12<br>20<br>21<br>21 | 21<br>21 | 23<br>24 | Push<br>IR ← src<br>Autodecrement contents of R                      |

# Arithmetic

| ADC<br>ADCB            | R,src  | R                        | 5                               | -                 |                   |                                 |                    | _                  | Add with Carry R ← R + src + carry                                                                                                                                                                                                                                            |

|------------------------|--------|--------------------------|---------------------------------|-------------------|-------------------|---------------------------------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD<br>ADDB<br>ADDL    | R,src  | R<br>IM<br>IR<br>DA<br>X | 4<br>7<br>7<br>9<br>10          | 10                | 12<br>13          | 8<br>14<br>14<br>15<br>16       | -<br>-<br>16<br>16 | -<br>-<br>18<br>19 | Add<br>R ← R + src                                                                                                                                                                                                                                                            |

| CP<br>CPB<br>CPL       | R,src  | R<br>IM<br>IR<br>DA<br>X | 4<br>7<br>7<br>9<br>10          | 10                | 12<br>13          | 8<br>14<br>14<br>15<br>16       | 16<br>16           | -<br>-<br>18<br>19 | Compare with Register<br>R - src                                                                                                                                                                                                                                              |

| CP<br>CPB              | dst,IM | IR<br>DA<br>X            | 11<br>14<br>15                  | 15<br>15          | 17<br>18          |                                 | _                  | _                  | Compare with Immediate dst - IM                                                                                                                                                                                                                                               |

| DAB                    | dst    | R                        | 5                               | -                 | -                 |                                 | _                  | _                  | Decimal Adjust                                                                                                                                                                                                                                                                |

| DEC<br>DECB            | dst,n  | R<br>IR<br>DA<br>X       | 4<br>11<br>13<br>14             | 14<br>14          | 16<br>17          |                                 | -                  |                    | Decrement by n<br>$dst \leftarrow dst - n$<br>$(n = 1 \dots 16)$                                                                                                                                                                                                              |

| DIV<br>DIVL            | R,src  | R<br>IM<br>IR<br>DA<br>X | 107<br>107<br>107<br>108<br>109 | 107<br>109<br>109 | 107<br>111<br>112 | 744<br>744<br>744<br>745<br>746 | 744<br>746<br>746  | 744<br>748<br>749  | $\begin{array}{l} \textbf{Divide} \ (\text{signed}) \\ \text{Word} : R_{n+1} \leftarrow R_{n,n+1} + \text{src} \\ R_n \leftarrow \text{remainder} \\ \text{Long Word} : R_{n+2,n+3} \leftarrow R_{nn+3} \\ + \text{src} \\ R_{n,n+1} \leftarrow \text{remainder} \end{array}$ |

| EXTS<br>EXTSB<br>EXTSL | dst    | R                        | 11                              | -                 | -                 | 11                              | -                  | •                  | Extend Sign Extend sign of low order half of dst through high order half of dst                                                                                                                                                                                               |

# Arithmetic (Continued)

|                     |          | . Addr. —                |                            | C                  | Clock C            | ycles <sup>(1</sup>                  | )                  |                    |                                                                                                                                                              |

|---------------------|----------|--------------------------|----------------------------|--------------------|--------------------|--------------------------------------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonics           | Operands | Modes                    | Word, Byte                 |                    |                    | Lo                                   | ong Wo             | rd                 | Operation                                                                                                                                                    |

|                     |          | -                        | NS                         | SS                 | SL                 | NS                                   | SS                 | SL                 |                                                                                                                                                              |

| INC<br>INCB         | dst,n    | R<br>IR<br>DA<br>X       | 4<br>11<br>13<br>14        | 14<br>14           | -<br>16<br>17      |                                      |                    |                    | Increment by n<br>dst ← dst + n<br>(n = 1 16)                                                                                                                |

| MULT<br>MULTL       | R,src    | R<br>IM<br>IR<br>DA<br>X | 70<br>70<br>70<br>71<br>72 | -<br>-<br>72<br>72 | -<br>-<br>74<br>75 | 282*<br>282*<br>282*<br>283*<br>284* | 284*<br>284*       | 286*<br>287*       | Multiply (signed) Word: $R_{n,n+1} \leftarrow R_{n+1} + src$ Long Word: $R_{n,m+3} \leftarrow R_{n+2,n+3}$ *Plus seven cycles for each 1 in the multiplicand |

| NEG<br>NEGB         | dst      | R<br>IR<br>DA<br>X       | 7<br>12<br>15<br>16        | 16<br>16           | -<br>18<br>19      |                                      |                    |                    | Negate<br>dst ← 0 - dst                                                                                                                                      |

| SBC<br>SBCB         | R,src    | R                        | 5                          | -                  | -                  |                                      |                    |                    | Subtract with Carry R ← R - src - carry                                                                                                                      |

| SUB<br>SUBB<br>SUBL | R,src    | R<br>IM<br>IR<br>DA<br>X | 4<br>7<br>7<br>9<br>10     | 10<br>10           | 12<br>13           | 8<br>14<br>14<br>15<br>16            | -<br>-<br>16<br>16 | -<br>-<br>18<br>19 | Subtract<br>R ← R - src                                                                                                                                      |

## Logical

| Logical                |        |                          |                        |                    |                    |                      |          |          |                                              |

|------------------------|--------|--------------------------|------------------------|--------------------|--------------------|----------------------|----------|----------|----------------------------------------------|

| AND<br>ANDB            | R,src  | R<br>IM<br>IR<br>DA<br>X | 4<br>7<br>7<br>9<br>10 | 10<br>10           | 12<br>13           |                      |          |          | AND<br>R ← R AND src                         |

| COMB                   | dst    | R<br>IR<br>DA<br>X       | 7<br>12<br>15<br>16    | 16<br>16           | 18<br>19           |                      |          |          | Complement<br>dst ← NOT dst                  |

| OR<br>ORB              | R,src  | R<br>IM<br>IR<br>DA<br>X | 4<br>7<br>7<br>9<br>10 | -<br>-<br>10<br>10 | -<br>-<br>12<br>13 |                      |          |          | <b>OR</b><br>R ← R OR src                    |

| TCC<br>TCCB            | cc,dst | R                        |                        |                    |                    |                      |          | 5        | Test Condition Code<br>Set LSB if cc is true |

| TEST<br>TESTB<br>TESTL | dst    | R<br>IR<br>DA<br>X       | 7<br>8<br>11<br>12     | 12<br>12           | 14<br>15           | 13<br>13<br>16<br>17 | 17<br>17 | 19<br>20 | <b>Test</b><br>dst OR 0                      |

| XOR<br>XORB            | R,src  | R<br>IM<br>IR<br>DA<br>X | 4<br>7<br>7<br>9<br>10 | -<br>-<br>10<br>10 | -<br>-<br>12<br>13 |                      |          |          | Exclusive OR<br>R ← R XOR src                |

# **Program Control**

| ••            | 0        | Addr                |                   | C           | Clock C             | ycles <sup>(</sup> | 1)                  |    | <del>-</del>                                                                                                 |

|---------------|----------|---------------------|-------------------|-------------|---------------------|--------------------|---------------------|----|--------------------------------------------------------------------------------------------------------------|

| Mnemonics     | Operands | Addr.<br>Modes      | W                 | ord, By     | te                  | L                  | ong Wo              | rd | Operation                                                                                                    |

|               |          | -                   | NS                | SS          | SL                  | NS                 | SS                  | SL | -                                                                                                            |

| CALL          | dst      | IR<br>DA<br>X       | 10<br>12<br>13    | 18<br>18    | 15<br>20<br>21      |                    | _                   |    | Call Subroutine Autodecrement SP @ SP ← PC PC ← dst                                                          |

| CALR          | dst      | RA                  | 10                | -           | 15                  |                    |                     |    | Call Relative Autodecrement SP @ SP ← PC PC ← PC + dst (range -4094 to +4096)                                |

| DJNZ<br>DBJNZ | R,dst    | RA                  | 11                | -           | -                   |                    |                     |    | Decrement and Jump if Non-Zero $R \leftarrow R - 1$ If $R \neq 0 : PC \leftarrow PC + dst$ (range -254 to 0) |

| IRET (2)      | -        |                     | 13                | -           | 16                  |                    |                     |    | Interrupt Return PS ← @ SP Autoincrement SP                                                                  |

| JP            | cc,dst   | IR<br>IR<br>DA<br>X | 10<br>7<br>7<br>8 | -<br>8<br>8 | 15<br>7<br>10<br>11 | (r                 | (taken)<br>not take |    | Jump Conditional<br>If cc is true : PC ← dst                                                                 |

| JR            | cc,dst   | RA                  | 6                 | -           | -                   |                    |                     |    | Jump Condition Relative If cc is true : PC ← PC + dst (range -256 to +254)                                   |

| RET           | СС       | -                   | 10<br>7           | -           | 13<br>7             | (r                 | (taken)<br>not take |    | Return Conditional If cc is true : PC ← @ SP Autoincrement SP                                                |

| SC            | src      | IM                  | 33                | -           | 39                  |                    |                     |    | System Call Autodecrement SP @ SP ← old PS Push instruction PS ← System Call PS                              |

# **Bit Manipulation**

| BIT<br>BITB | dst,B | R<br>IR<br>DA<br>X | 4<br>8<br>10<br>11  | 11<br>11 | -<br>13<br>14 |                                                                         |

|-------------|-------|--------------------|---------------------|----------|---------------|-------------------------------------------------------------------------|

| BIT<br>BITB | dst,R | R                  | 10                  | -        | -             | <b>Test Bit Dynamic</b> Z flag ← NOT dst bit specified by contents of R |

| RES<br>RESB | dst,b | R<br>IR<br>DA<br>X | 4<br>11<br>13<br>14 | 14<br>14 | 16<br>17      | Reset Bit Static Reset dst bit specified by b                           |

| RES<br>RESB | dst,R | R                  | 10                  | -        | -             | Reset Bit Dynamic Reset dst bit specified by contents R                 |

# Bit Manipulation (Continued)

| Mnemonics     | Operands | perands Addr<br>Modes - |                     | C        | Clock C  | ycles (   |    |    |                                                              |

|---------------|----------|-------------------------|---------------------|----------|----------|-----------|----|----|--------------------------------------------------------------|

|               |          |                         | Word, Byte          |          |          | Long Word |    |    | Operation                                                    |

|               |          |                         | NS                  | SS       | SL       | NS        | SS | SL | _                                                            |

| SET<br>SETB   | dst,b    | R<br>IR<br>DA<br>X      | 4<br>11<br>13<br>14 | 14<br>14 | 16<br>17 |           |    |    | Set Bit Dynamic<br>Set dst bit specified by b                |

| SET<br>SETB   | dst,R    | R                       | 10                  | -        | -        |           |    |    | Set Bit Dynamic<br>Set dst bit specified by contents of<br>R |

| TSET<br>TSETB | dst      | R<br>IR<br>DA<br>X      | 7<br>11<br>14<br>15 | 15<br>15 | 17<br>18 |           |    |    | Test and Set<br>S flag ← MSB of dst<br>dst ← all 1s          |

# **Rotate and Shift**

| RL<br>RLB           | dst,n | R<br>R | 6 for n = 1<br>7 for n = 2 |           | Rotate Left<br>by n bits (n = 1, 2)                                     |

|---------------------|-------|--------|----------------------------|-----------|-------------------------------------------------------------------------|

| RLC<br>RLCB         | dst,n | R<br>R | 6 for n = 1<br>7 for n = 2 |           | Rotate Left through Carry by n bits $(n = 1, 2)$                        |

| RLDB                | R,src | R      | 9                          | ·         | Rotate Digit Left                                                       |

| RR<br>RRB           | dst,n | R<br>R | 6 for n = 1<br>7 for n = 2 |           | Rotate Right<br>by n bits (n = 1,2)                                     |

| RRC<br>RRCB         | dst,n | R<br>R | 6 for n = 1<br>7 for n = 2 |           | Rotate Right through Carry by n bits (n = 1,2)                          |

| RRDB                | R,src | R      | 9                          |           | Rotate Digit Right                                                      |

| SDA<br>SDAB<br>SDAL | dst,R | R      | (15 + 3n)                  | (15 + 3n) | Shift Dynamic Arithmetic<br>Shift dst left or right<br>by contents of R |

| SDL<br>SDLB<br>SDLL | dst,R | R      | (15 + 3n)                  | (15 + 3n) | Shift Dynamic Logical<br>Shift dst left or right<br>by contents of R    |

| SLA<br>SLAB<br>SLAL | dst,n | R      | (13 + 3n)                  | (13 + 3n) | Shift Left Arithmetic<br>by n bits                                      |

| SLL<br>SLLB<br>SLLL | dst,n | R      | (13 + 3n)                  | (13 + 3n) | Shift Left Logical<br>by n bits                                         |

| SRA<br>SRAB<br>SRAL | dst,n | R      | (13 + 3n)                  | (13 + 3n) | Shift Right Arithmetic by n bits                                        |

| SRL<br>SRLB<br>SRLL | dst,n | R      | (13 + 3n)                  | (13 + 3n) | Shift Right Logical<br>by n bits                                        |

# **Block Transfer and String Manipulation**

|                 |                                        | Addr. |    |          | Clock | Cycles |         |     | _                                                                                                                                             |

|-----------------|----------------------------------------|-------|----|----------|-------|--------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonics       | Operands                               | Modes |    | ord, By  |       | L      | ong Wo  | ord | Operation                                                                                                                                     |

|                 |                                        |       | NS | SS       | SL    | NS     | SS      | SL  |                                                                                                                                               |

| CPD<br>CPDB     | R <sub>X</sub> ,src,R <sub>Y</sub> ,cc | IR    | 20 | -        |       |        |         |     | Compare and Decrement $R_X$ - src Autodecrement src address $R_Y \leftarrow R_Y$ - 1                                                          |

| CPDR<br>CPDRB   | R <sub>X</sub> ,src,R <sub>Y</sub> ,cc | IR    | (  | 11 + 9n  | )     |        | ~ 7 - 1 |     | Compare, Decrement and Repeat $R_X$ - $src$ Autodecrement $src$ address $R_Y \leftarrow R_Y$ - 1 Repeat until cc is true or $R_Y = 0$         |

| CPI<br>CPIB     | R <sub>X</sub> ,src,R <sub>Y</sub> ,cc | IR    | 20 | -        |       |        |         |     | Compare and Increment $R_X$ - src Autoincrement src address $R_Y \leftarrow R_Y$ - 1                                                          |

| CPIR<br>CPIRB   | R <sub>x</sub> ,src,R <sub>Y</sub> ,cc | IR    | (  | 11 + 9n  | )     |        |         |     | Compare, Increment and Repeat $R_X$ - $src$<br>Autoincrement $src$ address $R_Y \leftarrow R_Y$ - 1<br>Repeat until $cc$ is true or $R_Y$ = 0 |

| CPSD<br>CPSDB   | dst,src,R,cc                           | IR    | 25 | -        |       |        |         | -   | Compare String and Decrement dst - src Autodecrement dst and src addresses R ← R - 1                                                          |

| CPSDR<br>CPSDRB | dst,src,R,cc                           | IR    | († | 11 + 14r | ה)    |        |         |     | Compare String, Decr. and Repeat dst - src Autodecrement dst and src addresses $R \leftarrow R \cdot 1$ Repeat until cc is true or $R = 0$    |

| CPSI<br>CPSIB   | dst,src,R,cc                           | IR    | 25 | -        | ,     |        |         |     | Compare String and Increment dst - src Autoincrement dst and src addresses R ← R - 1                                                          |

| CPSIR<br>CPSIRB | dst,src,R,cc                           | IR    |    |          | (11   | + 14n) |         |     | Compare String, Incr. and Repea<br>dst - src<br>Autoincrement dst and src<br>addresses<br>R ← R - 1<br>Repeat until cc is true or R = 0       |

| LDD<br>LDDB     | dst,src,R                              | IR    | 20 | -        |       |        |         |     | Load and Decrement dst ← src Autodecrement dst and src addresses R ← R - 1                                                                    |

| LDDR<br>LDDRB   | dst,rsc,R                              | IR    | (  | 11 + 9n  | )     |        |         |     | Load, Decrement and Repeat dst ← src Autodecrement dst and src addresses R ← R - 1 Repeat until R = 0                                         |

# **Block Transfer and String Manipulation** (Continued)

| Mnemonics     |             | Addr. — |    | C         | Clock ( | ycles ( | 1)     |    | Operation                                                                                                                                       |

|---------------|-------------|---------|----|-----------|---------|---------|--------|----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonics     | Operands    | Modes   | W  | ord, By   | te      | L       | ong Wo | rd |                                                                                                                                                 |

|               |             |         | NS | SS        | SL      | NS      | SS     | SL |                                                                                                                                                 |

| LDI<br>LDIB   | dst,src,R   | IR      | 20 | -         | -       |         |        |    | Load and Increment dst ← src Autoincrement dst and src addresses R ← R - 1                                                                      |

| LDIR<br>LDIRB | dst,src,R   | IR      | (  | (11 + 9n) | )       |         | -      |    | Load, Increment and Repeat<br>dst ← src<br>Autoincrement dst and src<br>addresses<br>R ← R - 1<br>Repeat until R = 0                            |

| TRDB          | dst,src,R   | IR      | 25 | -         | -       | -       |        |    | Translate and Decrement dst ← src (dst) Autodecrement dst address R ← R - 1                                                                     |

| TRDRB         | dst,src,R   | IR      | (, | 11 + 14r  | 1)      |         |        |    | Translate, Decrement and Repea<br>dst ← src (dst)<br>Autodecrement dst address<br>R ← R - 1<br>Repeat until R = 0                               |

| TRIB          | dst,src,R   | IR      | 25 | -         | -       |         |        |    | Translate and Increment dst ← src (dst) Autoincrement dst address R ← R - 1                                                                     |

| TRIRB         | dst,src,R   | IR      | (  | 11 + 14r  | 1)      |         |        |    | Translate, Increment and Repeat dst $\leftarrow$ src (dst) Autoincrement dst address R $\leftarrow$ R - 1 Repeat until R = 0                    |

| TRTDB         | src1,src2,R | IR      | 25 | -         | -       |         | _      |    | Translate and Test, Decrement RH1 $\leftarrow$ src2 (src1) Autodecrement src1 address R $\leftarrow$ R -1                                       |

| TRTDRB        | src1,src2,R | IR      | (' | 11 + 14r  | 1)      |         |        |    | Translate and Test, Decr. and Repeat RH1 $\leftarrow$ src2 (src1) Autodecrement src1 address R $\leftarrow$ R -1 Repeat until R = 0 or RH1 = 0  |

| TRTIB         | src1,src2,R | IR      | 25 | -         | -       |         |        |    | Translate and Test, Increment RH1 $\leftarrow$ src2 (src1) Autoincrement src1 address R $\leftarrow$ R - 1                                      |

| TRTIRB        | src1,src2,R | IR      | (  | 11 + 14r  | 1)      |         |        |    | Translate and Test, Incr. and Repeat RH1 $\leftarrow$ src2 (src1) Autoincrement src1 address R $\leftarrow$ R - 1 Repeat until R = 0 or RH1 = 0 |

# Input/Output

|                                             |           |               |          | (       | Clock C | ycles <sup>(</sup> | 1)     |    |                                                                                                                     |

|---------------------------------------------|-----------|---------------|----------|---------|---------|--------------------|--------|----|---------------------------------------------------------------------------------------------------------------------|

| Mnemonics                                   | Operands  | Addr<br>Modes | W        | ord, By | te      | Le                 | ong Wo | rd | Operation                                                                                                           |

|                                             |           |               | NS       | SS      | SL      | NS                 | SS     | SL | _                                                                                                                   |

| IN <sup>(2)</sup><br>INB <sup>(2)</sup>     | R,src     | IR<br>DA      | 10<br>12 | -       | -       |                    |        |    | <b>Input</b><br>R ← src                                                                                             |

| IND <sup>(2)</sup><br>INDB <sup>(2)</sup>   | dst,src,R | IR            | 21       | -       | -       |                    |        |    | Input and Decrement dst ← src Autodecrement dst address R ← R - 1                                                   |

| INDR <sup>(2)</sup><br>INDRB <sup>(2)</sup> | dst,src,R | IR            | (1       | 1 + 10r | ۱)      |                    |        |    | Input, Decrement and Repeat dst $\leftarrow$ src Autodecrement dst address R $\leftarrow$ R - 1 Repeat until R = 0  |

| INI <sup>(2)</sup><br>INIB <sup>(2)</sup>   | dst,src,R | IR            | 21       | -       | -       |                    |        |    | Input and Increment dst $\leftarrow$ src Autoincrement dst address R $\leftarrow$ R - 1                             |

| INIR <sup>(2)</sup><br>INIRB <sup>(2)</sup> | dst,src,R | IR            | (1       | 1 + 10r | )<br>(n |                    |        |    | Input, Increment and Repeat dst $\leftarrow$ src Autoincrement dst address R $\leftarrow$ R - 1 Repeat until R = 0  |

| OUT (2)<br>OUTB (2)                         | dst,R     | IR<br>DA      | 10<br>12 | -       | -       |                    |        |    | Output<br>dst ← R                                                                                                   |

| OUTD (2)<br>OUTDB (2)                       | dst,src,R | IR            | 21       | -       | -       |                    |        |    | Output and Decrement dst $\leftarrow$ src Autodecrement src address R $\leftarrow$ R - 1                            |

| OTDR (2)<br>OTDRB (2)                       | dst,src,R | IR            | (1       | 1 + 10r | 1)      |                    |        |    | Output, Decrement and Repeat dst ← src Autodecrement src address R ← R - 1 Repeat until R = 0                       |

| OUTI <sup>(2)</sup><br>OUTIB <sup>(2)</sup> | dst,src,R | IR            | 21       | -       | -       |                    |        |    | Output and Increment dst $\leftarrow$ src Autoincrement src address R $\leftarrow$ R - 1                            |

| OTIR (2)<br>OTIRB (2)                       | dst,src,R | IR            | (1       | 1 + 10r | ۱)      |                    |        |    | Output, Increment and Repeat dst $\leftarrow$ src Autoincrement src address R $\leftarrow$ R - 1 Repeat until R = 0 |

# Input/Output (Continued)

| Mnemonics               | Operands  | Addr.<br>Modes |            | (       | Clock ( | Cycles <sup>(</sup> | 1) |    |                                                                                                                           |

|-------------------------|-----------|----------------|------------|---------|---------|---------------------|----|----|---------------------------------------------------------------------------------------------------------------------------|

|                         |           |                | Word, Byte |         |         | Long Word           |    |    | Operation                                                                                                                 |

|                         |           |                | NS         | SS      | SL      | NS                  | SS | SL | -                                                                                                                         |

| SIN (2)<br>SINB (2)     | R,src     | DA             | 12         | -       | -       |                     |    |    | Special Input<br>R ← src                                                                                                  |

| SIND (2)<br>SINDB (2)   | dst,src,R | IR             | 21         | -       | -       |                     |    |    |                                                                                                                           |

| SINDR (2)<br>SINDRB (2) | dst,src,R | IR             | (*         | 11 + 10 | n)      |                     |    |    | Special Input, Decr. and Repeat dst $\leftarrow$ src Autodecrement dst address R $\leftarrow$ R - 1 Repeat until R = 0    |

| SINI (2)<br>SINIB (2)   | dst,src,R | IR             | 21         | -       | -       |                     |    |    | Special Input and Increment dst ← src Autoincrement dst address R ← R - 1                                                 |

| SINIR (2)<br>SINIRB (2) | dst,src,R | IR             | ('         | 11 + 10 | n)      |                     |    |    | Special Input, Incr. and Repeat dst ← src Autoincrement dst address R ← R - 1 Repeat until R = 0                          |

| SOUT (2)<br>SOUTB (2)   | dst,src   | DA             | 12         | -       | -       |                     |    |    | Special Output<br>dst ← src                                                                                               |

| SOUTD (2)<br>SOUTDB (2) | dst,src,R | IR             | 21         | -       | -       |                     |    |    | Special Output and Decrement dst $\leftarrow$ src Autodecrement src address R $\leftarrow$ R - 1                          |

| SOTDR (2)<br>SOTDRB (2) | dst,src,R | IR             | (          | 11 + 10 | n)      |                     |    |    | Special Output, Decr. and Repeat dst $\leftarrow$ src Autodecrement src address $R \leftarrow R - 1$ Repeat until $R = 0$ |

| SOUTI (2)<br>SOUTIB (2) | dst,src,R | IR             | 21         | -       | -       |                     |    |    | Special Output and Increment dst ← src Autoincrement src address R ← R - 1                                                |

| SOTIR (2)<br>SOTIRB (2) | dst,src,R | IR             | (          | 11 + 10 | n)      |                     |    |    | Special Output, Incr. and Repeat dst $\leftarrow$ src Autoincrement src address R $\leftarrow$ R - 1 Repeat until R = 0   |

## **CPU Control**

| Mnemonics            | Operands | Addr.<br>Modes | Clock Cycles (1) |          |                |           |         |    |                                                                                         |  |

|----------------------|----------|----------------|------------------|----------|----------------|-----------|---------|----|-----------------------------------------------------------------------------------------|--|

|                      |          |                | Word, Byte       |          |                | Long Word |         |    | Operation                                                                               |  |

|                      |          |                | NS               | SS       | SL             | NS        | SS      | SL | -                                                                                       |  |

| COMFLG               | flags    | -              | 7                | -        | -              |           |         |    | Complement Flag<br>(Any combination of C, Z, S, P/V)                                    |  |

| DI <sup>(2)</sup>    | int      | -              | 7                | -        | -              |           |         |    | Disable Interrupt<br>(Any combination of NVI, VI)                                       |  |

| E1 <sup>(2)</sup>    | int      | -              | 7                | -        | -              | -         | -       |    | Enable Interrupt<br>(Any combination of NVI, VI)                                        |  |

| HALT (2)             | -        | -              | (                | (8 + 3n) |                |           | _       |    | HALT                                                                                    |  |

| LDCTL <sup>(2)</sup> | CTLR,src | R              | 7                | -        | -              |           |         |    | Load into Control Register<br>CTLR ← src                                                |  |

| LDCTL (2)            | dst,CTLR | R              | 7                | -        | -              | -         |         |    | Load from Control Register dst ← CTLR                                                   |  |

| LDCTLB               | FLGR,src | R              | 7                | -        | -              |           |         |    | Load into Flag Byte Register FLGR ← src                                                 |  |

| LDCTLB               | dst,FLGR | R              | 7                | -        | -              |           |         |    | Load from Flag Byte Register<br>dst ← FLGR                                              |  |

| LDPS (2)             | src      | IR<br>DA<br>X  | 12<br>16<br>17   | 20<br>20 | 16<br>22<br>23 |           |         |    | <b>Load Program Status</b> PS ← src                                                     |  |

| MBIT (2)             | -        | -              | 7                | -        | -              |           |         |    | Test Multi-Micro Bit Set S if M <sub>I</sub> is Low; reset S if M <sub>I</sub> is High. |  |

| MREQ (2)             | dst      | R              | (                | 12 + 7n) | )              |           |         |    | Multi-Micro Request                                                                     |  |

| MRES (2)             | •        | -              | 5                | -        | -              |           | · · · · |    | Multi-Micro Reset                                                                       |  |

| MSET (2)             | -        | -              | 5                | -        | -              |           |         |    | Multi-Micro Set                                                                         |  |

| NOP                  | -        | -              | 7                | -        | -              |           |         | -  | No Operation                                                                            |  |

| RESFLG               | flag     |                | 7                | -        | -              |           |         |    | Reset Flag<br>(Any combination of C, Z, S, P/V)                                         |  |

| SETFLG               | flag     | -              | 7                | -        | -              |           |         |    | Set Flag<br>(Any combination of C, Z, S, P/V)                                           |  |

#### Notes:

NS = Non-Segmented

SS = Segmented Short Offset

SL = Segmented Long Offset.

2. Privileged instruction. Executed in system mode only.

## **Condition Codes**

| Code | Meaning                        | Flag Settings             | CC Field |

|------|--------------------------------|---------------------------|----------|

|      | Always false                   | -                         | 0000     |

|      | Always true                    | -                         | 1000     |

| Z    | Zero                           | Z = 1                     | 0110     |

| NZ   | Not zero                       | Z = 0                     | 1110     |

| С    | Carry                          | C = 1                     | 0111     |

| NC   | No Carry                       | C = 0                     | 1111     |

| PL   | Plus                           | S = 0                     | 1101     |

| MI   | Minus                          | S = 1                     | 0101     |

| NE   | Not equal                      | Z = 0                     | 1110     |

| EQ   | Equal                          | Z = 1                     | 0110     |

| OV   | Overflow                       | P/V = 1                   | 0100     |

| NOV  | No overflow                    | P/V = 0                   | 1100     |

| PE   | Parity is even                 | P/V = 1                   | 0100     |

| PO   | Parity is odd                  | P/V = 0                   | 1100     |

| GE   | Greater than or equal (signed) | (S XOR P/V) = 0           | 1001     |

| LT   | Less than (signed)             | (S XOR P/V) = 1           | 0001     |

| GT   | Greater than (signed)          | [Z OR (S XOR P/V)] = 0    | 1010     |

| LE   | Less than or equal (signed)    | [Z OR (S XOR P/V)] = 1    | 0010     |

| UGE  | Unsigned greater than or equal | C = 0                     | 1111     |

| ULT  | Unsigned less than             | C = 1                     | 0111     |

| UGT  | Unsigned greater than          | [(C = 0) AND (Z = 0)] = 1 | 1011     |

| ULE  | Unsigned less than or equal    | (C OR Z) = 1              | 0011     |

Note that some condition codes have identical flag settings and binary fields in the instruction :

Z = EQ, NZ = NE, C = ULT, NC = UGE, OV = PE, NOV = PO

## PIN CONFIGURATION

#### Introduction

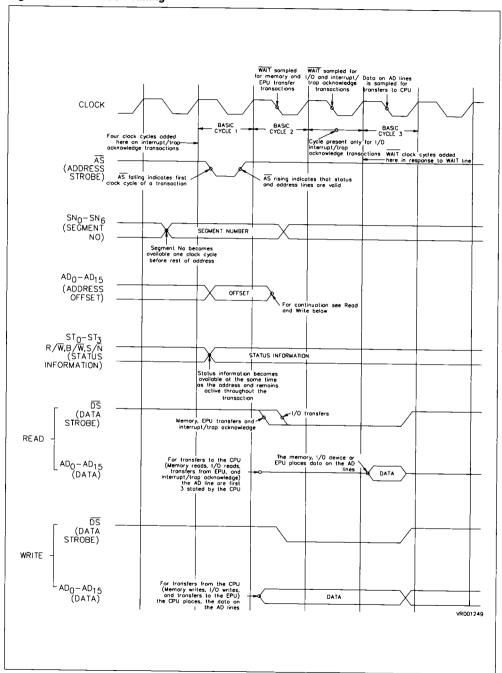

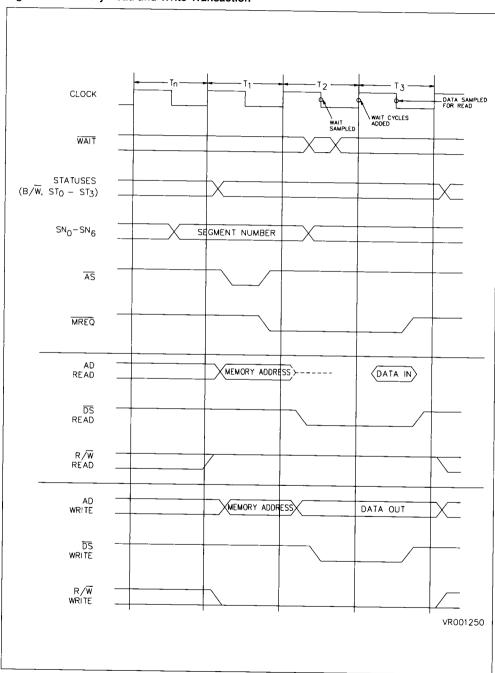

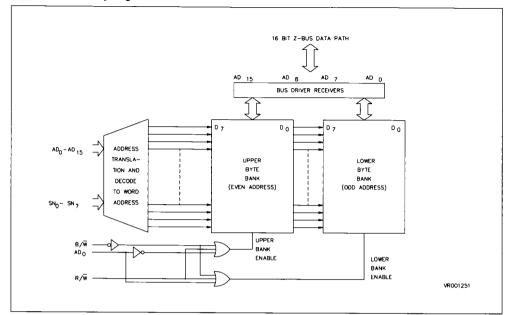

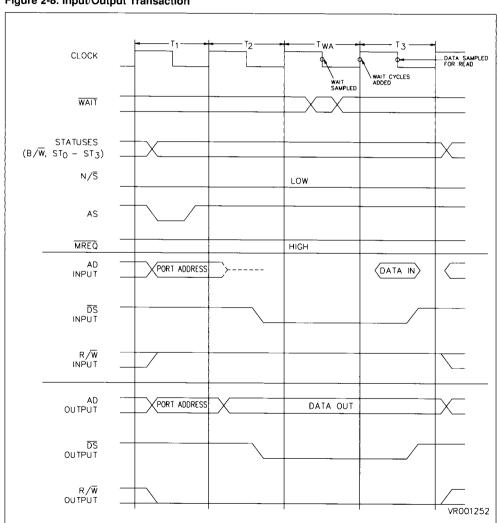

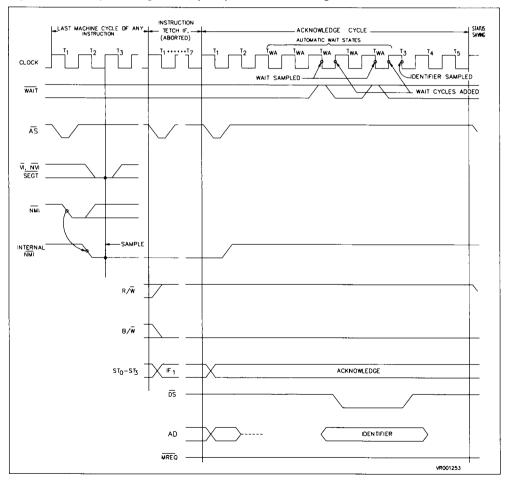

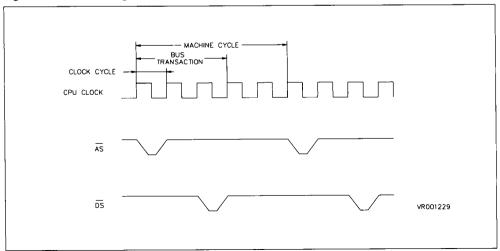

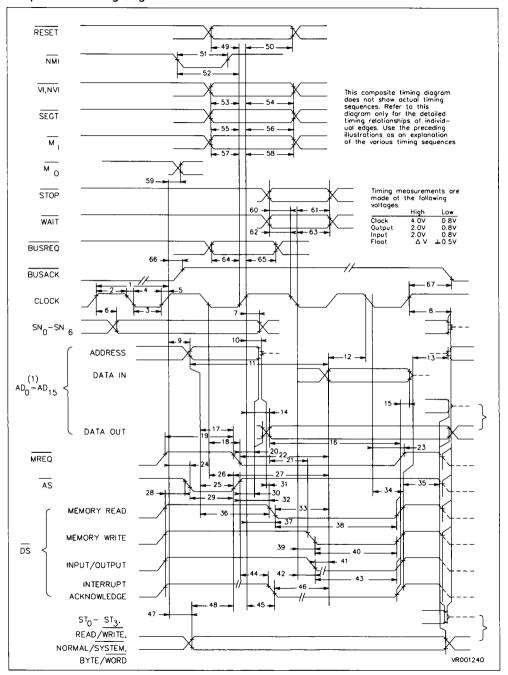

This chapter covers the external manifestations (e.g., the activity on the CPU pins) that result from the operations described in prerious chapters. Since the pins are connected to the system bus much of the discussion will center on the bus and bus operations. The Z8000 CPU is designed to be compatible with the Z-BUS protocols, which are described in the Z-BUS Summary. In the sections that follow, the interface between the Z8000 CPU and its environment is described in detail.

## **Bus Operations**

Two kinds of operations can occur on the system bus: transactions and requests. At any given time, one device (either the CPU or a bus requester, such as the Z8016 DMA Controller) has control of the bus and is known as the *bus master*. A transaction is initiated by the bus master and is responded to by some other device on the bus. Only one transaction can proceed at a time; six kinds of transactions can occur:

- Memory transaction. This type is used to transfer eight or 16 bits of data to or from a memory location

- I/O transaction. This type is used to transfer eight or 16 bits of data to or from a peripheral or CPU support component, such as an MMU

- EPU transfer. This type is used to transfer 16 bits of data between the CPU and an EPU

- Interrupt/Trap Acknowledge. This type is used to acknowledge an interrupt or trap and to transfer an identification/status word from the interrupting or trapping device

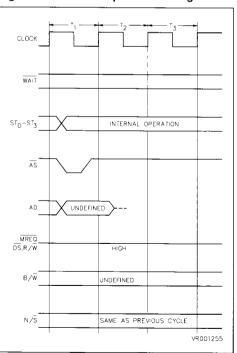

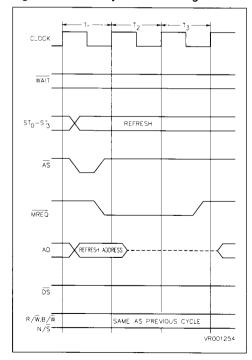

- Refresh. These transactions do not transfer data. They refresh dynamic memory

- Internal operation. These transactions do not transfer data. They indicate that the CPU is performing an operation that does not require data to be transferred on the bus

Only the bus master may initiate transactions. A request, however, may be initiated by a component that does not have control of the bus. Four types of requests can occur:

- Interrupt request. This type is used to request the attention of the CPU

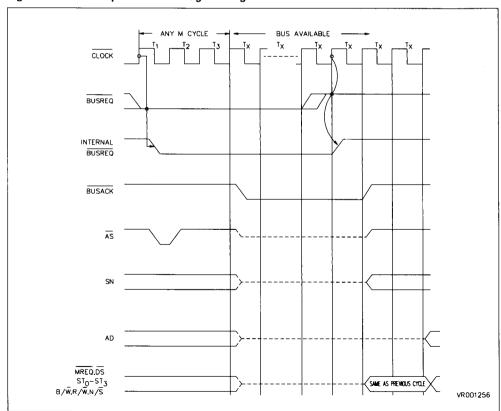

- Bus request. This type is used to request control of the bus to initiate transactions

- Resource request. This type is used to request control of a particular system resource

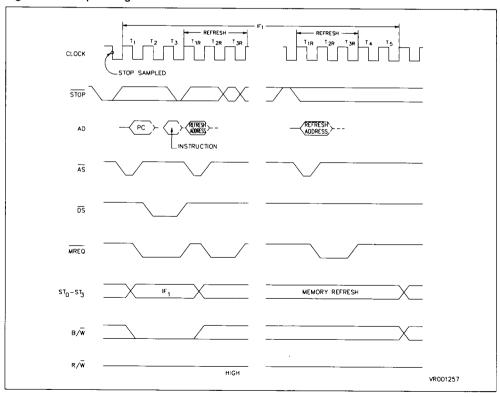

Stop request. This type is used to delay CPU instruction execution

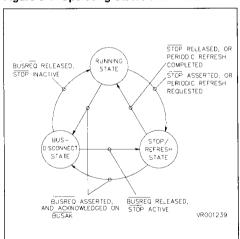

When an interrupt or bus request is made, it is answered by the CPU according to its type: for interrupt request, an interrupt acknowledge transaction is initiated; for bus requests, the CPU enters Bus Disconnect state, relinguishes the bus, and activates an acknowledge signal; for stop requests, the CPU stops execution and enters Stop/Refresh state. A resource request is generated by the CPU when it executes a multi-micro request instruction.

## Cpu Pins

The CPU pins can be grouped into five categories according to their functions.

**Transaction Pins.** These signals provide timing, control, and data transfer for Z-Bus transactions.

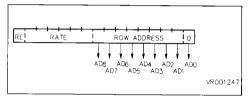

- ADo AD15. Address/Data (Output, active High, 3-state). These multiplexed data and address lines carry I/O addresses, memory addresses, and data during Z-Bus transactions. For the Z8001, only the offset portion of memory addresses is carried on these lines.

- SN<sub>0</sub> SN<sub>7</sub>. Segment Number (Z8001 only, Output, active High, 3-state). These lines contain the segment number portion of a memory address.