# S3C2501X

# 32-BIT RISC MICROPROCESSOR USER'S MANUAL

**Revision 1**

## **Important Notice**

The information in this publication has been carefully checked and is believed to be entirely accurate at the time of publication. Samsung assumes no responsibility, however, for possible errors or omissions, or for any consequences resulting from the use of the information contained herein.

Samsung reserves the right to make changes in its products or product specifications with the intent to improve function or design at any time and without notice and is not required to update this documentation to reflect such changes.

This publication does not convey to a purchaser of semiconductor devices described herein any license under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Samsung assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation any consequential or incidental damages.

S3C2501X RISC Microprocessor User's Manual, Revision 1

Publication Number: 21-S3-C2501X-122002

written consent of Samsung Electronics.

© 2002 Samsung Electronics

Samsung Electronics' Microprocessor business has been awarded full ISO-14001

Samsung Electronics' Microprocessor business has been awarded full ISO-14001 certification (BSI Certificate No. FM24653). All semiconductor products are designed and manufactured in accordance with the highest quality standards and objectives.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior

Samsung Electronics Co., Ltd. San #24 Nongseo-Ri, Kiheung-Eup Yongin-City, Kyunggi-Do, Korea C.P.O. Box #37, Suwon 449-900

TEL: (82)-(31)-209-2831 FAX: (82)-(31)-209-8309

Home-Page URL: http://www.samsungsemi.com

Printed in the Republic of Korea

"Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts.

Samsung products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, for other applications intended to support or sustain life, or for any other application in which the failure of the Samsung product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use a Samsung product for any such unintended or unauthorized application, the Buyer shall indemnify and hold Samsung and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim of personal injury or death that may be associated with such unintended or unauthorized use, even if such claim alleges that Samsung was negligent regarding the design or manufacture of said product.

## **Table of Contents**

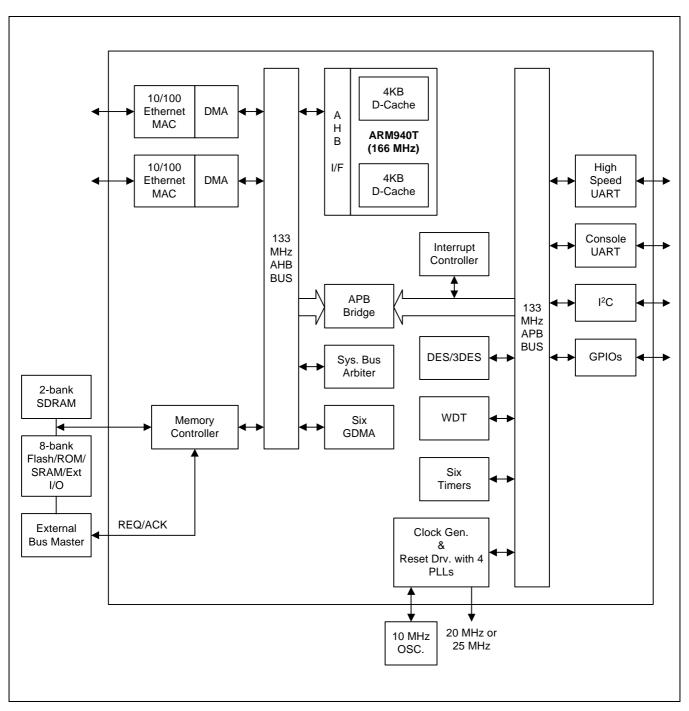

| Chapter 1        | Product Overview                                   |      |

|------------------|----------------------------------------------------|------|

|                  |                                                    |      |

|                  |                                                    |      |

|                  | am                                                 |      |

| •                | agram                                              |      |

|                  | ent                                                |      |

|                  | ription                                            |      |

|                  |                                                    |      |

| 1.8 Special Regi | isters                                             | 1-27 |

| Chapter 2        | Programmer's Model                                 |      |

| 2.1 Overview     |                                                    | 2-1  |

|                  | ate                                                |      |

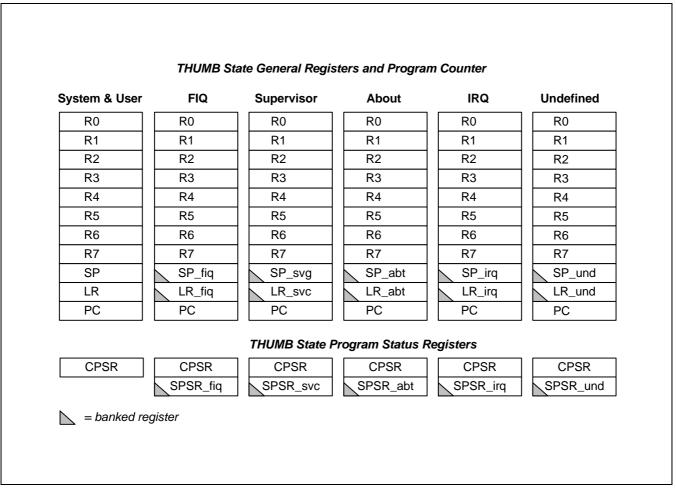

|                  | ring THUMB State                                   |      |

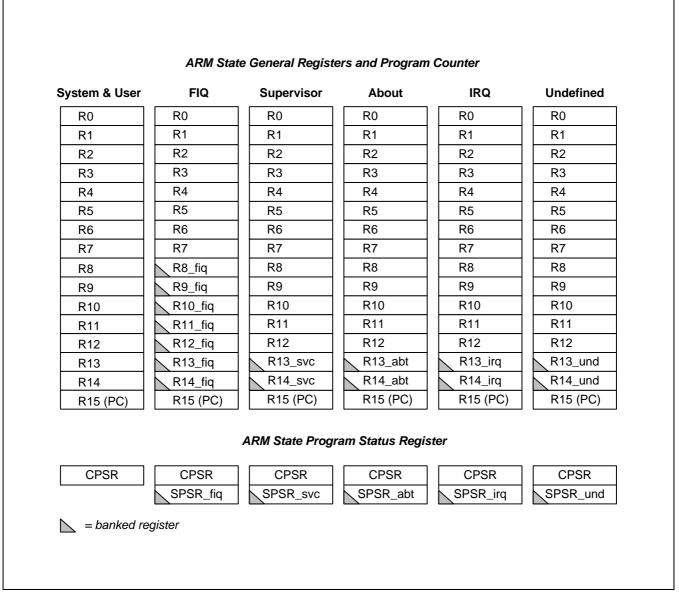

|                  | ring ARM State                                     |      |

|                  | mats                                               |      |

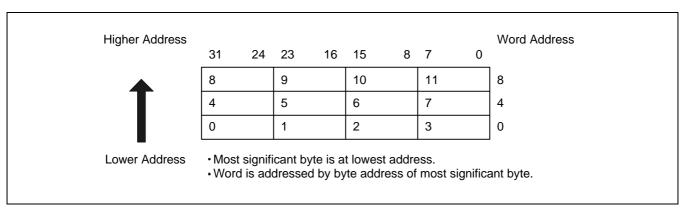

| -                | ndian Format                                       |      |

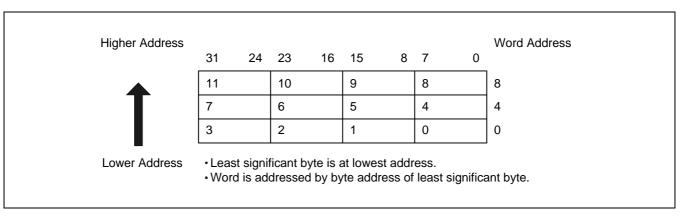

|                  | -Endian Format                                     |      |

|                  | ength                                              |      |

|                  |                                                    |      |

|                  | odes                                               |      |

|                  |                                                    |      |

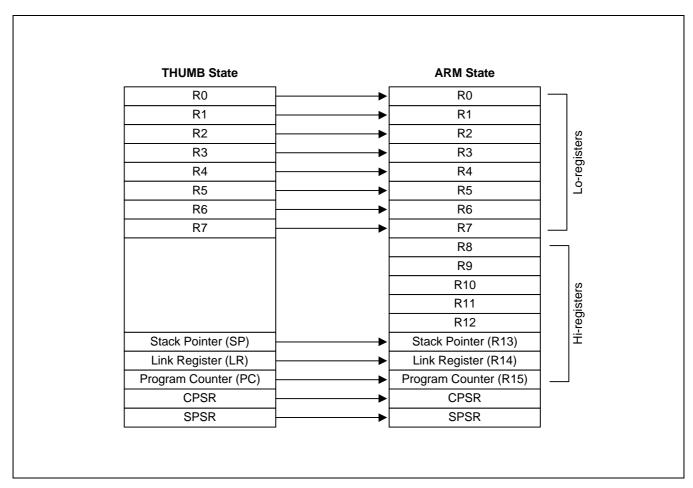

|                  | Relationship Between ARM and THUMB State Registers |      |

|                  | ssing Hi-Registers in THUMB State                  |      |

|                  | n Status Registers                                 |      |

|                  | Condition Code Flags                               |      |

|                  | Control Bits                                       |      |

|                  |                                                    |      |

|                  | n on Entering an Exception                         |      |

|                  | n on Leaving an Exception                          |      |

|                  | ption Entry/Exit Summary                           |      |

|                  |                                                    |      |

|                  |                                                    |      |

|                  | t                                                  |      |

|                  | vare Interrupt                                     |      |

|                  | fined Instruction                                  |      |

|                  | Vectors                                            |      |

|                  | eption Priorities                                  |      |

|                  | All Exceptions Can Occur at Once:                  |      |

|                  | atencies                                           |      |

|                  |                                                    |      |

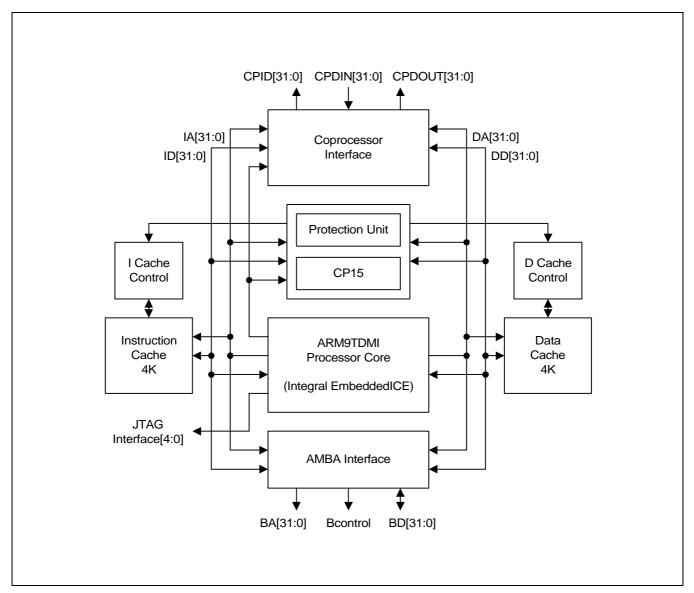

|                  | n for ARM940T                                      |      |

| 2.14 ARM940T E   | Block Diagram                                      | 2-18 |

2.15 About The ARM940T Programmer's Model

2-19

2.15.1 Data Abort Model

2-20

2.15.2 Instruction Set Extension Spaces

2-20

2.16 ARM940T CP15 Registers

2-21

2.16.1 CP15 Register Map Summary

2-21

S3C2501X

## Chapter 3 Instruction Set

| 3.1 Instruction Set Summay                                  | 3-1  |

|-------------------------------------------------------------|------|

| 3.1.1 Format Summary                                        |      |

| 3.1.2 Instruction Summary                                   | 3-2  |

| 3.2 The Condition Field                                     |      |

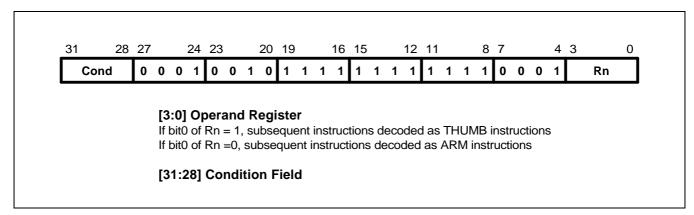

| 3.3 Branch and Exchange (BX)                                | 3-5  |

| 3.3.1 Instruction Cycle Times                               | 3-5  |

| 3.3.2 Assembler Syntax                                      |      |

| 3.3.3 Using R15 as an Operand                               | 3-5  |

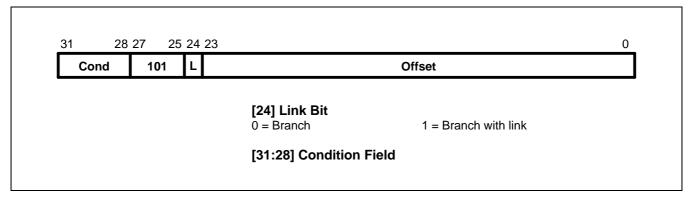

| 3.4 Branch and Branch with Link (B, BL)                     | 3-7  |

| 3.4.1 The Link Bit                                          |      |

| 3.4.2 Instruction Cycle Times                               | 3-7  |

| 3.4.3 Assembler Syntax                                      | 3-8  |

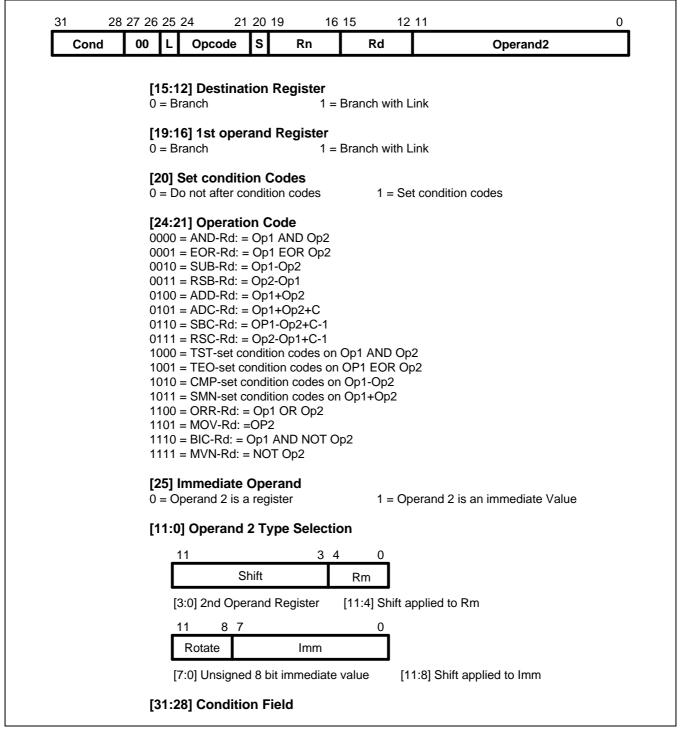

| 3.5 Data Processing                                         | 3-9  |

| 3.5.1 CPSR Flags                                            | 3-11 |

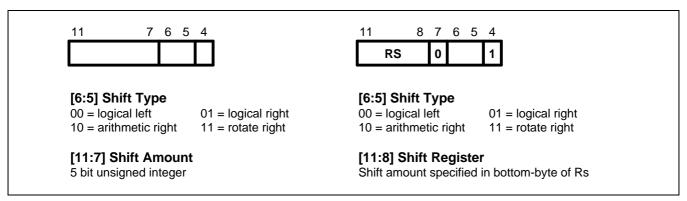

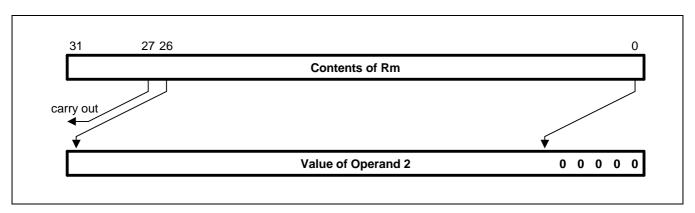

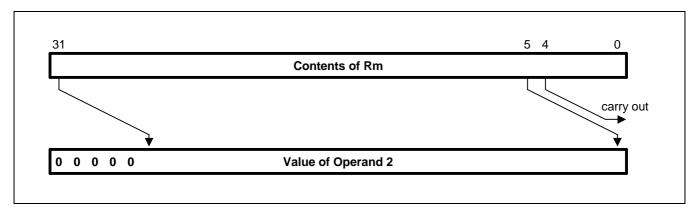

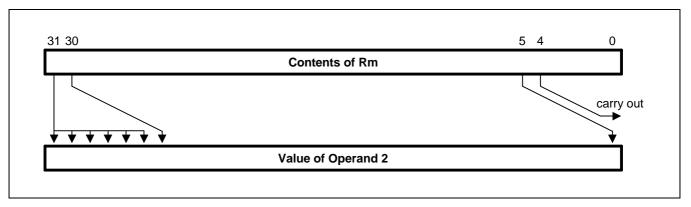

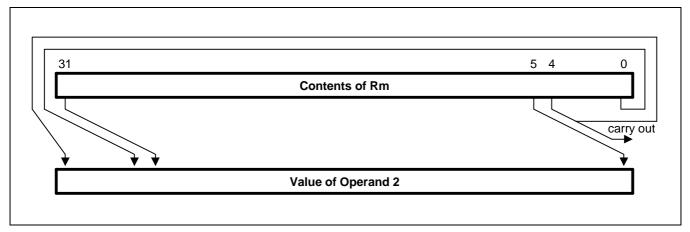

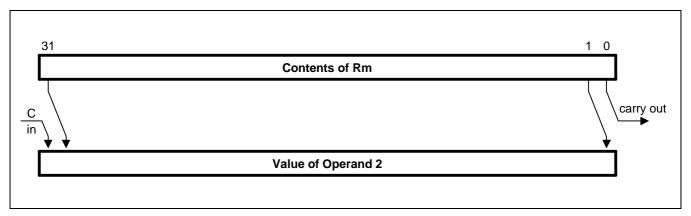

| 3.5.2 Shifts                                                |      |

| 3.5.3 Immediate Operand Rotates                             | 3-16 |

| 3.5.4 Writing to R15                                        | 3-16 |

| 3.5.5 Using R15 as an Operand                               |      |

| 3.5.6 Teq, Tst, Cmp and CMN Opcodes                         | 3-16 |

| 3.5.7 Instruction Cycle Times                               |      |

| 3.6.8 Assembler Syntax                                      |      |

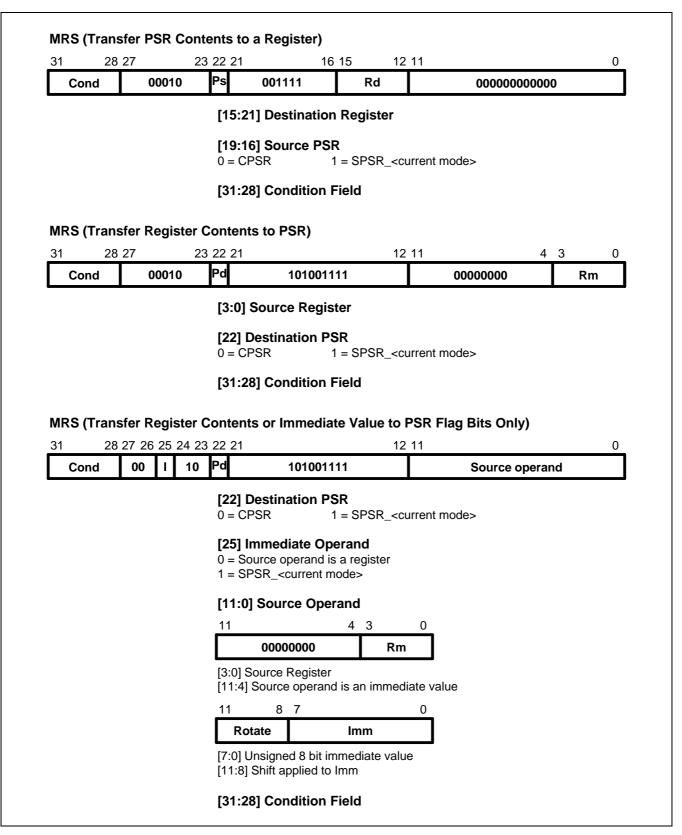

| 3.6 PSR Transfer (MRS, MSR)                                 |      |

| 3.6.1 Operand Restrictions                                  |      |

| 3.6.2 Reserved Bits                                         |      |

| 3.6.3 Instruction Cycle Times                               |      |

| 3.6.4 Assembler Syntax                                      |      |

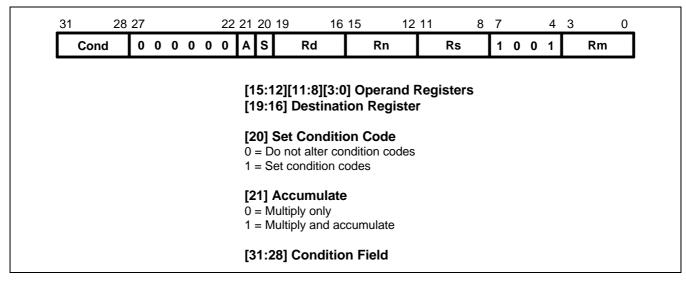

| 3.7 Multiply and Multiply-Accumulate (MUL, MLA)             |      |

| 3.7.1 CPSR Flags                                            | 3-24 |

| 3.7.2 Instruction Cycle Times                               |      |

| 3.7.3 Assembler Syntax                                      |      |

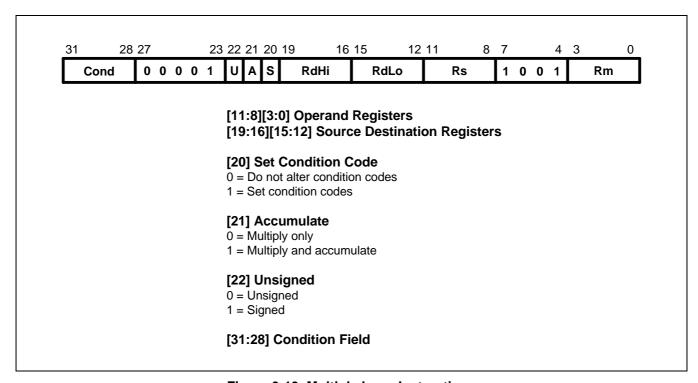

| 3.8 Multiply Long and Multiply-Accumulate Long (MULL, MLAL) | 3-25 |

| 3.8.1 Operand Restrictions                                  |      |

| 3.8.2 CPSR Flags                                            |      |

| 3.8.3 Instruction Cycle Times                               |      |

| 3.8.4 Assembler Syntax                                      |      |

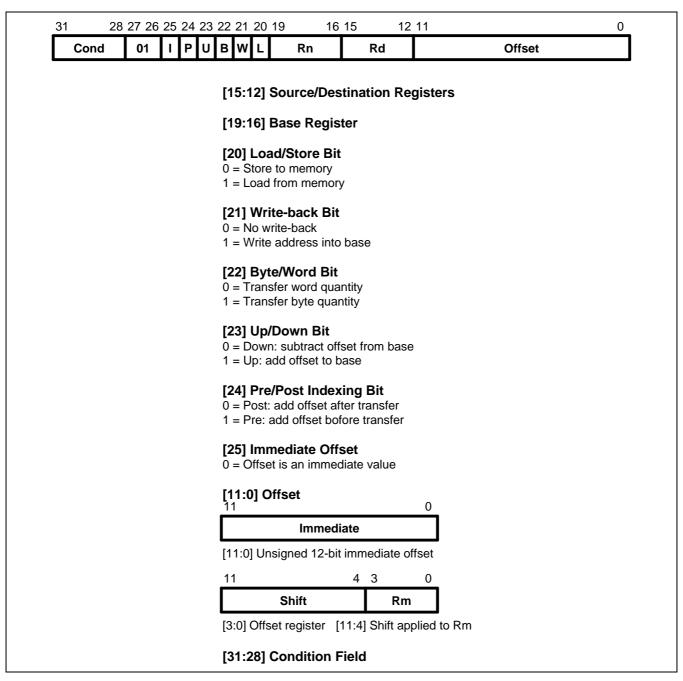

| 3.9 Single Data Transfer (LDR, STR)                         |      |

| 3.9.1 Offsets and Auto-Indexing                             |      |

| 3.9.2 Shifted Register Offset                               |      |

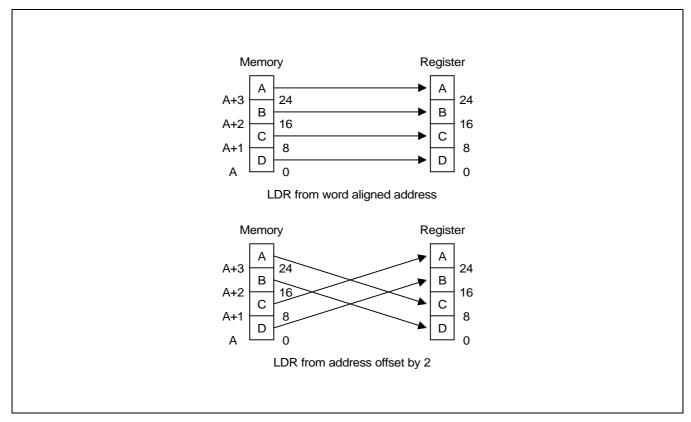

| 3.9.3 Bytes and Words                                       | 3-29 |

| 3.9.4 Use of R15                                            |      |

| 3.9.5 Restriction on the Use of Base Register               |      |

| 3.9.6 Data Aborts                                           | 3-31 |

| 3.9.7 Instruction Cycle Times                               | 3-31 |

| 3.9.8 Assembler Syntax                                      | 3-32 |

## Chapter 3 Instruction Set (Continued)

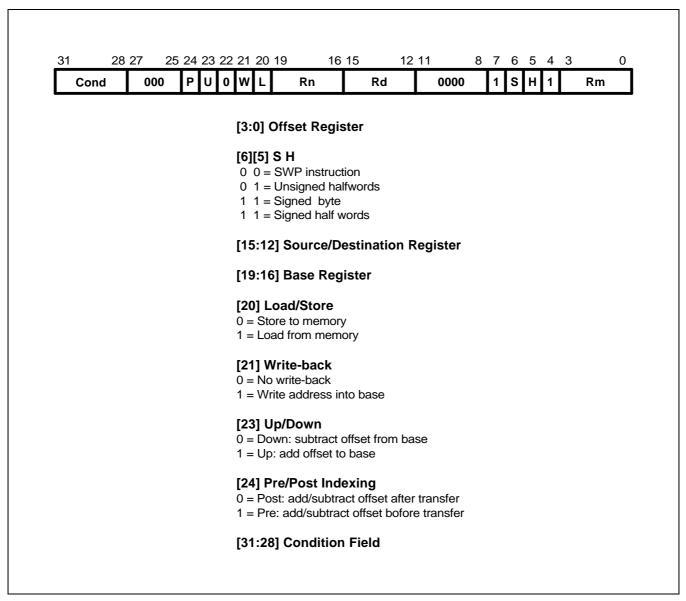

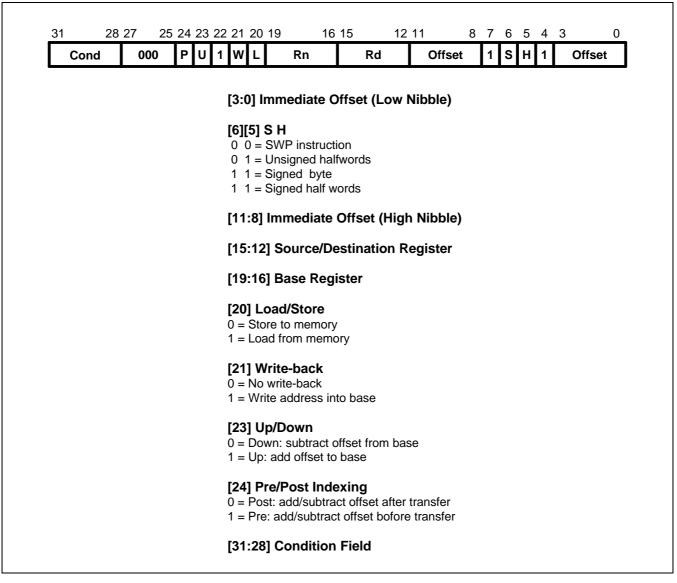

| 3.10 Halfword and Signed Data Transfer (LDRH/STRH/LDRSB/LDRSH) | 3-34 |

|----------------------------------------------------------------|------|

| 3.10.1 Offsets and Auto-Indexing                               |      |

| 3.10.2 Half-Word Load and Stores                               |      |

| 3.10.3 Signed Byte and Half-Word Loads                         | 3-36 |

| 3.10.4 Endianness and Byte/Half-Word Selection                 |      |

| 3.10.5 Use of R15                                              |      |

| 3.10.6 Data Aborts                                             |      |

| 3.10.7 Instruction Cycle Times                                 | 3-37 |

| 3.10.8 Assembler Syntax                                        |      |

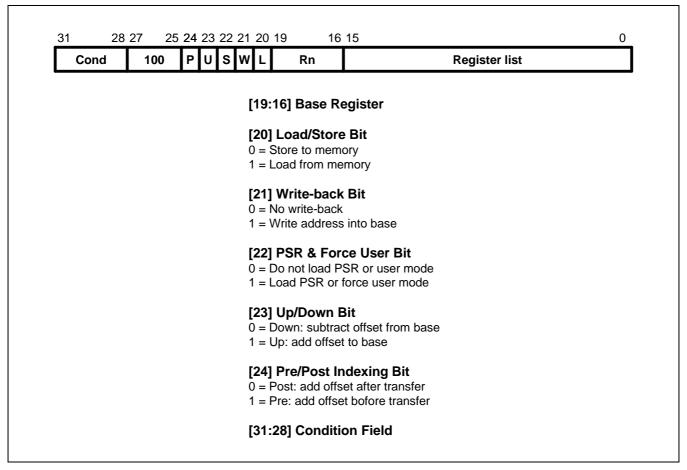

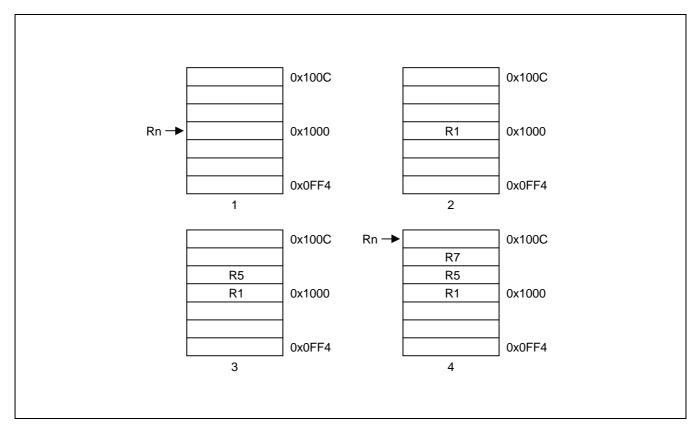

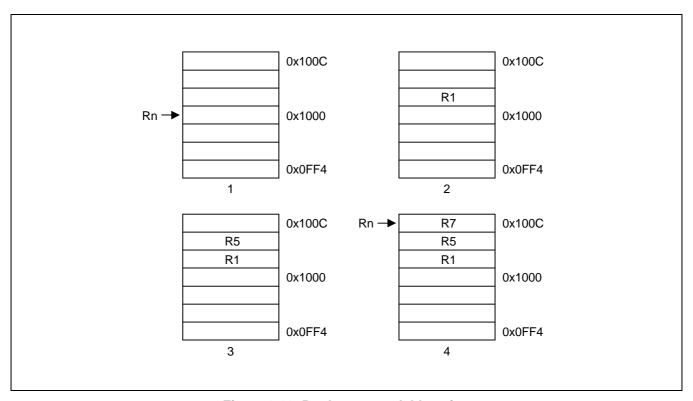

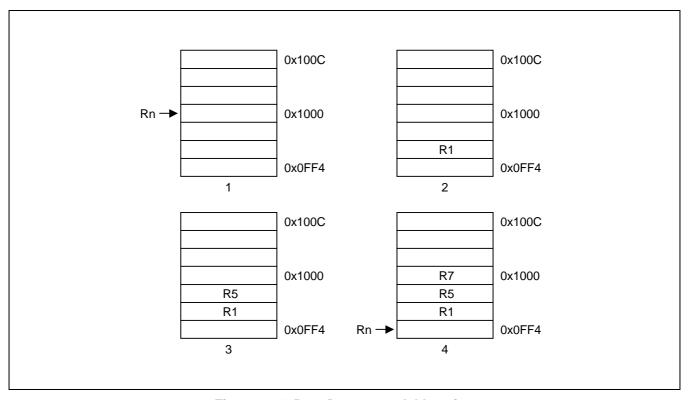

| 3.11 Block Data Transfer (LDM, STM)                            |      |

| 3.11.1 The Register List                                       |      |

| 3.11.2 Addressing Modes                                        |      |

| 3.11.3 Address Alignment                                       |      |

| 3.11.4 Use of the Š Bit                                        |      |

| 3.11.5 Use of R15 as the Base                                  |      |

| 3.11.6 Inclusion of the Base in the Register List              |      |

| 3.11.7 Data Aborts                                             |      |

| 3.11.8 Instruction Cycle Times                                 |      |

| 3.11.9 Assembler Syntax                                        |      |

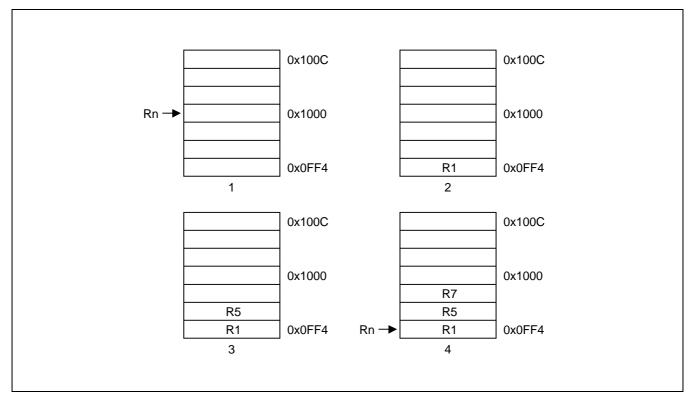

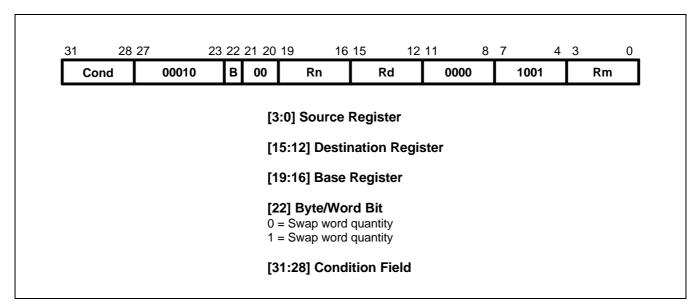

| 3.12 Single Data Swap (ŚWP)                                    |      |

| 3.12.1 Bytes and Words                                         |      |

| 3.12.2 Use of R15                                              | 3-47 |

| 3.12.3 Data Aborts                                             | 3-48 |

| 3.12.4 Instruction Cycle Times                                 | 3-48 |

| 3.12.5 Assembler Syntax                                        | 3-48 |

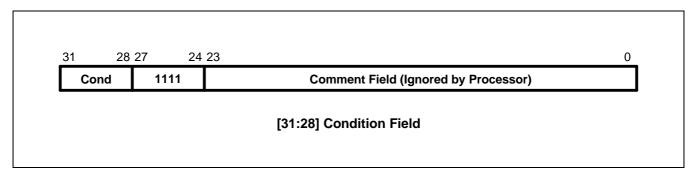

| 3.13 Software Interrupt (SWI)                                  | 3-49 |

| 3.13.1 Return from the Supervisor                              |      |

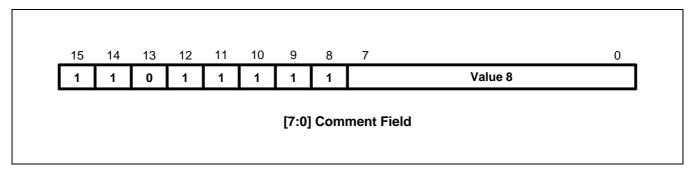

| 3.13.2 Comment Field                                           | 3-49 |

| 3.13.3 Instruction Cycle Times                                 | 3-49 |

| 3.13.4 Assembler Syntax                                        | 3-50 |

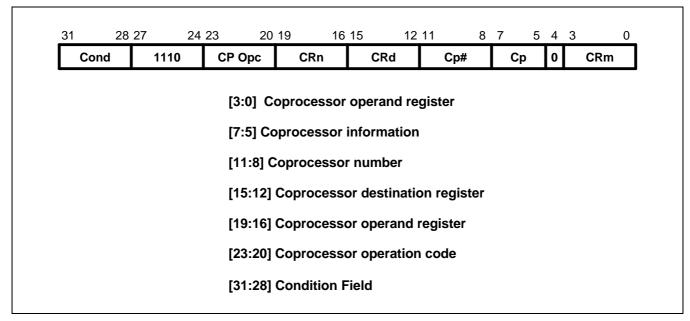

| 3.14 Coprocessor Data Operations (CDP)                         | 3-51 |

| 3.14.1 Coprocessor Instructions                                | 3-51 |

| 3.14.2 The Coprocessor Fields                                  | 3-51 |

| 3.14.3 Instruction Cycle Times                                 | 3-52 |

| 3.14.4 Assembler Syntax                                        | 3-52 |

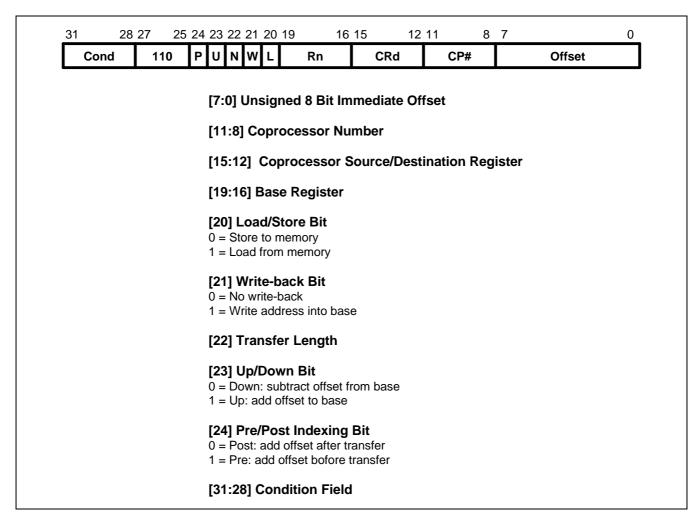

| 3.15 Coprocessor Data Transfers (LDC, STC)                     | 3-53 |

| 3.15.1 The Coprocessor Fields                                  | 3-53 |

| 3.15.2 Addressing Modes                                        | 3-54 |

| 3.15.3 Address Alignment                                       |      |

| 3.15.4 Use of R15                                              |      |

| 3.15.5 Data Aborts                                             | 3-54 |

| 3.15.6 Instruction Cycle Times                                 | 3-54 |

| 3.15.7 Assembler Syntax                                        | 3-55 |

S3C2501X

## Chapter 3 Instruction Set (Continued)

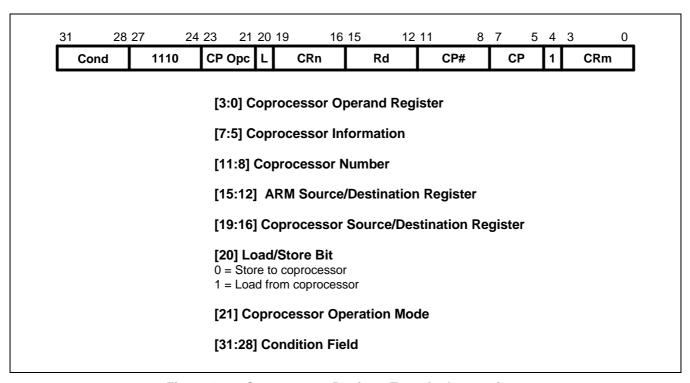

| 3.16 Coprocessor Register Transfers (MRC, MCR)             | 3-56 |

|------------------------------------------------------------|------|

| 3.16.1 The Coprocessor Fields                              | 3-56 |

| 3.16.2 Transfers to R15                                    |      |

| 3.16.3 Transfers from R15                                  | 3-57 |

| 3.16.4 Instruction Cycle Times                             |      |

| 3.16.5 Assembler Syntax                                    |      |

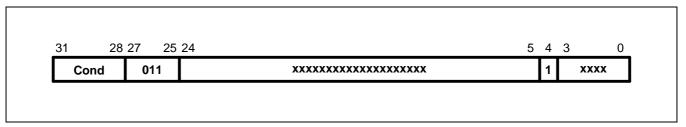

| 3.17 Undefined Instruction                                 |      |

| 3.17.1 Instruction Cycle Times                             | 3-58 |

| 3.17.2 Assembler Syntax                                    | 3-58 |

| 3.18 Instruction Set Examples                              |      |

| 3.18.1 Using The Conditional Instructions                  |      |

| 3.18.2 Pseudo-Random Binary Sequence Generator             | 3-61 |

| 3.18.3 Multiplication by Constant Using The Barrel Shifter | 3-61 |

| 3.18.4 Loading a Word From an Unknown Alignment            | 3-63 |

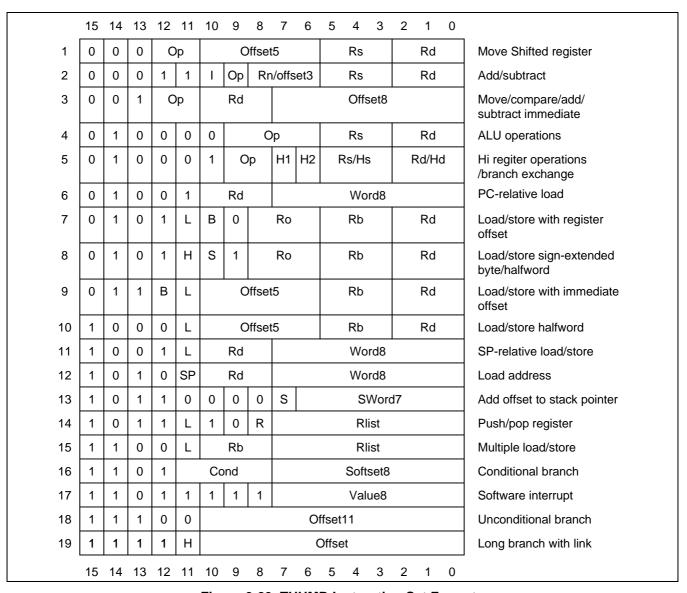

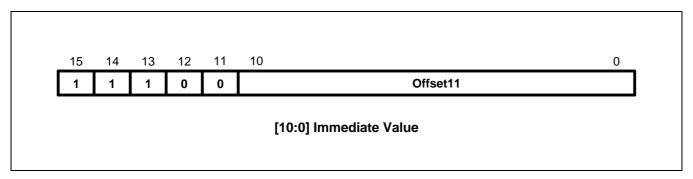

| 3.19 Thumb Instruction Set Format                          | 3-64 |

| 3.19.1 Format Summary                                      | 3-64 |

| 3.19.2 Opcode Summary                                      | 3-65 |

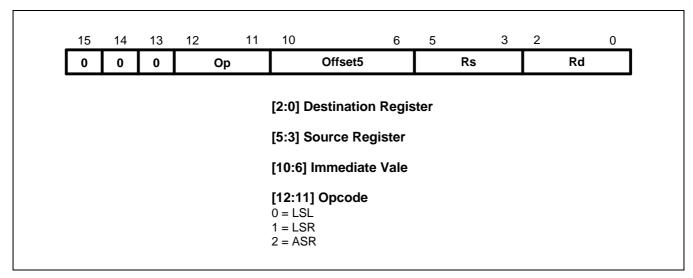

| 3.20 Format 1: Move Shifted Register                       | 3-67 |

| 3.20.1 Operation                                           | 3-67 |

| 3.20.2 Instruction Cycle Times                             | 3-67 |

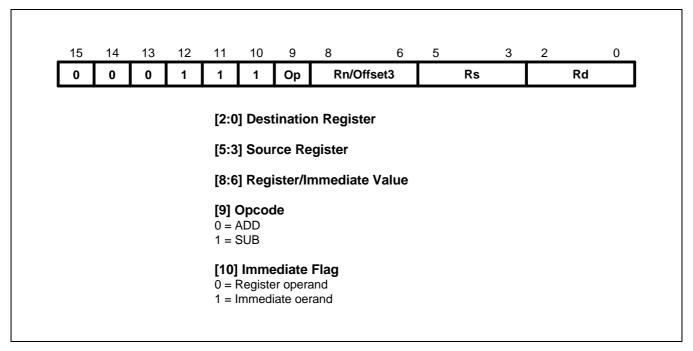

| 3.21 Format 2: Add/Subtract                                |      |

| 3.21.1 Operation                                           |      |

| 3.21.2 Instruction Cycle Times                             | 3-69 |

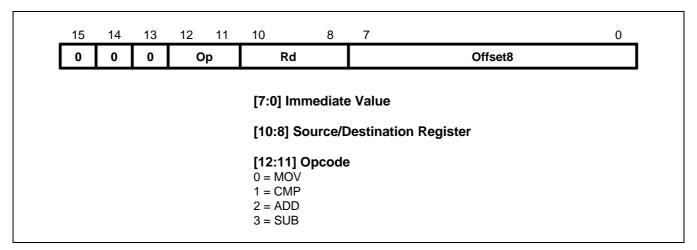

| 3.22 Format 3: Move/Compare/Add/Subtract Immediate         |      |

| 3.22.1 Operations                                          |      |

| 3.22.2 Instruction Cycle Times                             |      |

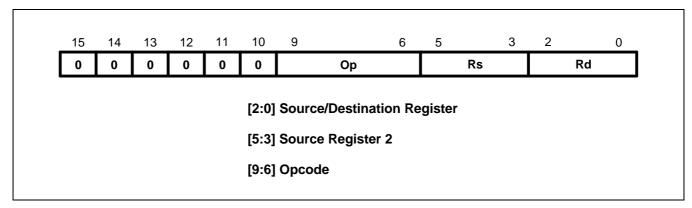

| 3.23 Format 4: ALU Operations                              |      |

| 3.23.1 Operation                                           |      |

| 3.23.2 Instruction Cycle Times                             |      |

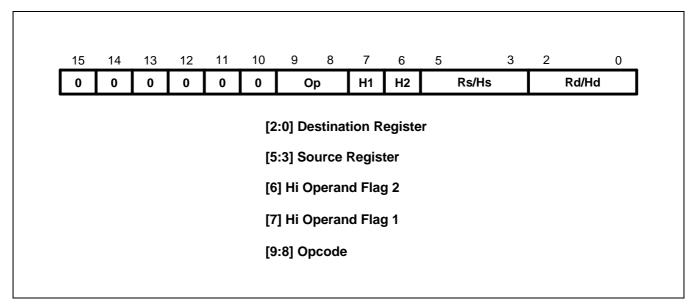

| 3.24 Format 5: Hi-Register Operations/Branch Exchange      | 3-73 |

| 3.24.1 Operation                                           |      |

| 3.24.2 Instruction Cycle Times                             |      |

| 3.24.3 The Bx Instruction                                  |      |

| 3.24.4 Using R15 as an Operand                             |      |

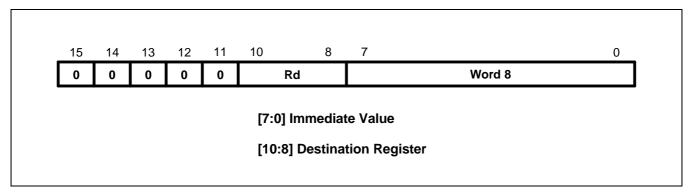

| 3.25 Format 6: PC-Relative Load                            |      |

| 3.25.1 Operation                                           |      |

| 3.25.2 Instruction Cycle Times                             |      |

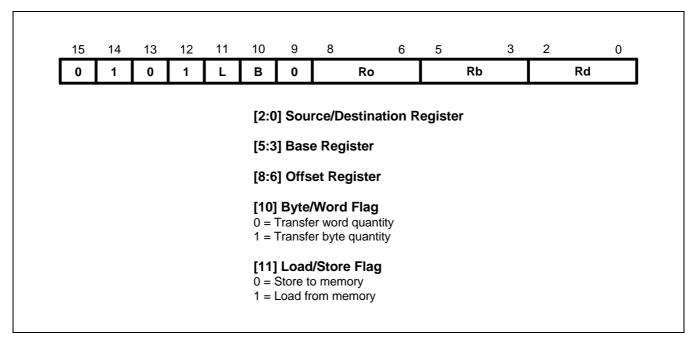

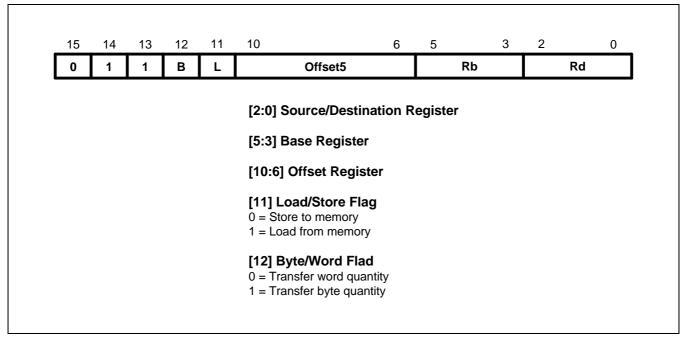

| 3.26 Format 7: Load/Store With Register Offset             |      |

| 3.26.1 Operation                                           | 3-77 |

| 3.26.2 Instruction Cycle Times                             | 3-78 |

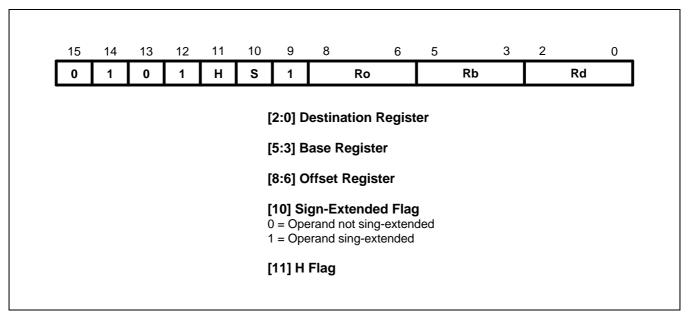

| 3.27 Format 8: Load/Store Sign-Extended Byte/Half-Word     |      |

| 3.27.1 Operation                                           |      |

| 3.27.2 Instruction Cycle Times                             | 3-80 |

vi S3C2501X

## Chapter 3 Instruction Set (Continued)

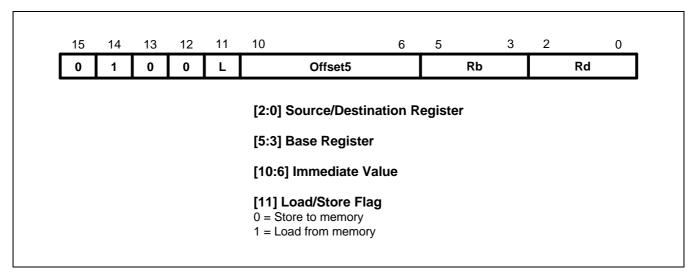

| 3.28 | Format 9: Load/Store with Immediate Offset                | 3-81  |

|------|-----------------------------------------------------------|-------|

|      | 3.28.1 Operation                                          | 3-81  |

|      | 3.28.2 Instruction Cycle Times                            | 3-82  |

| 3.29 | Format 10: Load/Store Half-Word                           | 3-83  |

|      | 3.29.1 Operation.                                         | 3-83  |

|      | 3.29.2 Instruction Cycle Times                            |       |

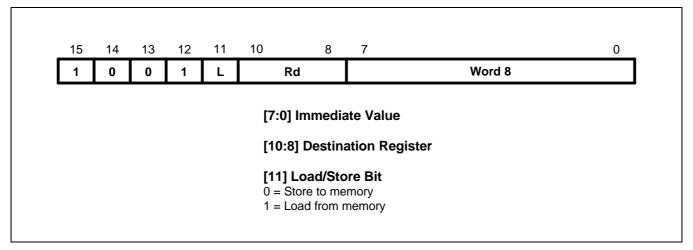

| 3.30 | Format 11: SP-Relative Load/Store                         |       |

|      | 3.30.1 Operation                                          | 3-84  |

|      | 3.30.2 Instruction Cycle Times                            |       |

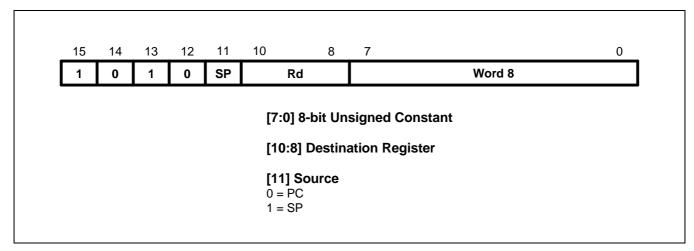

| 3.31 | Format 12: Load Addres                                    |       |

|      | 3.31.1 Operation                                          |       |

|      | 3.31.2 Instruction Cycle Times                            |       |

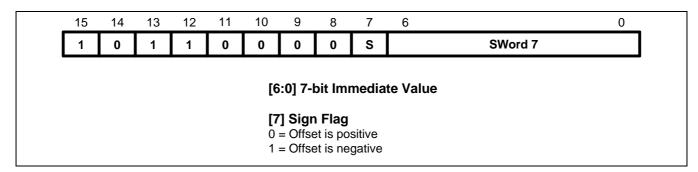

| 3.32 | Format 13: Add Offset to Stack Pointer                    |       |

|      | 3.32.1 Operation                                          |       |

|      | 3.32.2 Instruction Cycle Times                            | 3-87  |

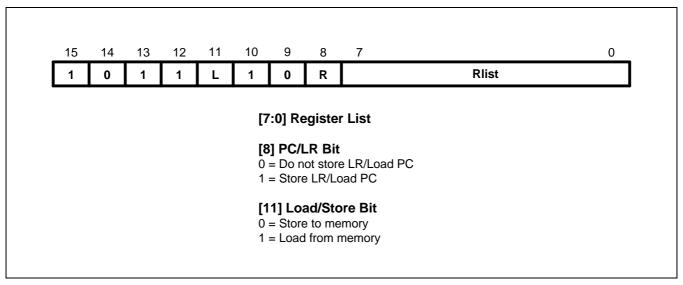

| 3.33 | Format 14: Push/Pop Registers                             |       |

|      | 3.33.1 Operation                                          |       |

|      | 3.33.2 Instruction Cycle Times                            |       |

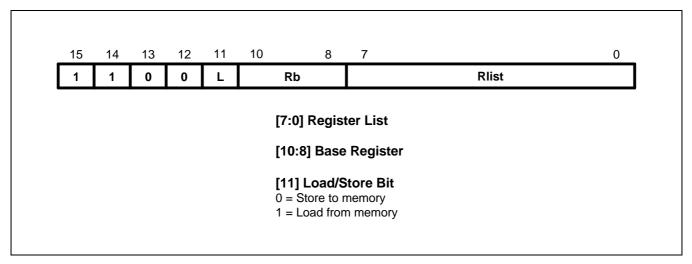

| 3.34 | Format 15: Multiple Load/Store                            | 3-90  |

|      | 3.34.1 Operation                                          | 3-90  |

|      | 3.34.2 Instruction Cycle Times                            | 3-90  |

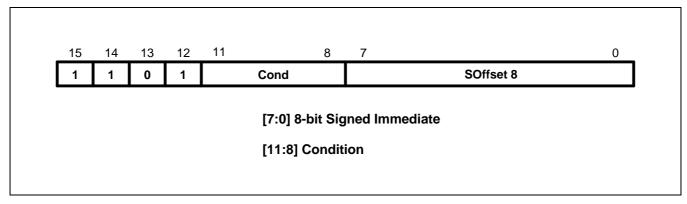

| 3.35 | Format 16: Conditional Branch                             | 3-91  |

|      | 3.35.1 Operation                                          | 3-91  |

|      | 3.35.2 Instruction Cycle Times                            | 3-92  |

| 3.36 | Format 17: Software Interrupt                             | 3-93  |

|      | 3.36.1 Operation                                          | 3-93  |

|      | 3.36.2 Instruction Cycle Times                            | 3-93  |

| 3.37 | Format 18: Unconditional Branch                           | 3-94  |

|      | 3.37.1 Operation                                          |       |

| 3.38 | Format 19: Long Branch With Link                          | 3-95  |

|      | 3.38.1 Operation                                          | 3-95  |

|      | 3.38.2 Instruction Cycle Times                            | 3-96  |

| 3.39 | Instruction Set Examples                                  | 3-97  |

|      | 3.39.1 Multiplication by a Constant Using Shifts and Adds | 3-97  |

|      | 3.39.2 General Purpose Signed Divide                      |       |

|      | 3.39.3 Division by a Constant                             | 3-100 |

S3C2501X vii

| Chapter 4        | System Configuration                       |      |

|------------------|--------------------------------------------|------|

| 4.1 Overview     |                                            | 4-1  |

|                  |                                            |      |

|                  | p                                          |      |

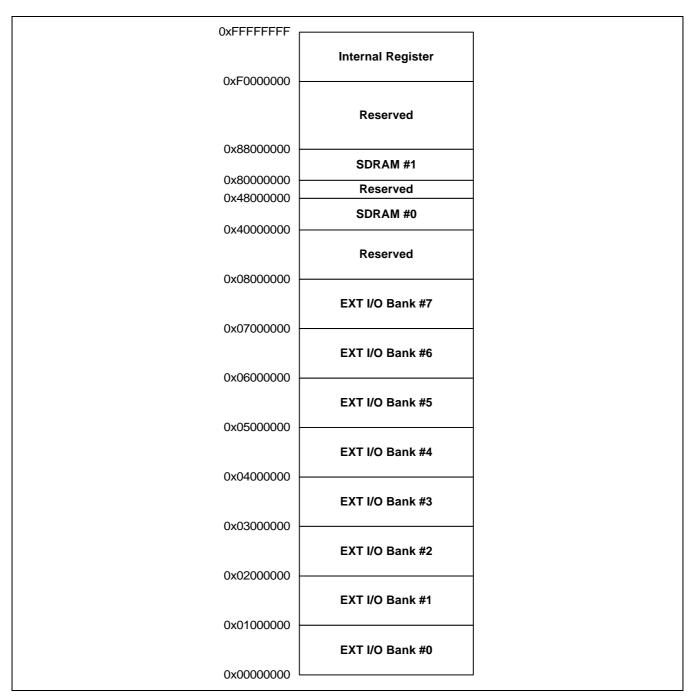

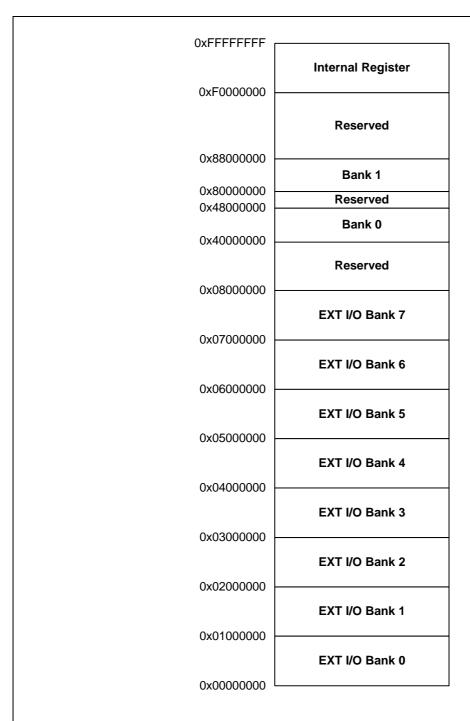

|                  | lemory Space                               |      |

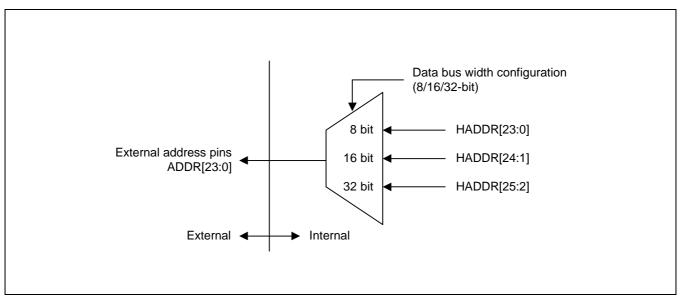

| 4.5 External Add | dress Translation                          | 4-3  |

|                  | Scheme                                     |      |

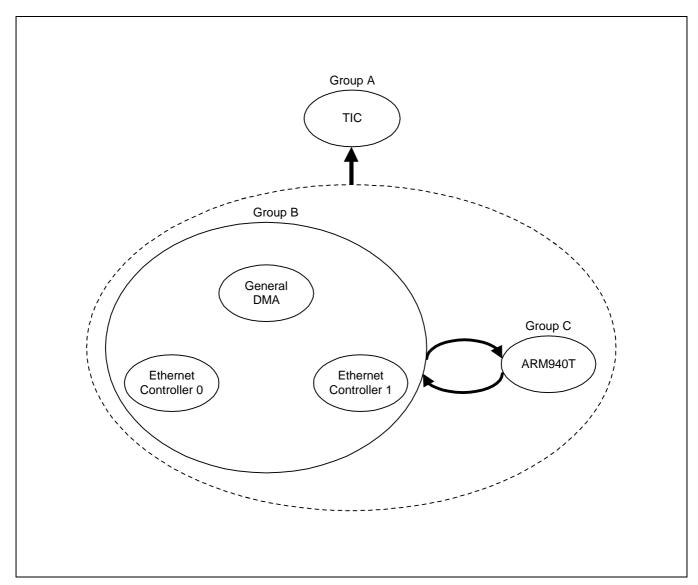

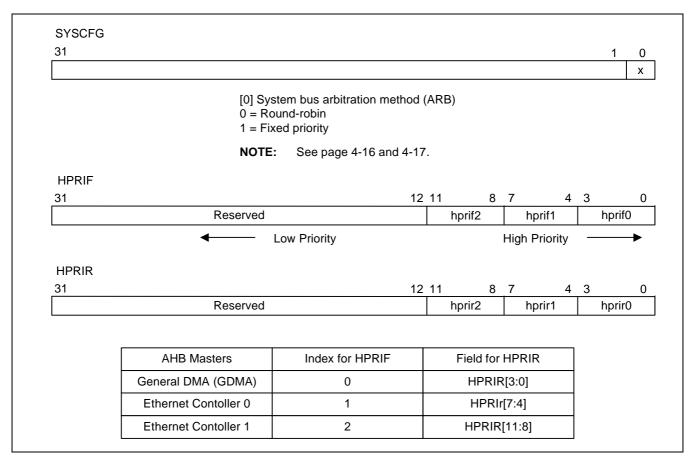

|                  | lem Solvings with Programmable Round-Robin |      |

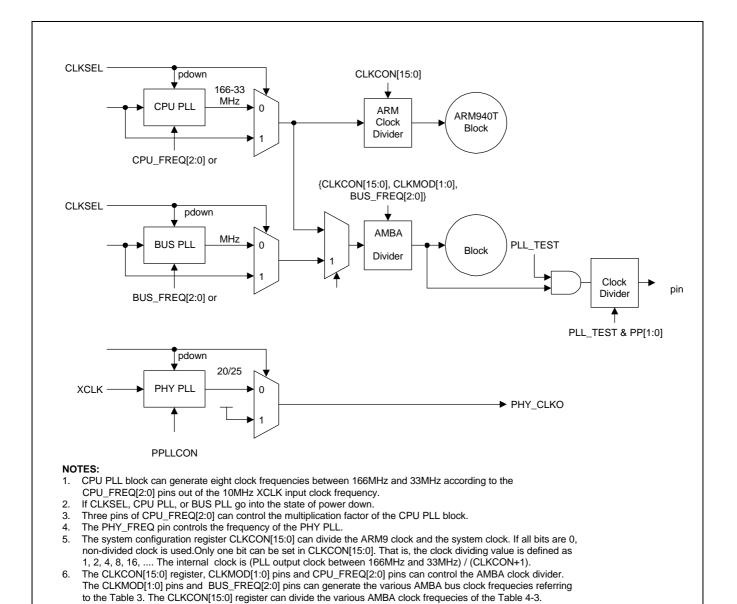

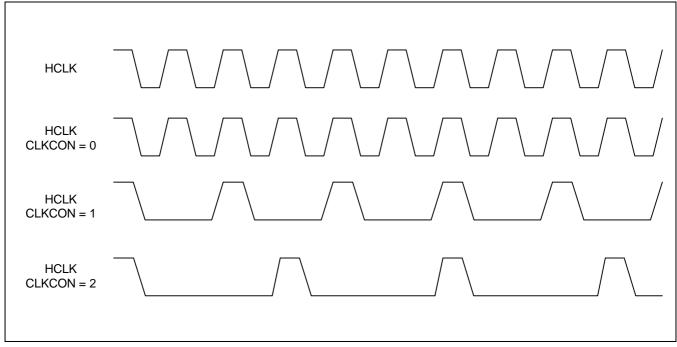

| 4.7 Clock Config | guration                                   | 4-9  |

| 4.8 System Con   | figuration Special Registers               | 4-15 |

|                  | em Configuration Register                  |      |

| 4.8.2 Prod       | uct Code and Revision Number Register      | 4-18 |

|                  | k Control Register                         |      |

|                  | heral Clock Disable Register               |      |

|                  | k Status Register                          |      |

|                  | Bus Master Priority Register               |      |

|                  | PLL Control Register                       |      |

|                  | em Bus PLL Control Register                |      |

| 4.8.9 PHY        | PLL Control Register                       | 4-24 |

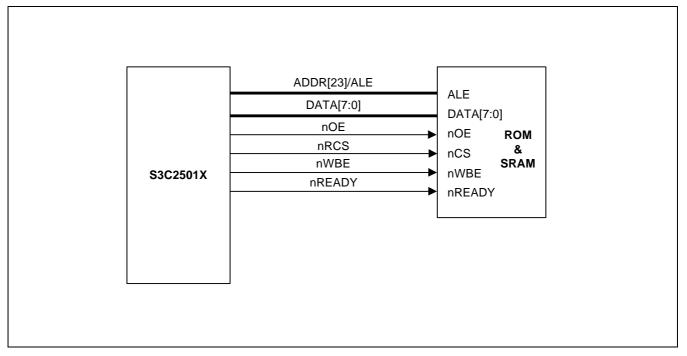

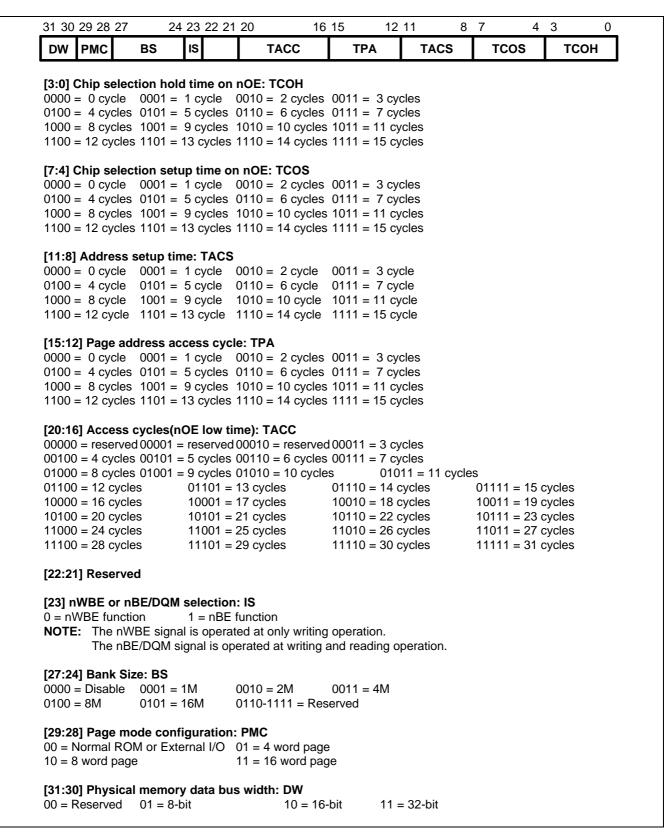

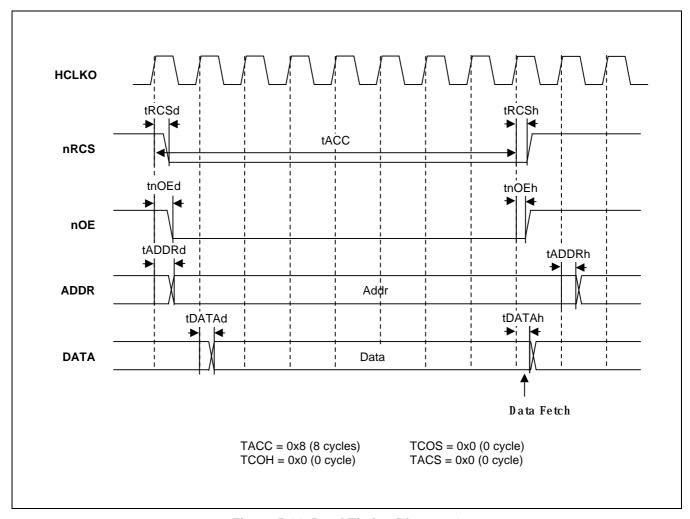

| Chapter 5        | Memory Controller                          |      |

| 5.1 Overview     |                                            | 5-1  |

| 5.2 Features     |                                            | 5-2  |

|                  | p                                          |      |

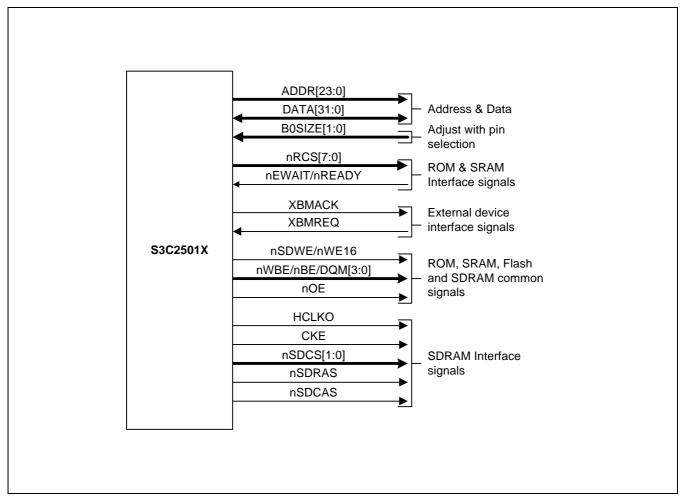

|                  | e Signals                                  |      |

|                  | es                                         |      |

|                  | k Controller                               |      |

|                  | ures                                       |      |

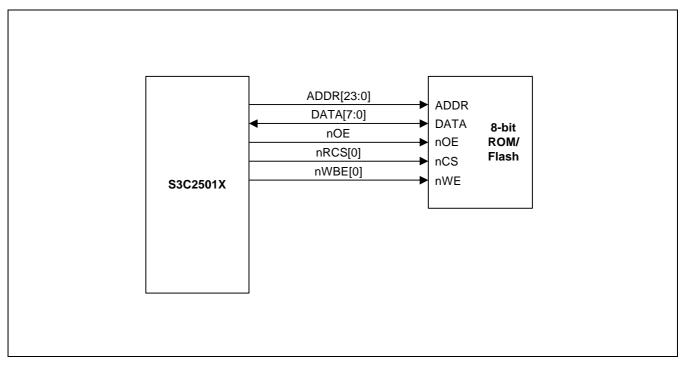

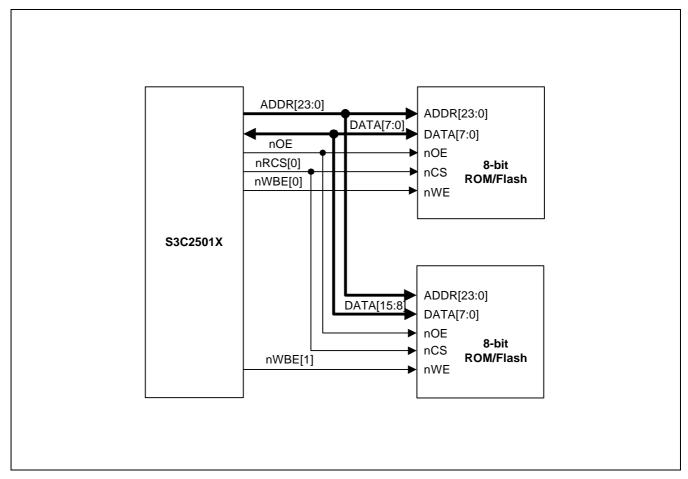

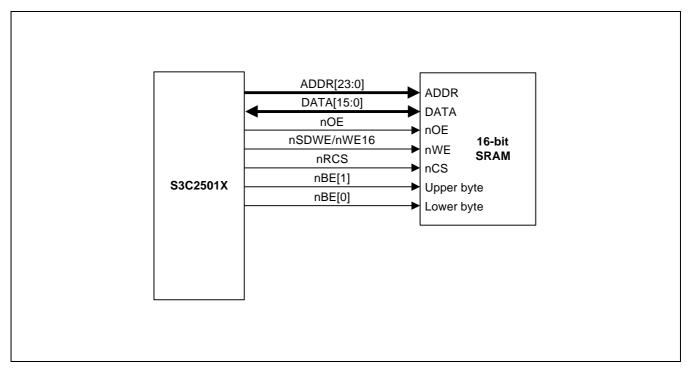

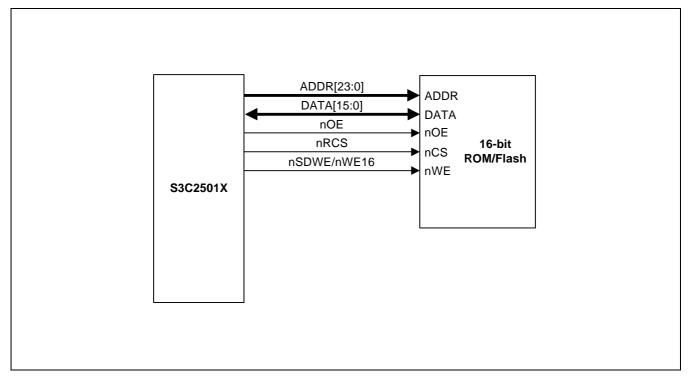

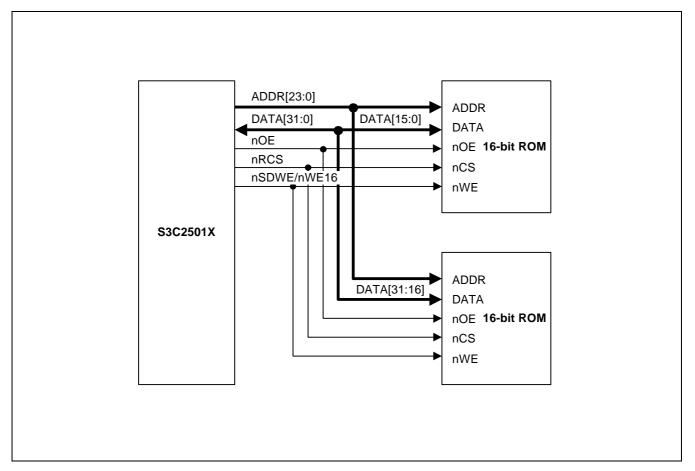

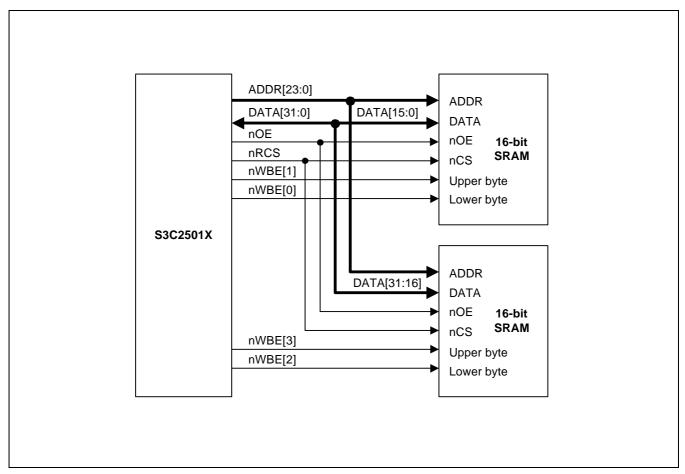

|                  | rnal Device Connection                     |      |

|                  | I/O Bank Controller Special Register       |      |

|                  | ng Diagram                                 |      |

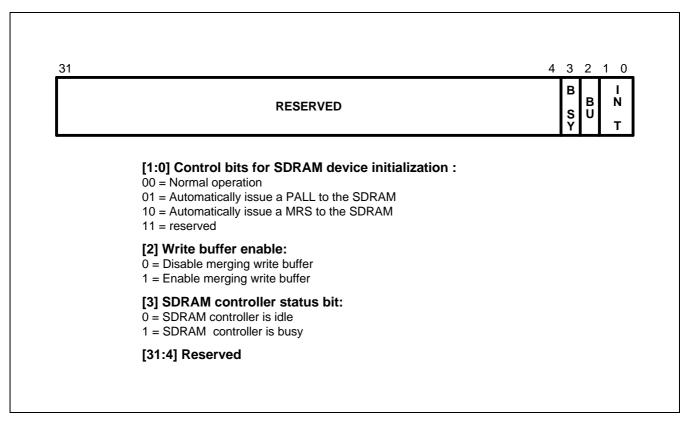

|                  | ntroller                                   |      |

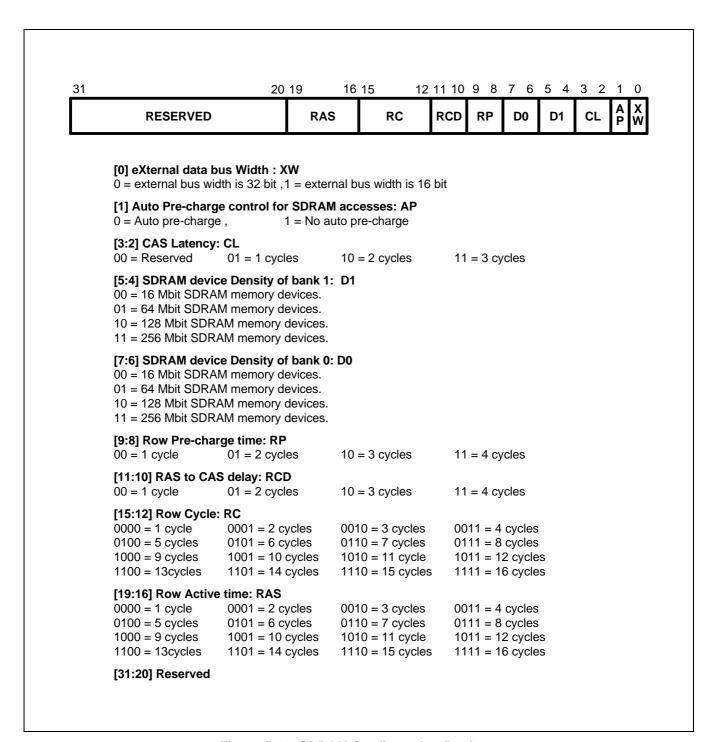

|                  | uresAM Size and Configuration              |      |

|                  | ess Mapping                                |      |

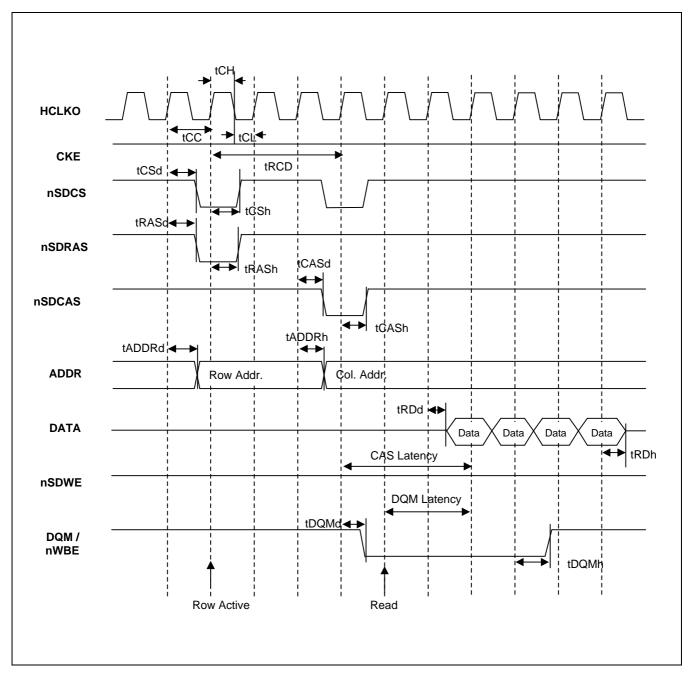

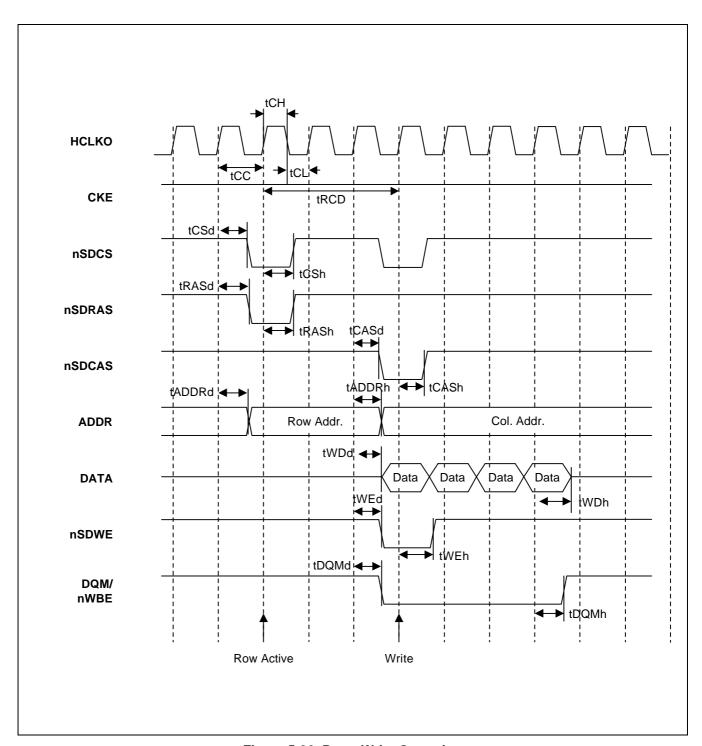

|                  | AM Commands                                |      |

|                  | rnal Data Bus Width                        |      |

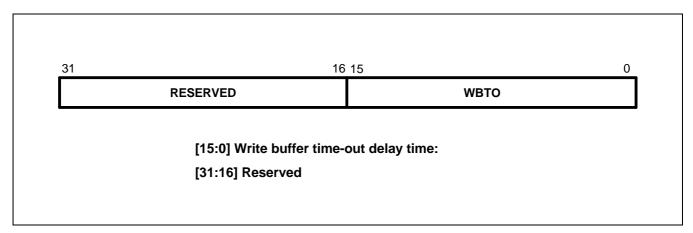

|                  | ging Write Buffer                          |      |

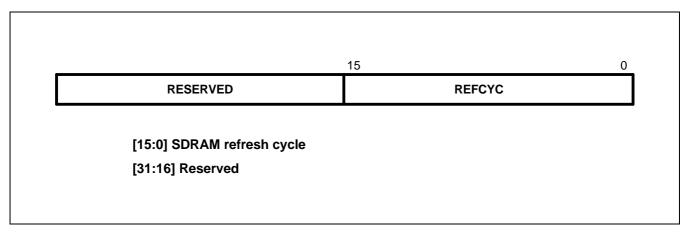

|                  | Refresh                                    |      |

|                  | C Operation                                |      |

| 5.7.0 Dask       |                                            | 5-47 |

viii S3C2501X

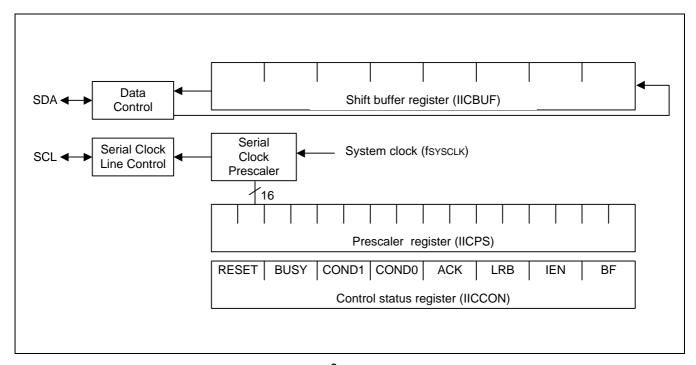

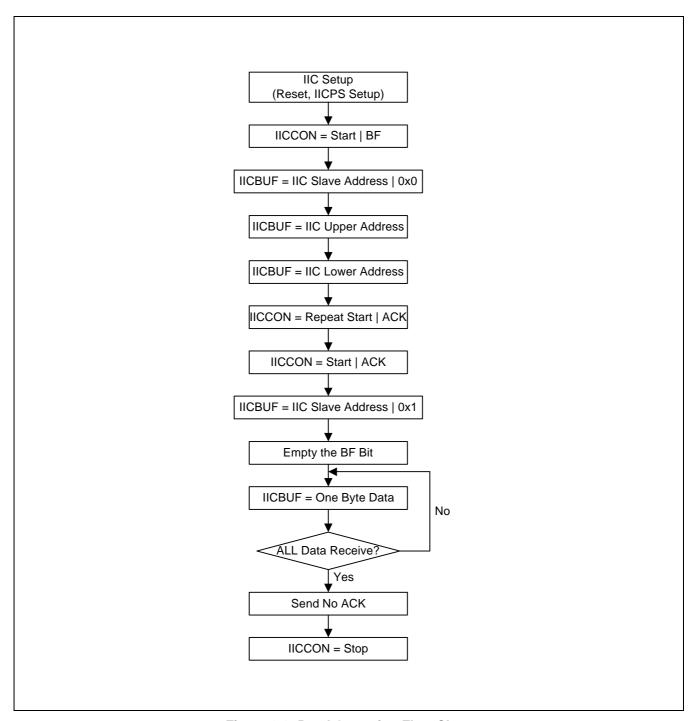

## Chapter 6 I<sup>2</sup>C Bus Controller

| 6.1 Overview                              | 6-1                                                          |

|-------------------------------------------|--------------------------------------------------------------|

| 6.2 Features                              |                                                              |

| 6.3 Functional Description                |                                                              |

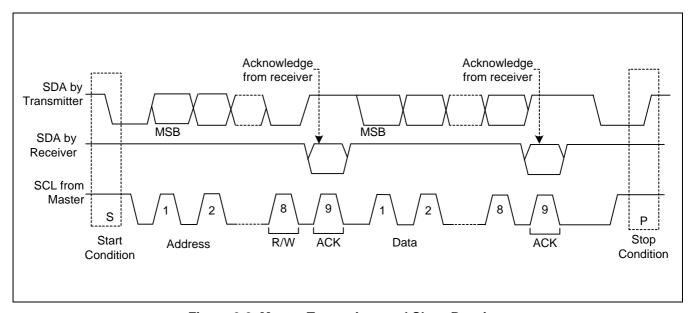

| 6.4 I <sup>2</sup> C Concepts             |                                                              |

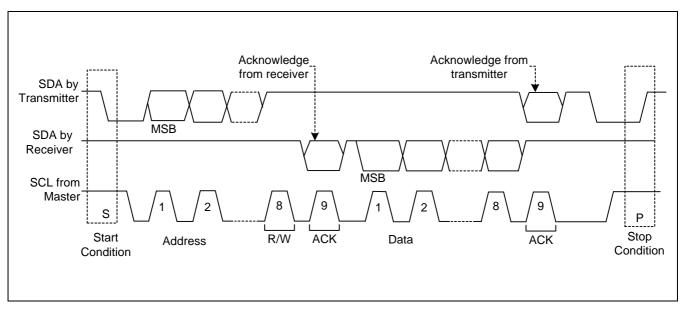

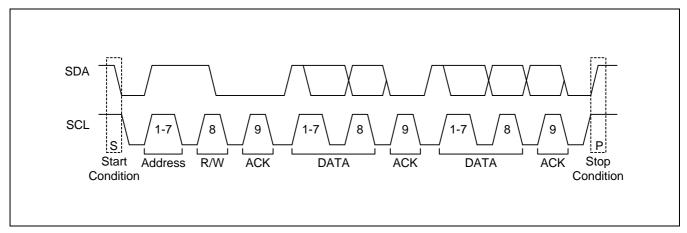

| 6.4.1 Basic Operation                     |                                                              |

| 6.4.2 General Characteristics             |                                                              |

| 6.4.3 Bit Transfers                       |                                                              |

| 6.4.4 Data Validity                       |                                                              |

| 6.4.5 Start and Stop Conditions           |                                                              |

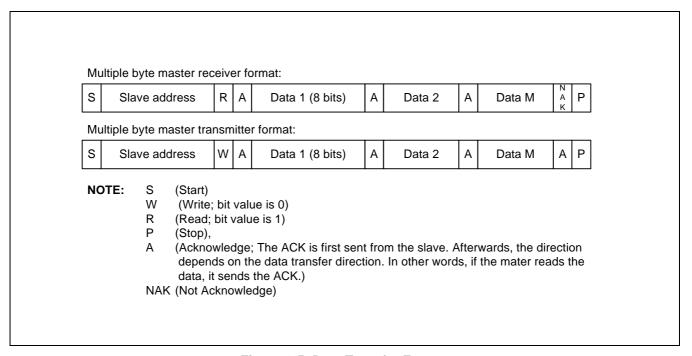

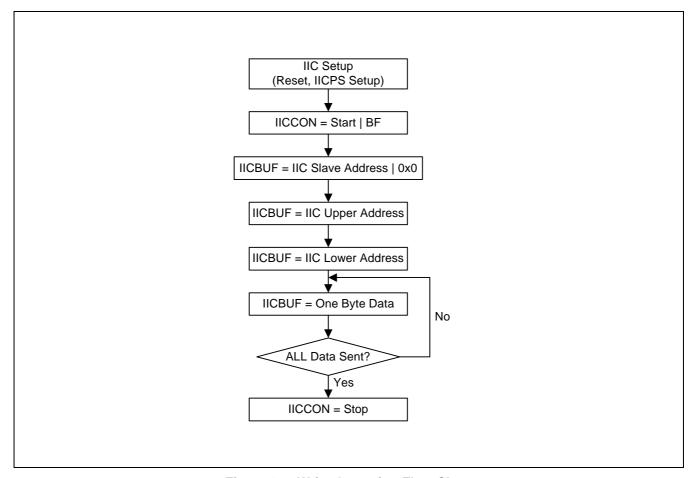

| 6.4.6 Data Transfer Operations            | 6-6                                                          |

| 6.5 I <sup>2</sup> C Special Registers    |                                                              |

| 6.5.1 Control Status Register             |                                                              |

| 6.5.2 Shift Buffer Register               | 6-10                                                         |

| 6.5.3 Prescaler Register                  |                                                              |

| 6.5.4 Prescaler Counter Register          |                                                              |

| 6.5.5 Interrupt Pending Register          |                                                              |

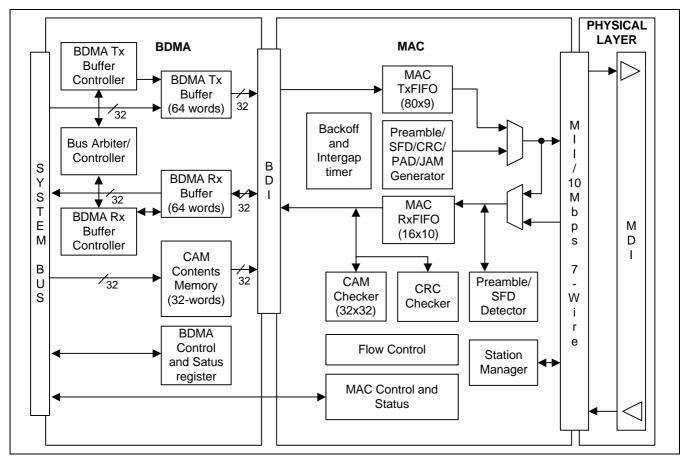

| 7.1 Overview                              | 7-1                                                          |

| 7.1 Overview                              |                                                              |

| 7.3 MAC Function Blocks                   |                                                              |

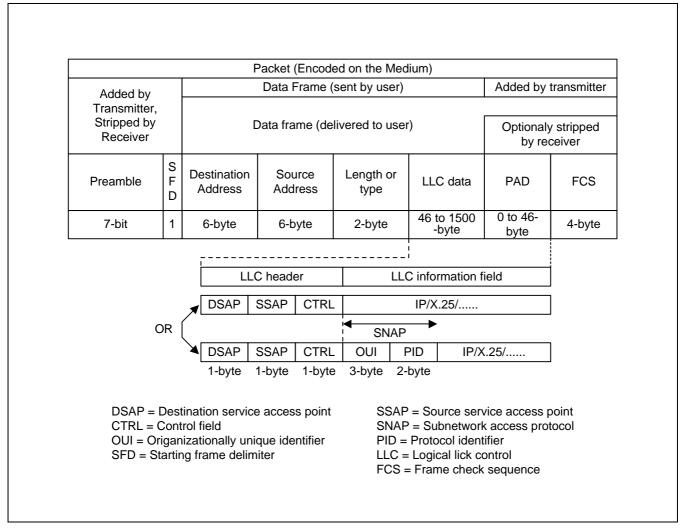

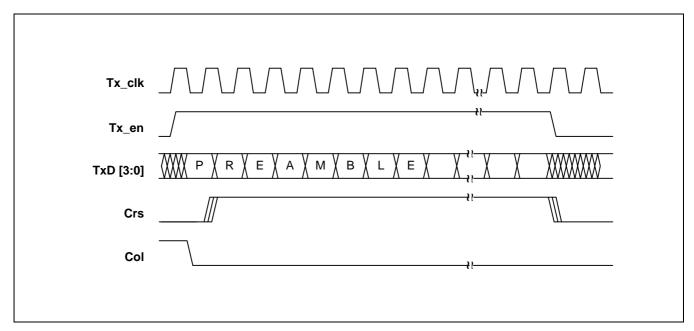

| 7.3.1 Media Independent Interface (MII)   |                                                              |

| 7.3.2 Physical Layer Entity (PHY)         |                                                              |

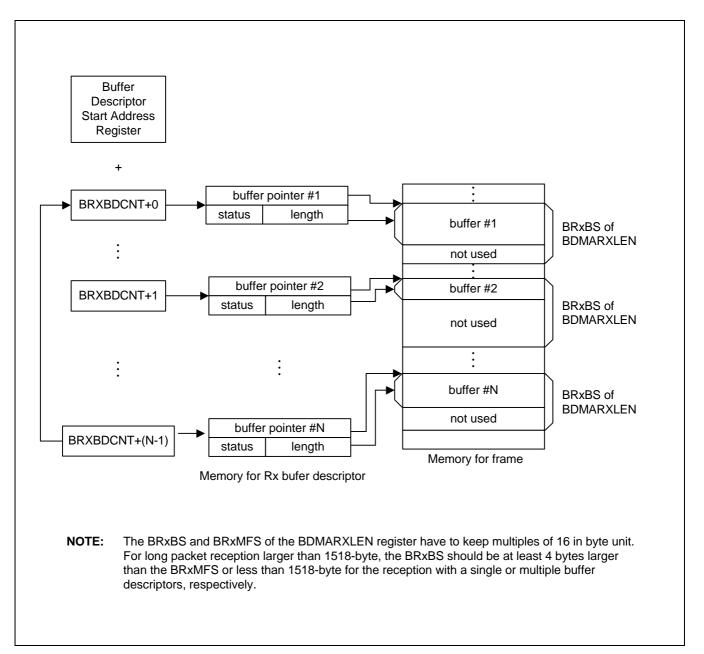

| 7.3.3 Buffered Dma Interface (BDI)        |                                                              |

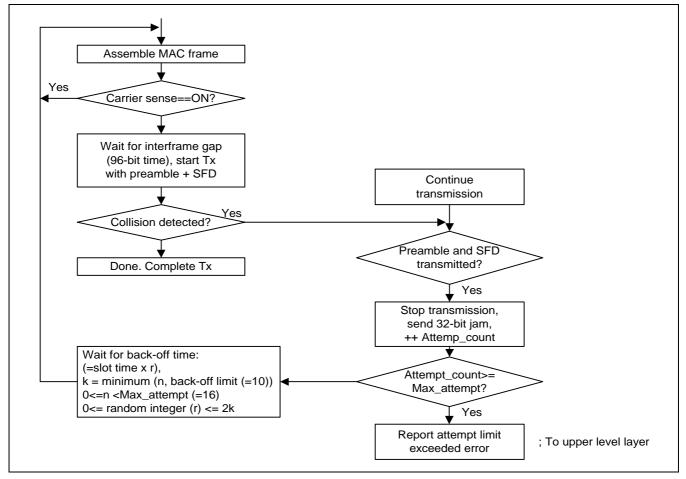

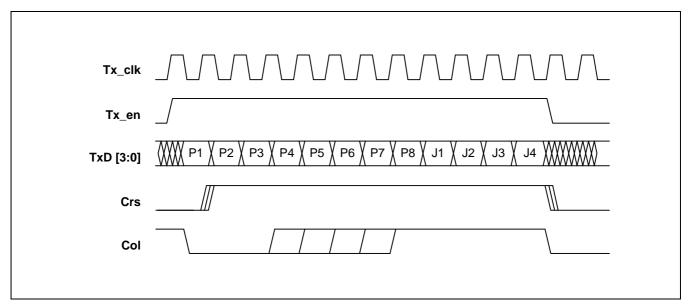

| 7.3.4 The MAC Transmitter Block           |                                                              |

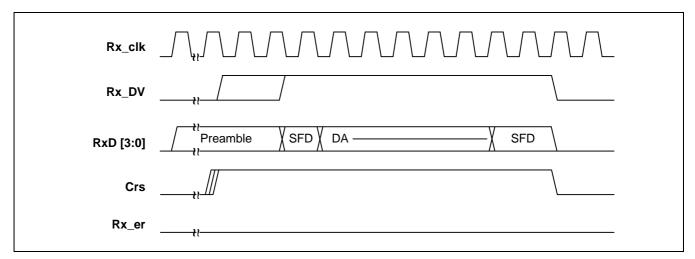

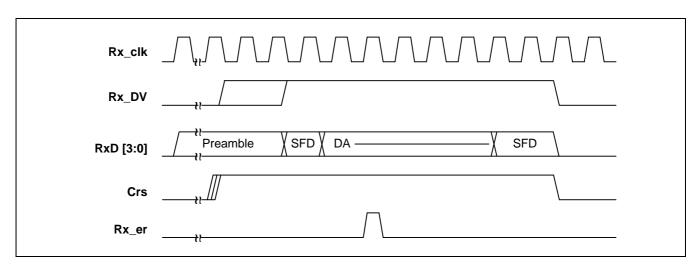

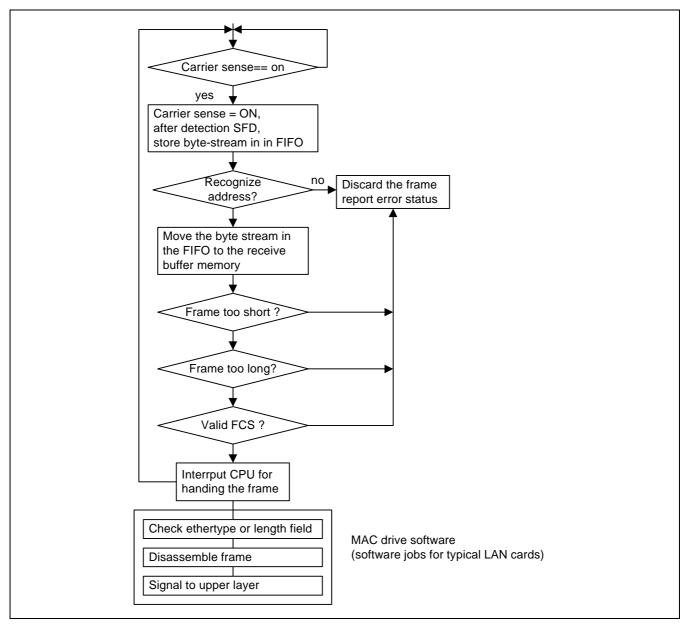

| 7.3.5 The MAC Receiver Block              | 7-4                                                          |

| 7.3.6 Flow Control Block                  | 7-4<br>7-4                                                   |

| 7.3.7 Buffered DMA (BDMA) Overview        |                                                              |

|                                           |                                                              |

|                                           |                                                              |

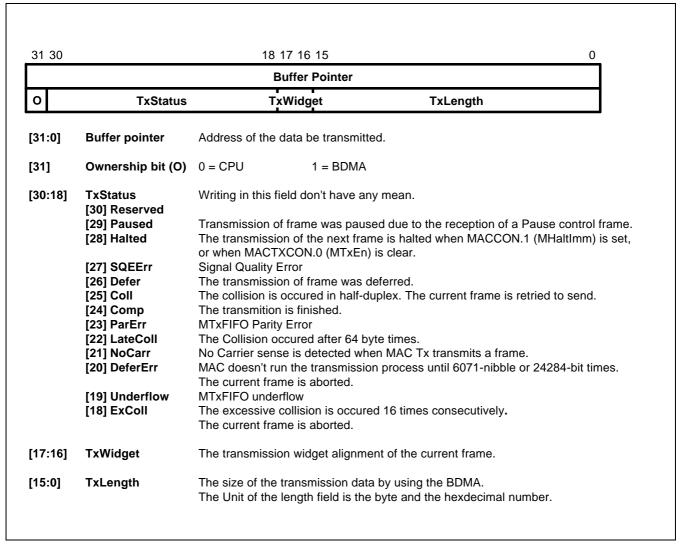

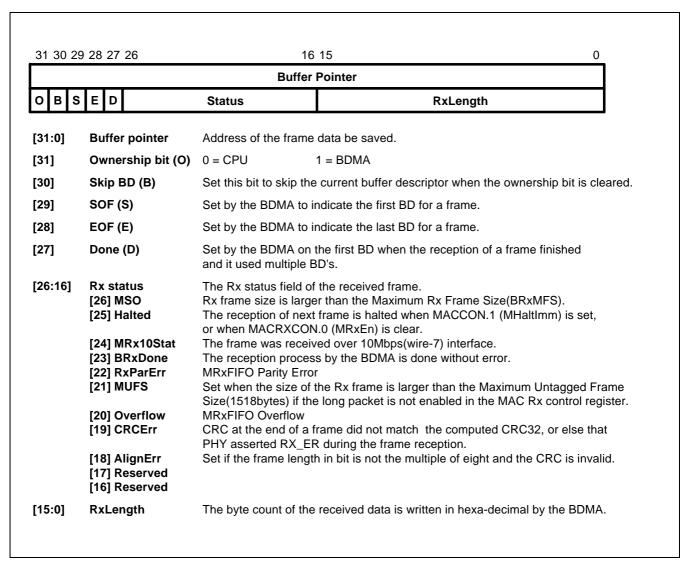

| 7.4 Ethernet Controller Special Registers |                                                              |

| 7.4 Ethernet Controller Special Registers |                                                              |

| 7.4 Ethernet Controller Special Registers | 7-4<br>7-4<br>7-6<br>7-7<br>7-7<br>7-13<br>7-15              |

| 7.4 Ethernet Controller Special Registers | 7-4 7-4 7-6 7-6 7-7 7-7 7-13 7-15 7-24                       |

| 7.4 Ethernet Controller Special Registers | 7-4                                                          |

| 7.4 Ethernet Controller Special Registers | 7-4                                                          |

| 7.4 Ethernet Controller Special Registers | 7-4 7-4 7-4 7-6 7-7 7-7 7-7 7-1 7-15 7-2 7-37 7-37 7-45 7-46 |

S3C2501X ix

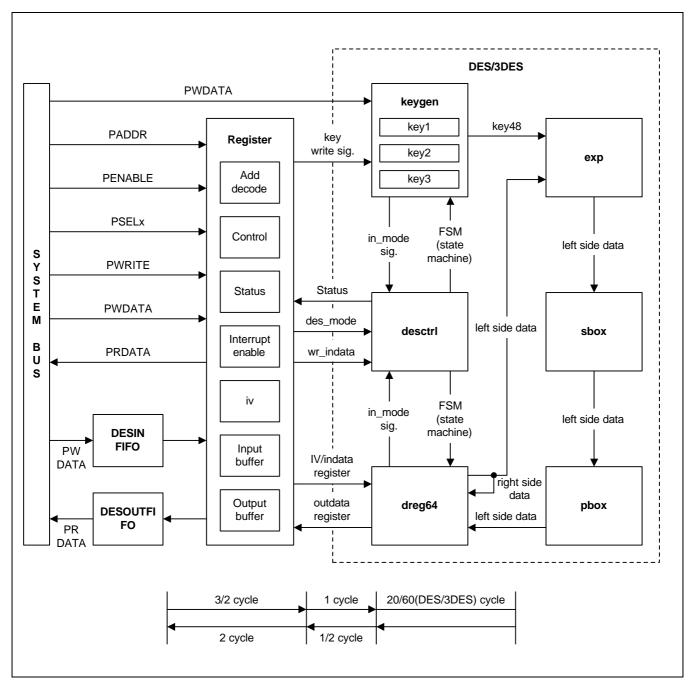

| Chapter 8    | DE9/3DE9 |

|--------------|----------|

| 8.1 Overview |          |

|   | 8.1 Overview                                    | 8-1  |

|---|-------------------------------------------------|------|

|   | 8.2 Feature                                     |      |

|   | 8.3 DES/3DES Special Registers                  |      |

|   | 8.3.1 DES/3DES Control Register                 |      |

|   | 8.3.2 DES/3DES Status Register                  |      |

|   | 8.3.3 DES/3DES Interrupt Enable Register        | 8-6  |

|   | 8.3.4 DES/3DES Run Enable Register              |      |

|   | 8.3.5 DES/3DES Key1 Left/Right Side Register    | 8-6  |

|   | 8.3.6 DES/3DES Key 2 Left/Right Side Register   | 8-7  |

|   | 8.3.7 DES/3DES Key 3 Left Side Register         |      |

|   | 8.3.8 DES/3DES IV Left/Right Side Register      | 8-7  |

|   | 8.3.9 DES/3DES Input/Output Data FIFO Register  | 8-8  |

|   | 8.4 DES/3DES Operation                          | 8-9  |

|   | 8.5 Performance Calculation Guide               | 8-10 |

|   |                                                 |      |

| _ | Showton O. ODMA Controller                      |      |

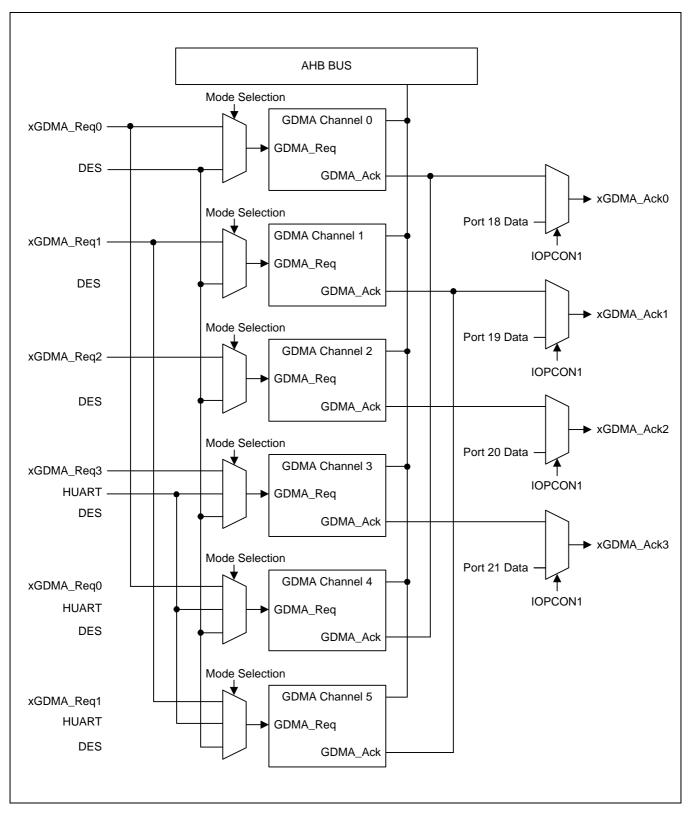

| J | hapter 9 GDMA Controller                        |      |

|   | 9.1 Overview                                    | 9-1  |

|   | 9.2 Feature                                     |      |

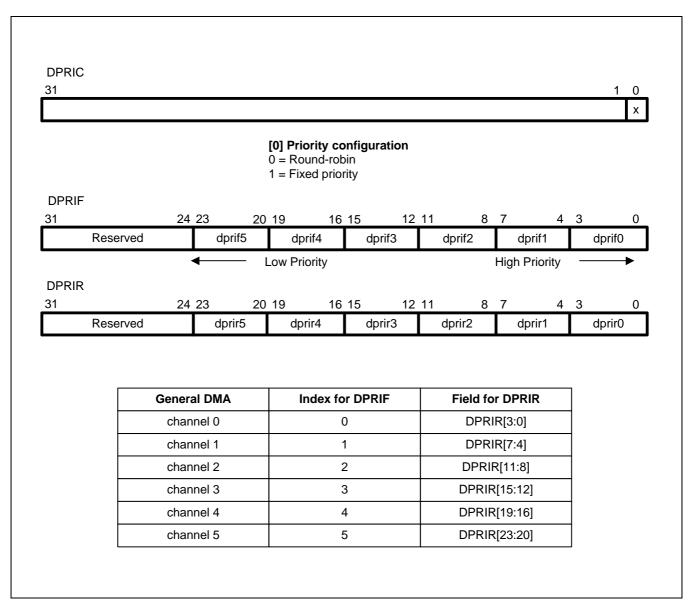

|   | 9.3 GDMA Special Registers                      | 9-3  |

|   | 9.3.1 GDMA Programmable Priority Registers      |      |

|   | 9.3.2 GDMA Control Registers                    |      |

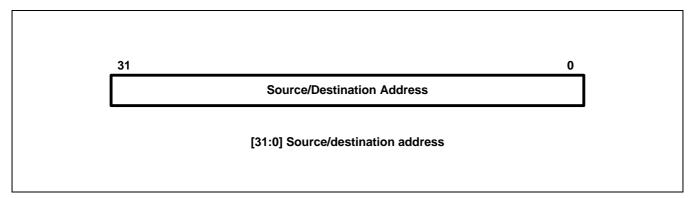

|   | 9.3.3 GDMA Source/Destination Address Registers |      |

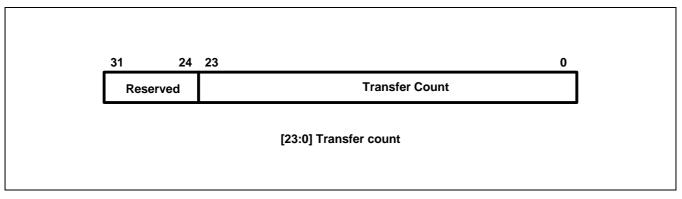

|   | 9.3.4 GDMA Transfer Count Registers             |      |

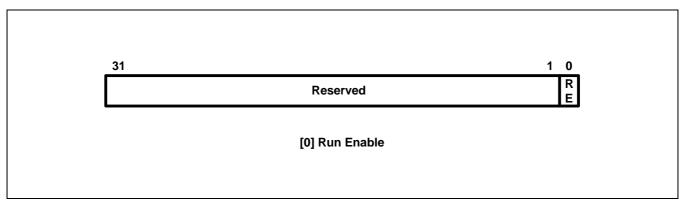

|   | 9.3.5 GDMA Run Enable Registers                 |      |

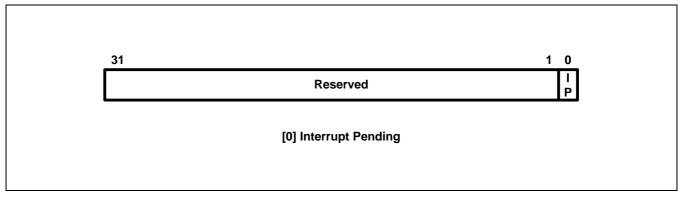

|   | 9.3.6 GDMA Interrupt Pending Register           |      |

|   | 9.4 GDMA Mode Operation                         |      |

|   | 9.4.1 Software Mode                             |      |

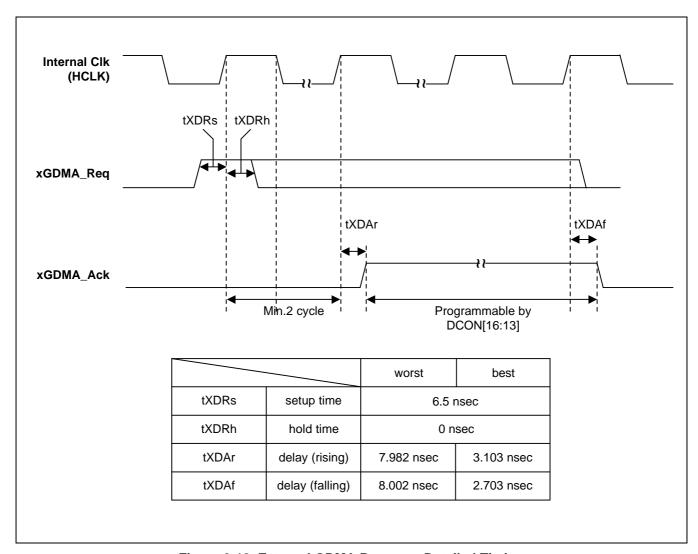

|   | 9.4.2 External GDMA Request Mode                | 9-16 |

|   | 9.4.3 HUART Mode                                | 9-16 |

|   | 9.4.4 DES Mode                                  |      |

|   | 9.5 GDMA Function Description                   | 9-17 |

|   | 9.5.1 GDMA Transfers                            |      |

|   | 9.5.2 Starting/Ending GDMA Transfers            | 9-17 |

|   | 9.5.3 Data Transfer Modes                       |      |

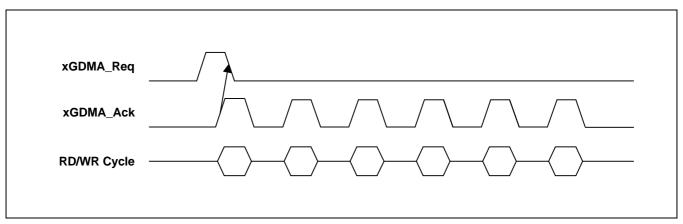

|   | 9.6 GDMA Transfer Timing Data                   |      |

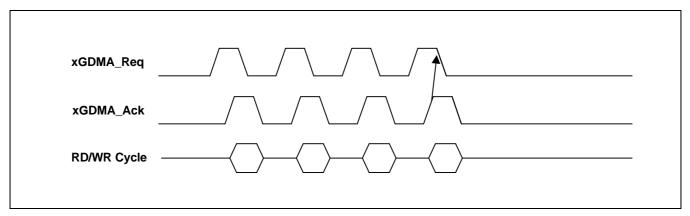

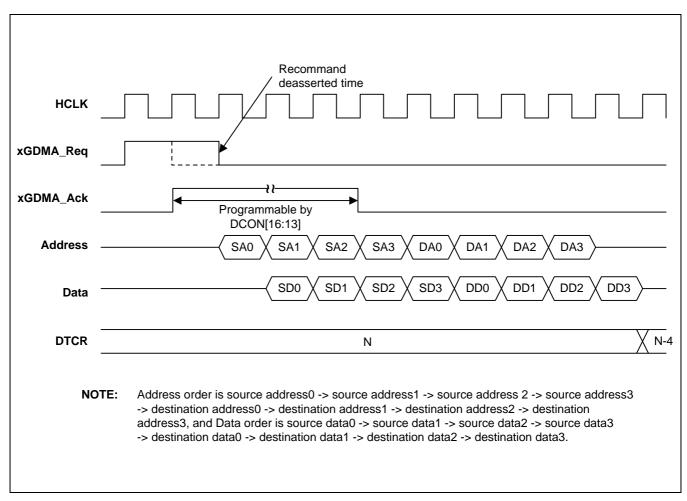

|   | 9.6.1 Single and One Data Burst Mode            |      |

|   | 9.6.2 Single and Four Data Burst Mode           |      |

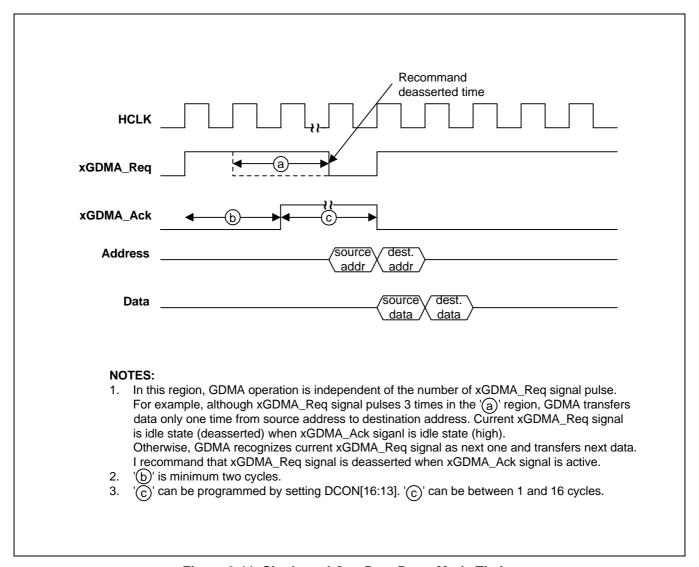

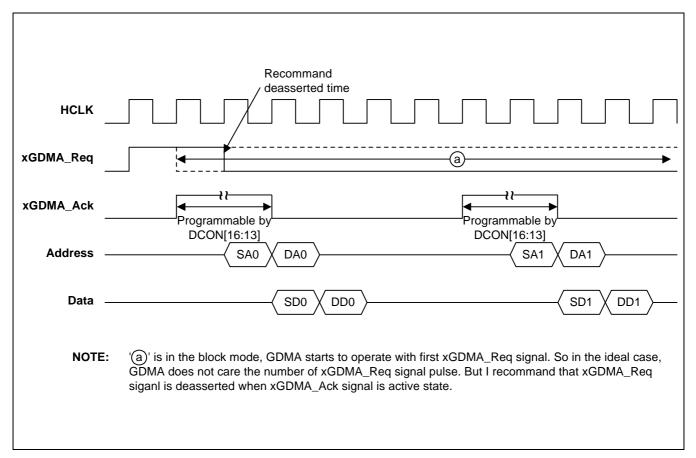

|   | 9.6.3 Block and One Data Burst Mode             |      |

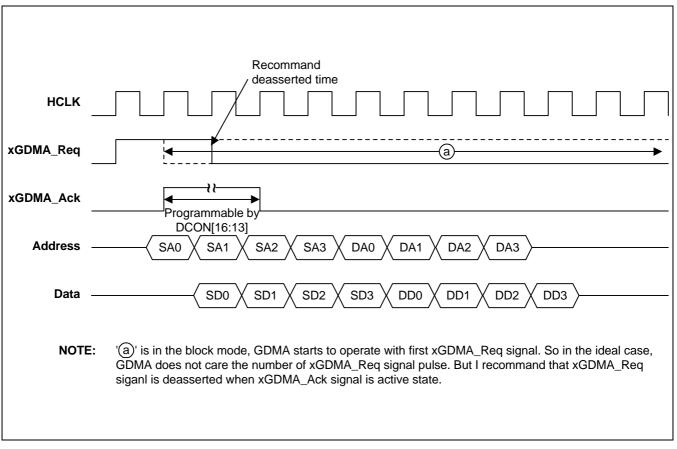

|   | 9.6.4 Block and Four Data Burst                 |      |

|   |                                                 |      |

x S3C2501X

## Chapter 10 Serial I/O (Console UART)

| 10.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10-1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 10.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10-1  |

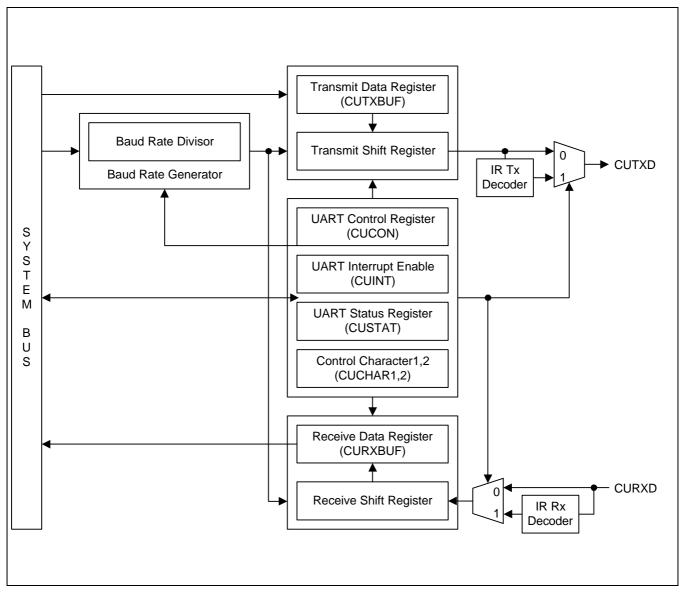

| 10.3 Console UART Special Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10-3  |

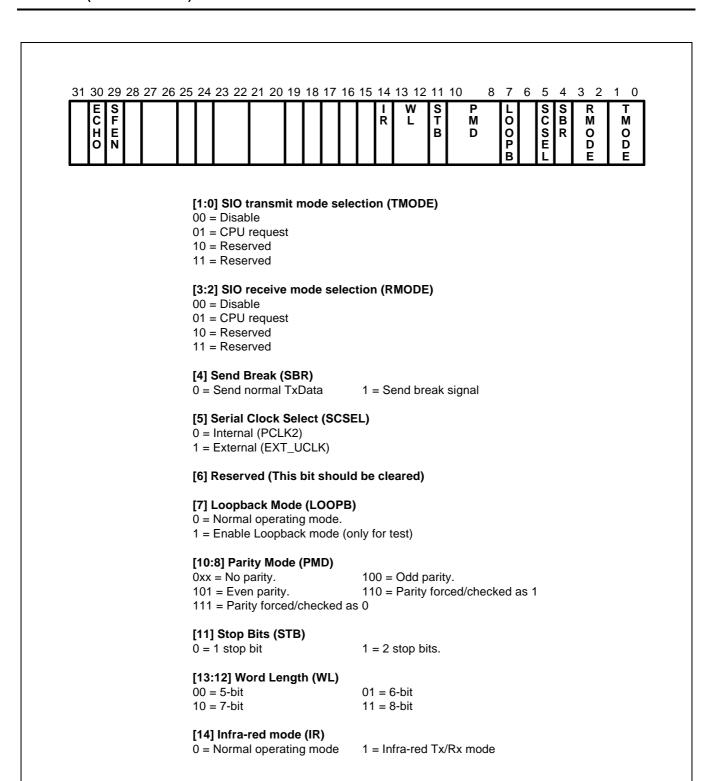

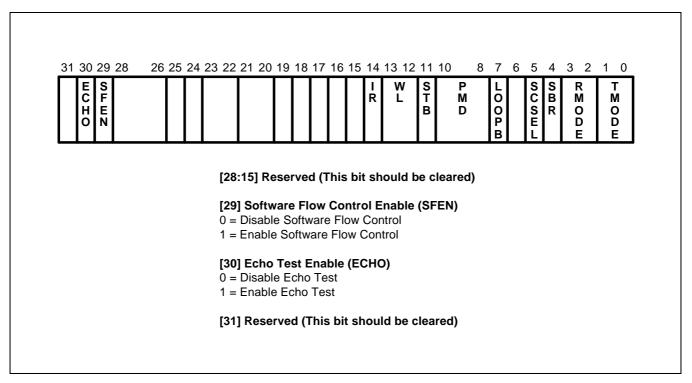

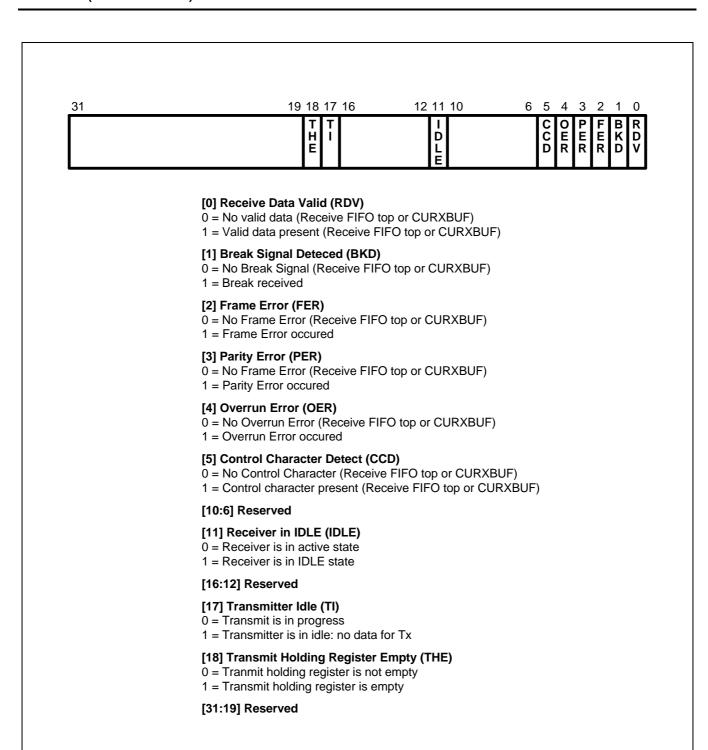

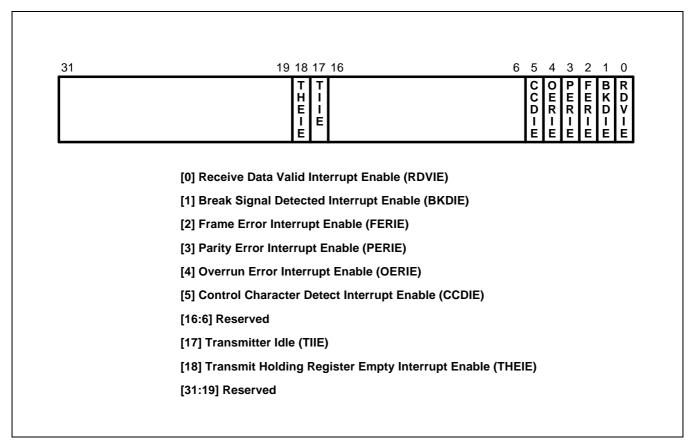

| 10.3.1 Console UART Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10-4  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

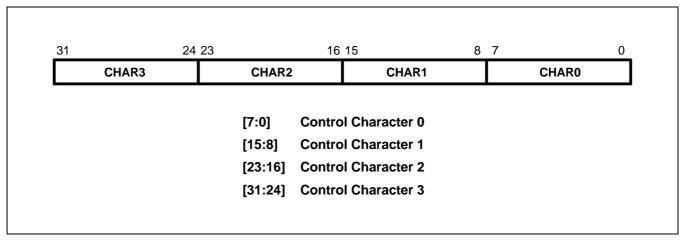

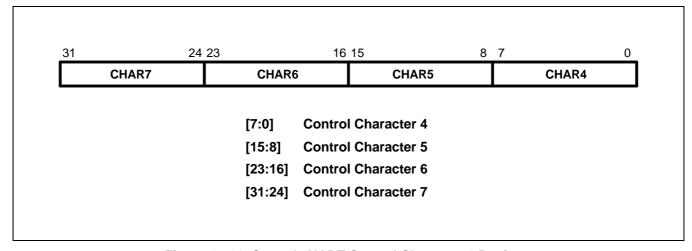

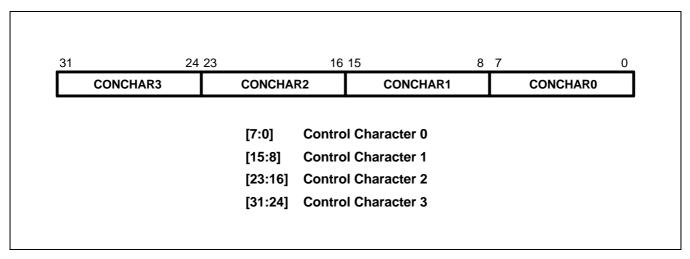

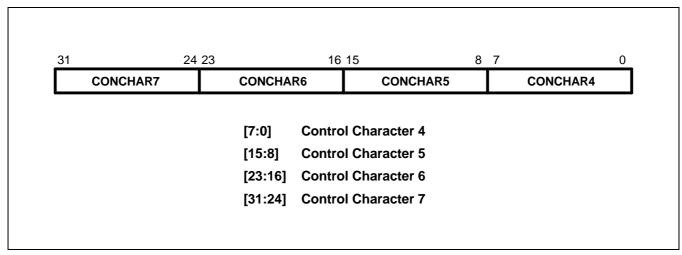

| 10.3.8 UART Control Character Register 1 and 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10-17 |

| Chapter 11Serial I/O (High-Speed UART)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 11.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

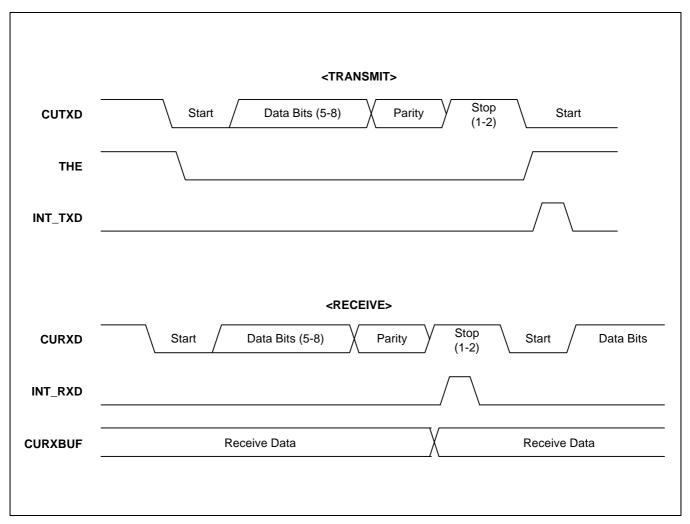

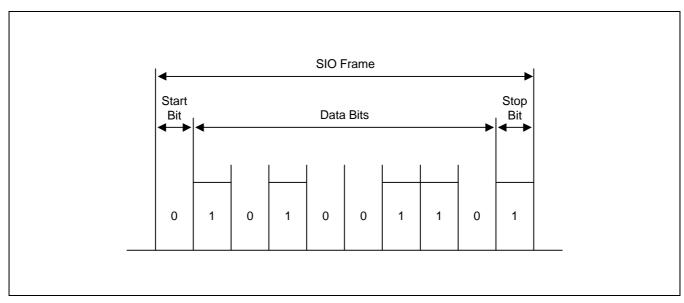

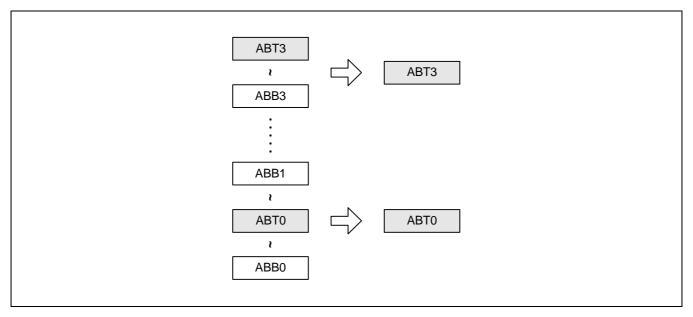

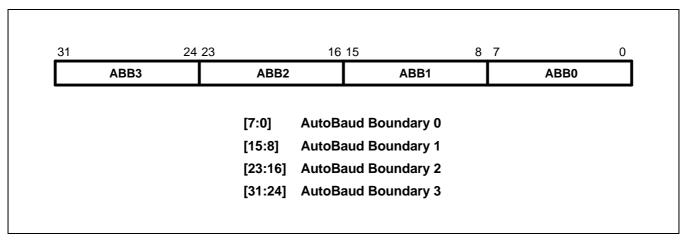

| 10.2 Features 10.3 Console UART Special Registers 10.3.1 Console UART Status Registers 10.3.2 Console UART Status Registers 10.3.3 Console UART Interrupt Enable Register 10.3.5 UART Receive Data Register 10.3.5 UART Receive Data Register 10.3.6 UART Baud Rate Divisor Register 10.3.8 UART Control Character Register 10.3.8 UART Control Character Register 1 and 2  Chapter 11 Serial I/O (High-Speed UART)  11.1 Overview 11.2 Features 11.3 High-Speed UART Special Registers 11.3.1 High-Speed UART Status Registers 11.3.2 High-Speed UART Status Registers 11.3.3 High-Speed UART Interrupt Enable Register 11.3.4 High-Speed UART Receive Buffer Register 11.3.5 High-Speed UART Receive Buffer Register 11.3.6 High-Speed UART Baud Rate Divisor Register 11.3.7 High-Speed UART Baud Rate Divisor Register 11.3.8 High-Speed UART Baud Rate Divisor Register 11.3.9 High-Speed UART Control Character 1 Register 11.3.9 High-Speed UART Control Character 1 Register 11.3.10 High-Speed UART Autoband Boundary Register 11.3.10 High-Speed UART Autoband Boundary Register 11.3.11 High-Speed UART Optrol Character 2 Register 11.3.11 High-Speed UART Optrol Character 1 Register 11.3.11 High-Speed UART Optrol Character 2 Register 11.3.11 High-Speed UART Optrol Character 1 Register 11.4.1 FIFO Operation 11.4.2 Hardware Flow Control 11.4.3 Software Flow Control 11.4.4 Auto Baud Rate Detection. |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |