#### SN54AS181A, SN54AS881A, SN74AS181A, SN74AS881A ARITHMETIC LOGIC UNITS/FUNCTION GENERATORS

D2661, DECEMBER 1982-REVISED MAY 1986

- Package Options Include the 'AS181A in Compact 300-mil or Standard 600-mil Packages. The 'AS881A is Offered in 300-mil Packages. Both Devices are Available in Both Plastic and Ceramic Chip Carriers.

- Full Look-Ahead for High-Speed Operations on Long Words

- Arithmetic Operating Modes:

Addition

Subtraction

Shift Operand A One Position

Magnitude Comparison

Plus Twelve Other Arithmetic Operations

- Logic Function Modes

Exclusive-OR

Comparator

AND, NAND, OR, NOR

'AS881A Provides Status Register Checks

Plus Ten Other Logic Operations

- Dependable Texas Instruments Quality and Reliability

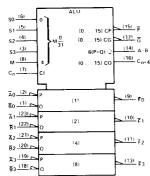

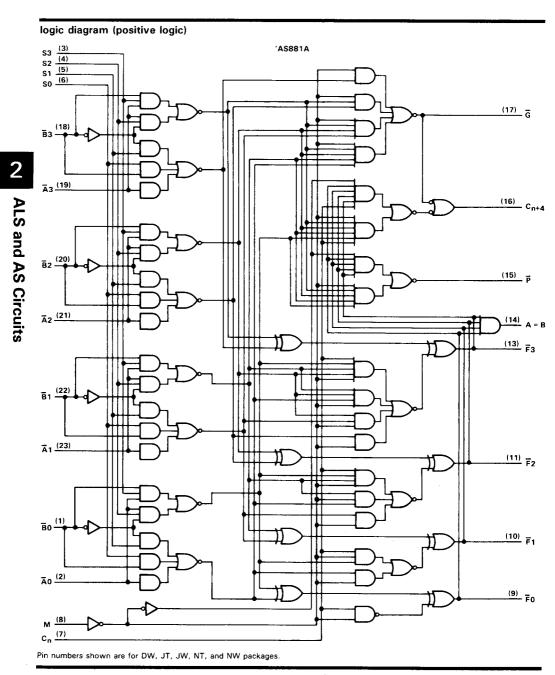

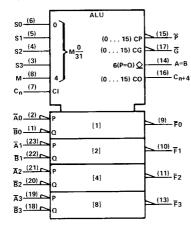

#### logic symbol<sup>†</sup>

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for DW, JT, JW, NT, and NW packages.

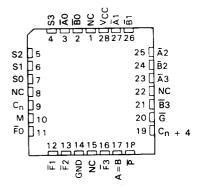

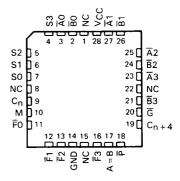

SN54AS181A . . . JT OR JW PACKAGE SN54AS881A . . . JT PACKAGE SN74AS181A . . . DW, NT OR NW PACKAGE SN74AS881A . . . DW OR NT PACKAGE (TOP VIEW)

| Ē0 □             | 1  | <b>J24</b> | ∐∨cc           |

|------------------|----|------------|----------------|

| Ā0 [             | 2  | 23         | ∏Ā1            |

| S3 [             | 3  | 22         | ∏Ē1            |

| S2 [             | 4  | 21         | ∏Ã2            |

| S1 [             | 5  | 20         | ∏Ē2            |

| so [             | 6  | 19         | ∏Ã3            |

| C <sub>n</sub> [ | 7  | 18         | ∏Вз            |

| М [              | 8  | 17         | ∏Ġ             |

| FO [             | 9  | 16         | $\Box C_{n+4}$ |

| Ŧ1 [             | 10 | 15         | ΡĒ             |

| F2 [             | 11 | 14         | □ A = B        |

| GND              | 12 | 13         | F3             |

SN54AS181A, SN54AS881A . . . FK PACKAGE SN74AS181A, SN74AS881A . . . FN PACKAGE (TOP VIEW)

NC-No internal connection

| TYPICAL ADDITION TIMES (CL = | 15 pF, $R_L = 280 \Omega$ , $T_A = 25^{\circ}C$ ) |

|------------------------------|---------------------------------------------------|

| DITION TIMES                 | PACKAGE COUNT                                     |

| NUMBER     | A                          | DDITION TIMES               |                          | PACK                      | AGE COUNT                      | CARRY METHOD    |

|------------|----------------------------|-----------------------------|--------------------------|---------------------------|--------------------------------|-----------------|

| OF<br>BITS | USING 'AS881A<br>AND'AS882 | USING 'AS181A<br>AND 'AS882 | USING 'S181<br>AND 'S182 | ARITHMETIC<br>LOGIC UNITS | LOOK-AHEAD<br>CARRY GENERATORS | BETWEEN<br>ALUs |

| 1 to 4     | 5 ns                       | 5 ns                        | 11 ns                    | 1                         |                                | NONE            |

| 5 to 8     | 10 ns                      | 10 ns                       | 18 ns                    | 2                         |                                | RIPPLE          |

| 9 to 16    | 14 ns                      | 14 ns                       | 19 ns                    | 3 or 4                    | 1                              | FULL LOOK-AHEAD |

| 17 to 64   | 19 ns                      | 19 ns                       | 28 ns                    | 5 to 16                   | 2 to 5                         | FULL LOOK-AHEAD |

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Taxas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1982, Texas Instruments Incorporated

description

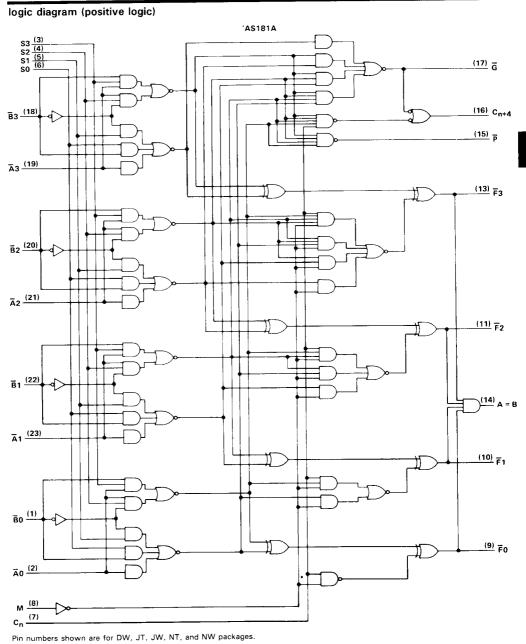

# The 'AS181A and 'AS881A are arithmetic logic units (ALU)/function generators that have a complexity of 75 and 77 equivalent gates, respectively, on a monolithic chip. These circuits perform 16 binary arithmetic operations on two 4-bit words as shown in Tables 1 and 2. These operations are selected by the four function-select lines (S0, S1, S2, S3) and include addition, subtraction, decrement, and straight transfer. When performing arithmetic manipulations, the internal carries must be enabled by applying a low-level voltage to the mode control input (M). A full carry look-ahead scheme is made available in these devices

When performing arithmetic manipulations, the internal carries must be enabled by applying a low-level voltage to the mode control input (M). A full carry look-ahead scheme is made available in these devices for fast, simultaneous carry generation by means of two cascade-outputs (pins 15 and 17) for the four bits in the package. When used in conjunction with the SN54AS882 or SN74AS882 full carry look-ahead circuits, high-speed arithmetic operations can be performed. The typical addition times shown previously illustrate the little additional time required for addition of longer words when full carry look-ahead is employed. The method of cascading 'AS882 circuits with these ALUs to provide multilevel full carry look-ahead is illustrated under signal designations.

If high speed is not of importance, a ripple-carry input  $(C_n)$  and a ripple-carry output  $(C_n+4)$  are available. However, the ripple-carry delay has also been minimized so that arithmetic manipulations for small word lengths can be performed without external circuitry.

The 'AS181A and 'AS881A will accommodate active-high or active-low data if the pin designations are interpreted as follows:

| PIN NUMBER                 | 2  | 1  | 23 | 22 | 21 | 20 | 19 | 18 | 9  | 10 | 11 | 13 | 7  | 16     | 15 | 17 |

|----------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|----|----|

| Active-low data (Table 1)  | ÃO | ВO | Ã1 | B1 | Ā2 | B2 | Ā3 | B3 | FO | F1 | F2 | Ē3 | Cn | Cn + 4 | P  | Ğ  |

| Active-high data (Table 2) | AO | во | A1 | B1 | A2 | B2 | А3 | В3 | FO | F1 | F2 | F3 | Čn | Cn+4   | х  | Υ  |

Subtraction is accomplished by 1's complement addition where the 1's complement of the subtrahend is generated internally. The resultant output is A-B-1, which requires an end-around or forced carry to provide A-B.

The 'AS181A and 'AS881A can also be utilized as a comparator. The A = B output is internally decoded from the function outputs (F0, F1, F2, F3) so that when two words of equal magnitude are applied at the A and B inputs, it will assume a high level to indicate equality (A = B). The ALU must be in the subtract mode with  $C_n$  = H when performing this comparison. The A = B output is open-collector so that it can be wire-AND connected to give a comparison for more than four bits. The carry output ( $C_{n+4}$ ) can also be used to supply relative magnitude information. Again, the ALU must be placed in the subtract mode by placing the function select input S3, S2, S1, S0 at L, H, H, L, respectively.

| INPUT Cn | OUTPUT C <sub>n+4</sub> | ACTIVE-LOW DATA<br>(FIGURE 1) | ACTIVE-HIGH DATA<br>(FIGURE 2) |

|----------|-------------------------|-------------------------------|--------------------------------|

| Н        | н                       | A ≥ B                         | A ≤ B                          |

| Н        | L                       | A < B                         | A > B                          |

| L        | Н                       | A > B                         | A < B                          |

| L        | L                       | A ≤ B                         | A≥B                            |

These circuits have been designed to not only incorporate all of the designer's requirements for arithmetic operations, but also to provide 16 possible functions of two Boolean variables without the use of external circuitry. These logic functions are selected by use of the four function-select inputs (S0, S1, S2, S3) with the mode-control input (M) at a high level to disable the internal carry. The 16 logic functions are detailed in Tables 1 and 2 and include exclusive-OR, NAND, AND, NOR, and OR functions.

#### description (continued)

The 'AS881A has the same pinout and same functionality as the 'AS181A except for the  $\overline{P}$ ,  $\overline{G}$ , and  $C_{n+4}$  outputs when the device is in the logic mode (M = H).

In the logic mode the 'AS881A provides the user with a status check on the input words A and B, and the ouput word F. While in the logic mode the  $\overline{P}$ ,  $\overline{G}$ , and  $C_{n+4}$  outputs supply status information based upon the following logical combinations:

$$\overline{P} = FO + F1 + F2 + F3$$

$\overline{G} = H$

$C_{n+4} = PC_n$

#### FUNCTION TABLE FOR INPUT BITS EQUAL/NOT EQUAL

#### FUNCTION TABLE FOR INPUT PAIRS HIGH/NOT HIGH

S0=S3=H, S1=S2=L, and M=H

|    |         |                                 |                                 |                                 | 0 | UTF | PUTS   |

|----|---------|---------------------------------|---------------------------------|---------------------------------|---|-----|--------|

| Cn |         | DATA                            | INPUTS                          |                                 | Ğ | P   | Cn + 4 |

| н  | Ā0 = B0 | $\overline{A}1 = \overline{B}1$ | A2 = B2                         | $\overline{A}3 = \overline{B}3$ | Н | L   | н      |

| L  | A0 = 80 | $\overline{A}1 = \overline{B}1$ | $\overline{A}2 = \overline{B}2$ | $\overline{A}3 = \overline{B}3$ | н | L   | L      |

| ×  | Ã0 ≠ BO | ×                               | X                               | X                               | н | Н   | L      |

| x  | x       | Ā1≠B1                           | Х                               | Х                               | н | Н   | L      |

| ×  | ×       | X                               | Ā2≠ <u>B</u> 2                  | X                               | Н | н   | L      |

| ×  | ×       | ×                               | X                               | A3≠B3                           | н | Н   | L      |

|   |    |                                          | S0 - S1 - S3 - L                       | , S2 = H, and M                        | <b>-</b> H                             |   |     |        |

|---|----|------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|---|-----|--------|

| ſ |    |                                          |                                        |                                        |                                        |   | DUT | PUTS   |

| 1 | Cn |                                          | DATA                                   | INPUTS                                 |                                        | Ğ | P   | Cn + 4 |

| İ | н  | AO or BO = L                             | Ā1 or B1 = L                           | Ã2 or B2 = L                           | $\overline{A}3$ or $\overline{B}3 = L$ | Τ | L   | н      |

| - | į. | $\overline{A}$ 0 or $\overline{B}$ 0 = L | $\overline{A}1$ or $\overline{B}1 = L$ | $\overline{A}2$ or $\overline{B}2 = L$ | $\overline{A}3$ or $\overline{B}3 = L$ | н | L   | L      |

| - | Х  | $\overline{A}O = \overline{B}O = H$      | ×                                      | x                                      | ×                                      | н | Н   | L      |

| 1 | х  | ×                                        | $\overline{A}1 = \overline{B}1 = H$    | ×                                      | ×                                      | н | Н   | L      |

|   | X  | ×                                        | ×                                      | $\overline{A}2 = \overline{B}2 = H$    | ×                                      | Н | Н   | L      |

|   | X  | ×                                        | ×                                      | ×                                      | $\overline{A}3 = \overline{B}3 = H$    | н | Н   | L      |

The combination of signals on the S3 through S0 control lines determine the operation performed on the data words to generate the output bits  $\overline{F}i$ . By monitoring the  $\overline{P}$  and  $C_{n+4}$  outputs, the user can determine if all pairs of input bits are equal (see table above) or if any pair of inputs are both high (see table above). The 'AS881A has the unique feature of providing an A=B status while the exclusive-OR( $\bigoplus$ ) function is being utilized. When the control inputs (S3, S2, S1, S0) equal H, L, L, H; a status check is generated to determine whether all pairs ( $\overline{A}i$ ,  $\overline{B}i$ ) are equal in the following manner:  $\overline{P}=(A0\bigoplus B0)+(A1\bigoplus B1)+(A2\bigoplus B2)+(A3\bigoplus B3)$ . This unique bit-by-bit comparison of the data words, which is available on the totem-pole  $\overline{P}$  output, is particularly useful when cascading 'AS881s. As the A=B condition is sensed in the first stage, the signal is propagated through the same ports used for carry generation in the arithmetic mode ( $\overline{P}$  and  $\overline{G}$ ). Thus the A=B status is transmitted to the second stage more quickly without the need for external multiplexing logic. The A=B open-collector output allows the user to check the validity of the bit-by-bit result by comparing the two signals for parity.

If the user wishes to check for any pair of data inputs  $(\overline{A}i, \overline{B}i)$  being high, it is necessary to set the control lines (S3,S2,S1,S0) to L, H, L, L. The data pairs will then be ANDed together and the results ORed in the following manner:  $\overline{P} = \overline{A}0\overline{B}0 + \overline{A}1\overline{B}1 + \overline{A}2\overline{B}2 + \overline{A}3\overline{B}3$ .

|   | S3 | S2 | S1 | so | М | $\overline{P} = F0 + F1 + F2 + F3$                                                |

|---|----|----|----|----|---|-----------------------------------------------------------------------------------|

| Ì | L  | H  | L  | L  | Η | Ã0B0 + Ā1B1 + Ā2B2 + Ā3B3                                                         |

| ı | н  | L  | L  | Τ  | Η | (AO \( \phi \) BO) + (A1 \( \phi \) B1) + (A2 \( \phi \) B2) + (A3 \( \phi \) B3) |

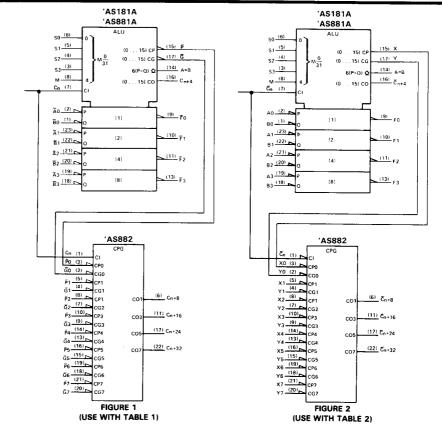

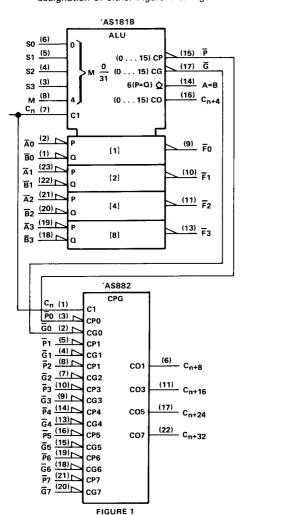

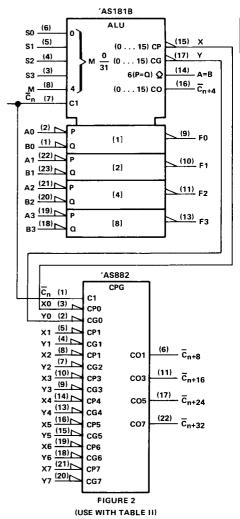

#### signal designations

In both Figures 1 and 2, the polarity indicators ( ) indicate that the associated input or output is active-low with respect to the function shown inside the symbol and the symbols are the same in both figures. The signal designations in Figure 1 agree with the indicated internal functions based on active-low data, and are for use with the logic functions and arithmetic operations shown in Table 1. The signal designations have been changed in Figure 2 to accommodate the logic functions and arithmetic operations for the active-high data given in Table 2. The 'AS181A and 'AS881A together with 'AS882 and 'S182 can be used with the signal designation of either Figure 1 or Figure 2.

TABLE 1

| c  | ELE: | CTIC | 181 |           | ACTIVE-LOW             | DATA                      |

|----|------|------|-----|-----------|------------------------|---------------------------|

| 3  | ELE: | LIIC | ,,, | M = H     | M = L; ARITHM          | ETIC OPERATIONS           |

| 63 | S2   | C1   | ۰۵  | LOGIC     | C <sub>n</sub> = L     | C <sub>n</sub> = H        |

| 33 | JZ   | 31   | 30  | FUNCTIONS | (no carry)             | (with carry)              |

| L  | L    | ι    | L   | F = Ā     | F = A MINUS 1          | F = A                     |

| Ł  | Ĺ    | L    | н   | F = AB    | F = AB MINUS 1         | F = AB                    |

| L  | L    | н    | ι   | F = Ā + B | F = AB MINUS 1         | F = AB                    |

| L  | L    | Н    | н   | F = 1     | F = MINUS 1 (2's COMP) | F = ZERO                  |

| L  | Н    | L    | L   | F = A + B | F = A PLUS (A + B)     | F - A PLUS (A . B) PLUS 1 |

| Ł  | н    | L    | Н   | F = B     | F = AB PLUS (A + B)    | F = AB PLUS (A + B) PLUS  |

| L  | н    | н    | L   | F = A ⊕ B | F - A MINUS B MINUS 1  | F = A MINUS B             |

| L  | н    | н    | н   | F = A + 8 | F = A + B              | F = (A + B) PLUS 1        |

| н  | L    | L    | L   | F = ÃB    | F = A PLUS (A + B)     | F = A PLUS (A + B) PLUS 1 |

| H  | L    | L    | н   | F = A ⊕ B | F = A PLUS B           | F = A PLUS B PLUS 1       |

| н  | L    | н    | L   | F = B     | F = AB PLUS (A + B)    | F = AB PLUS (A + B) PLUS  |

| н  | L    | н    | н   | F = A + B | F = {A + B}            | F = (A + B) PLUS 1        |

| н  | Н    | L    | L   | F = 0     | F = A PLUS A T         | F = A PLUS A PLUS 1       |

| н  | Н    | L    | н   | F = AB    | F = AB PLUS A          | F = AB PLUS A PLUS 1      |

| Н  | н    | н    | L   | F = AB    | F = AB PLUS A          | F = AB PLUS A PLUS 1      |

| н  | н    | н    | н   | F - A     | F = A                  | F = A PLUS 1              |

<sup>&</sup>lt;sup>†</sup>Each bit is shifted to the next more significant position.

TABLE 2

|    | ELEC |       |     |           | ACTIVE-HIGH I                | DATA                      |  |  |  |  |

|----|------|-------|-----|-----------|------------------------------|---------------------------|--|--|--|--|

| 31 | LLEC | . 110 | 114 | M = H     | M = L; ARITHMETIC OPERATIONS |                           |  |  |  |  |

| 53 | \$2  | S1    | SO: | LOGIC     | С <sub>п</sub> = н           | Č <sub>n</sub> = L        |  |  |  |  |

|    |      |       |     | FUNCTIONS | (no carry)                   | (with carry)              |  |  |  |  |

| L  | Ł    | L     | 1   | F = A     | F = A                        | F = A PLUS 1              |  |  |  |  |

| L  | L    | L     | н   | F = A + B | F = A + B                    | F = (A + B) PLUS 1        |  |  |  |  |

| L  | L    | н     | L   | F = ĀB    | F = A + B                    | F = (A + B) PLUS 1        |  |  |  |  |

| L  | L    | н     | н   | F = 0     | F = MINUS 1 (2's COMPL)      | F = ZERO                  |  |  |  |  |

| L  | н    | L     | L   | F ≈ AB    | F = A PLUS AB                | F = A PLUS AB PLUS 1      |  |  |  |  |

| L  | н    | L     | н   | F = B     | F = (A + B) PLUS AB          | F = (A + B) PLUS AB PLUS  |  |  |  |  |

| L  | н    | н     | L   | F÷A ⊕ B   | F : A MINUS B MINUS 1        | F = A MINUS B             |  |  |  |  |

| L  | Н    | н     | н   | F = AB    | F = AB MINUS 1               | F = AB                    |  |  |  |  |

| н  | L    | L     | L   | F = X + B | F = A PLUS AB                | F = A PLUS AB PLUS 1      |  |  |  |  |

| н  | L    | L     | н   | F = A ① B | F = A PLUS B                 | F = A PLUS B PLUS 1       |  |  |  |  |

| н  | L    | н     | L   | F = B     | F = {A + B} PLUS AB          | F = (A + B) PLUS AB PLUS  |  |  |  |  |

| н  | L    | н     | н   | F = AB    | F = AB MINUS 1               | F = AB                    |  |  |  |  |

| н  | н    | L     | L   | F = 1     | F = A PLUS A T               | F = A PLUS A PLUS 1       |  |  |  |  |

| н  | н    | L     | н   | F = A + B | F = (A + B) PLUS A           | F = (A + B) PLUS A PLUS 1 |  |  |  |  |

| н  | н    | н     | L   | F = A + B | F = (A + B) PLUS A           | F = (A + B) PLUS A PLUS 1 |  |  |  |  |

| н  | н    | н     | н   | F = A     | F = A MINUS 1                | F = A                     |  |  |  |  |

## SN54AS181A, SN54AS881A, SN74AS181A, SN74AS881A ARITHMETIC LOGIC UNITS/FUNCTION GENERATORS

| bsolute maximum ratings over operating free-air temperature range (unless otherwise noted) |

|--------------------------------------------------------------------------------------------|

| Supply voltage, VCC                                                                        |

| Off-state output voltage (A = B output only)                                               |

| Storage temperature range – 65 °C to 150 °C                                                |

#### recommended operating conditions

|                 |                              |                                 |      | SN54AS |            | SN74AS' |     |                          | UNIT |

|-----------------|------------------------------|---------------------------------|------|--------|------------|---------|-----|--------------------------|------|

|                 |                              |                                 | MIN  | NOM    | MAX        | MIN     | NOM | MAX                      | ONIT |

| Vcc             | Supply voltage               |                                 | 4.5  | 5      | 5.5        | 4.5     | 5   | 5.5                      | ٧    |

| ViH             | High-level input voltage     |                                 | 2    |        |            | 2       |     |                          | l v  |

| V <sub>JL</sub> | Low-level input voltage      |                                 |      |        | 0.8        |         |     |                          | V    |

| Voн             | High-level output voltage    | A = B output only               |      |        | 5.5        |         |     | 5.5                      |      |

| Іон             | High-level output current    | All outputs except  A = B and G |      |        | <b>– 2</b> |         |     | - 2                      | mA   |

| ЮН              | riigir ic voi output ouriont | G                               |      |        | - 3        |         |     | MAX<br>5.5<br>0.8<br>5.5 | mA   |

| IOL Low         | Low-level output current     | All outputs except G            |      |        | 20         |         |     | 20                       | mA   |

|                 |                              | G                               |      |        | 48         |         |     | 48                       | mA   |

| TA              | Operating free-air temperatu |                                 | - 55 |        | 125        | 0       |     | 70                       | °C   |

|       | PARAMETER                                     | TEST COM                                            | UDITIONS                    |                   | N54AS            | ,     | S        | N74AS            |       | LINUT |

|-------|-----------------------------------------------|-----------------------------------------------------|-----------------------------|-------------------|------------------|-------|----------|------------------|-------|-------|

|       | FANAIWETEN                                    | TEST CON                                            | NDITIONS                    | MIN               | TYP <sup>↑</sup> | MAX   | MIN      | TYP <sup>†</sup> | MAX   | UNIT  |

| VIK   |                                               | $V_{CC} = 4.5 V$ ,                                  | I <sub>I</sub> = -18 mA     |                   |                  | - 1.2 |          |                  | - 1.2 | V     |

| Voн   | Any output except A = B                       | $V_{CC} = 4.5 \text{ V to } 5.5$                    | V, $I_{OH} = -2 \text{ mA}$ | v <sub>cc</sub> - | 2                |       | vcc-     | 2                | -     | ٧     |

|       | G                                             | $V_{CC} = 4.5 \text{ V},$ $V_{CC} = 4.5 \text{ V},$ | $I_{OH} = -3 \text{ mA}$    | 2.4               | 3.4              |       | 2.4      | 3.4              |       | V     |

| ЮН    | A = B                                         | $V_{CC} = 4.5 V_{c}$                                | $V_{OH} = 5.5 V$            |                   |                  | 0.1   |          |                  | 0.1   | mA    |

| VOL   | Any output except $\overline{G}$              | V <sub>CC</sub> = 4.5 V.                            | I <sub>OL</sub> = 20 mA     |                   | 0.3              | 0.5   |          | 0.3              | 0.5   | ٧     |

|       | G                                             | $V_{CC} = 4.5 V,$                                   | IOL = 48 mA ,               |                   | 0.4              | 0.5   |          | 0.4              | 0.5   | V     |

|       | M input                                       |                                                     |                             |                   |                  | 0.1   |          |                  | 0.1   |       |

| 1,    | Any A or B input                              | V <sub>CC</sub> = 5.5 V,                            |                             |                   |                  | 0.3   |          |                  | 0.3   | 1 .   |

| "     | Any S input                                   | νCC = p.p ν,                                        | V  = 7 V                    |                   |                  | 0.4   | t        |                  | 0.4   | mA    |

|       | Carry input                                   |                                                     |                             |                   |                  | 0.6   |          | -                | 0.6   | 1 1   |

|       | M input                                       |                                                     |                             |                   |                  | 20    |          |                  | 20    |       |

| ин    | Any A or B input                              | V <sub>CC</sub> = 5.5 V,                            | V 27V                       |                   |                  | 60    |          |                  | 60    | 1.1   |

| 'IH   | Any S input                                   | vCC = 5.5 v,                                        | V  = 2.7 V                  |                   |                  | 80    | <u> </u> |                  | 80    | μA    |

|       | Carry input                                   |                                                     |                             |                   |                  | 120   | 1        |                  | 120   | 1     |

|       | M input                                       |                                                     |                             |                   |                  | 2     |          |                  | - 2   |       |

| I IIL | Any A or B input                              | $V_{CC} = 5.5 \text{ V},$                           | V: 0.4.V                    |                   |                  | - 6   | T        |                  | - 6   | 1 . 1 |

| ] "L  | Any S input                                   | VCC = 5.5 V,                                        | V  = 0.4 V                  |                   |                  | -8    |          |                  | - 8   | mA    |

|       | Carry input                                   |                                                     |                             |                   |                  | -12   |          |                  | - 12  |       |

| lo‡   | All outputs except $A = B$ and $\overline{G}$ | V <sub>CC</sub> = 5.5 V,                            | V <sub>O</sub> = 2.25 V     | - 30              | - 45             | - 112 | - 30     | - 45             | - 112 | mA    |

|       | G                                             |                                                     | -                           |                   | - 165            |       |          | - 165            |       |       |

|       |                                               |                                                     | 'AS181A                     | <b> </b>          | 135              | 200   | İ        | 135              | 200   |       |

| lcc   |                                               | $V_{CC} = 5.5 V$                                    | 'AS881A                     |                   | 135              | 210   |          | 135              | 210   | mA    |

$<sup>^{\</sup>dagger}$ All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ .

<sup>&</sup>lt;sup>‡</sup>The output conditions have been chosen to produce a current that closely approximates one-half of the true short-circuit current, los.

#### switching characteristics (see Note 1)

| PARAMETER       | FROM<br>(INPUT) | TO<br>(OUTPUT)   | TEST<br>CONDITIONS                                         | $V_{CC} = 5 \text{ V},$ $C_L = 15 \text{ pF},$ $R_L = 500 \Omega$ $(280 \Omega \text{ for } A)$ $T_A = 25 ^{\circ}\text{C}$ $A = 25 ^{\circ}\text{C}$ | A | C<br>R<br>T<br>SN54<br>SN54<br>MIN 1 | L = 5(<br>L = 5(<br>A = M<br>AS1<br>AS8 | 81A<br>MAX | 5 pF fe<br>80 Ω f<br>IAX<br>SN7-<br>SN7-<br>MIN | or A =<br>or A =<br>4AS1<br>4AS8<br>TYP <sup>†</sup> | 81A<br>81A<br>MAX | UNIT |

|-----------------|-----------------|------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------|-----------------------------------------|------------|-------------------------------------------------|------------------------------------------------------|-------------------|------|

| t <sub>pd</sub> | Cn              | C <sub>n+4</sub> |                                                            | 5                                                                                                                                                                                                                                                                                       |   | 2                                    | 7                                       | 11         | 2                                               | 7                                                    | 9                 | ns   |

| t <sub>pd</sub> | Any<br>Ā or B   | Cn + 4           | M = 0  V, S1 = S2 = 0  V,<br>S0 = S3 = 4.5  V (SUM  mode)  | 6                                                                                                                                                                                                                                                                                       |   | 2                                    | 8                                       | 14         | 2                                               | 8                                                    | 12                | ns   |

| t <sub>pd</sub> | Any<br>Ā or B   | C <sub>n+4</sub> | M = 0 V, S0 = S3 = 0 V,<br>S1 = S2 = 4.5 V (DIFF mode)     | 7                                                                                                                                                                                                                                                                                       |   | 2                                    | 8                                       | 20         | 2                                               | 8                                                    | 16                | ns   |

| t <sub>pd</sub> | Cn              | Any F            | M = 0 V (SUM or DIFF mode)                                 | 5                                                                                                                                                                                                                                                                                       |   | 3                                    | 6                                       | 11         | 3                                               | 6                                                    | 9                 | ns   |

| <sup>t</sup> pd | Any<br>Ā or B   | Ğ                | M = 0  V,  S1 = S2 = 0  V,<br>S0 = S3 = 4.5  V (SUM  mode) | 4                                                                                                                                                                                                                                                                                       |   | 2                                    | 5                                       | 9          | 2                                               | 5                                                    | 7                 | ns   |

| <sup>t</sup> pd | Any<br>Ā or B   | Ğ                | M=0 V, S0=S3=0 V,<br>S1=S2=4.5 V (DIFF mode)               | 5                                                                                                                                                                                                                                                                                       |   | 2                                    | 6                                       | 12         | 2                                               | 6                                                    | 9                 | ns   |

| t <sub>pd</sub> | Any<br>Ā or B   | P                | M=0 V, S1 = S2 = 0 V,<br>S0 = S3 = 4.5 V (SUM mode)        | 5                                                                                                                                                                                                                                                                                       |   | 2                                    | 6                                       | 11         | 2                                               | 6                                                    | 8                 | ns   |

| <sup>t</sup> pd | Any<br>A or B   | P                | M = 0 V, S0 = S3 = 0 V,<br>S1 = S2 = 4.5 V (DIFF mode)     | 5                                                                                                                                                                                                                                                                                       |   | 2                                    | 6                                       | 13         | 2                                               | 6                                                    | 10                | ns   |

| <sup>t</sup> pd | Āi or<br>Bi     | Fi               | M = 0 V, S1 = S2 = 0 V,<br>S0 = S3 = 4.5 V (SUM mode)      | 5                                                                                                                                                                                                                                                                                       |   | 2                                    | 5                                       | 11         | 2                                               | 5                                                    | 8                 | ns   |

| <sup>t</sup> pd | Āi or<br>Bi     | Fi               | M = 0 V, S0 = S1 = 0 V,<br>S1 = S2 = 4.5 V (DIFF mode)     | 5                                                                                                                                                                                                                                                                                       |   | 2                                    | 6                                       | 12         | 2                                               | 6                                                    | 10                | ns   |

| <sup>t</sup> pd | Ai or<br>Bi     | Fi               | M = 4.5 V (LOGIC mode)                                     | 6                                                                                                                                                                                                                                                                                       |   | 2                                    | 6                                       | 16         | 2                                               | 6                                                    | 11                | ns   |

| t <sub>pd</sub> | Any Ā<br>or B   | A = B            | M = 0 V, S0 = S3 = 0 V,<br>S1 = S2 = 4.5 V (DIFF mode)     | 12                                                                                                                                                                                                                                                                                      |   | 4                                    | 14                                      | 26         | 4                                               | 14                                                   | 21                | ns   |

### additional 'AS881A switching characteristics involving status checks (see Note 1)

| PARAMETER       | FROM<br>(INPUT) | то<br>(оитрит)   | TEST<br>CONDITIONS                                                                                                                                                                                        | $V_{CC} = 5 \text{ V},$ $C_L = 15 \text{ pF},$ $R_L = 500 \Omega,$ $T_A = 25 ^{\circ}\text{C}$ $AS881A$ MIN TYP <sup>†</sup> MAX | SN5 | CL=!<br>RL=!<br>TA= | = 4.5 V<br>50 pF,<br>500 Ω,<br>MIN to<br>881A<br>MAX | MAX<br>SN: | 74AS | B81A<br>MAX | UNIT |

|-----------------|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|------------------------------------------------------|------------|------|-------------|------|

| <sup>t</sup> pd | Any<br>Ā or B   | P                | $C_n = 4.5V$ , $M = 4.5V$ ,<br>S0 = S3 = 4.5V, $S1 = S2 = 0V$ ,<br>Equality $(\overline{A}i = \overline{B}i \text{ or } \overline{A}i \neq \overline{B}i)$                                                | 8                                                                                                                                | 2   | 10                  | 19                                                   | 2          | 10   | 15          | ns   |

| t <sub>pd</sub> | Any<br>Ā or B   | C <sub>n+4</sub> | $C_n = 4.5 \text{ V}, M = 4.5 \text{ V},$<br>S0 = S3 = 4.5  V, S1 = S2 = 0  V,<br>Equality ( $\vec{A}i = \vec{B}i \text{ or } \vec{A}i \neq \vec{B}i$ )                                                   | 10                                                                                                                               | 2   | 12                  | 24                                                   | 2          | 12   | 18          | ns   |

| <sup>t</sup> pd | Any<br>Ā or Ē   | P                | $C_n = 4.5 \text{ V}, M = 4.5 \text{ V},$<br>S2 = 4.5  V, S0 = S1 = S3 = 0  V,<br>$(\overline{A}i = \overline{B}i = H \text{ or } \overline{A}i \text{ or } \overline{B}i = L)$                           | 8                                                                                                                                | 2   | 10                  | 19                                                   | 2          | 10   | 15          | ns   |

| <sup>t</sup> pd | Any<br>Ā or B   | C <sub>n+4</sub> | $C_{n} = 4.5 \text{ V}, M = 4.5 \text{ V},$<br>S2 = 4.5  V, S0 = S1 = S3 = 0  V,<br>$(\overrightarrow{A}i = \overrightarrow{B}i = H \text{ or } \overrightarrow{A}i \text{ or } \overrightarrow{B}i = L)$ | Ť1                                                                                                                               | 2   | 13                  | 25                                                   | 2          | 13   | 19          | ns   |

$t_{pd}$  = tpHL or tpLH TAII typical values are at  $V_{CC}$  = 5 V,  $T_A$  = 25 °C.

#### SUM MODE TEST TABLE FUNCTION INPUTS: S0 = S3 = 4.5 V, S1 = S2 = M = 0 V

| PARAMETER                            | INPUT     |                | R INPUT      | OTHER DA             | TA INPUTS                                                          | ОИТРИТ                       | OUTPUT       |

|--------------------------------------|-----------|----------------|--------------|----------------------|--------------------------------------------------------------------|------------------------------|--------------|

| PARAMETER                            | TEST      | APPLY<br>4.5 V | APPLY<br>GND | APPLY<br>4.5 V       | APPLY<br>GND                                                       | UNDER<br>TEST                | (SEE NOTE 1) |

| tPLH<br>tPHL                         | Ãi        | Bi             | None         | Remaining<br>Ā and B | Cn                                                                 | Fi                           | In-Phase     |

| tPLH<br>tPHL                         | Bi        | Āi             | None         | Remaining<br>Ā and B | Cn                                                                 | Fi                           | In-Phase     |

| tPLH<br>tPHL                         | Āi        | Бi             | None         | None                 | Remaining<br>Ā and B, C <sub>n</sub>                               | P                            | In-Phase     |

| tPLH<br>tPHL                         | Bi Āi Non |                | None         | None                 | Remaining<br>$\overrightarrow{A}$ and $\overrightarrow{B}$ , $C_n$ | . "   D                      |              |

| <sup>†</sup> PLH<br><sup>†</sup> PHL | Āi        | None           | Bi           | Remaining<br>B       | Remaining<br>Ā, C <sub>n</sub>                                     | Ğ                            | In-Phase     |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Bi        | None           | Āi           | Remaining<br>B       | Remaining<br>A, C <sub>n</sub>                                     | G                            | In-Phase     |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Cn        | None           | None .       | Ail<br>Ā             | AII<br>B                                                           | Any F<br>or C <sub>n+4</sub> | In-Phase     |

| tpLH<br>tpHL                         | Āi        | None           | Bi           | Remaining<br>B       | Remaining<br>Ā, C <sub>n</sub>                                     | C <sub>n + 4</sub>           | Out-of-Phase |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Bi        | None           | Āi           | Remaining<br>B       | Remaining<br>Ā, C <sub>n</sub>                                     | C <sub>n + 4</sub>           | Out-of-Phase |

#### DIFF MODE TEST TABLE FUNCTION INPUTS: S1 = S2 = 4.5 V, S0 = S3 = M = 0 V

| PARAMETER                            | INPUT |                | R INPUT<br>TE BIT | OTHER DA       | TA INPUTS                                              | OUTPUT                       | OUTPUT       |  |

|--------------------------------------|-------|----------------|-------------------|----------------|--------------------------------------------------------|------------------------------|--------------|--|

| TANAMETER                            | TEST  | APPLY<br>4.5 V | APPLY<br>GND      | APPLY<br>4.5 V | APPLY<br>GND                                           | TEST                         | (SEE NOTE 1) |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Āi    | None           | Bi                | Remaining<br>A | Remaining<br>B, C <sub>n</sub>                         | Fi                           | In-Phase     |  |

| tPLH<br>tPHL                         | Bi    | Āi             | None              | Remaining<br>Ā | Remaining<br>B, C <sub>n</sub>                         | Fi                           | Out-of-Phase |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Āi    | None           | Bi                | None           | Remaining<br>A and B, C <sub>n</sub>                   | P                            | In-Phase     |  |

| tPLH<br>tPHL                         | Bi    | Āi             | None              | None           | Remaining<br>A and B, C <sub>n</sub>                   | P                            | Out-of-Phase |  |

| tPLH<br>tPHL                         | Āi    | Bi             | None              | None           | Remaining<br>$\overline{A}$ and $\overline{B}$ , $C_n$ | G                            | In-Phase     |  |

| tPLH<br>tPHL                         | Bi    | None           | Āi                | None           | Remaining<br>$\overline{A}$ and $\overline{B}$ , $C_n$ | G                            | Out-of-Phase |  |

| tPLH<br>tPHL                         | Āi    | None           | Bi                | Remaining Ā    | remaining<br>B, C <sub>n</sub>                         | A = B                        | In-Phase     |  |

| tPLH<br>tPHL                         | Bi    | Āi             | None              | Remaining<br>Ā | Remaining<br>B, C <sub>n</sub>                         | A = B                        | Out-of-Phase |  |

| tPLH<br>tPHL                         | Cn    | None           | All               |                | None                                                   | C <sub>n+4</sub><br>or any F | In-Phase     |  |

| tPLH<br>tPHL                         | Āi    | Bi             | None              | None           | Remaining<br>Ā, Ē, C <sub>n</sub>                      | C <sub>n + 4</sub>           | Out-of-Phase |  |

| t <sub>PLH</sub>                     | Bi    | None           | Āi                | None           | Remaining<br>Ā, Ē, C <sub>n</sub>                      | C <sub>n+4</sub>             | In-Phase     |  |

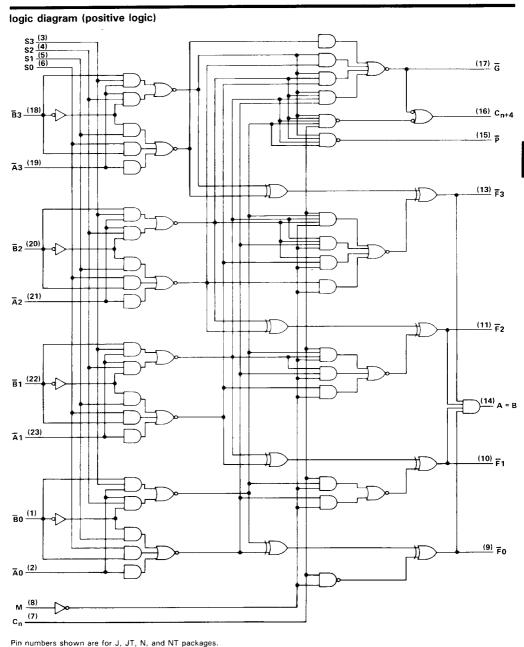

## SN54AS181B, SN74AS181B

D2661, DECEMBER 1985-REVISED MAY 1986

- Package Options Include Compact 300-mil or Standard 600-mil DIPs and Both Plastic and Ceramic Chip Carriers

- Full Look-Ahead for High-Speed Operations on Long Words

- **Arithmetic Operating Modes:**

Addition Subtraction Shift Operand A One Position Magnitude Comparison Plus Twelve Other Arithmetic Operations

- Logic Function Modes **Exclusive-OR** Comparator AND, NAND, OR, NOR

- Dependable Texas Instruments Quality and Reliability

#### logic symbol†

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for J, JT, N, and NT packages.

#### SN54AS181B . . . JT OR JW PACKAGE SN74AS181B . . . N OR NT PACKAGE (TOP VIEW)

ARITHMETIC LOGIC UNITS/FUNCTION GENERATORS

Ā0 ∏2 23 A 1 s3 **□**3 22 B1 21 🗖 🗚 2 S2 🛛 4 20 B2 S1 ∏5 19 🗖 🗚 3 so ∏6 18 🗍 🛱 3  $C_n$ М 17 🛮 🗑 Fo ∏9 16 Cn + 4 F1 ∏10 15 P F2 []11 14 ☐ A = B GND ∏12 13∏ F̃3

SN54AS181B . . . FK PACKAGE SN74AS181B . . . FN PACKAGE (TOP VIEW)

NC-No internal connection

#### TYPICAL ADDITION TIMES (C<sub>L</sub> = 15 pF, R<sub>L</sub> = 280 $\Omega$ , T<sub>A</sub> = 25 °C)

| NUMBER     |                            | ADDITION TIMES              |                          | PACK                      | AGE COUNT                      | CARRY METHOD    |  |

|------------|----------------------------|-----------------------------|--------------------------|---------------------------|--------------------------------|-----------------|--|

| OF<br>BITS | USING 'AS181B<br>AND'AS882 | USING 'AS881B<br>AND 'AS882 | USING 'S181<br>AND 'S182 | ARITHMETIC<br>LOGIC UNITS | LOOK-AHEAD<br>CARRY GENERATORS | BETWEEN<br>ALUs |  |

| 1 to 4     | 5 ns                       | 5 ns                        | 11 ns                    | 1                         |                                | NONE            |  |

| 5 to 8     | 10 ns                      | 10 ns                       | 18 ns                    | 2                         |                                | RIPPLE          |  |

| 9 to 16    | 14 ns                      | 14 ns                       | 19 ns                    | 3 or 4                    | 1                              | FULL LOOK-AHEAD |  |

| 17 to 64   | 19 ns                      | 19 ns                       | 28 ns                    | 5 to 16                   | 2 to 5                         | FULL LOOK-AHEAD |  |

Texas 💠 INSTRUMENTS

#### description

The 'AS181B arithmetic logic units (ALU)/function generators have a complexity of 75 equivalent gates on a monolithic chip. These circuits perform 16 binary arithmetic operations on two 4-bit words as shown in Tables 1 and 2. These operations are selected by the four function-select lines (S0, S1, S2, S3) and include addition, subtraction, decrement, and straight transfer. When performing arithmetic manipulations, the internal carries must be enabled by applying a low-level voltage to the mode control input (M). A full carry look-ahead scheme is made available in these devices for fast, simultaneous carry generation by means of two cascade-outputs,  $\overline{G}$  and  $\overline{P}$ , for the four bits in the package. When used in conjunction with the SN54AS882 or SN74AS882 full carry look-ahead circuits, high-speed arithmetic operations can be performed. The typical addition times shown previously illustrate the little additional time required for addition of longer words when full carry look-ahead is employed. The method of cascading 'AS882 circuits with these ALUs to provide multilevel full carry look-ahead is illustrated under signal designations.

If high speed is not of importance, a ripple-carry input  $(C_n)$  and a ripple-carry output  $(C_{n+4})$  are available. However, the ripple-carry delay has also been minimized so that arithmetic manipulations for small word lengths can be performed without external circuitry.

The 'AS181B will accommodate active-high or active-low data if the pin designations are interpreted as follows:

| PIN NUMBER                 | 2  | 1  | 23 | 22 | 21 | 20             | 19 | 18 | 9  | 10 | 11 | 13 | 7       | 16               | 15 | 17 |

|----------------------------|----|----|----|----|----|----------------|----|----|----|----|----|----|---------|------------------|----|----|

| Active-low data (Table 1)  | ĀO | Вo | Ā1 | B1 | Ā2 | B <sub>2</sub> | Ā3 | B3 | FO | ₹1 | F2 | F3 | Cn      | C <sub>n+4</sub> | P  | G  |

| Active-high data (Table 2) | A0 | BO | A1 | В1 | A2 | B2             | А3 | В3 | F0 | F1 | F2 | F3 | <u></u> | <u>C</u> n+4     | X  | Y  |

Subtraction is accomplished by 1's complement addition where the 1's complement of the subtrahend is generated internally. The resultant output is A-B-1, which requires an end-around or forced carry to provide A-B.

The 'AS181B can also be utilized as a comparator. The A=B output is internally decoded from the function outputs (F0, F1, F2, F3) so that when two words of equal magnitude are applied at the A and B inputs, it will assume a high level to indicate equality (A=B). The ALU must be in the subtract mode with  $C_n=H$  when performing this comparison. The A=B output is open-collector so that it can be wire-AND connected to give a comparison for more than four bits. The carry output ( $C_{n+4}$ ) can also be used to supply relative magnitude information. Again, the ALU must be placed in the subtract mode by placing the function select input S3, S2, S1, S0 at L, H, H, L, respectively.

| INPUT C <sub>n</sub> | OUTPUT Cn+4 | ACTIVE-LOW DATA<br>(FIGURE 1) | ACTIVE-HIGH DATA<br>(FIGURE 2) |

|----------------------|-------------|-------------------------------|--------------------------------|

| Н                    | Н           | A≥B                           | A≤B                            |

| н                    | Ĺ           | A < B                         | A > B                          |

| L                    | Н           | A > B                         | A < B                          |

| L                    | L           | A≤B                           | A≥B                            |

These circuits have been designed to not only incorporate all of the designer's requirements for arithmetic operations, but also to provide 16 possible functions of two Boolean variables without the use of external circuitry. These logic functions are selected by use of the four function-select inputs (S0, S1, S2, S3) with the mode-control input (M) at a high level to disable the internal carry. The 16 logic functions are detailed in Tables 1 and 2 and include exclusive-OR, NAND, AND, NOR, and OR functions.

#### signal designations

In both Figures 1 and 2, the polarity indicators ( ) indicate that the associated input or output is active-low with respect to the function shown inside the symbol and the symbols are the same in both figures. The signal designations in Figure 1 agree with the indicated internal functions based on active-low data, and are for use with the logic functions and arithmetic operations shown in Table 1. The signal designations have been changed in Figure 2 to accommodate the logic functions and arithmetic operations for the active-high data given in Table 2. The 'AS181B together with 'AS882 and 'S182 can be used with the signal designation of either Figure 1 or Figure 2.

(USE WITH TABLE I)

#### TABLE I

|    | SELE | CTIO | ı.  |                             | ACTIVE-LOW DATA                  |                                         |

|----|------|------|-----|-----------------------------|----------------------------------|-----------------------------------------|

| L  | SELE | CIIC | //N | M = H                       | M = L; ARITHI                    | METIC OPERATIONS                        |

| 63 | S2   | 61   | 60  | LOGIC                       | C <sub>n</sub> = L               | C <sub>n</sub> = H                      |

| 33 | 32   | 31   | 30  | FUNCTIONS                   | (no carry)                       | (with carry)                            |

| L  | L    | L    | L   | F = Ā                       | F = A MINUS 1                    | F = A                                   |

| L  | L    | Ł    | н   | $F = \overline{AB}$         | F = AB MINUS 1                   | F = AB                                  |

| L  | L    | Н    | L   | F = A + B                   | F = AB MINUS 1                   | F = AB                                  |

| L  | L    | Н    | н   | F = 1                       | F = MINUS 1 (2's COMP)           | F = ZERO                                |

| L  | Н    | L    | L   | $F = \overline{A + B}$      | $F = A PLUS (A + \overline{B})$  | $F = A PLUS (A + \overline{B}) PLUS 1$  |

| L  | Н    | L    | Н   | F = B                       | $F = AB PLUS (A + \overline{B})$ | $F = AB PLUS (A + \overline{B}) PLUS 1$ |

| L  | Н    | Н    | L   | $F = \overline{A \oplus B}$ | F = A MINUS B MINUS 1            | F = A MINUS B                           |

| L  | Н    | Н    | Н   | F = A + B                   | $F = A + \overline{B}$           | $F = (A + \overline{B}) PLUS 1$         |

| Н  | L    | L    | L   | F = ĀB                      | F = A PLUS (A + B)               | F = A PLUS (A + B) PLUS 1               |

| Н  | L    | Ł    | Н   | F = A ⊕ B                   | F = A PLUS B                     | F = A PLUS B PLUS 1                     |

| н  | L    | Н    | L   | F = B                       | F = AB PLUS (A + B)              | $F = A\overline{B} PLUS (A + B) PLUS 1$ |

| Н  | L    | Н    | Н   | F = A + B                   | F = (A + B)                      | F = (A + B) PLUS 1                      |

| Н  | Н    | L    | L   | F = 0                       | F = A PLUS A*                    | F = A PLUS A PLUS 1                     |

| н  | Н    | Ł    | Н   | $F = A\overline{B}$         | F = AB PLUS A                    | F = AB PLUS A PLUS 1                    |

| н  | Н    | Н    | L   | F = AB                      | F = AB PLUS A                    | F = AB PLUS A PLUS 1                    |

| Н  | Н    | Н    | Н   | F = A                       | F = A                            | F = A PLUS 1                            |

#### TABLE II

|    | 051.5 | OT16 |    |                             | ACTIVE-HIGH DATA                 | 1                               |

|----|-------|------|----|-----------------------------|----------------------------------|---------------------------------|

|    | SELE  | CIIC | )N | M = H                       | M = L; ARITH                     | METIC OPERATIONS                |

| 63 | S2    | C1   |    | LOGIC                       | C <sub>n</sub> = H               | ¯cn = L                         |

| 33 | 32    | 31   | 30 | FUNCTIONS                   | (no carry)                       | (with carry)                    |

| L  | L     | L    | L  | F = Ā                       | F = A                            | F = A PLUS 1                    |

| L  | L     | L    | Н  | $F = \overline{A + B}$      | F = A + B                        | F = (A + B) PLUS 1              |

| L  | L     | Н    | L  | F = $\overline{A}B$         | $F = A + \overline{B}$           | $F = (A + \overline{B}) PLUS 1$ |

| L  | L     | Н    | Н  | F = 0                       | F = MINUS 1 (2's COMP)           | F = ZERO                        |

| L  | Н     | L    | L  | F = AB                      | F = A PLUS AB                    | F = A PLUS AB PLUS 1            |

| L  | н     | L    | Н  | F = B                       | $F = (A + B) PLUS A\overline{B}$ | F = (A + B) PLUS AB PLUS 1      |

| L  | Н     | H    | L  | F = A + B                   | F = A MINUS B MINUS 1            | F = A MINUS B                   |

| L  | Н     | Н    | Н  | $F = A\overline{B}$         | F = AB MINUS 1                   | F = AB                          |

| Н  | L     | L    | L  | $F = \overline{A} + B$      | F = A PLUS AB                    | F = A PLUS AB PLUS 1            |

| Н  | L     | Ł    | Н  | $F = \overline{A \oplus B}$ | F ≃ A PLUS B                     | F = A PLUS B PLUS 1             |

| Н  | L     | н    | L  | F = B                       | $F = (A + \overline{B}) PLUS AB$ | F = (A + B) PLUS AB PLUS 1      |

| Н  | L     | н    | н  | F = AB                      | F = AB MINUS 1                   | F = AB                          |

| н  | Н     | L    | L  | F = 1                       | F = A PLUS A*                    | F = A PLUS A PLUS 1             |

| н  | Н     | L    | Н  | F = A + B                   | F = (A + B) PLUS A               | A = (A + B) PLUS A PLUS 1       |

| н  | Н     | Н    | L  | F = A + B                   | $F = (A + \overline{B}) PLUS A$  | F = (A + B) PLUS A PLUS 1       |

| н  | Н     | Н    | Н. | F = A                       | F = A MINUS 1                    | F = A                           |

<sup>\*</sup>Each bit is shifted to the next more significant position.

| absolute maximum ratings over operating free-air temperature range (unless otherwise noted) |

|---------------------------------------------------------------------------------------------|

| Supply voltage, VCC                                                                         |

| Input voltage                                                                               |

| Off-state output voltage (A = B output only)                                                |

| Operating free-air temperature range: SN54AS181B 55 °C to 125 °C                            |

| SN74AS181B 0 °C to 70 °C                                                                    |

| Storage temperature range65°C to 150°C                                                      |

#### recommended operating conditions

|     |                                |                                | SN   | 154AS18 | 31B | SN  | 74AS18 | 31B | UNIT |

|-----|--------------------------------|--------------------------------|------|---------|-----|-----|--------|-----|------|

|     |                                |                                | MIN  | NOM     | MAX | MIN | NOM    | MAX | UNII |

| Vcc | Supply voltage                 |                                | 4.5  | 5       | 5.5 | 4.5 | 5      | 5.5 | V    |

| VIH | High-level input voltage       |                                | 2    |         |     | 2   |        |     | V    |

| VIL | Low-level input voltage        |                                |      |         | 0.8 |     |        | 0.8 | V    |

| Voн | High-level output voltage      | A = B output only              |      |         | 5.5 |     |        | 5.5 | V    |

| Іон | High-level output current      | All outputs except A = B and G |      |         | - 2 |     |        | - 2 | mA   |

|     |                                | G                              |      |         | - 3 | Ī   |        | - 3 | mA   |

| loL | Low-level output current       | All outputs except G           |      |         | 20  |     |        | 20  | mA   |

|     |                                | G                              |      |         | 48  |     |        | 48  | mA   |

| TA  | Operating free-air temperature |                                | - 55 |         | 125 | 0   |        | 70  | °C   |

#### SN54AS181B, SN74AS181B ARITHMETIC LOGIC UNITS/FUNCTION GENERATORS

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| DADAMETED |                                               | TEST CONDITIONS                             |                          |      | 154AS1 | 31B   | SN74AS181B      |                  |        | UNIT |  |

|-----------|-----------------------------------------------|---------------------------------------------|--------------------------|------|--------|-------|-----------------|------------------|--------|------|--|

|           | PARAMETER                                     | TEST CONDITI                                | IUNS                     | MIN  | TYP    | MAX   | MIN             | TYP <sup>†</sup> | MAX    | ONT  |  |

| Vik       |                                               | V <sub>CC</sub> = 4.5 V,                    | I <sub>I</sub> = -18 mA  |      |        | - 1.2 |                 |                  | -1.2   | V    |  |

| Voн       | Any output<br>except A = B                    | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V},$ | $I_{OH} = -2 \text{ mA}$ | Vcc- | 2      |       | v <sub>CC</sub> | - 2              |        | ٧    |  |

|           | G                                             | $V_{CC} = 4.5 \text{ V},$                   | $I_{OH} = -3 \text{ mA}$ | 2.4  | 3.4    |       | 2.4             | 3.4              |        | ٧    |  |

| ТОН       | A = B                                         | $V_{CC} = 4.5 \text{ V},$                   | V <sub>OH</sub> = 5.5 V  |      |        | 0.1   |                 |                  | 0.1    | mA   |  |

| VOL       | Any output except G                           | V <sub>CC</sub> = 4.5 V,                    | I <sub>OL</sub> = 20 mA  |      | 0.3    | 0.5   |                 | 0.3              | 0.5    | V    |  |

|           | G                                             | V <sub>CC</sub> = 4.5 V,                    | I <sub>OL</sub> = 48 mA  |      | 0.4    | 0.5   |                 | 0.4              | 0.5    | V    |  |

|           | M input                                       | V <sub>CC</sub> = 5.5 V,                    |                          |      |        | 0.1   |                 |                  | 0.1    | mA   |  |

|           | Any A or B input                              |                                             | V <sub>I</sub> = 7 V     |      |        | 0.3   |                 |                  | 0.3    |      |  |

| li l      | Any S input                                   |                                             |                          |      |        | 0.4   |                 | -                | 0.4    |      |  |

|           | Carry input                                   |                                             |                          |      |        | 0.6   |                 |                  | 0.6    |      |  |

|           | M input                                       | V <sub>CC</sub> = 5.5 V,                    | V <sub>I</sub> = 2.7 V   |      |        | 20    |                 |                  | 20     |      |  |

| ۱. '      | Any A or B input                              |                                             |                          |      |        | 60    |                 |                  | 60     | μΑ   |  |

| hH :      | Any S input                                   |                                             |                          |      |        | 80    |                 |                  | 80     | } "^ |  |

|           | Carry input                                   |                                             |                          |      |        | 120   |                 |                  | 120    |      |  |

|           | M input                                       |                                             |                          |      |        | -0.5  |                 |                  | -0.5   |      |  |

|           | Any A or B input                              | V <sub>CC</sub> = 5.5 V,                    |                          |      |        | -1.5  |                 |                  | -1.5   | 1    |  |

| կլ        | Any S input                                   |                                             | V <sub>1</sub> = 0.4 V   |      |        | - 2   |                 |                  | 2      | _    |  |

|           | Carry input                                   |                                             |                          |      |        | - 3   |                 |                  | -3     |      |  |

| lo‡       | All outputs except $A = B$ and $\overline{G}$ | V <sub>CC</sub> = 5.5 V,                    | V <sub>O</sub> = 2.25 V  | - 30 | - 45   | -112  | - 30            | -45              | -112   | mA   |  |

|           | G                                             | 00 - 1,                                     |                          | - 30 |        | -125  | - 30            |                  | .– 125 | 1    |  |

| Icc       |                                               | V <sub>CC</sub> = 5.5 V                     |                          | 1    | 74     | 117   |                 | 74               | 117    | mA   |  |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 \text{ °C}$ .

<sup>‡</sup> The output conditions have been chosen to produce a current that closely approximates one-half of the true short-circuit current, los.

|                  |                |                  |                              |      | V <sub>CC</sub> = 4.5  | V to 5.5             | v,   |     |  |  |

|------------------|----------------|------------------|------------------------------|------|------------------------|----------------------|------|-----|--|--|

|                  |                |                  |                              |      | C <sub>L</sub> ≃ 50 pF | :,                   |      |     |  |  |

| }                |                | ROM TO           |                              |      | $R_L = 500 \Omega$ ,   |                      |      |     |  |  |

| PARAMETER        | FROM           |                  | TEST CONDITIONS              |      |                        | UNIT                 |      |     |  |  |

| TANAMETEN        | (INPUT)        | (OUTPUT)         |                              | SN54 | 4AS181B                | to MAX<br>SN74AS181B |      | 1   |  |  |

|                  |                |                  |                              | MIN  | MAX                    | MIN                  | MAX  |     |  |  |

| tPLH             | Cn             | C .              |                              | 3    | 9                      | 3                    | 8.5  |     |  |  |

| tPHL             | ∪n             | C <sub>n+4</sub> |                              | 2    | 7                      | 2                    | 6.5  | ns  |  |  |

| tPLH             | Any            | Cn+4             | M = 0 V, S1 = S2 = 0 V,      | 3.5  | 13                     | 5                    | 12   | ns  |  |  |

| tPHL             | Ā or B̄        | ∨n+4             | S0 = S3 = 4.5 V (SUM mode)   | 3.5  | 12.5                   | 5                    | 12   | 115 |  |  |

| <sup>t</sup> PLH | Any            | C <sub>n+4</sub> | M = 0 V, S0 = S3 = 0 V,      | 5    | 14.5                   | 5                    | 13   | ns  |  |  |

| tPHL             | ĀorB           | On + 4           | S1 = S2 = 4.5  V (DIFF mode) | 5    | 13.5                   | 5                    | 12.5 | 2   |  |  |

| <sup>t</sup> PLH | C <sub>n</sub> | Any F            | M = 0 V (SUM or DIFF mode)   | 3    | 10.5                   | 3                    | 9    | ns  |  |  |

| tPHL             | 911            | 7                |                              | 3    | 8                      | 3                    | 7.5  | 2   |  |  |

| <sup>t</sup> PLH | Any            | G                | M = 0 V, S1 = S2 = 0 V,      | 3    | 8.5                    | 3                    | 8    | ns  |  |  |

| <sup>t</sup> PHL | Ā or ₿         | )                | S0 = S3 = 4.5 V (SUM mode)   | 2    | 7                      | 2                    | 6    | 2   |  |  |

| tPLH             | Any            | ন                | M = 0 V, S0 = S3 = 0 V,      | 3    | 10.5                   | 3                    | 9.5  | ns  |  |  |

| <sup>t</sup> PHL | Ā or B̄        | -                | S1 = S2 = 4.5  V (DIFF mode) | 2    | 9                      | 2                    | 7    | 113 |  |  |

| <sup>†</sup> PLH | Anγ            | ē                | M = 0 V, S1 = S2 = 0 V,      | 3    | 8.5                    | 3                    | 7.5  | ns  |  |  |

| <sup>t</sup> PHL | A or B         |                  | S0 = S3 = 4.5  V (SUM mode)  | 2    | 7.5                    | 2                    | 6    | 2   |  |  |

| <sup>t</sup> PLH | Any            | P                | M = 0 V, S0 = S3 = 0 V,      | 3    | 10.5                   | 3                    | 9    | ns  |  |  |

| <sup>t</sup> PHL | A or B         | ,                | S1 = S2 = 4.5 V (DIFF mode)  | 3    | 8.5                    | 3                    | 8    | 113 |  |  |

| tPLH             | Āi or          | Fi               | M = 0 V, S1 = S2 = 0 V,      | 3    | 11                     | 3                    | 9.5  | ns  |  |  |

| tPHL             | Bi             | • • •            | S0 = S3 = 4.5 V (SUM mode)   | 3    | 9                      | 3                    | 7.5  | 115 |  |  |

| <sup>t</sup> PLH | ⊼i or          | Ē                | M = 0 V, S0 = S3 = 0 V,      | 3    | 12                     | 3                    | 10.5 | ns  |  |  |

| t <sub>PHL</sub> | Bi             | Fi               | S1 = S2 = 4.5 V (DIFF mode)  | 3    | 11                     | 3                    | 9.5  | 115 |  |  |

| tPLH             | Any            | Any F            | M = 0 V, S1 = S2 = 0 V,      | 3    | 13.5                   | 3                    | 12   | ns  |  |  |

| tPHL             | A or B         | Ally t           | S0 = S3 = 4.5 V (SUM mode)   | 3    | 13                     | 3                    | 11.5 | 115 |  |  |

| tPLH             | Any            | Any F            | M = 0 V, S0 = S3 = 0 V,      | 3    | 16                     | 3                    | 14.5 | ns  |  |  |

| <sup>t</sup> PHL | ĀorB           | - Cuy F          | S1 = S2 = 4.5 V (DIFF mode)  | 3    | 13                     | 3                    | 12.5 | 118 |  |  |

| <sup>t</sup> PLH | ⊼ior Bi        | Fi               | M = 4.5 V (LOGIC mode)       | 3    | 12.5                   | 3                    | 11   | ns  |  |  |

| <sup>†</sup> PHL | ,,, 5, 5,      | . ,              |                              | 3    | 10                     | 3                    | 9.5  | 115 |  |  |

| <sup>t</sup> PLH | Any            | A ≂ B            | M = 0 V, S0 = S3 = 0 V,      | 4    | 19                     | 4                    | 17   | ne. |  |  |

| tPHL             | Ā or B         | 7~5              | S1 = S2 = 4.5  V (DIFF mode) | 5    | 18.5                   | 5                    | 15   | ns  |  |  |

SUM MODE TEST TABLE FUNCTION INPUTS: S0 = S3 = 4.5 V, S1 = S2 = M = 0 V

| PARAMETER                            | INPUT   | 1    |      | OTHER DAT            | A INPUTS                             | OUTPUT                       | OUTPUT<br>WAVEFORM |  |

|--------------------------------------|---------|------|------|----------------------|--------------------------------------|------------------------------|--------------------|--|

| PARAMETER                            | TEST    |      |      | APPLY<br>GND         | TEST                                 | (SEE NOTE 1)                 |                    |  |

| tPLH<br>tPHL                         | Āi      | Bi   | None | Remaining<br>A and B | Cn                                   | Fi                           | In-Phase           |  |

| tPLH<br>tPHL                         | Bi      | Āi   | None | Remaining<br>Ā and B | Cn                                   | Fi                           | In-Phase           |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Āi      | Bi   | None | None                 | Remaining<br>A and B, C <sub>n</sub> | P                            | In-Phase           |  |

| tPLH<br>tPHL                         | -<br>Bi | Āi   | None | None                 | Remaining<br>A and B, C <sub>n</sub> | P                            | In-Phase           |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Āi      | None | Bi   | Remaining<br>B       | Remaining<br>A, C <sub>n</sub>       | Ğ                            | in-Phase           |  |

| tPLH<br>tPHL                         | Bi      | None | Āi   | Remaining<br>B       | Remaining<br>Ā, C <sub>n</sub>       | G                            | In-Phase           |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Cn      | None | None | All<br>Ā             | All<br>B                             | Any F<br>or C <sub>n+4</sub> | In-Phase           |  |

| t <sub>PLH</sub>                     | Āi      | None | Bi   | Remaining<br>B       | Remaining<br>A, C <sub>n</sub>       | C <sub>n+4</sub>             | Out-of-Phase       |  |

| tPLH<br>tPHL                         | Bi      | None | Āi   | Remaining<br>B       | Remaining<br>A, C <sub>n</sub>       | C <sub>n+4</sub>             | Out-of-Phase       |  |

NOTE 1: Load circuit and voltage waveforms are shown in Section 1.

DIFF MODE TEST TABLE FUNCTION INPUTS: S1 = S2 = 4.5 V, S0 = S3 = M = 0 V

|                  | INPUT                                 |                         | R INPUT<br>E BIT | OTHER DAT                               | A INPUTS                                  | OUTPUT           | OUTPUT         |  |

|------------------|---------------------------------------|-------------------------|------------------|-----------------------------------------|-------------------------------------------|------------------|----------------|--|

| PARAMETER        | UNDER<br>TEST                         | APPLY APPLY APPLY APPLY |                  |                                         | UNDER<br>TEST                             | (SEE NOTE 1)     |                |  |

|                  |                                       | 4.5 V                   | GND              | 4.5 V                                   | GND                                       |                  | (022 100 12 17 |  |

| <sup>t</sup> PLH | Āi                                    | None                    | Bi               | Remaining                               | Remaining                                 | Fi               | In-Phase       |  |

| tPHL             |                                       |                         |                  | Ā                                       | B, C <sub>n</sub>                         |                  |                |  |

| <sup>t</sup> PLH | Bi                                    | Āi                      | None             | Remaining                               | Remaining                                 | Fi               | Out-of-Phase   |  |

| t <sub>PHL</sub> | ,                                     | , "                     |                  | Ā                                       | B, C <sub>n</sub>                         |                  |                |  |

| <sup>t</sup> PLH | Āi                                    | None                    | Bi               | None                                    | Remaining                                 | P                | In-Phase       |  |

| tPHL             |                                       | 110110                  | 3                |                                         | A and B, C <sub>n</sub>                   | ,                |                |  |

| tPLH             | Β̃i                                   | Āi                      | None             | None                                    | Remaining                                 | İΡ               | Out-of-Phase   |  |

| <sup>t</sup> PHL | , , , , , , , , , , , , , , , , , , , | / "                     |                  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | $\overline{A}$ and $\overline{B}$ , $C_n$ |                  |                |  |