Crusoe

# **BIOS** Programmer's Guide

Transmeta Crusoe™ Processor

TM5500/TM5800 Hardware Version 0.x/1.x Code Morphing Software Version 4.2.x/4.3.x

Property of:

Transmeta Corporation 3940 Freedom Circle Santa Clara, CA 95054 USA (408) 919-3000 http://www.transmeta.com

The information contained in this document is provided solely for use in connection with Transmeta products, and Transmeta reserves all rights in and to such information and the products discussed herein. This document should not be construed as transferring or granting a license to any intellectual property rights, whether express, implied, arising through estoppel or otherwise. Except as may be agreed in writing by Transmeta, all Transmeta products are provided "as is" and without a warranty of any kind, and Transmeta hereby disclaims all warranties, express or implied, relating to Transmeta's products, including, but not limited to, the implied warranties of merchantability, fitness for a particular purpose and non-infringement of third party intellectual property. Transmeta products may contain design defects or errors which may cause the products to deviate from published specifications, and Transmeta documents may contain inaccurate information. Transmeta makes no representations or warranties with respect to the accuracy or completeness of the information contained in this document, and Transmeta reserves the right to change product descriptions and product specifications at any time, without notice.

Transmeta products have not been designed, tested, or manufactured for use in any application where failure, malfunction, or inaccuracy carries a risk of death, bodily injury, or damage to tangible property, including, but not limited to, use in factory control systems, medical devices or facilities, nuclear facilities, aircraft, watercraft or automobile navigation or communication, emergency systems, or other applications with a similar degree of potential hazard.

Transmeta reserves the right to discontinue any product or product document at any time without notice, or to change any feature or function of any Transmeta product or product document at any time without notice.

Trademarks: Transmeta, the Transmeta logo, Crusoe, the Crusoe logo, Code Morphing, LongRun, and combinations thereof are trademarks of Transmeta Corporation in the USA and other countries. Other product names and brands used in this document are for identification purposes only, and are the property of their respective owners.

Copyright © 2002 Transmeta Corporation. All rights reserved.

# Table of Contents

|           | List of | Tables                                                       | 5  |

|-----------|---------|--------------------------------------------------------------|----|

|           | Introdu | iction                                                       | 7  |

| Chapter 1 | Process | sor and Frequency Detection                                  | 9  |

|           | 1.1     | Processor Detection                                          | 9  |

|           |         | 1.1.1 String Representation                                  | 9  |

|           |         | 1.1.2 Reserved Functions                                     | 10 |

|           |         | 1.1.3 CPUID Standard Functions                               | 11 |

|           |         | 1.1.4 CPUID Extended Functions                               |    |

|           |         | 1.1.5 CPUID Transmeta-Specific Functions Frequency Detection | 15 |

| Chapter 2 | PCI Co  | nfiguration Registers                                        | 19 |

|           | 2.1     | SMRAM Differences                                            | -  |

|           | 2.2     | I/O Mapped Registers                                         |    |

|           | 2.3     | PCI Configuration Registers                                  |    |

|           |         | 2.3.1 Host-to-PCI Bridge Registers (Function 0)              |    |

|           |         | 2.3.2 SDRAM Memory Controller Registers (Function 1)         |    |

|           |         | 2.3.3 Extended BIOS Scratch Pad (Function 2)                 | 72 |

|           | 2.4     | SDRAM Controller Error Codes                                 | 75 |

| Chapter 3 | Model-S | Specific Registers                                           |    |

|           | 3.1     | Introduction                                                 | 77 |

|           | 3.2     | Intel-Compatible MSRs                                        | 77 |

|           | 3.3     | Transmeta-Specific MSRs                                      | 79 |

| Chapter 4 |         | Management                                                   |    |

|           | 4.1     | Power Management Control                                     |    |

|           |         | 4.1.1 Processor Power States                                 |    |

|           |         | 4.1.2 State Transitions                                      |    |

|           |         | 4.1.3 State Preservation                                     |    |

|           | 4.2     | Power Management Registers                                   |    |

|           | 4.3     | LongRun™ Power Management                                    |    |

|           | 4.4     | Example Configuration for PIIX4                              |    |

|           | 4.5     | Special Considerations                                       | 91 |

|           |         | 4.5.1 PCI Arbiter                                            | -  |

|           |         | 4.5.2 Configuration Register Context during STR              |    |

|           |         | 4.5.3 DRAM Refresh                                           |    |

|           |         | 4.5.4 STPCLK Behavior of ALI 1535                            | 92 |

| Chapter 5 | System  | n Management Mode                                            |    |

|           | 5.1     | SMM Address Space                                            |    |

|            |         | 5.1.1      | Standard and Extended SMM Memory Configuration     | 93  |

|------------|---------|------------|----------------------------------------------------|-----|

|            |         | 5.1.2      | High SMM Memory Configuration                      | 94  |

|            |         | 5.1.3      | Address Space Location and Use                     | 94  |

|            | 5.2     | SMM I      | nitialization and State Change                     | 95  |

|            |         | 5.2.1      | State Save Map                                     | 95  |

|            |         | 5.2.2      | State Save Prior to Power Off                      | 96  |

|            |         | 5.2.3      | Address Space Caching                              | 96  |

|            | 5.3     | SMM E      | Execution Environment                              |     |

|            |         | 5.3.1      | SMM Entry State                                    | 97  |

|            |         | 5.3.2      | Exceptions, Interrupts, and A20 Masking within SMM |     |

|            |         | 5.3.3      | SMM Exit Considerations                            | 98  |

| Appendix A | Evam    | nlo Pogis  | ster Settings for SDR SDRAM Controller             | 00  |

| Appendix A |         | pie ivegia |                                                    |     |

| Appendix B | Power   | r Manage   | ment Configuration Code Example                    | 101 |

| Appendix C | PCI Pa  | assive Re  | elease                                             | 105 |

| Appendix D | Initial | Process    | or State                                           | 107 |

| Appendix E | BIOS    | and Keyk   | poard Controller Checklists                        | 109 |

# List of Tables

| Table 1:  | String Fragment Order for Strings Returned by CPUID Functions       | 10 |

|-----------|---------------------------------------------------------------------|----|

| Table 2:  | CPUID Standard Functions                                            | 11 |

| Table 3:  | CPUID Extended Functions                                            | 13 |

| Table 4:  | CPUID Transmeta-Specific Extended Functions                         | 15 |

| Table 5:  | PCI Register Access Classifications                                 | 19 |

| Table 6:  | SMRAM Differences Between 82443BX and Transmeta VNB                 | 20 |

| Table 7:  | I/O Mapped Register Summary                                         | 20 |

| Table 8:  | PCI Registers (Function 0) Summary                                  |    |

| Table 9:  | SDRAM Memory Controller Registers (PCI Function 1) Summary          | 53 |

| Table 10: | Extended BIOS Scratch Pad Registers (PCI Function 2) Summary        | 72 |

| Table 11: | SDRAM Controller Error Codes                                        | 75 |

| Table 12: | Intel-Compatible MSR Summary                                        | 77 |

| Table 13: | Transmeta-Specific MSR Summary                                      | 79 |

| Table 14: | Power Management System States                                      |    |

| Table 15: | Processor Power States                                              |    |

| Table 16: | Example Settings for Power Management Registers (PIIX4 Southbridge) |    |

| Table 17: | Initial Processor State                                             |    |

|           |                                                                     |    |

List of Tables

# Introduction

This document provides information necessary to implement a system BIOS that supports the Crusoe™ processor. The Crusoe processor consists of a Transmeta microprocessor and x86 Code Morphing™ Software that together provide the functionality of an x86-compatible processor.

This document focuses on unique features of the Crusoe processor and is not intended to document generic system BIOS requirements.

## **Reference Documents**

The following documents should be used in conjunction with this guide:

- Crusoe<sup>™</sup> Processor Data Book

- Crusoe<sup>™</sup> Processor Development and Manufacturing Guide

- PCI Local Bus Specification, PCI SIG Revision 2.1

- PCI Hardware and Software Architecture and Design (4th edt.), by Edward Solari amd George Willse, Annabooks, San Diego, 1998

- JEDEC Standard No. 21-C (11/25/97)

Introduction

Chapter 1

# Processor and Frequency Detection

# 1.1 Processor Detection

The recommended method of processor detection for the Crusoe<sup>™</sup> Processor Model TM5500/TM5800 is to use the CPUID instruction. Before executing CPUID, the ID bit in the EFLAGS register should be tested. The TM5500/TM5800 ID bit can be modified which indicates that the processor supports the CPUID instruction.

The CPUID instruction uses the EAX register as an input. If the upper 16 bits in EAX are clear (0000h), the CPUID standard function set is selected. If the upper 16 bits in EAX are set to 8000h, the extended function set is selected. A Transmeta-specific extended function set is also available by setting the upper 16 bits of EAX to 8086h. The output or return values are loaded into the EAX, EBX, ECX and EDX registers. CPUID is a non-privileged serializing instruction.

The TM5500/TM5800 supports the standard and extended functions listed in the following tables. All EAX input values other than those listed in the tables are reserved and return the value of 0000 0000h in the output registers. Implicitly reserved functions have zero return values in all output registers. Additionally, some of the bits listed are designated as "reserved" bits. Software should not rely on the value of reserved bits.

# 1.1.1 String Representation

Several CPUID function codes return character strings. These strings have the common properties described below.

#### Note

These properties apply only to Transmeta-supplied defaults. Programmable strings may deviate from this description.

| Character set | For maximum compatibility, Transmeta uses only the most universal subset of ASCII for string values: the Unique Graphics Characters of ISO 646:1991 and ECMA–6 (the latter is available from http://www.ecma.ch). |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Zero fill     | CPUID function codes that return string data specify the size for each string.<br>Unused characters are filled with a value of 00h.                                                                               |

| Null termination not<br>guaranteed | The entire reserved size of the string may be taken up with printable characters; nulls are only present if required for fill. Thus, programs should not assume these are null-terminated strings, even if they appear to be null-terminated for a particular chip revision.                                                                                                                                  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| String fragment order              | Strings returned by CPUID functions are broken up into fragments in order to present the data in the CPUID output registers EAX, EBX, ECX, EDX. Thus, you must know the intended order of these fragments in order to reassemble them into the desired string. Transmeta uses two distinct orderings, as shown in the table below: one for strings that fit into three registers, and one for longer strings. |

## Table 1: String Fragment Order for Strings Returned by CPUID Functions

| Function code | String fragment order | String description                                  |

|---------------|-----------------------|-----------------------------------------------------|

| 0000 0000h    | EBX, EDX, ECX         | Standard vendor-ID string.                          |

| 0000 0003h    | EAX, EBX, ECX, EDX    | Processor serial number (in upper-case hexadecimal) |

| 8000 0000h    | EBX, EDX, ECX         | Extended vendor-ID string.                          |

| 8000 0002h    | EAX, EBX, ECX, EDX    | Preferred processor-name string.                    |

| 8000 0003h    | EAX, EBX, ECX, EDX    |                                                     |

| 8000 0004h    | EAX, EBX, ECX, EDX    |                                                     |

| 8086 0000h    | EBX, EDX, ECX         | Transmeta vendor-ID string.                         |

| 8086 0003h    | EAX, EBX, ECX, EDX    | Transmeta information string.                       |

| 8086 0004h    | EAX, EBX, ECX, EDX    |                                                     |

| 8086 0005h    | EAX, EBX, ECX, EDX    |                                                     |

| 8086 0006h    | EAX, EBX, ECX, EDX    |                                                     |

# 1.1.2 Reserved Functions

All CPUID function values other than those listed explicitly in this document are reserved for future extensions. Implicitly reserved functions have zero return values in all output registers.

# 1.1.3 CPUID Standard Functions

## Table 2: CPUID Standard Functions

| EAX Input<br>Value | Output<br>Register | Output Value     | Output Definition                                                                                                                                                 |

|--------------------|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 0000h         | EAX                | 0000 0001h<br>or | Standard Function Maximum Level Maximum level supported for the standard function.                                                                                |

|                    |                    | 0000 0003h       | If the processor serial number (PSN) function is disabled,<br>the maximum level supported is 1. If PSN is enabled, the<br>maximum level supported is 3.           |

|                    | EBX                | 756E 6547h       | Vendor ID String The sequence EBX-EDX-ECX forms                                                                                                                   |

|                    | ECX                | 3638 784Dh       | the vendor identification string. The value after reset is<br>"GenuineTMx86". This value is programmable using the                                                |

|                    | EDX                | 5465 6E69h       | CPUID_VND1, CPUID_VND2, and CPUID_VND3 MSRs<br>(see CPUID Vendor ID String Registers on page 80 in<br>Chapter 3, Model-Specific Registers).                       |

|                    |                    |                  | Also see String Representation on page 9.                                                                                                                         |

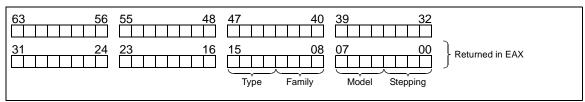

| 0000 0001h         | EAX                | 0000 0543h       | Processor Identification Bits are defined as follows:                                                                                                             |

|                    |                    |                  | 31-14: Reserved                                                                                                                                                   |

|                    |                    |                  | 13-12: CPU type = 0h<br>11-8: Family = 5                                                                                                                          |

|                    |                    |                  | 7-4: Model = 4                                                                                                                                                    |

|                    |                    |                  | 3-0: Stepping = 3                                                                                                                                                 |

|                    |                    |                  | All bits are programmable using the CPUID_TFMS MSR (see <i>CPUID Type, Family, Model, and Stepping Register</i> on page 80).                                      |

|                    | EBX                | 0000 0000h       | <b>Brand Identification</b> Bits 7-0 indicate the brand ID. This function is not supported; this register always returns 0000 0000h. All other bits are reserved. |

|                    | ECX                | 0000 0000h       | Reserved.                                                                                                                                                         |

| EAX Input<br>Value        | Output<br>Register | Output Value       | Output Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 0001h<br>(continued) | EDX                | X see below        | <b>Processor Feature Flags</b> All bits not listed are reserved. A set bit indicates the presence of a feature. A bits may be forced to 0 using the CPUID_MASK MSR (see <i>CPUID Feature Flag Mask Registers</i> on page 81 in Chapter 3, <i>Model-Specific Registers</i> ).                                                                                                                                                                                                                      |

|                           |                    |                    | Bits are defined as follows (all bits not listed are reserved):                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           |                    |                    | <ul> <li>23: MMX MMX instructions supported</li> <li>18: PSN Processor serial number</li> <li>15: CMOV CMOV supported</li> <li>11: SEP Fast System Call Extension</li> <li>8: CX8 CMPXCHG8B supported</li> <li>5: MSR Model specific regs supported</li> <li>4: TSC Time stamp counter supported</li> <li>3: PSE Page size extensions supported</li> <li>2: DE Debug extensions supported</li> <li>1: VME Virtual mode extensions supported</li> <li>0: FPU FPU instructions supported</li> </ul> |

|                           |                    | 0084 803Fh         | PSN enabled, SEP not supported, CX8 masked                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           |                    | 0080 803Fh         | PSN disabled, SEP not supported, CX8 masked                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                           |                    | 0084 813Fh         | PSN enabled, SEP not supported, CX8 unmasked                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                           |                    | 0080 813Fh         | PSN disabled, SEP not supported, CX8 unmasked                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                           |                    | 0084 883Fh         | PSN enabled, SEP supported, CX8 masked                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                           |                    | 0080 883Fh         | PSN disabled, SEP supported, CX8 masked                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                           |                    | 0084 893Fh         | PSN enabled, SEP supported, CX8 unmasked (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                           |                    | 0080 893Fh         | PSN disabled, SEP supported, CX8 unmasked                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0000 0002h                | EAX                | 0000 0000h         | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                           | EBX                | 0000 0000h         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | ECX                | 0000 0000h         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | EDX                | 0000 0000h         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

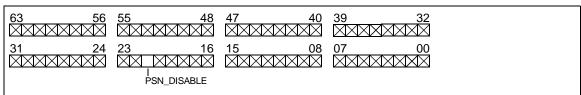

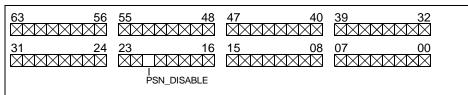

| 0000 0003h                | EAX                | 0000 0000h         | Processor Serial Number (PSN) This function returns                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                           | EBX                | <i>xxxx xxxx</i> h | the processor serial number. If PSN is disabled, the<br>returned register values are undefined. Due to technica                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | ECX                | <i>xxxx xxxx</i> h | reasons, Transmeta does not guarantee that the PSN is                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                           | EDX                | xxxx xxxxh         | truly unique, and ECX and EDX may return zero values on evaluation parts.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                           |                    |                    | OEMs may permanantly disable PSN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                           |                    |                    | Also see String Representation on page 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### Table 2: CPUID Standard Functions (Continued)

# 1.1.4 CPUID Extended Functions

## Table 3: CPUID Extended Functions

| EAX Input<br>Value | Output<br>Register | Output Value       | Output Definition                                                                                                                                                                                                                                                                                             |

|--------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8000 0000h         | EAX                | 8000 0006h         | <b>Extended Function Maximum Level</b> Maximum level supported for the extended function is 6.                                                                                                                                                                                                                |

|                    | EBX                | 6E61 7254h         | Vendor ID String The sequence EBX-EDX-ECX forms the                                                                                                                                                                                                                                                           |

|                    | ECX                | 5550 4361h         | vendor identification string. The value after reset is<br>"TransmetaCPU". This value is not programmable.                                                                                                                                                                                                     |

|                    | EDX                | 7465 6D73h         | Also see <i>String Representation</i> on page 9.                                                                                                                                                                                                                                                              |

| 8000 0001h         | EAX                | 0000 0543h         | Processor Identification Bits are defined as follows:                                                                                                                                                                                                                                                         |

|                    |                    |                    | 31-14:       Reserved         3-12:       CPU type = 0         11-8:       Family = 5         7-4:       Model = 4         3-0:       Stepping = 3         This value is not programmable.                                                                                                                    |

|                    | EBX                | 0000 0000h         | Reserved.                                                                                                                                                                                                                                                                                                     |

|                    | ECX                | 0000 0000h         | Reserved.                                                                                                                                                                                                                                                                                                     |

|                    | EDX                | 0081 893Fh         | <b>Processor Feature Flags</b> Bits are defined as follows (all bits not listed are reserved):                                                                                                                                                                                                                |

|                    |                    |                    | 23:MMXMMX instructions supported16:FCMOVFCMOV supported15:CMOVCMOV supported8:CX8CMPXCHG8B supported5:MSRModel specific regs supported4:TSCTime stamp counter supported3:PSEPage size extensions supported2:DEDebug extensions supported1:VMEVirtual mode extensions supported0:FPUFPU instructions supported |

|                    |                    |                    | This value is not programmable.                                                                                                                                                                                                                                                                               |

| 8000 0002h         | EAX                | xxxx xxxxh         | <b>Processor Name</b> The output of these function codes, when consecutively stored into memory in the order EAX-EBX-                                                                                                                                                                                         |

|                    | EBX                | xxxx xxxxh         | ECX-EDX, forms the processor name. This name may be up                                                                                                                                                                                                                                                        |

|                    | ECX                | xxxx xxxxh         | to 48 ASCII characters. Unused characters are filled with a                                                                                                                                                                                                                                                   |

|                    | EDX                | xxxx xxxxh         | value of 00h. This value is not programmable. The value is:                                                                                                                                                                                                                                                   |

| 8000 0003h         | EAX                | <i>xxxx xxxx</i> h | Transmeta(tm) Crusoe(tm) Processor TMxxxx                                                                                                                                                                                                                                                                     |

|                    | EBX                | xxxx xxxxh         | where xxxx stands for the model number, which can be up<br>to 11 characters in length and is derived from an entry in the                                                                                                                                                                                     |

|                    | ECX                | xxxx xxxxh         | OF Configuration table.                                                                                                                                                                                                                                                                                       |

|                    | EDX                | <i>xxxx xxxx</i> h | Transmeta highly recommends using this string whenever the                                                                                                                                                                                                                                                    |

| 8000 0004h         | EAX                | <i>xxxx xxxx</i> h | processor name is displayed to the end user.                                                                                                                                                                                                                                                                  |

|                    | EBX                | <i>xxxx xxxx</i> h | Also see String Representation on page 9.                                                                                                                                                                                                                                                                     |

|                    | ECX                | xxxx xxxxh         |                                                                                                                                                                                                                                                                                                               |

|                    | EDX                | <i>xxxx xxxx</i> h |                                                                                                                                                                                                                                                                                                               |

## Table 3: CPUID Extended Functions (Continued)

| EAX Input<br>Value | Output<br>Register | Output Value                        | Output Definition                                                                                                                                                                                          |

|--------------------|--------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8000 0005h         | EAX                | 0000 0000h                          | Reserved.                                                                                                                                                                                                  |

|                    | EBX                | 04FF 04FFh                          | TLB Characteristics Bits are defined as follows:                                                                                                                                                           |

|                    |                    |                                     | <ul> <li>31-24: Data TLB associativity = 4-way</li> <li>23-16: Data TLB size = 256 entries</li> <li>15-8: Code TLB associativity = 4-way</li> <li>7-0: Code TLB size = 256 entries</li> </ul>              |

|                    | ECX                | 4010 0120h                          | L1 Data Cache Characteristics Bits are defined as follows:                                                                                                                                                 |

|                    |                    |                                     | 31-24:Cache size = 64 KBytes23-16:Cache associativity = 16-way15-8:Cache lines/tag = 17-0:Cache bytes/line = 32                                                                                            |

|                    | EDX                | 4008 0140h                          | L1 Code Cache Characteristics Bits are defined as follows:                                                                                                                                                 |

|                    |                    |                                     | 31-24: Cache size = 64 KBytes                                                                                                                                                                              |

|                    |                    |                                     | 23-16: Cache associativity = 8-way                                                                                                                                                                         |

|                    |                    |                                     | 15-8: Cache lines/tag = 1                                                                                                                                                                                  |

|                    |                    |                                     | 7-0: Cache bytes/line = 64                                                                                                                                                                                 |

| 8000 0006h         | EAX                | 0000 0000h                          | Reserved.                                                                                                                                                                                                  |

|                    | EBX                | 0000 0000h                          | Reserved.                                                                                                                                                                                                  |

|                    | ECX                | TM5500:                             | L2 Cache Characteristics Bits are defined as follows:                                                                                                                                                      |

|                    |                    | 0100 4180h<br>TM5800:<br>0200 4180h | <ul> <li>31-16: Cache size = 256 KBytes (TM5500) or<br/>512 KBytes (TM5800)</li> <li>23-16: Cache associativity = 4-way</li> <li>15-8: Cache lines/tag = 1</li> <li>7-0: Cache bytes/line = 128</li> </ul> |

|                    | EDX                | 0000 0000h                          | 7-0: Cache bytes/line = 128<br>Reserved.                                                                                                                                                                   |

|                    | EDA                |                                     |                                                                                                                                                                                                            |

# 1.1.5 CPUID Transmeta-Specific Functions Frequency

### Table 4: CPUID Transmeta-Specific Extended Functions

| EAX Input<br>Value | Output<br>Register | Output<br>Value                          | Output Definition                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|--------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8086 0000h         | EAX                | 8086 0007h                               | Transmeta-Specific Extended Function Maximum Level                                                                                                                                                                                                                                                                                                                                            |

|                    |                    |                                          | Maximum level supported for the extended function is 7.                                                                                                                                                                                                                                                                                                                                       |

|                    | EBX                | 6E61 7254h                               | Vendor ID String The sequence EBX-EDX-ECX forms the                                                                                                                                                                                                                                                                                                                                           |

|                    | ECX                | 5550 4361h                               | vendor identification string. The value after reset is<br>"TransmetaCPU". This value is not programmable.                                                                                                                                                                                                                                                                                     |

|                    | EDX                | 7465 6D73h                               | Also see <i>String Representation</i> on page 9.                                                                                                                                                                                                                                                                                                                                              |

| 8086 0001h         | EAX                | 0000 0543h                               | Processor Identification Bits are defined as follows:                                                                                                                                                                                                                                                                                                                                         |

| 000000011          |                    |                                          | 31-14:       Reserved         13-12:       CPU type = 0         11-8:       Family = 5         7-4:       Model = 4         3-0:       Stepping = 3         This value is not programmable.                                                                                                                                                                                                   |

|                    | EBX                | <i>aabb ccdd</i> h<br>(see below,        | <b>Crusoe Processor Revision ID</b> The processor version and processor-mask revision. Bits are defined as follows:                                                                                                                                                                                                                                                                           |

|                    |                    | description)                             | 31-24:Major processor version23-16:Minor processor version15-8:Major processor-mask revision7-0:Minor processor-mask revision                                                                                                                                                                                                                                                                 |

|                    |                    |                                          | Display the processor revision ID and frequency as follows:                                                                                                                                                                                                                                                                                                                                   |

|                    |                    |                                          | a.b-c.d-x                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |                    |                                          | <i>a</i> , <i>b</i> , <i>c</i> , and <i>d</i> are the unsigned decimal representations of th<br>numbers <i>aa</i> h, <i>bb</i> h, <i>cc</i> h, and <i>dd</i> h (respectively) from EBX. <i>x</i><br>the frequency from ECX, also an unsigned decimal. For<br>example, if EBX is 070B_1311h (7, 11, 19, 17 decimal) and<br>ECX is 1E61h (7777 decimal), display the revision ID as<br>follows: |

|                    |                    |                                          | 7.11-19.17-7777                                                                                                                                                                                                                                                                                                                                                                               |

|                    |                    | 0104 <i>ccdd</i> h<br>0105 <i>ccdd</i> h | TM5500-TM5800 (Use the reported cache size to distinguish between TM5500 and TM5800 processors)                                                                                                                                                                                                                                                                                               |

|                    |                    | 0200 0000h                               | See CPUID function 8086 0002h, register EAX                                                                                                                                                                                                                                                                                                                                                   |

|                    | ECX                | xxxx xxxxh                               | <b>Processor Core Frequency</b> This value represents the current processor core clock frequency in MHz. Fractional frequencies may be rounded up or down. See the descriptio for EBX above for printing specifications.                                                                                                                                                                      |

|                    | EDX                | 0010 000 <i>x</i> h                      | <b>Transmeta-Specific Processor Feature Flags</b> A set bit represents the presence of a feature, while a cleared bit indicates either the absence of a feature or a reserved flag.                                                                                                                                                                                                           |

|                    |                    |                                          | <ul> <li>3: LRTI (LongRun Table Interface)</li> <li>1: LongRun<sup>™</sup> support <sup>1</sup></li> <li>0: Recovery active. If this bit is set, the processor is runnin in a failure recovery mode. This is an indication that the primary version of the Code Morphing Software in the ROM damaged and should be replaced via upgrade mechanism.</li> </ul>                                 |

| EAX Input<br>Value | Output<br>Register | Output<br>Value | Output Definition                                                                                                                                                                                                                                                                                       |

|--------------------|--------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8086 0002h         | EAX                | xxxx xxxxh      | If CPUID function 8086 0001h, register EBX reports 0200 0000h, then this register reports the Transmeta processor revision ID in hexadecimal, upper-case.                                                                                                                                               |

|                    | EBX                | aabb ccddh      | Code Morphing Software Revision The first part (the EBX                                                                                                                                                                                                                                                 |

|                    | ECX                | xxxx xxxxh      | register) consists of four 8-bit-wide numbers: for example,<br>0102 0304h represents the numbers 1, 2, 3, and 4. The<br>second part (the ECX register) consists of one 32-bit-wide<br>number.                                                                                                           |

|                    |                    |                 | Display the Code Morphing Software revision ID as follows:                                                                                                                                                                                                                                              |

|                    |                    |                 | a.b.c-d-x                                                                                                                                                                                                                                                                                               |

|                    |                    |                 | a, b, c, d, and x are the unsigned decimal representations of<br>the numbers aah, bbh, cch, ddh, and xxxx xxxxh from<br>registers EBX and ECX, respectively. For example, if EBX is<br>0509 011Fh (5, 9, 1, 31 decimal) and ECX is 0041 A028h<br>(4300840 decimal), display the revision ID as follows: |

|                    |                    |                 | 5.9.1-31-4300840                                                                                                                                                                                                                                                                                        |

|                    | EDX                | 0000 0000h      | Reserved.                                                                                                                                                                                                                                                                                               |

| 8086 0003h         | EAX                | xxxx xxxxh      | <b>Transmeta-Specific Information String</b> The output of these function codes, when consecutively stored into memory in the                                                                                                                                                                           |

|                    | EBX                | xxxx xxxxh      | - order EAX-EBX-ECX-EDX, forms a Transmeta-specific                                                                                                                                                                                                                                                     |

|                    | ECX                | xxxx xxxxh      | information string which may consist of up to 64 ASCII                                                                                                                                                                                                                                                  |

|                    | EDX                | xxxx xxxxh      | characters. Unused characters are filled with a value of 00h.<br>Also see <i>String Representation</i> on page 9.                                                                                                                                                                                       |

| 8086 0004h         | EAX                | xxxx xxxxh      |                                                                                                                                                                                                                                                                                                         |

|                    | EBX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

|                    | ECX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

|                    | EDX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

| 8086 0005h         | EAX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

|                    | EBX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

|                    | ECX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

|                    | EDX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

| 8086 0006h         | EAX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

|                    | EBX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

|                    | ECX                | xxxx xxxxh      | _                                                                                                                                                                                                                                                                                                       |

|                    | EDX                | xxxx xxxxh      |                                                                                                                                                                                                                                                                                                         |

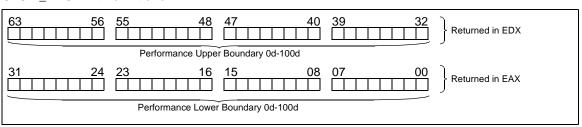

| 8086 0007h         | EAX                | xxxx xxxxh      | <b>Current Processor Core Frequency</b> This value represents<br>the current processor core clock frequency in MHz. Fractiona<br>frequencies may be rounded up or down.                                                                                                                                 |

|                    |                    |                 | This value is 0000 0000h if LongRun is not supported.                                                                                                                                                                                                                                                   |

|                    | EBX                | xxxx xxxxh      | <b>Current Processor Core Voltage</b> This value represents the current processor core voltage, in millivolts.                                                                                                                                                                                          |

|                    |                    |                 | This value is 0000 0000h if LongRun is not supported.                                                                                                                                                                                                                                                   |

|                    | ECX                | xxxx xxxxh      | <b>Current Performance Percentage</b> This value represents th current performance percentage (0-100d).                                                                                                                                                                                                 |

|                    |                    |                 | This value is 0000 0000h if LongRun is not supported.                                                                                                                                                                                                                                                   |

|                    | EDX                | 0000 0000h      | Reserved.                                                                                                                                                                                                                                                                                               |

### Table 4: CPUID Transmeta-Specific Extended Functions (Continued)

1. Disabled LongRun<sup>™</sup>. The feature flag remains set even when LongRun has been effectively disabled by programming the LONGRUN MSR to a performance percentage of 100%:100% (see LongRun<sup>™</sup> Control and Status Register on page 82).

# Detection

The recommended method for determining the frequency of the TM5500/TM5800 is to use the Transmetaspecific extended functions of the CPUID instruction, as follows:

- Executing CPUID with an input value of 8086 0001h always returns the nominal (i.e. maximum) CPU core frequency in the ECX register.

- If LongRun is enabled, the actual CPU frequency can be determined from CPUID Function 8086 0007h, EAX register. See *Processor Core Frequency* on page 15.

You can determine whether LongRun is enabled with CPUID Function 8086 0001, EDX register, bit 1 (see *Transmeta-Specific Processor Feature Flags* on page 15).

Memory and PCI bus frequencies are available in the PCI configuration registers described in Chapter 2, PCI Configuration Registers.

## Chapter 2

# **PCI** Configuration Registers

#### Note

Any future upgrade to CMS for the TM5500/TM5800 will be compatible with older OEM configuration tables and BIOS configurations. In particular, no VNB registers will change in name or function.

The Crusoe<sup>™</sup> Processor Model TM5500/TM5800 contains two sets of configuration registers accessible by software via the host CPU I/O address space: I/O-mapped registers and PCI configuration registers. I/O mapped registers provide access to the PCI configuration registers. Both sets of registers are accessible only by the host processor—they cannot be accessed by PCI bus masters.

The registers can be accessed as byte, word or dword quantities unless otherwise specified. As required by the PCI Revision 2.1 specification, all multiple-byte numeric fields use *little-endian* ordering (the least significant bit corresponds to the lowest address). Registers are classified as either read-only, read/write, read/write clear, read-after-write-once, or reserved, as defined in the following table:

#### Table 5: PCI Register Access Classifications

| Access Classification | Symbol | Read Effect                 | Write Effect                                                              |  |  |  |

|-----------------------|--------|-----------------------------|---------------------------------------------------------------------------|--|--|--|

| Read-only             | RO     | Reads contents of register. | None.                                                                     |  |  |  |

| Read/write            | R/W    | Reads contents of register. | Writes data to register.                                                  |  |  |  |

| Read/write clear      | R/WC   | Reads contents of register. | Write of 1 sets the corresponding bit to zero. Write of 0 has no effect.  |  |  |  |

| Read after write-once | R/WO   | Reads contents of register. | Write of non-zero value can only be changed by CPU RESET (i.e. not init). |  |  |  |

| Reserved              |        | Always returns 0.           | None.                                                                     |  |  |  |

The TM5500/TM5800 contains address locations in the PCI configuration space that are *reserved*. The TM5500/TM5800 responds to these addresses by completing the cycle and returning a value of 0. Software should not write to reserved configuration registers in the device-specific address region (above offset 3Fh).

Some of the PCI configuration registers listed contain *reserved bits*. Software should not modify or rely on the value of reserved bits.

# 2.1 SMRAM Differences

The Transmeta Virtual Northbridge (VNB) embedded virtual host bridge is designed to achieve maximal compatibility with the Intel 82443BX Northbridge.

The Intel 82443BX SMRAM programming model is not 100% compatible with the Transmeta SMRAM programming model. The differences stem from the fact that the Intel 82443BX Northbridge supports split code/data accesses while the CPU executes in SMM mode, whereas the Transmeta VNB does not. As a result, the Transmeta northbridge has to relocate the video frame buffer out of the Compatibility SMRAM region (located in A0000h to BFFFFh) into a user-specified virtual video window.

The following table summarizes the resulting SMRAM differences between a Intel 82443BX Northbridge and the Transmeta Virtual Northbridge.

Table 6: SMRAM Differences Between 82443BX and Transmeta VNB

|            | Intel 82443BX Northbridge                                                                       |                  | Transmeta Virtual Northbridge                                                         |                                                                                                                  |  |

|------------|-------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

|            | Transaction                                                                                     | DRAM             | Transaction                                                                           | DRAM                                                                                                             |  |

| Compatible | A0000h to BFFFFh                                                                                | A0000h to BFFFFh | A0000h to BFFFFh                                                                      | TOM+896K to TOM+1024K                                                                                            |  |

| A region   | <ul> <li>not write-back<br/>cacheable</li> <li>optional split<br/>code/data accesses</li> </ul> |                  | <ul> <li>write-back<br/>cacheable</li> <li>no split code/data<br/>accesses</li> </ul> | <ul> <li>DMA accesses must be<br/>directed to physical<br/>DRAM rather than SMM<br/>Transaction space</li> </ul> |  |

| High       | 100A0000h to 100BFFFFh                                                                          | A0000h to BFFFFh | TOM+896K to TOM+1024K                                                                 |                                                                                                                  |  |

| H region   | write-back cacheable                                                                            |                  | DMA accesses must be directed to physical DRA rather than SMM Transaction space       |                                                                                                                  |  |

| Extended   | TOM-TSEG_SZ+256M                                                                                | TOM-TSEG_SZ to   | TOM to TOM+896K                                                                       |                                                                                                                  |  |

| T region   | to TOM 256M TOM                                                                                 |                  | write-back cacheable                                                                  |                                                                                                                  |  |

|            | write-back cacheable                                                                            |                  |                                                                                       |                                                                                                                  |  |

# 2.2 I/O Mapped Registers

The TM5500/TM5800 Virtual Northbridge provides two I/O-mapped registers that in turn provide access to all other PCI configuration registers: the Configuration Address Register (CONFADDR) and the Configuration Data Register (CONFDATA). A third I/O mapped register (PM\_CR2) is used to disable PCI bus master activity prior to entering a CPU stop clock state.

The I/O addresses and bit definitions for these registers are listed in the following sections.

| Table 7: | I/O Mapped Register Summary |

|----------|-----------------------------|

| Table II | i e mappea regiotor earmary |

| I/O<br>Location    | Register Description                   | Register<br>Name | Size    | Access           | Default Value | Page |

|--------------------|----------------------------------------|------------------|---------|------------------|---------------|------|

| 0022h <sup>1</sup> | ACPI Power Management Control Register | PM_CR2           | 8 Bits  | R/W              | 00h           | 21   |

| 0CF8h              | Configuration Address Register         | CONFADDR         | 32 Bits | R/W (DWORD only) | 0000 0000h    | 22   |

| 0CFCh              | Configuration Data Register            | CONFDATA         | 32 Bits | R/W              | 0000 0000h    | 23   |

1. This value is programmable via the ACPI Power Management Control Address Register (PM\_CR2\_ADDR).

# ACPI Power Management Control Register

| I/O Location       | Register Name | Size   | Access | Default Value |

|--------------------|---------------|--------|--------|---------------|

| 0022h <sup>1</sup> | PM_CR2        | 8 Bits | R/W    | 00h           |

1. This value is programmable via the ACPI Power Management Control Address Register (PM\_CR2\_ADDR).

The PM\_CR2 register is used to disable the PCI arbiter to prevent any external bus masters from acquiring the PCI bus. Any currently running PCI cycles terminate properly.

Accesses to this register are controlled by the power management control registers:

- PM\_CR2\_ADDR (offset 78-79h): This register specifies the address where the PM\_CR2 register is mapped into I/O space. It defaults to 22h, which is compatible to the Intel 82443BX Northbridge and PIIX4 Southbridge.

- PM\_CR.PM\_CR2\_EN (offset 7Ah, bit 6):