# WD16 MICROCOMPUTER

(Using MCP 3-Chip Microprocessor Set)

**PROGRAMMER'S REFERENCE MANUAL**

## **WD1600 MICROCOMPUTER**

(Using MCP 3-Chip Microprocessor Set)

**PROGRAMMER'S REFERENCE MANUAL**

**4 OCTOBER 1976**

© 1977-WESTERN DIGITAL CORP. NEWPORT BEACH, CA. 92663

## TABLE OF CONTENTS

|                                          | PAGE |

|------------------------------------------|------|

| CHAPTER ONE - GENERAL                    | 1.1  |

| Abbreviations                            |      |

| Processor Status Word                    |      |

| Registers                                |      |

|                                          |      |

| CHAPTER TWO - INTRODUCTION               | 2.1  |

| Addressing Modes                         |      |

| Stack Operations                         |      |

| Interrupt Lines                          |      |

| Priority Mask                            |      |

| External Status Register                 |      |

| Power Up Options                         |      |

| Halt Options                             |      |

| User Bootstrap Routine                   |      |

| System Error Traps                       |      |

| Reserved Core Locations                  |      |

| CUADERD BUDER OF CODEC                   | 3.1  |

| CHAPTER THREE - OP CODES                 | 2.1  |

| Format 1 Op Codes                        |      |

| Format 2 Op Codes                        |      |

| Format 4 On Codes                        |      |

| Format 4 Op Codes                        |      |

| Format 5 Op Codes                        |      |

| Format 7 On Codes                        |      |

| Format 7 Op Codes                        |      |

| Format 8 Op Codes                        |      |

| Format 9 Op Codes<br>Format 10 Op Codes  |      |

| Format 11 Op Codes                       |      |

| rormac ir op codes                       |      |

| APPENDIX A - Numeric Op Code Table       | Al   |

| APPENDIX B - Assembler Notes             | Bl   |

| APPENDIX C - Programming Notes           | Cl   |

| APPENDIX D - Microm State Code Functions | Dl   |

| APPENDIX E - Op Code Timings             | E1   |

|                                          |      |

#### CHAPTER 1 - GENERAL

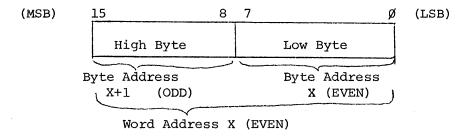

The WD1600 microcomputer is a 16 bit machine with both word and byte addressing, an automatic push down hardware stack, vectored interrupt handling, eight 16 bit registers, and PC relative addressing. A byte is defined as 8 bits, and a word is defined as 2 bytes. A memory address increment of one is an increment of 1 byte. An address increment of two is an increment of 1 word. Word addresses always start on even bytes. For any memory location the even byte is the least significant byte. Bit 0 is defined as the LSB of a memory location.

Unless otherwise stated, word addressing is implied. All addresses and op codes are done in hex unless otherwise stated. All hex numbers are enclosed within double quotes.

## LEGEND OF ABBREVIATIONS

REG = Register

SRC = Source Address

(SRC) = Contents of Source Address

DST = Destination Address

(DST) = Contents of Destination Address

$(SRC)_B$  = Contents of Source Byte Address

$(DST)_B$  = Contents of Destination Byte Address

$\overline{x}$  = Ones Complement of X

$\rightarrow$  = Twos Complement of X

$\Delta$  = Logical And

∇ = Logical Or

@ = Indirect

↓ = Push

$\uparrow$  = Pop

← = Destination Direction

+ = Addition

- = Subtraction

\* = Multiplication

/ = Division

: = Double Precision Chain Link

## PROCESSOR STATUS WORD

| A 16 bit Processor | Status (PS) | Word | exists. | The format | is as follows: |

|--------------------|-------------|------|---------|------------|----------------|

|                    | 7           |      |         |            |                |

| Ext. Status Reg.   | ALU         | N    | ZVC     |            |                |

Where bits 8-15 are the contents of the external status register (see chapter 2), bits 4-7 are the status of the microprocessor ALU flags, and bits  $\emptyset$  -3 are the status of the condition indicators at the time the PS is formed. The ALU flags are of no use or concern to the programmer. They are stored along with the condition indicators automatically as a function of the micro-op. The four condition flags are updated during the execution of most op codes, and are used by the branch instructions to test for valid branch conditions. The exact status of each indicator is defined along with the descriptions of individual op codes in chapter 3. In general, however, the indicators are set by the following conditions:

N = set if the MSB of the result is set.

Z = set if the result is zero.

V = set if arithmetic overflow (underflow) occurs during addition (subtraction). Set to exclusive -or of N and C indicators otherwise.

C= set if carry (borrow) occurs during addition (subtraction). Also set to last bit shifted out during a shift operation.

## REGISTERS

There are 8 registers in the WD1600. All are 16 bits long. Six can be used as either accumulators or index registers, one is the stack pointer (SP), and one is the program counter (PC). The registers are numbered RØ - R7 with R6 = SP and R7 = PC. The register set is usually referred to in the following manner: RØ - R5, SP, PC.

## CHAPTER TWO - INTRODUCTION

#### ADDRESSING MODES

In general there are 8 addressing modes for both source and destination addressing. Not all op codes accept all 8 modes (see chapter 3). Those that do use the following format: 3 bits for the index register (RØ - R5, SP, PC) and 3 bits for the mode. The mode bits are the upper 3 bits of the 6 bit set. The modes are defined below. The numbers in parenthesis refer to notes that follow the definitions.

\_\_\_\_\_

| MODE | NAME SY                      | MBOLIC  | DESCRIPTION                                                                        |

|------|------------------------------|---------|------------------------------------------------------------------------------------|

| ø    | Direct Register              | REG     | REG is or contains operand.                                                        |

| 1    | Indirect Register            | @REG    | REG contains address of operand.                                                   |

| 2    | Auto-increment               | (REG)+  | REG contains address of operand. REG is post-incremented (1).                      |

| 3    | Auto-increment<br>deferred   | @(REG)+ | REG contains address of add-<br>ress of operand. REG is post-<br>incremented by 2. |

| 4    | Auto-decrement               | - (REG) | REG is predecremented (1). REG then contains address of operand.                   |

| 5    | Auto-decrement<br>deferred   | @-(REG) | REG is predecremented by 2. REG then contains address of address of operand.       |

| 6    | Indexed register             | X(REG)  | Contents of REG plus X is address of operand (2).                                  |

| 7    | Indexed register<br>deferred | @X(REG) | Contents of REG plus X is address of address of operand (2).                       |

\_\_\_\_\_

NOTE 1: For word operations the increment/decrement is 2. For byte operations the increment/decrement is 1 unless the index register is SP or PC. In this case the increment/decrement is always 2.

NOTE 2: The contents of REG remain unchanged.

When using PC as the index register the assembler accepts the following 4 formats in place of the formats mentioned above for ease of programming.

| MODE | NAME              | SYMBOLIC | DESCRIPTION                                                         |

|------|-------------------|----------|---------------------------------------------------------------------|

| 2    | Immediate         | #N       | Operand N follows op code.                                          |

| 3    | Absolute          | @#N      | Address of operand is N and it                                      |

|      |                   |          | follows the op code in memory.                                      |

| 6    | Relative          | A        | PC relative offset to address A, which contains operand, follows    |

|      |                   |          | op code.                                                            |

| 7    | Relative deferred | A9       | PC relative offset to address A, which contains address of operand, |

|      |                   |          | follows the op code.                                                |

The 8 modes are referred to as Source Mode Ø to Source Mode 7 (SMØ -SM7) and Destination Mode Ø to Destination Mode 7 (DMØ -DM7). In Chapter 3 these modes are referred to in general terms during op code definitions as "SRC" and "DST".

#### STACK OPERATIONS

Although automatic stack operations are provided for, no specific area of memory is set aside for the stack. The user must assign an area of memory by loading the stack pointer with the top address of the designated stack area. Stack operations are pushdown pop-up operations with predecrements and post-increments of SP. Stack operations may also be executed explicitly by using SP as an index register with op codes that allow SMØ - SM7 and/or DMØ - DM7 addressing.

When pushing the PS the word is formed just prior to the push. When popping the PS the condition indicators and interrupt enable flag are set to the status of the appropriate bits in the popped PS. Other than that the popped PS goes nowhere. Unless otherwise stated popping the PS from the stack performs the above mentioned operations and only the above mentioned operations.

When pushing the PC onto the stack PC will be set to the address of the op code that follows the op code that caused the push. There are cases where some op code formats can alter this rule. They generally involve advanced programming techniques. A few are mentioned in appendix C. In particular, system errors that are caused by programming errors and not real time error conditions will push a PC that points to the op code that follows the op code that caused the error. The stored PC must be decremented by two to get the address of the offending op code.

#### INTERRUPT LINES

There are 4 interrupt lines available to the system. They are labeled  $I\emptyset$  - I3. These lines are assigned functions as follows:

IØ = Vectored interrupt line

Il = Nonvectored interrupt line

I2 = Enable/disable for IØ and Il.

I3 = Halt switch

The priority among the lines is as follows:

I3, I1 $\Delta$ I2, I $\emptyset$  $\Delta$ I2.

Note that I3 is always enabled. Note also that the nonvectored interrupt has priority over the vectored interrupt. The system is currently set up so that power fail and a real time clock can be assigned to I1, and up to 16 devices assigned to IØ.\* The two interrupts operate as follows:

A) Nonvectored Interrupt (I1)

PS and PC are pushed onto the stack. I2 is disabled. The external status register is tested for a power fail. If power fail is true PC is fetched from location "14". If power fail is false PC is fetched from location "2A", and a microm state code is transmitted to clear the line clock (see appendix D).

B) Vectored Interrupt (IØ)

PS and PC are pushed onto the stack. I2 is disabled. An Interrupt Acknowledge is executed, and the device code of the interrupting device is read in and stripped to bits 1-4. PC is fetched from location \*NOTE: Although only a 4 bit device code is currently used, a minor microm change can allow a device code of from 1-15 bits.

"28" and the device code is added to it. The contents of this intermediate location are read in and added to PC to form the final address. Each intermediate location is a table entry that contains the PC relative offset from the start of the device handler routine to itself. The absolute address of the start of the table is in location "28".

## PRIORITY MASK

Associated with the interrupts is a priority interrupt mask. This is a 16 bit mask where each bit position represents a priority level. Each priority level can be assigned to one or more devices. A one in any bit position can represent an interrupt enable or disable for its associated devices as the hardware dictates. The SAVS, RSTS, and MSKO op codes each alter the mask. When the mask is altered it is written into location "2E" for storage. While the mask is on the bus a microm state code is transmitted (see appendix D) to signal the I/O devices that a new mask is being transmitted. Each device can then look at its assigned mask bit while the memory write to location "2E" is taking place. Whether or not the mask feature is actually used by the I/O devices in no way alters the operations of the op codes mentioned above.

## EXTERNAL STATUS REGISTER

As a part of the hardware external to the CPU the External Status Register supplies the CPU, upon demand, with information about the status of certain hardware areas. This register is gated onto the bus when its associated microm state code is present (see appendix D). The format of the register is as follows:

Bit 7 = Power Fail Status

Bit 6 = Bus Error (Time Out) Status

Bit 5 = Parity Error Status

Bit 4 = I2 Interrupt Line Status

Bit 3 = Halt Option Jumper #2

Bit 2 = Halt Option Jumper #1

Bit 1 = Power Up Option Jumper #2

Bit Ø = Power Up Option Jumper #1

Bits 8-15 are don't care. Bits 5-7 are real time error conditions that also generate a system reset (see next section). Bit 4 is the interrupt enable status. The jumpers can be logic units, switches, or hard wired jumpers as the user wishes. The various options associated with the 4 jumpers are discussed later.

#### POWER UP OPTIONS

A system reset indicate one of 4 conditions: power fail, bus error, parity error, or power up. There are 2 levels of power fail possible in this system (see appendix C): minor and major. Only a major power fail generates a system reset. Both types set bit 7 in the External Status Register. The following steps are performed after a system reset.

- Al) Trace and wait flags are reset if on.

- A2) The external Status Register is fetched.

- A3) The Line-clock-clear state code is transmitted.

- A4) I2 is reset.

- A5) If power fail bit is set go to D1.

- A6) If bus error bit is set go to C1.

- A7) If parity error bit is set go to B1.

- A8) Go to D2 otherwise.

- Bl) Push PS and PC onto stack.

- B2) Fetch PC from location "12" and begin execution.

- C1) Push PS and PC onto stack.

- C2) Fetch PC from location "18" and begin execution.

- D1) Wait until power fail status =  $\emptyset$ .

- D2) Send a system reset microm state code.

- D3) Wait 300 cycles.

- D4) Execute power up option 1,2,3 or 4 per jumpers.

For a proper initial power up either bit 7 must be set or bits 5-7 must be reset when the system reset line is released.

The 4 power up options are as follows:

| JUMPERS | OPERATION                                                                          |

|---------|------------------------------------------------------------------------------------|

| ØØ      | Execute user bootstrap routine.                                                    |

| Ø1      | Pick up RØ-R5, SP, PC, and PS from memory locations $\emptyset$ -"l $\emptyset$ ". |

| 1.Ø     | Execute selected halt option.                                                      |

| 11      | Fetch PC from location "16".                                                       |

|         | •                                                                                  |

#### HALT OPTIONS

When the halt switch (I3) is set during program execution one of 4 halt options is selected. The halt op code\* and power up option #2 also select the halt option specified. The options are as follows:

| JUMPERS  | OPERATION                                                                                                                     |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| ØØ<br>Ø1 | Execute user bootstrap routine.                                                                                               |

| μī       | Save RØ-R5,SP,PC and PS in memory locations $\emptyset$ -"l $\emptyset$ ". Wait until I3 = $\emptyset$ , then restore RØ-     |

| lø       | R5,SP,PC and PS from memory locations $\emptyset$ -"l $\emptyset$ ".<br>Lock up processor (requires a system reset to clear). |

| 11       | Fetch new PC from location "16".                                                                                              |

\*NOTE: Conditional. See Chapter 3.

## USER BOOTSTRAP ROUTINE

When the user bootstrap routine is selected as an option the system creates the starting address by placing address "C $\emptyset\emptyset\emptyset$ " in PC and then replacing bits 8-13 with the contents of the 6 bit External Address Register. This register is gated in with a microm status code (see appendix D).

It allows the user 64 different starting addresses in the range "CØØØ" to "FFØØ".

## SYSTEM ERROR TRAPS

With the exception of the major power fail error that is a function of a system reset, all error conditions perform a common routine as outlined below. A non-vectored interrupt and some op codes also use this routine. The numbers in parenthesis refer to notes that follow the table.

- 1) PS is pushed onto the stack

- 2) PC is pushed onto the stack

- 3) PC is fetched from location X where "X" is from the following table

- (1)(2)(3) "12" for bus error PC

- (1)(2)(3) "14" for nonvectored interrupt power fail PC

- (1)(2)(3) "18" for parity error PC

- (1)(2)(3) "lA" for reserved op code error PC

- (1)(2)(3) "1C" for illegal op code format error PC

- (1)(2)(3) "lE" for XCT error PC

- (1)(2) "2Ø" for XCT trace PC

- (1)(2)(3) "2A" for nonvectored interrupt PC

- (1)(2) "2C" for BPT PC

- NOTE 1: wait flag reset if on

- NOTE 2: trace flag reset if on

- NOTE 3: interrupt enable (I2) reset if on

The meaning of the wait and trace flags is discussed in chapter 3. Note that the nonvectored interrupt power fail PC is a minor power fail condition, not a major one. See appendix C for full detail on how to include both major and minor power fail conditions in the hardware.

## RESERVED CORE LOCATIONS

The following is a complete list of memory locations that are reserved for specific system functions or options. Byte addresses are given.

| LOCATIONS   | RESERVED FUNCTION                                |

|-------------|--------------------------------------------------|

|             |                                                  |

| Ø - "11"    | RØ - R5, SP, PC and PS for power up/halt options |

| "12" - "13" | bus error PC                                     |

| "14 - "15"  | nonvectored interrupt power fail PC              |

| "16" - "17" | power up/halt option power restore PC            |

| "18" - "19" | parity error PC                                  |

| "1A" -"1B"  | reserved op code PC                              |

| "1C" - "1D" | illegal op code format PC                        |

| "1E" - "1F" | XCT error PC                                     |

| "2Ø" - "21" | XCT trace PC                                     |

| "22" - "23" | SVCA table address                               |

| "24" - "25" | SVCB PC                                          |

| "26" - "27" | SVCC PC                                          |

| "28"- "29"  | vectored interrupt (IØ) table address            |

| "2A" - "2B" | nonvectored interrupt (I1) PC                    |

| "2C" - "2D" | BPT PC                                           |

| "2E" - 2F"  | I/O priority interrupt mask                      |

| "3Ø" – "3F" | reserved for floating point option               |

| ·           | 5                                                |

## CHAPTER 3 - OP CODES

This chapter is divided into a number of sections, each representing one class of op codes. At the beginning of each section there is a detailed description of the format for that class. A list of op codes and their base numeric values, less arguments, is also included. A detailed description of each op code in the class then follows.

## FORMAT 1 OP CODES

Single word - no arguments

| 15 | 12 | 11 8 | 7 | 4 | 3 0 |

|----|----|------|---|---|-----|

|    | Ø  | Ø    |   | Ø | OPC |

There are 16 op codes in this class representing op codes "ØØØØ" to "ØØØF". Each is a one word op code with no arguments with the exception of the SAVS op code which is a two word op code. Word two of the SAVS op code is the I/O priority interrupt mask. The op codes and their mnemonics are:

| BASE OP CODE | MNEMONIC                          |

|--------------|-----------------------------------|

|              |                                   |

| ØØØØ         | NOP                               |

| ØØØ1         | RESET                             |

| ØØØ2         | IEN                               |

| ØØØ3         | IDS                               |

| ØØØ4         | HALT                              |

| øøø5         | XCT                               |

| øøø6         | BPT                               |

| ØØØ7         | WFI                               |

| øøø8         | RSVC                              |

| øøø9         | RRTT                              |

| ØØØA         | SAVE                              |

| ØØØB         | SAVS                              |

| øøøc         | REST                              |

| ØØØD         | RRTN                              |

| ØØØE         | RSTS                              |

| ØØØF         | RTT                               |

| NOP          | NO OPERATION                      |

| FORMAT:      | NOP                               |

| FUNCTION:    | No operations are performed       |

| INDICATORS:  | Unchanged                         |

| RESET        | I/O RESET                         |

| FORMAT:      | RESET                             |

| FUNCTION:    | An I/O reset pulse is transmitted |

| INDICATORS:  | Unchanged                         |

IEN INTERRUPT ENABLE

FORMAT:

IEN

FUNCTION:

The interrupt enable (I2) flag is set. Allows one more instruction to execute before inter-

rupts are recognized.

INDICATORS:

Unchanged

IDS

INTERRUPT DISABLE

FORMAT:

IDS

FUNCTION:

The interrupt enable (I2) flag is reset. This instruction can honor interrupts, but the I2 bit in the PS that is stored on the stack

is reset if an interrupt occurs.\*

INDICATORS:

Unchanged

\*NOTE: On some machines I2 will be set or reset during the IEN or IDS. If so the change will be valid immediately, not one op code later.

HALT HALT

FORMAT:

דאדת

FUNCTION:

Tests the status of the Power Fail bit in the external status register. If the bit is set it is assumed that the HALT occured in a power fail routine, and the following operations occur:

- 1) The interrupt enable (I2) flag is reset

- 2) The CPU waits until the Power Fail bit is reset

- 3) PC is fetched from location "16", and program execution begins at this new location

If the power fail bit is reset then the CPU waits until the halt switch (I3) is set. At that time the selected halt option (see chapter 2) is executed.

The interrupt enable flag is also reset.

INDICATORS:

Unchanged

XCT

## EXECUTE SINGLE INSTRUCTION

FORMAT:

OPERATION:

XCT

$PC \leftarrow @SP, SP \uparrow$  $PS \leftarrow @SP, SP \uparrow$

Trace flag set, execute op code

$\forall$  SP, @SP  $\leftarrow$  PS  $\forall$  SP, @SP  $\leftarrow$  PC Trace flag reset

PC ←(loc "2Ø") if no error PC ←(loc "lE") if error

FUNCTION:

PC and PS are popped from the stack, but I2 is not altered. The trace flag, which disables all interrupts except I3, is set. The op code is executed. PS and PC are pushed back onto the stack, and PC is fetched from location "20". The trace flag is reset. If the program tries to execute a HALT, XCT, BPT, or WFI the attempt is aborted, PS and PC are

pushed onto the stack, and PC is fetched from location "lE" instead.

| INDICATORS:   | Depends upon executed op code                                                                                                                |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| BPT           | BREAKPOINT TRAP                                                                                                                              |

| FORMAT:       | врт                                                                                                                                          |

| OPERATION:    | ↓SP, @SP ←PS                                                                                                                                 |

|               | ↓SP, @SP ←PC                                                                                                                                 |

|               | PC ← (loc "2C")                                                                                                                              |

| FUNCTION:     | PS and PC are pushed onto the stack. PC is fetched from location "2C"                                                                        |

| INDICATORS:   | Unchanged                                                                                                                                    |

| WFI           | WAIT FOR INTERRUPT                                                                                                                           |

|               | MINT                                                                                                                                         |

| FORMAT:       | WFI                                                                                                                                          |

| FUNCTION:     | The CPU loops internally without accessing the data bus until an interrupt occurs. Program execution continues with the op code that follows |

|               | the WFI after the interrupt has been serviced.                                                                                               |

|               | The interrupt enable flag is also set.                                                                                                       |

| TNIDTCA MODC. | Unchanged                                                                                                                                    |

| INDICATORS:   | Olichangeu                                                                                                                                   |

| SAVE          | SAVE REGISTERS                                                                                                                               |

| FORMAT:       | SAVE                                                                                                                                         |

| OPERATION:    | ↓ SP , @SP + R5                                                                                                                              |

|               | ↓SP, @SP ← R4                                                                                                                                |

|               | $\downarrow \text{SP}$ , $\text{@SP} \leftarrow \text{R3}$                                                                                   |

|               | ♦SP, @SP + R2                                                                                                                                |

|               | ↓SP, @SP ← R1                                                                                                                                |

|               | ↓SP, @SP ← RØ                                                                                                                                |

| FUNCTION:     | Registers R5 to RØ are pushed onto the stack.                                                                                                |

| INDICATORS:   | Unchanged.                                                                                                                                   |

| SAVS          | SAVE STATUS                                                                                                                                  |

| TONKS M       | CALLC MACK                                                                                                                                   |

| FORMAT:       | SAVS MASK                                                                                                                                    |

| OPERATION:    | SAVE<br>√SP, @SP ← (loc "2E")                                                                                                                |

|               | (loc "2E") ← (loc "2E") ▼ mask                                                                                                               |

|               | MSKO                                                                                                                                         |

|               | MSRO<br>IEN                                                                                                                                  |

| TODA 5        |                                                                                                                                              |

| FORMAT:       | Registers R5 to RØ and the priority mask in location "2E" are pushed onto the stack. The old and new masks                                   |

|               | are ORED together and placed in location "2E".                                                                                               |

|               | A mask out state code (see appendix D) is transmitted                                                                                        |

|               | and the interrupt enable (I2) flag is set.                                                                                                   |

| INDICATORS:   | Unchanged                                                                                                                                    |

| INDICATORS:   | onenanged                                                                                                                                    |

| REST          | RESTORE REGISTERS                                                                                                                            |

| FORMAT:       | REST                                                                                                                                         |

| OPERATION:    | $R\emptyset \leftarrow QSP$ , $SP \uparrow$                                                                                                  |

|               | Rl ← @SP, SP ↑                                                                                                                               |

|               |                                                                                                                                              |

R2 + @SP, SP \*

$R3 \leftarrow @SP, SP \uparrow$  $R4 \leftarrow @SP, SP \uparrow$  $R5 \leftarrow @SP, SP \uparrow$

FUNCTION: Registers Rg to  $\ensuremath{\text{R}}\xspace5$  are popped from the stack, INDICATORS: Unchanged

| RTT          | RETURN FROM TRAP                                |

|--------------|-------------------------------------------------|

| FORMAT:      | RTT                                             |

| OPERATION:   | PC ←@SP, SP↑                                    |

|              | PS ←@SP, SP↑                                    |

| FUNCTION:    | PC and PS are popped from stack                 |

| INDICATORS:  | N = Set per PS bit 3                            |

|              | Z = Set per PS bit 2                            |

|              | V = Set per PS bit 1                            |

|              | C = Set per PS bit Ø                            |

| RRTN         | RESTORE AND RETURN FROM SUBROUTINE              |

| FORMAT:      | RRTN                                            |

| OPERATION:   | REST                                            |

| or Brutton.  | PC ← @SP, SP↑                                   |

| FUNCTION:    | Registers RØ to R5 and PC are popped            |

|              | from the stack                                  |

| INDICATORS:  | Unchanged                                       |

| RRTT         | RESTORE AND RETURN FROM TRAP                    |

| FORMAT:      | RRTT                                            |

| OPERATION:   | REST                                            |

| or Bittizon. | RTT                                             |

| FUNCTION:    | Registers RØ to R5, PC and PS are popped        |

|              | from the stack.                                 |

| INDICATORS:  | Set per PS bits ∅ - 3                           |

| RSTS         | RESTORE STATUS                                  |

| FORMAT:      | RSTS                                            |

| OPERATION:   | (LOC "2E") ← @SP, SP↑                           |

|              | MSKO                                            |

|              | REST                                            |

|              | RTT                                             |

| FUNCTION:    | The priority mask is popped from the stack and  |

|              | restored to locaton "2E". A MASK OUT state code |

|              | (See Appendix D) is transmitted. Registers RØ   |

|              | to B, PC and PS are popped from the stack.      |

| INDICATORS:  | Set per PS bits Ø - 3                           |

| RSVC         | RETURN FROM SUPERVISOR CALL (B or C)            |

| FORMAT:      | RSVC                                            |

| OPERATION:   | REST                                            |

|              | SP                                              |

|              | RTT                                             |

|              |                                                 |

FUNCTION:

INDICATORS:

Registers  $R\beta$  to R5 , PC and PS are popped from the stack with the saved SP bypassed.

Set per PS bits  $\emptyset$  - 3

## FORMAT 2 OP CODES

## SINGLE WORD - 3 BIT REGISTER ARGUMENT

| 15 12 | 11 8 | 7 3 | 2 0 |

|-------|------|-----|-----|

| ø     | Ø    | OPC | REG |

There are 4 op codes in this class representing op codes " $\emptyset\emptyset$ 1 $\emptyset$ " to " $\emptyset\emptyset$ 2F". Each is a one word op code with a single 3 - bit register argument. The op codes and their mnemonics are:

| BASE OP CODE                 | MNEMONIC                                                                                                                                                                                                                    |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ØØ1Ø<br>ØØ18<br>ØØ2Ø<br>ØØ28 | IAK<br>RTN<br>MSKO<br>PRTN                                                                                                                                                                                                  |

| IAK                          | INTERRUPT ACKNOWLEDGE                                                                                                                                                                                                       |

| FORMAT: FUNCTION:            | IAK REG An interrupt acknowledge (READ and IACK) is executed, and the 16 bit code that is returned is placed in REG unmodified. Used with the nnnvectored interrupt when the user does not wish to use the vectored format. |

| INDICATORS:                  | Unchanged                                                                                                                                                                                                                   |

| RTN                          | RETURN FROM SUBROUTINE                                                                                                                                                                                                      |

| FORMAT: OPERATION:           | RTN REG<br>PC ← REG<br>REG ← @SP,SP↑                                                                                                                                                                                        |

| FUNCTION:                    | The linkage register is placed in PC and the saved linkage register is popped from the stack. The register used must be the same one that was used for the subroutine call.                                                 |

| INDICATORS:                  | Unchanged                                                                                                                                                                                                                   |

| MSKO                         | MASK OUT                                                                                                                                                                                                                    |

| FORMAT: OPERATION:           | MSKO REG<br>(LOC "2E" ) ← REG<br>MSKO                                                                                                                                                                                       |

| FUNCTION:                    | The contents of REG are written into location "2E" and a MASK OUT state code (see appendix D) is transmitted.                                                                                                               |

| INDICATORS:                  | Unchanged                                                                                                                                                                                                                   |

| PRTN                         | POP STACK AND RETURN                                                                                                                                                                                                        |

| FORMAT: OPERATION:           | PRTN REG TMP ← @SP SP ← SP+(TMP*2) RTN REG                                                                                                                                                                                  |

FUNCTION:

Twice the value of the top word on the stack is added to SP, and a standard RTN call is then executed.

INDICATORS:

Unchanged

## FORMAT 3 OP CODES

## SINGLE WORD - 4 BIT NUMERIC ARGUMENT

| 15 | 12 | 11 | 8 | 7 | 4   | 3  | Ø  |

|----|----|----|---|---|-----|----|----|

| Ø  |    | 1  | Ø |   | OPC | Al | RG |

There is only one op code in this class representing op codes " $\emptyset\emptyset3\emptyset$ " to " $\emptyset\emptyset3F$ ". It is a one word op code with a 4-bit numeric argument.

| BASE OP CODE | MNEMONIC                                                                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|

| ØØ3Ø         | LCC                                                                                                                            |

| LCC          | LOAD CONDITION CODES                                                                                                           |

| FORMAT:      | LCC ARG                                                                                                                        |

| FUNCTION:    | The 4 indicators are loaded from bits $\emptyset$ -3 of the op code as specified.                                              |

| INDICATORS:  | <pre>N = Set per bit 3 of op code Z = Set per bit 2 of op code V = Set per bit 1 of op code C = Set per bit Ø of op code</pre> |

## FORMAT 4 OP CODES

## SINGLE WORD - 6 BIT NUMERIC ARGUMENT

| 15 12 | 11 8 | 7 6 | 5 Ø |

|-------|------|-----|-----|

| Ø     | 18   | OPC | ARG |

There are 3 op codes in this class representing op codes " $\emptyset\emptyset4\emptyset$ " to " $\emptyset\emptysetFF$ ". All 3 are supervisor calls . All 3 are one word op codes with a 6-bit numeric argument.

| BASE OP CODE         | MNEMONIC                                                                                                                                                                                                                                                                                                                                  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ØØ4Ø<br>ØØ8Ø<br>ØØCØ | SVCA<br>SVCB<br>SVCC                                                                                                                                                                                                                                                                                                                      |

| SVCA                 | SUPERVISOR CALL "A"                                                                                                                                                                                                                                                                                                                       |

| FORMAT: OPERATION:   | SVCA ARG<br>↓SP, @SP ← PS; ↓ SP, @SP← PC<br>PC ← (LOC "22") + (ARG *2)<br>PC ← PC + @PC                                                                                                                                                                                                                                                   |

| FUNCTION:            | PS and PC are pushed onto the stack. The contents of location "22" plus twice the value of the argument (which is always positive) is placed in PC to get the table address. The contents of the table address is added to PC to get the final destination address. Each table entry is the relative offset from the start of the desired |

| INDICATORS:          | routine to itself.<br>Unchanged                                                                                                                                                                                                                                                                                                           |

| SVCB<br>SVCC         | SUPERVISOR CALL "B" SUPERVISOR CALL "C"                                                                                                                                                                                                                                                                                                   |

| FORMAT:              | SVCB ARG SVCC ARG                                                                                                                                                                                                                                                                                                                         |

| OPERATION:           | TMPA ← SP<br>↓SP, @SP ← PS<br>↓SP, @SP ← PC                                                                                                                                                                                                                                                                                               |

|                      | TMPB ←SP<br>→SP, @SP ← TMPA<br>SAVE<br>R1 ← TMPB                                                                                                                                                                                                                                                                                          |

|                      | R5 ← ARG*2 PC ← (LOC "24") if SVCB PC ← (LOC "26") if SVCC                                                                                                                                                                                                                                                                                |

| FUNCTION:            | PS and PC are pushed onto the stack. The value                                                                                                                                                                                                                                                                                            |

of SP at the start of op code execution is the pushed followed by registers R5 to RØ. The address of the saved PC is placed in R1, and twice the value of the 6-bit positive argument is placed in R5.

PC is loaded from location "24" for SVCB or "26" for SVCC. Unchanged.

INDICATORS:

## FORMAT 5 OP CODES

## SINGLE WORD - 8 BIT SIGNED NUMERIC ARGUMENT

| 15 |     | 8 | 7 | Ø            |  |

|----|-----|---|---|--------------|--|

|    | OPC |   |   | DISPLACEMENT |  |

There are 15 op codes in this class representing op codes "Ø1ØØ" to "Ø7FF" and "8ØØØ" to "87FF". All are branches with a signed 8 bit displacement that represents the word offset from PC (which points to the op code that follows) to the desired branch location. The op codes consist on one unconditional branch, 8 signed conditional branches, and 6 unsigned conditional branches. No op code in this class modifies any of the indicator flags. Maximum branch range is +128, -127 words from the branch op code.

| BASE OP CODE | MNEMONIC                                                    |

|--------------|-------------------------------------------------------------|

|              |                                                             |

| ØlØØ         | BR                                                          |

| Ø2ØØ         | BNE                                                         |

| Ø3ØØ         | BEQ                                                         |

| Ø4ØØ         | BGE                                                         |

| Ø5ØØ         | BLT                                                         |

| ø6øø         | BGT                                                         |

| Ø7ØØ         | BLE                                                         |

| 8ØØØ         | BPL                                                         |

| 81ØØ         | BMI                                                         |

| 82ØØ         | BHI                                                         |

| 83ØØ         | BLOS                                                        |

| 84ØØ         | BVC                                                         |

| 85ØØ         | BVS                                                         |

| 86ØØ         | BCC, BHIS                                                   |

| 87ØØ         | BCS, BLO                                                    |

| ששוט         |                                                             |

| BR           | BRANCH UNCONDITIONALLY                                      |

|              |                                                             |

| FORMAT:      | BR DEST                                                     |

| OPERATION:   | PC ← PC+ (DISP *2)                                          |

| FUNCTION:    | Twice the value of the signed displacement                  |

|              | is added to PC.                                             |

|              |                                                             |

|              | SIGNED BRANCHES                                             |

|              | BRANCH IF NOT EQUAL TO ZERO                                 |

| BNE          | BRANCH II NOT EXCEL TO                                      |

|              | BNE DEST                                                    |

| FORMAT:      | IF $Z = \emptyset$ , $PC \leftarrow PC + (DISP *2)$         |

| OPERATION:   |                                                             |

| BEQ          | BRANCH IF EQUAL TO ZERO                                     |

| BEQ          |                                                             |

| FORMAT:      | BEO DEST                                                    |

| OPERATION:   | $\overline{IFZ} = 1$ , PC $\leftarrow$ PC + (DISP $*2$ )    |

| OF BIGHTON.  |                                                             |

| BGE          | BRANCH IF GREATER THAN OR EQUAL TO ZERO                     |

|              |                                                             |

| FORMAT:      | BGE DEST                                                    |

| OPERATION:   | IF $N\nabla V = \emptyset$ , PC $\leftarrow$ PC + (DISP *2) |

|              |                                                             |

|              |                                                             |

| BLT                | BRANCH IF LESS THAN ZERO                                                 |

|--------------------|--------------------------------------------------------------------------|

| FORMAT: OPERATION: | BLT DEST<br>IF N∀V = 1, PC ← PC + (DISP *2)                              |

| BGT                | BRANCH IF GREATER THAN ZERO                                              |

| FORMAT: OPERATION: | BGT DEST<br>IF Z ∇(NΨV) = Ø, PC + PC + (DISP *2)                         |

| BLE                | BRANCH IF LESS THAN OR EQUAL TO ZERO                                     |

| FORMAT: OPERATION: | BLE DEST<br>IF $Z\nabla(N\nabla V) = 1$ , PC $\leftarrow$ PC + (DISP *2) |

| BPL                | BRANCH IF PLUS                                                           |

| FORMAT: OPERATION: | BPL DEST<br>IF N = $\emptyset$ , PC $\leftarrow$ PC + (DISP *2)          |

| BMI                | BRANCH IF MINUS                                                          |

| FORMAT: OPERATION: | BMI DEST<br>IF N = 1, PC $\leftarrow$ PC + (DISP *2)                     |

|                    | UNSIGNED BRANCHES                                                        |

| ВНІ                | BRANCH IF HIGHER                                                         |

| FORMAT: OPERATION: | BHI DEST<br>IF $C\nabla Z = \emptyset$ , $PC \leftarrow PC + (DISP *2)$  |

| BLOS               | BRANCH IF LOWER OR SAME                                                  |

| FORMAT: OPERATION: | BLOS DEST<br>IF $C\nabla Z = 1$ , $PC \leftarrow PC + (DISP *2)$         |

| BVC                | BRANCH IF OVERFLOW CLEAR                                                 |

| FORMAT: OPERATION: | BVC DEST<br>IF $V = \emptyset$ , PC $\leftarrow$ PC + (DISP *2)          |

| BVS                | BRANCH IF OVERFLOW SET                                                   |

| FORMAT: OPERATION: | BVS DEST<br>IF V = 1, PC \( \text{PC} + (DISP *2)                        |

| BCC                | BRANCH IF CARRY CLEAR                                                    |

| BHIS               | BRANCH IF HIGHER OR SAME                                                 |

| FORMAT:            | BCC DEST                                                                 |

| OPERATION:         | BHIS DEST<br>IF $C = \emptyset$ , $PC \leftarrow PC + (DISP *2)$         |

| BCS        | BRANCH IF CARRY SET                         |

|------------|---------------------------------------------|

| BLO        | BRANCH IF LOWER                             |

| FORMAT:    | BCS DEST<br>BLO DEST                        |

| OPERATION: | IF $C = 1$ , $PC \leftarrow PC + (DISP *2)$ |

## FORMAT 6 OP CODES

SINGLE WORD - SINGLE OPS - SPLIT FIELD - DMØ ONLY

| 15      | 9 | 8 | 6  | 5 | 4   | 3  | 0   |

|---------|---|---|----|---|-----|----|-----|

| OPC BAS | E | R | EG |   | OPC | CC | UNT |

There are 12 op codes in this class representing op codes " $\emptyset 8 \emptyset \emptyset$ " to " $\emptyset 9 F F$ ", " $88 \emptyset \emptyset$ " to "89 F F", and " $8E \emptyset \emptyset$ " to "8F F F". There are 4 immediate mode op codes with a register as a destination, 4 multiple count single register shifts, and 4 multiple count double register shifts. In all op codes the actual count (or number in the case of the immediates) is the value of bits  $\emptyset$  - 3 plus one. Count is always a positive number in the range 1 - " $1\emptyset$ ", but it is stored in the op code as  $\emptyset$  - "F". All of these op codes are one word op codes with the op codes themselves split between bits 9-15 and 4-5.

In the case of the double shifts the 32 bit number (REG+1) : (REG) is the operand. If REG = PC then (REG+1) =  $R\emptyset$ .

| BASE OP CODE    | MNEMONIC                                        |

|-----------------|-------------------------------------------------|

| ø8øø            | ADDI                                            |

| Ø81Ø            | SUBI                                            |

| Ø82Ø            | BICI                                            |

| Ø83Ø            | MOVI                                            |

| 88ØØ            | SSRR                                            |

| 881Ø            | SSLR                                            |

| 882Ø            | SSRA                                            |

| 883Ø            | SSLA                                            |

| 8EØØ            | SDRR                                            |

| 8E1Ø            | SDLR                                            |

| 8E2Ø            | SDRA                                            |

| 8E3Ø            | SDLA                                            |

| ADDI            | ADD IMMEDIATE                                   |

|                 |                                                 |

| FORMAT;         | ADDI NUMBER, REG                                |

| OPERATION:      | REG ← REG + COUNT + 1                           |

| FUNCTION:       | The stored number plus one is added to the      |

| T               | destination register.                           |

| INDICATORS:     | N = Set if bit 15 of the result is set          |

|                 | $Z = Set if the result = \emptyset$             |

|                 | V = Set if arithmetic overflow occurs; i.e. set |

|                 | if both operands were positive and the sign of  |

|                 | the result is negative                          |

|                 | C = Set if a carry was generated from bit 15    |

|                 | of the result                                   |

| SUBI            | SUBTRACT IMMEDIATE                              |

| FORMAT:         | SUBI NUMBER, REG                                |

| OPERATION:      | REG ← REG - (COUNT +1)                          |

| FUNCTION:       | The stored number plus one is subtracted from   |

| ··, <del></del> | the destination register                        |

|                 | •                                               |

INDICATORS:

N = Set if bit 15 of the result is set

$Z = Set if the result = \emptyset$

V = Set if arithmetic underflow occurs; i.e. set if the operands were of opposite signs and

the sign of the result is positive

C = Set if a borrow was generate from bit 15

of the result

BICI

BIT CLEAR IMMEDIATE

FORMAT:

OPERATION:

BICI NUMBER, REG REG  $\leftarrow$  REG  $\triangle$  (COUNT + 1)

FUNCTION:

The stored number plus one is one's complemented

and ANDED to the destination register

INDICATORS:

N = Set if bit 15 of the result is set

$Z = Set if the result = \emptyset$

V = Reset

C = Unchanged

IVOM

MOVE IMMEDIATE

FORMAT:

OPERATION:

IVOM NUMBER, REG

REG ← COUNT + 1

FUNCTION:

The stored number plus one is placed in

the destination register

INDICATORS:

N = Reset Z = Reset

V = Reset

C = Unchanged

SSRR

SHIFT SINGLE RIGHT ROTATE

FORMAT:

FUNCTION:

SSRR REG, COUNT

A 17-bit right rotate is done stored count+1 times on REG: C-Flag. The C-Flag is shifted into

bit 15 of REG, and the C-Flag gets the last bit

shifted out of REG bit Ø.

INDICATORS:

N = Set if bit 7 of REG is set

$Z = Set if REG = \emptyset$

V = Set to exclusive or of N and C flags C = Set to the value of the last bit shifted

out of REG bit Ø

SSLR

SHIFT SINGLE LEFT ROUTINE

FORMAT:

SSLR REG, COUNT

FUNCTION:

INDICATORS:

A 17-bit left rotate is done stored count+1 times on C-Flag: REG . The C-Flag is shifted into bit  $\emptyset$  of REG and the C-Flag gets the

last bit shifted out of REG bit 15.

N = Set if bit 15 of REG is set

$Z = Set if REG = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the last bit shifted

out of REG bit 15.

## SSRA SHIFT SINGLE RIGHT ARITHMETIC

FORMAT: SSRA REG, COUNT

FUNCTION: A 17-bit right arithmetic shift is done stored count+1 times on REG: C-Flag. Bit

15 of REG is replicated. The C-Flag gets the last bit shifted out of REG bit Ø. Bits shifted

out of the C-Flag are lost.

INDICATORS: N = Set if bit 7 of REG is set

$Z = Set if REG = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the last bit shifted

out of REG bit Ø

## SSLA SHIFT SINGLE LEFT ARITHMETIC

FORMAT: SSLA REG, COUNT

FUNCTION: A 17-bit left arithmetic shift is done stored

count+1 times on C-Flag:REG. Zeros are shifted into REG bit  $\emptyset$ , and the C-FLAG gets the last bit shifted out of REG bit 15. Bits shifted out of the

C-Flag are lost

INDICATORS:  $N = Set \ if \ REG \ bit \ 15 \ is \ set$

$Z = Set if REG = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the last bit shifted

out of REG bit 15

#### SDRR SHIFT DOUBLE RIGHT ROTATE

FORMAT: SDRR REG, COUNT

FUNCTION: REG+1:REG:C-Flag is rotate right stored

count+1 times. The C-Flag is shifted into REG+1 bit 15, REG+1 bit Ø is shifted into

REG bit 15, and REG bit Ø is shifted into the C-Flag.

INDICATORS: N = Set if bit 7 of REG is set

$Z = Set if REG = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the last bit shifted

out of REG bit Ø

## SDLR SHIFT DOUBLE LEFT ROTATE

FORMAT: SDLR REG, COUNT

FUNCTION: A 33 bit left rotate is done stored count+1

times on C-Flag:REG+1:REG. The C-Flag is shifted into REG bit Ø, REG bit 15 is shifted into REG+1 bit Ø, and REG+1 bit 15 is shifted

into the C-Flag

INDICATORS: N = Set if REG+1 bit 15 is set

$Z = Set if REG+1 = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the last bit shifted

out of REG+1 bit 15.

| DRA | SHIFT | DOUBLE | RIGHT | ARITHMETIC |

|-----|-------|--------|-------|------------|

|     | <br>  |        |       |            |

FORMAT:

SDRA REG, COUNT

FUNCTION:

A right arithmetic shift is done stored

count+1 times on REG+1:REG:C-Flag.

Bit 15 of REG+1 is replicated. Bit  $\emptyset$  of REG+1 is shifted to bit 15 of REG. Bit  $\emptyset$  of REG is shifted to the C-Flag. Bits

shifted out of the C-Flag are lost.

INDICATORS:

N = Set if bit 7 of REG is set

$Z = Set if REG = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the last bit

shifted out of REG bit Ø

#### SDLA

## SHIFT DOUBLE LEFT ARITHMETIC

FORMAT: FUNCTION:

SDLA REG, COUNT

A left arithmetic shift is done stored

count+1 times on C-Flag: REG+1: REG.

Zeros are shifted into REG bit  $\emptyset$ , REG bit 15 is shifted to REG+1 bit  $\emptyset$ . REG+1 bit 15 is shifted to the C-Flag. Bits shifted out of the C-Flag are lost.

INDICATORS:

N = Set if REG+l bit 15 is set

$Z = Set if REG+l = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the last bit shifted

out of REG+1 bit 15

#### FORMAT 7 OP CODES

SINGLE OPS - ONE OR TWO WORDS - DMØ TO DM7

| 1. | 5   | 6 | 5 | 3   | 2 | 0   |

|----|-----|---|---|-----|---|-----|

| Г  | OPC |   | N | ODE |   | REG |

There are 32 op codes in this class representing op codes "@A@@" to "@DFF" and "8A@@" to "8DFF". All addressing modes from @ to 7 are available with all registers available as index registers (see chapter two). A one word op code is generated for addressing modes @ to 5. A two word op code is generated for addressing modes 6 and 7 with the offset value in word two. For DM6 and DM7 with PC as the index register PC is added to the offset from word two after the offset is fetched from memory. The offset is therefore relative to a PC that points to the op code that follows (i.e. current op code + 4). Codes "8A@@" to "8CC@" are BYTE ops.

| BASE OP CODE | MNEMONIC                      | BASE OP CODE  | MNEMONIC |  |

|--------------|-------------------------------|---------------|----------|--|

|              |                               |               |          |  |

| ØAØØ         | ROR                           | 8aøø          | RORB     |  |

| ØA4Ø         | ROL                           | 8A4Ø          | ROLB     |  |

| ØA8Ø         | $	extbf{T}	extbf{S}	extbf{T}$ | 8A8Ø          | TSTB     |  |

| ØACØ         | ASL                           | 8ACØ          | ASLB     |  |

| øbøø         | SET                           | 8B <b>Ø</b> Ø | SETB     |  |

| ØB4Ø         | CLR                           | 8B4Ø          | CLRB     |  |

| ØB8Ø         | ASR                           | 8B8Ø          | ASRB     |  |

| ØBCØ         | SWAB                          | 8BCØ          | SWAD     |  |

| ØCØØ         | COM                           | 8CØØ          | COMB     |  |

| ØC4Ø         | NEG                           | 8C4Ø          | NEGB     |  |

| ØC8Ø         | INC                           | 8C8Ø          | INCB     |  |

| ØCCØ         | DEC                           | 8CCØ          | DECB     |  |

| ØDØØ         | IW2                           | 8DØØ          | LSTS     |  |

| ØD4Ø         | SXT                           | SD4Ø          | SSTS     |  |

| ØD8Ø         | TCALL                         | 8D8Ø          | ADC      |  |

| ØDCØ         | TJMP                          | 8DCØ          | SBC      |  |

| م د ح م      |                               |               |          |  |

## WORD OPS

| ROR         | ROTATE RIGHT                                         |

|-------------|------------------------------------------------------|

|             |                                                      |

| FORMAT:     | ROR DST                                              |

| FUNCTION:   | A 1-bit right rotate is done on (DST):C-Flag         |

|             | The C-Flag is shifted into (DST) bit 15, and (DST)   |

|             | bit Ø is shifted into the C-flag.                    |

| INDICATORS: | N = Set if bit 7 of (DST) is set                     |

| INDICATORS. | $Z = Set if (DST) = \emptyset$                       |

|             |                                                      |

|             | V = Set to exclusive or of N and C flags             |

|             | C = Set to the value of the bit shifted out of (DST) |

|             |                                                      |

| ROL         | ROTATE LEFT                                          |

|             |                                                      |

| FORMAT:     | ROL DST                                              |

| FUNCTION:   | A 1-bit left rotate is done on C-Flag: (DST). The    |

C-Flag is shifted into (DST) bit Ø, and (DST)

bit 15 is shifted into the C-Flag.

INDICATORS: N = Set if bit 15 of (DST) is set

$Z = Set if (DST) = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the bit shifted out of (DST)

TEST WORD

TSTFORMAT: OPERATION: (DST) A (DST)

The indicators are set to reflect the destination FUNCTION:

DST

operand status.

INDICATORS: N = Set if (DST) bit 15 is set

$Z = Set if (DST) = \emptyset$

V = Reset C = Unchanged

ASL ARITHMETIC SHIFT LEFT

FORMAT: ASL DST

A 1-bit left arithmetic shift is done on (DST). A FUNCTION:

zero is shifted into (DST) bit  $\emptyset$ , and (DST) bit 15

is shifted into the C-Flag.

N = Set if (DST) bit 15 is set INDICATORS:

$Z = Set if (DST) = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the bit shifted out of (DST)

SET TO ONES SET

FORMAT: SET DST (DST) ← "FFFF" OPERATION:

FUNCTION: The destination operand is set to all ones

N = SetINDICATORS: Z = Reset

> V = Reset C = Unchanged

CLR CLEAR TO ZEROS

FORMAT: CLR DST OPERATION:  $(DST) \leftarrow \emptyset$

The destination operand is cleared to all zeros FUNCTION:

INDICATORS: N = ResetZ = SetV = Reset

C = Unchanged if DMØ. Reset if DMl-DM7.

ARITHMETIC SHIFT RIGHT

FORMAT: ASR DST

FUNCTION: A 1-bit right arithmetic shift is done on (DST). Bit

15 of (DST) is replicated. Bit Ø of (DST) is shifted

into the C-Flag.

```

N = Set if (DST) bit 7 is set

INDICATORS:

Z = Set if (DST) = \emptyset

V = Set to exclusive or of N and C flags

C = Set to the value of the bit shifted out of (DST)

SWAP BYTES

SWAB

FORMAT:

SWAB

DST

(DST) 15-8 \stackrel{?}{\leftarrow} (DST) 7-\emptyset

OPERATION:

The upper and lower bytes of (DST) are exhanged.

FUNCTION:

N = Set if (DST) bit 7 is set

INDICATORS:

Z = Set if (DST) lower byte = \emptyset

V = Reset

C = Unchanged

COMPLEMENT

COM

FORMAT:

COM

DST

(DST) \leftarrow (DST)

OPERATION

The destination operand is one's complemented.

FUNCTION:

N = Set if (DST) bit 15 is set

INDICATORS:

Z = Set if (DST) = \emptyset

V = Reset

C = Set

NEGATE

NEG

DST

NEG

FORMAT:

OPERATION:

(DST) \leftarrow -(DST)

The destination operand is two's complemented.

FUNCTION:

N = Set if (DST) bit 15 is set

INDICATORS:

Z = Set if (DST) = \emptyset

V = Set if (DST) = "8000"

C = Reset if (DST) = \emptyset

INC

INCREMENT

INC

DST

FORMAT:

OPERATION:

(DST) \leftarrow (DST) + 1

The destination operand is incremented by one.

FUNCTION:

N = Set if (DST) bit 15 is set

INDICATORS:

Z = Set if (DST) = \emptyset

V = Set if (DST) = "8000"

C = Set if a carry is generated from (DST) bit 15

DECREMENT

DEC

FORMAT:

DEC

DST

(DST) \leftarrow (DST) - 1

OPERATION:

The destination operand is decremented by one.

FUNCTION:

```

C = Set if a borrow is generated from (DST) bit 15

N = Set if (DST) bit 15 is set

$Z = Set if (DST) = \emptyset$ V = Set if (DST) = "7FFF"

INDICATORS:

INCREMENT WORD BY TWO IW2 DST FORMAT: IW2  $(DST) \leftarrow (DST) + 2$ OPERATION: The destination operand is incremented by two. FUNCTION: N = Set if (DST) bit 15 is setINDICATORS:  $Z = Set if (DST) = \emptyset$ V = Set if (DST) = "8000" or "8001"C = Set if a carry is generated from (DST) bit 15 SIGN EXTEND SXT SXT DST FORMAT:  $(DST) \leftarrow \emptyset$  $IF N = \emptyset,$ OPERATION: (DST) ← "FFFF" IF N = 1,The N-Flag status is replicated in the destination operand FUNCTION: Unchanged INDICATORS: TABLED SUBROUTINE CALL TCALL DST TCALL FORMAT: ↓ SP, @SP ← PC OPERATION:  $PC \leftarrow PC + (DST)$ PC ← PC + @PC PC, which points to the op code that follows, is pushed FUNCTION: onto the stack. The destination operand is added to PC. The contents of this intermediate table address is also added to PC to get the final destination address. Note that at least one op code must exist between the TCALL and the table for a subroutine return. Unchanged INDICATORS: TABLED JUMP TJMP FORMAT: TJMP DST  $PC \leftarrow PC + (DST)$ OPERATION:  $PC \leftarrow PC + @PC$ The destination operand is added to PC, and the contents FUNCTION: of this intermediate location is also added to PC to get the final destination address. Unchanged INDICATORS: LOAD PROCESSOR STATUS LSTS LSTS DST FORMAT: The four indicators and the interrupt enable (I2) FUNCTION: are loaded from the destination operand. Set to the status of (DST) bits  $\emptyset$  - 3 INDICATORS: STORE PROCESSOR STATUS SSTS SSTS FORMAT:

Unchanged

FUNCTION:

INDICATORS:

The processor status word is formed and stored in (DST).

ADD CARRY

FORMAT:

ADC DST

OPERATION:

$(DST) \leftarrow (DST) + C-flag$

FUNCTION:

The carry flag is added to the destination operand

INDICATORS:

N= Set if (DST) bit 15 is set

$Z = Set if (DST) = \emptyset$

V = Set to exclusive or of N and C flags

C = Set if a carry is generated from (DST) bit 15

SBC

SUBTRACT CARRY

FORMAT:

SBC DST

OPERATION:

$(DST) \leftarrow (DST) - C-Flag$

FUNCTION:

The Carry flag is subtracted from the destination operand

INDICATORS:

N = Set if (DST) bit 15 is set

$Z = Set if (DST) = \emptyset$

V = Set to exclusive or of N and C flags

C = Set if a borrow is generated from (DST) bit 15

#### BYTE OPS

For DMØ addressing only the lower byte of the destination register is affected by a byte op code. For DM1-DM7 addressing only the specified memory byte is affected by a byte op. For even memory addresses the lower byte is altered, and for ddd memory addresses the upper byte is altered.

| RURR |

|------|

## ROTATE RIGHT BYTE

FORMAT:

RORB DST

FUNCTION:

A 1-bit right rotate is done on (DST)<sub>B:</sub>C-Flag. Bit  $\emptyset$  of (DST)<sub>B</sub> is shifted into the C-Flag, and the C-Flag

is shifted into  $(DST)_B$  bit 7.

INDICATORS:

$N = Set if (DST)_B bit 7 is set$

$Z = Set if (DST)_B = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the bit shifted out of (DST)<sub>B</sub>bit  $\emptyset$

#### ROLB

## ROTATE LEFT BYTE

FORMAT:

ROLB DST

FUNCTION:

A 1-bit left rotate is done on C-flag :(DST) $_{\rm B}$ . Bit 7 of (DST)B is shifted into the C-flag, and the C-flag

is shifted into (DST) B bit Ø

INDICATORS:

$N = Set if (DST)_B bit 7 is set$

$Z = Set if (DST)_B = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the bit shifted out of  $(DST)_B$  bit 7

TEST BYTE

TSTB

**EORMAT:**

$(DST)_B \Delta (DST)_B$

OPERATION:

FUNCTION:

The destination operand status sets the indicators.

INDICATORS:

$N = Set if (DST)_{R} bit 7 is set$

$Z = Set if (DST)_B = \emptyset$

V = Reset C = Unchanged

ASLB

ARITHMETIC SHIFT LEFT BYTE

FORMAT:

ASLB DST

FUNCTION:

A 1-bit left arithmetic shift is done on C-Flag: (DST) B A zero is shifted into (DST)<sub>B</sub> bit  $\emptyset$ , and (DST)<sub>B</sub> bit 7 is

shifted into the C-flag.

INDICATORS:

$N = \text{set if } (DST)_B \text{ bit 7 is set}$

$z = Set if (DST)_B = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the bit shifted out of  $(DST)_B$  bit 7

SETB

SET BYTE TO ONES

FORMAT:

SETB DST

OPERATION:

$(DST)_R \leftarrow "FF"$

FUNCTION:

The destination byte operand is set to all ones

INDICATORS:

N = SetZ = Reset V = Reset C = Unchanged

CLRB

CLEAR BYTE TO ZEROS

FORMAT:

CLRB DST

OPERATION:

$(DST)_R \leftarrow \emptyset$

FUNCTION:

The destination byte operand is cleared to all zeros.

INDICATORS:

N = Reset Z = Set

V = Reset

C = Reset

ASRB

ARITHMETIC SHIFT RIGHT BYTE

FORMAT:

ASRB DST

FUNCTION:

INDICATORS:

A 1-bit right arithmetic shift is done on (DST)<sub>R</sub>:

C-flag. Bit 7 of (DST)  $_{\rm B}$  is replicated. Bit  $\emptyset$  of (DST)  $_{\rm B}$  is shifted into the C-flag.

$N = Set if (DST)_B bit 7 is set$

$Z = Set if (DST)_{R}^{D} = \emptyset$

V = Set to exclusive or of N and C flags

C = Set to the value of the bit shifted out of (DST)<sub>R</sub> bit  $\emptyset$

SWAD

SWAP DIGITS

FORMAT:

SWAD

FUNCTION:

The two hex digits in the destination byte operand

are exchanged with each other,

INDICATORS:

$N = Set if (DST)_B bit 7 is set$

$Z = Set if (DST)_B = \emptyset$

$V = Set if (DST)_B bit 7 is set$

C = Reset

#### COMPLEMENT BYTE COMB

FORMAT: COMB DST OPERATION:  $(DST)_B \leftarrow \overline{(DST)_B}$

The destination byte operand is one's complemented FUNCTION:

INDICATORS:  $N = Set if (DST)_B bit 7 is set$

$Z = Set if (DST)_B = \emptyset$

V = Reset C = Set

#### NEGATE BYTE NEGB

FORMAT: NEGB DST (DST)<sub>B</sub> - (DST)<sub>B</sub> OPERATION:

FUNCTION: The destination byte operand is two's complemented

INDICATORS:  $N = Set if (DST)_B bit 7 is set$

$z = Set if (DST)_B = \emptyset$  $V = Set if (DST)_B = "8000"$  $C = Reset if (DST)_B = \emptyset$

#### INCB INCREMENT BYTE

FORMAT: INCB DST OPERATION:  $(DST)_B \leftarrow (DST)_B + 1$

FUNCTION: The destination byte operand is incremented by one

$N = Set if (DST)_B is set$ INDICATORS:

Z = Set if (DST)<sub>B</sub> =  $\emptyset$ V = Set if (DST)<sub>B</sub> = "8 $\emptyset$  $\emptyset$  $\emptyset$ "

$C = Set if a carry is generated from (DST)_R bit 7$

#### **DECB** DECREMENT BYTE

FORMAT: DECB DST

**OPERATION:**  $(DST)_B \leftarrow (DST)_B - 1$

FUNCTION: The destination byte operand is decremented by one

INDICATORS:  $N = Set if (DST)_B bit 7 is set$

$Z = Set if (DST)_B = \emptyset$ V = Set if (DST)\_B = "7FFF"

C = Set if a borrow is generated from (DST)<sub>B</sub> bit 7

#### FORMAT 8 OP CODES\*

DOUBLE OPS - SINGLE WORD - SMØ AND DMØ ONLY

| 15  | 6 | 5 |     | 3 | 2 | ø   |

|-----|---|---|-----|---|---|-----|

| OPC |   | S | REG |   | D | REG |