# **PRELIMINARY**

May 1991

# NS32GX32-20/NS32GX32-25/NS32GX32-30 High-Performance 32-Bit Embedded System Processor

# **General Description**

The NS32GX32 is a high-performance 32-bit embedded system processor in the Series 32000® family. It is software compatible with the previous microprocessors in the family but with a greatly enhanced internal implementation.

The NS32GX32 integrates more than 320,000 transistors fabricated in a 1.25  $\mu m$  double-metal CMOS technology. The advanced technology and mainframe-like design of the device enable it to achieve peak performance of 15 million instructions per second.

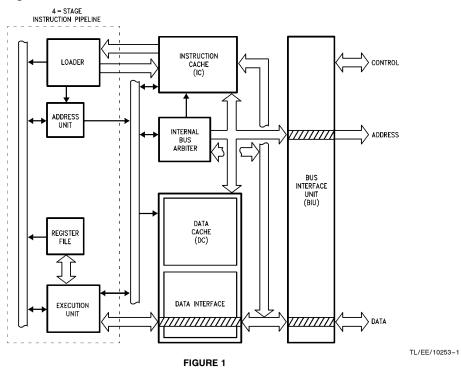

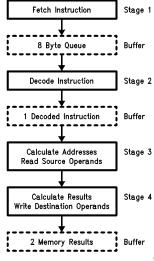

The high-performance specifications are the result of a fourstage instruction pipeline, on-chip instruction and data caches, and a significantly increased clock frequency. In addition, the system interface provides optimal support for applications spanning a wide range, from low-cost, real-time controllers to highly sophisticated, embedded systems.

In addition to generally improved performance, the NS32GX32 offers much faster interrupt service and task switching for real-time applications.

# **Features**

- Software compatible with the Series 32000 family

- 32-bit architecture and implementation

- 4-GByte uniform addressing space

- 4-Stage instruction pipeline

- 512-Byte on-chip instruction cache

- 1024-Byte on-chip data cache

- High-performance bus

- Separate 32-bit address and data lines

- Burst mode memory accessing

- Dynamic bus sizing

- Floating-point support via the NS32381

- $\blacksquare$  1.25  $\mu m$  double-metal CMOS technology

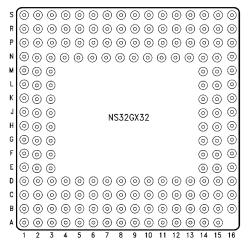

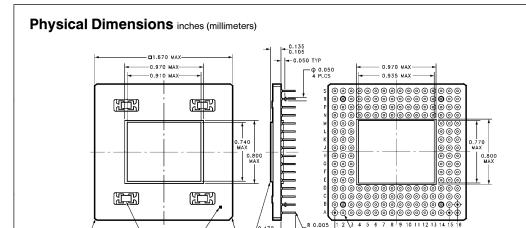

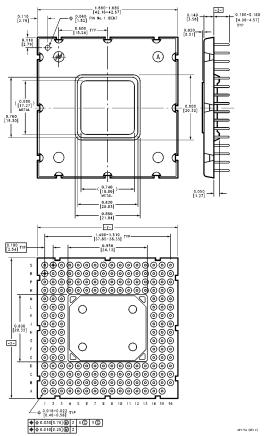

- 175-pin PGA package

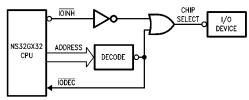

# **Block Diagram**

Series 32000® and TRI-STATE® are registered trademarks of National Semiconductor Corporation.

# **Table of Contents**

#### 1.0 PRODUCT INTRODUCTION

#### 2.0 ARCHITECTURAL DESCRIPTION

- 2.1 Register Set

- 2.1.1 General Purpose Registers

- 2.1.2 Address Registers

- 2.1.3 Processor Status Register

- 2.1.4 Configuration Register

- 2.1.5 Debug Registers

- 2.2 Memory Organization

- 2.2.1 Address Mapping

- 2.3 Modular Software Support

- 2.4 Instruction Set

- 2.4.1 General Instruction Format

- 2.4.2 Addressing Modes

- 2.4.3 Instruction Set Summary

#### 3.0 FUNCTIONAL DESCRIPTION

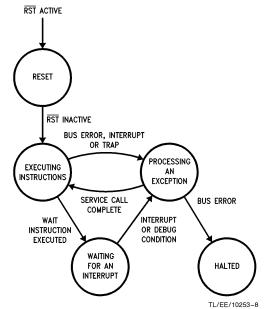

- 3.1 Instruction Execution

- 3.1.1 Operating States

- 3.1.2 Instruction Endings

- 3.1.2.1 Completed Instructions

- 3.1.2.2 Suspended Instructions

- 3.1.2.3 Terminated Instructions

- 3.1.2.4 Partially Completed Instructions

#### 3.0 FUNCTIONAL DESCRIPTION (Continued)

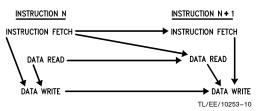

- 3.1.3 Instruction Pipeline

- 3.1.3.1 Branch Prediction

- 3.1.3.2 Memory Mapped I/O

- 3.1.3.3 Serializing Operations

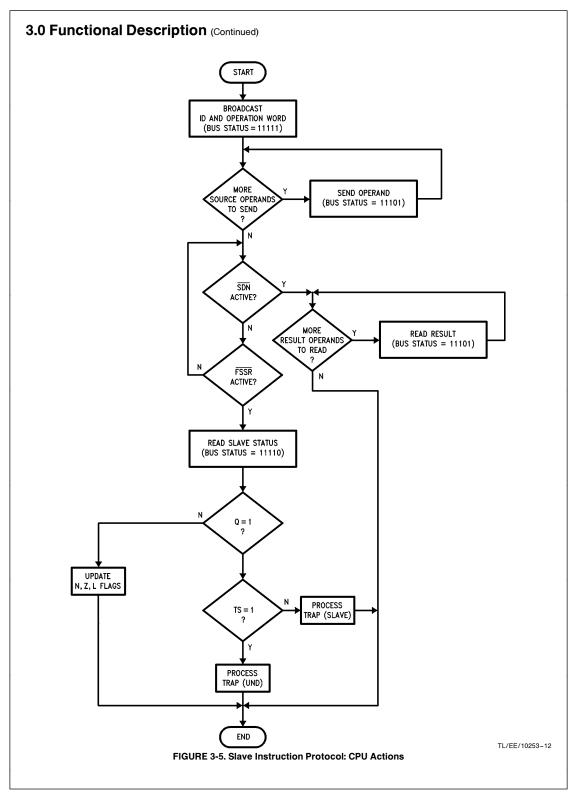

- 3.1.4 Slave Processor Instructions

- 3.1.4.1 Slave Instruction Protocol

- 3.1.4.2 Floating-Point Instructions

- 3.1.4.3 Custom Slave Instructions

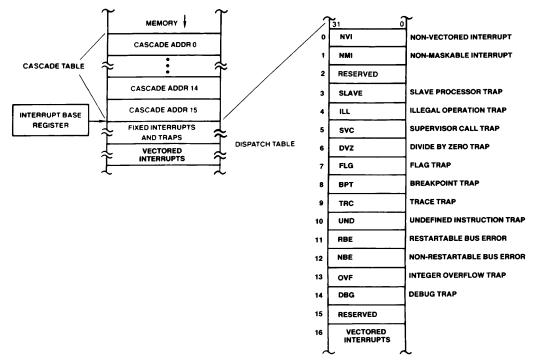

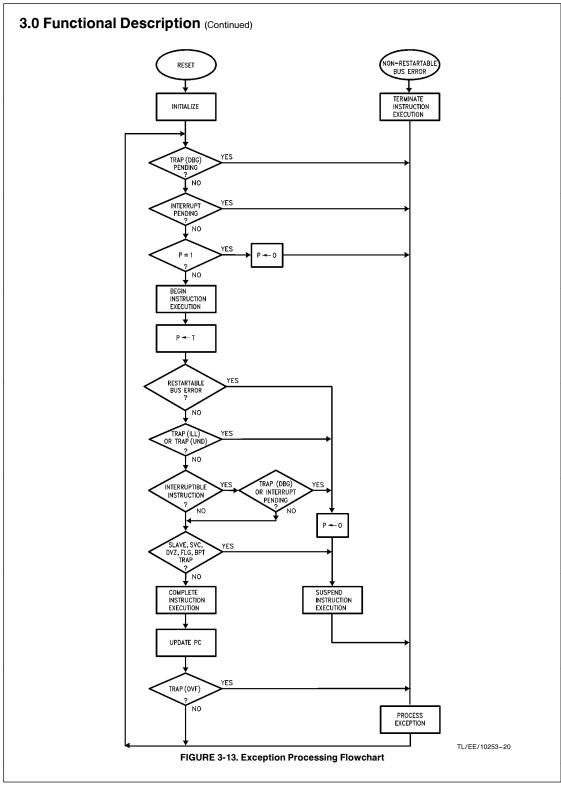

- 3.2 Exception Processing

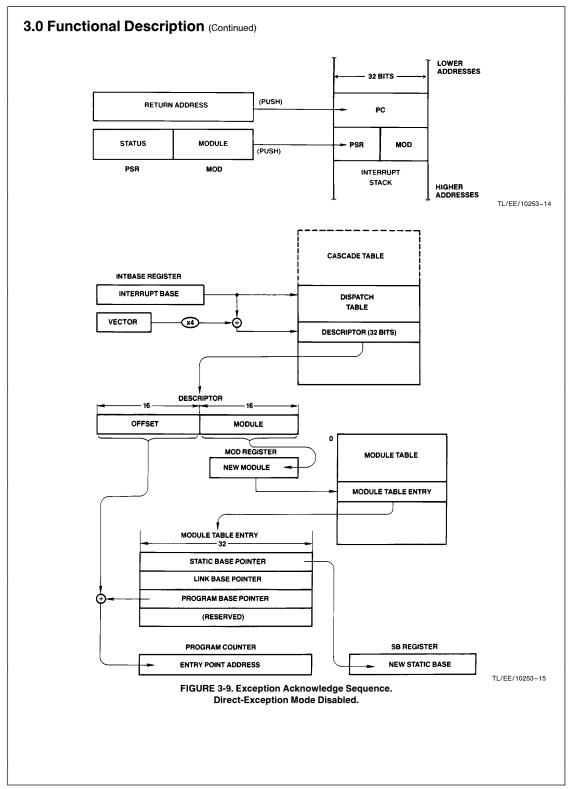

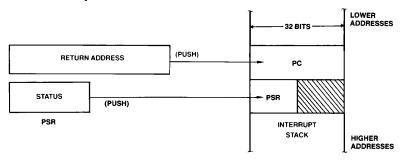

- 3.2.1 Exception Acknowledge Sequence

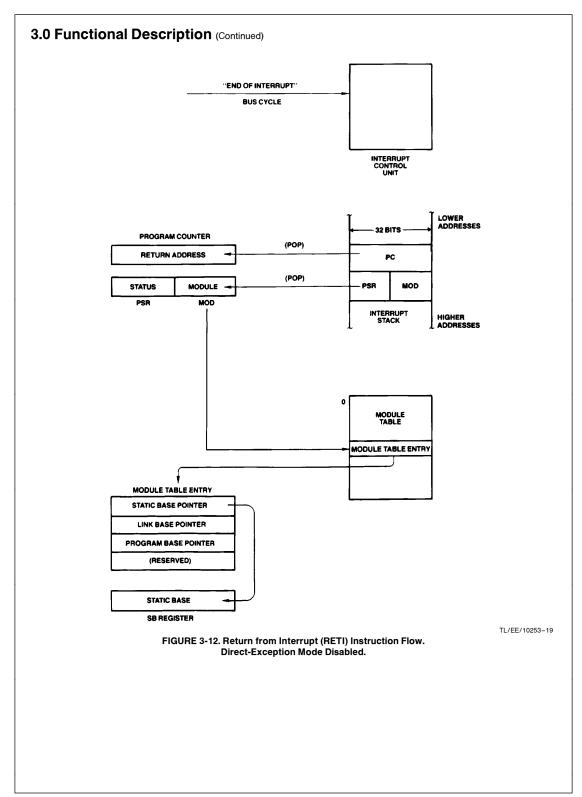

- 3.2.2 Returning from an Exception Service Procedure

- 3.2.3 Maskable Interrupts

- 3.2.3.1 Non-Vectored Mode

- 3.2.3.2 Vectored Mode: Non-Cascaded Case

- 3.2.3.3 Vectored Mode: Cascaded Case

- 3.2.4 Non-Maskable Interrupt

- 3.2.5 Traps

- 3.2.6 Bus Errors

- 3.2.7 Priority Among Exceptions

- 3.2.8 Exception Acknowledge Sequences: Detailed Flow

- 3.2.8.1 Maskable/Non-Maskable Interrupt Sequence

- 3.2.8.2 Restartable Bus Error Sequence

- 3.2.8.3 SLAVE/ILL/SVC/DVZ/FLG/BPT/UND Trap Sequence

- 3.2.8.4 Trace Trap Sequence

# Table of Contents (Continued)

#### 3.0 FUNCTIONAL DESCRIPTION (Continued)

3.2.8.5 Integer-Overflow Trap Sequence

3.2.8.6 Debug Trap Sequence

3.2.8.7 Non-Restartable Bus Error Sequence

3.3 Debugging Support

3.3.1 Instruction Tracing

3.3.2 Debug Trap Capability

3.4 On-Chip Caches

3.4.1 Instruction Cache (IC)

3.4.2 Data Cache (DC)

3.4.3 Cache Coherence Support

3.5 System Interface

3.5.1 Power and Grounding

3.5.2 Clocking

3.5.3 Resetting

3.5.4 Bus Cycles

3.5.4.1 Bus Status

3.5.4.2 Basic Read and Write Cycles

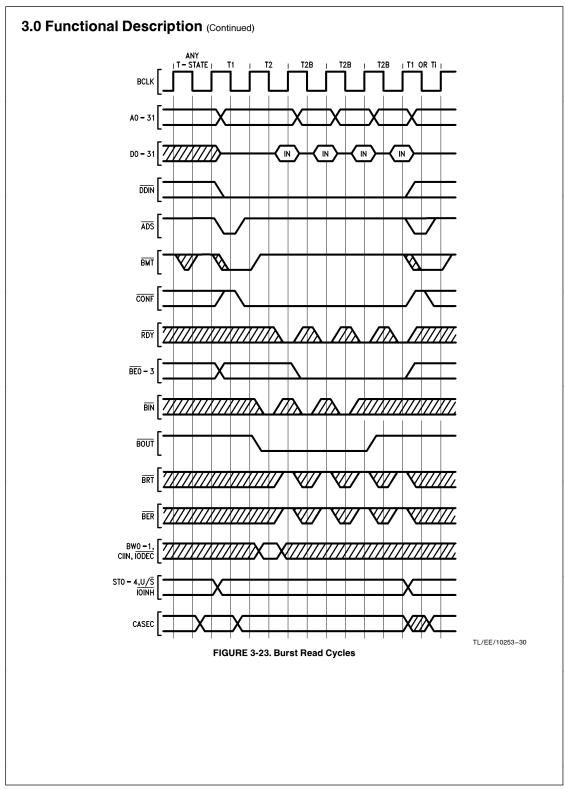

3.5.4.3 Burst Cycles

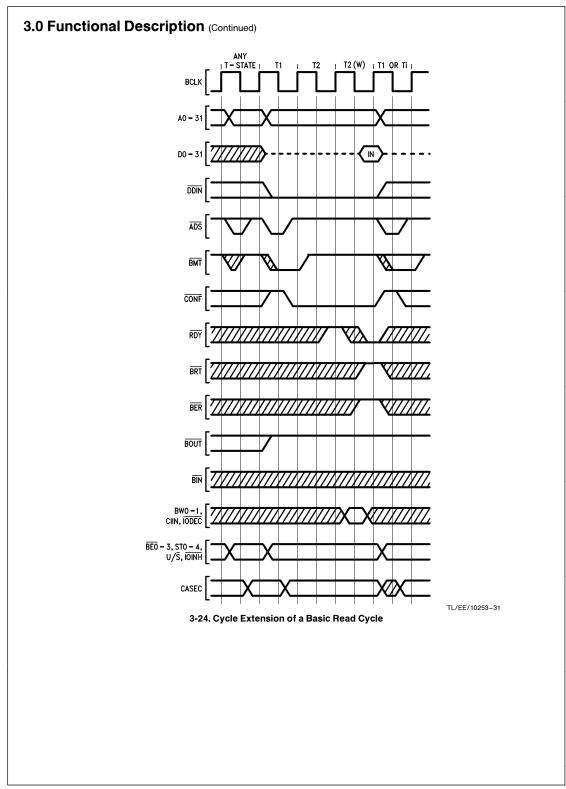

3.5.4.4 Cycle Extension

3.5.4.5 Interlocked Bus Cycles

3.5.4.6 Interrupt Control Cycles

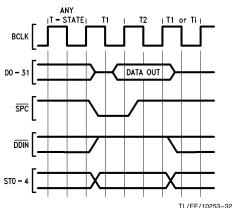

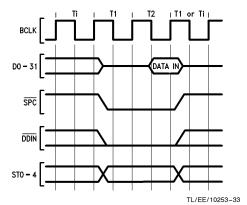

3.5.4.7 Slave Processor Bus Cycles

3.5.5 Bus Exceptions

3.5.6 Dynamic Bus Configuration

3.5.6.1 Instruction Fetch Sequences

3.5.6.2 Data Read Sequences

3.5.6.3 Data Write Sequences

3.5.7 Bus Access Control

3.5.8 Interfacing Memory-Mapped I/O Devices

3.5.9 Interrupt and Debug Trap Requests

3.5.10 Internal Status

# 4.0 DEVICE SPECIFICATIONS

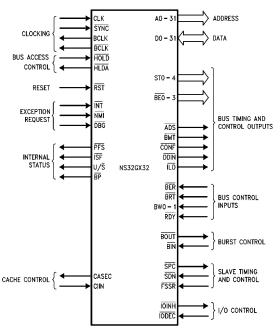

4.1 Pin Descriptions

4.1.1 Supplies

4.1.2 Input Signals

4.1.3 Output Signals

4.1.4 Input/Output Signals

4.2 Absolute Maximum Ratings

4.3 Electrical Characteristics

4.4 Switching Characteristics

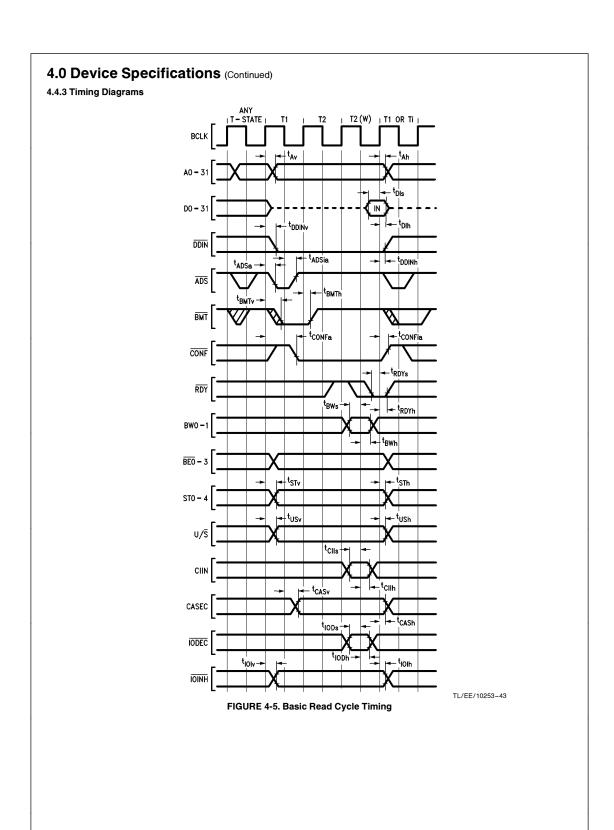

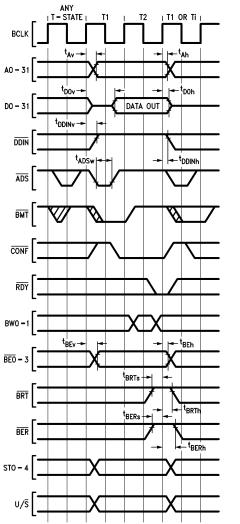

#### 4.0 DEVICE SPECIFICATIONS (Continued)

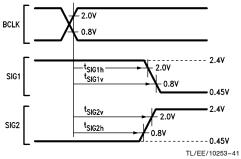

4.4.1 Definitions

4.4.2 Timing Tables

4.4.2.1 Output Signals: Internal Propagation

Delavs

4.4.2.2 Input Signal Requirements

4.4.3 Timing Diagrams

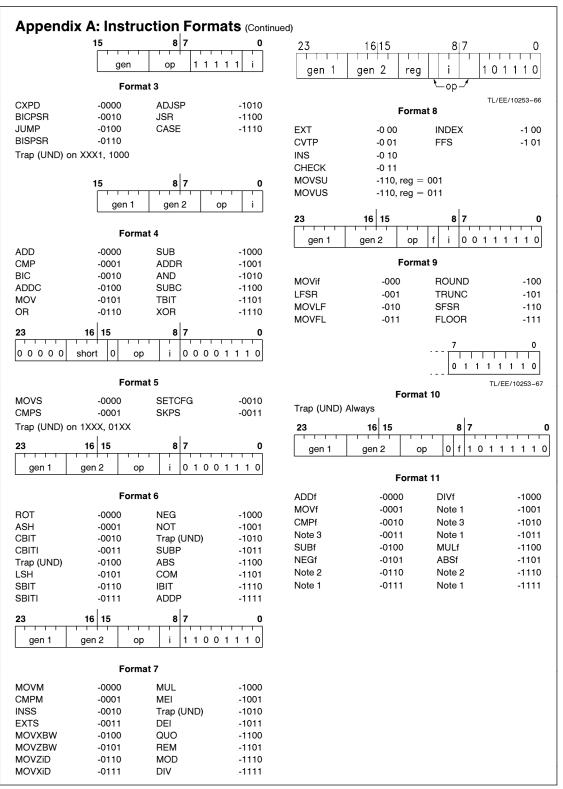

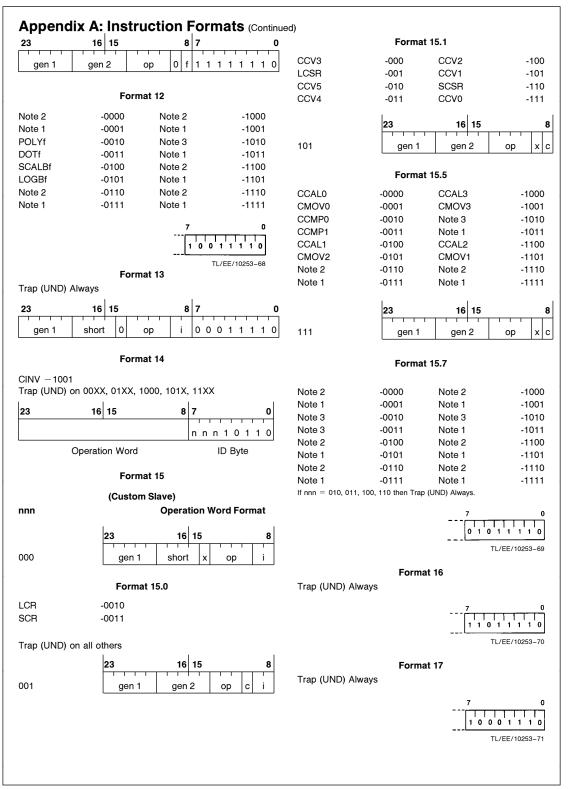

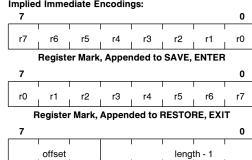

#### **APPENDIX A: INSTRUCTION FORMATS**

#### **B: COMPATIBILITY ISSUES**

**B.1 Restrictions on Compatibility**

**B.2 Architecture Extensions**

B.3 Integer-Overflow Trap

B.4 Self-Modifying Code

B.5 Memory-Mapped I/O

#### **C: INSTRUCTION SET EXTENSIONS**

C.1 Processor Service Instructions

C.2 Instruction Definitions

#### **D: INSTRUCTION EXECUTION TIMES**

D.1 Internal Organization and Instruction Execution

D.2 Basic Execution Times

D.2.1 Loader Timing

D.2.2 Address Unit Timing

D.2.3 Execution Unit Timing

D.3 Instruction Dependencies

D.3.1 Data Dependencies

D.3.1.1 Register Interlocks

D.3.1.2 Memory Interlocks

D.3.2 Control Dependencies

D.4 Storage Delays

D.4.1 Instruction Cache Misses

D.4.2 Data Cache Misses

D.4.3 Instruction and Operand Alignment

D.5 Execution Time Calculations

D.5.1 Definitions

D.5.2 Notes on Table Use

D.5.3 T<sub>eff</sub> Evaluation

D.5.4 Instruction Timing Example

D.5.5 Execution Timing Tables

D.5.5.1 Basic and Memory

Management Instructions

D.5.5.2 Floating-Point Instructions,

CPU Portion

# **List of Illustrations**

| CPU Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NS32GX32 Internal Registers2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Processor Status Register (PSR) 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Configuration Register (CFG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Debug Condition Register (DCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Debug Status Register (DSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NS32GX32 Address Mapping2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NS32GX32 Run-Time Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| General Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Index Byte Format         2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Displacement Encodings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Operating States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NS32GX32 Internal Instruction Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Memory References for Consecutive Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Memory References after Serialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Slave Instruction Protocol: CPU Actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ID and Operation Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Slave Processor Status Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

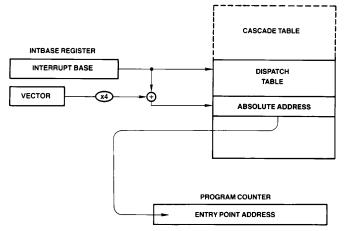

| Interrupt Dispatch Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Exception Acknowledge Sequence: Direct-Exception Mode Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Exception Acknowledge Sequence: Direct-Exception Mode Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Exception Acknowledge Sequence. Direct-Exception winde Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

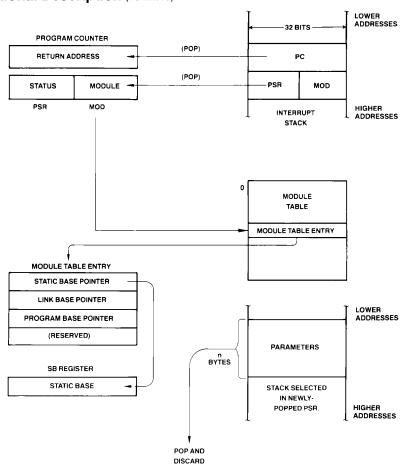

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

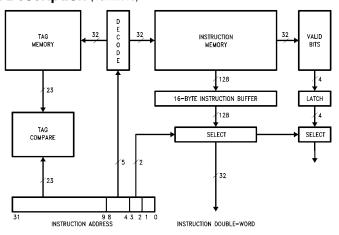

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

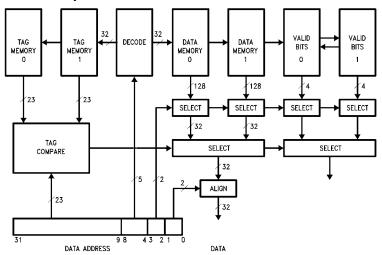

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

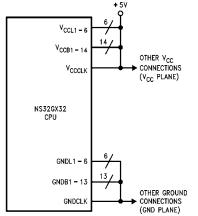

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

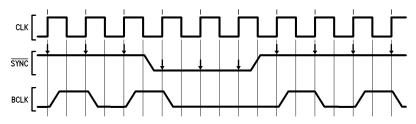

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

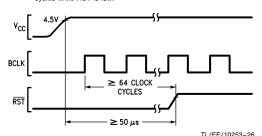

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19                                                                                                                                                                                                                                                                                                                                                                                                                     |

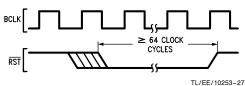

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19         General Reset Timing       3-20                                                                                                                                                                                                                                                                                                                                                                             |

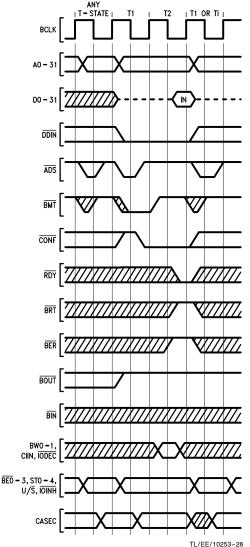

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19         General Reset Timing       3-20         Basic Read Cycle       3-21                                                                                                                                                                                                                                                                                                                                         |

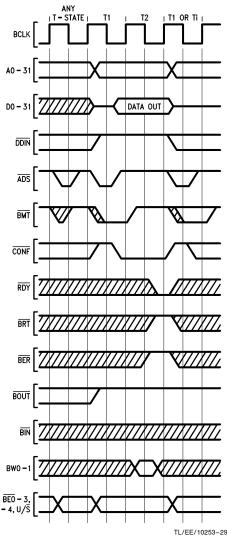

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19         General Reset Timing       3-20         Basic Read Cycle       3-21         Write Cycle       3-22                                                                                                                                                                                                                                                                                                          |

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19         General Reset Timing       3-20         Basic Read Cycle       3-21         Write Cycle       3-22         Burst Read cycles       3-23         Cycle Extension of a Basic Read Cycle       3-24         Slave Processor Write Cycle       3-25                                                                                                                                                             |

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19         General Reset Timing       3-20         Basic Read Cycle       3-21         Write Cycle       3-22         Burst Read cycles       3-23         Cycle Extension of a Basic Read Cycle       3-24         Slave Processor Write Cycle       3-25         Slave Processor Read Cycle       3-25                                                                                                               |

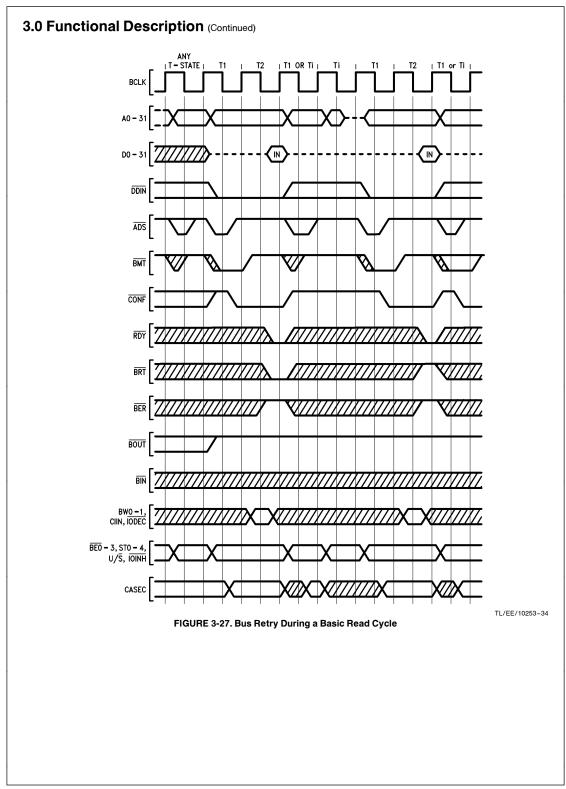

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19         General Reset Timing       3-20         Basic Read Cycle       3-21         Write Cycle       3-22         Burst Read cycles       3-23         Cycle Extension of a Basic Read Cycle       3-24         Slave Processor Write Cycle       3-25         Slave Processor Read Cycle       3-26         Bus Retry During a Basic Read Cycle       3-27                                                        |

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19         General Reset Timing       3-20         Basic Read Cycle       3-21         Write Cycle       3-22         Burst Read cycles       3-23         Cycle Extension of a Basic Read Cycle       3-24         Slave Processor Write Cycle       3-25         Slave Processor Read Cycle       3-25                                                                                                               |

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19         General Reset Timing       3-20         Basic Read Cycle       3-21         Write Cycle       3-22         Burst Read cycles       3-23         Cycle Extension of a Basic Read Cycle       3-24         Slave Processor Write Cycle       3-25         Slave Processor Read Cycle       3-26         Bus Retry During a Basic Read Cycle       3-27                                                        |

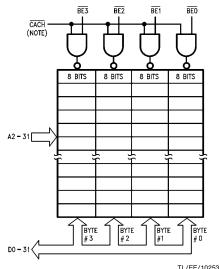

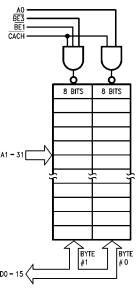

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled       3-11         Return From Interrupt (RETl) Instruction Flow: Direct-Exception Mode Disabled       3-12         Exception Processing Flowchart       3-13         Service Sequence       3-14         Instruction Cache Structure       3-15         Data Cache Structure       3-16         Power and Ground Connections       3-17         Bus Clock Synchronization       3-18         Power-On Reset Requirements       3-19         General Reset Timing       3-20         Basic Read Cycle       3-21         Write Cycle       3-21         Burst Read cycles       3-23         Cycle Extension of a Basic Read Cycle       3-24         Slave Processor Write Cycle       3-25         Slave Processor Read Cycle       3-25         Bus Retry During a Basic Read Cycle       3-27         Basic Interface for 32-Bit Memories       3-28 |

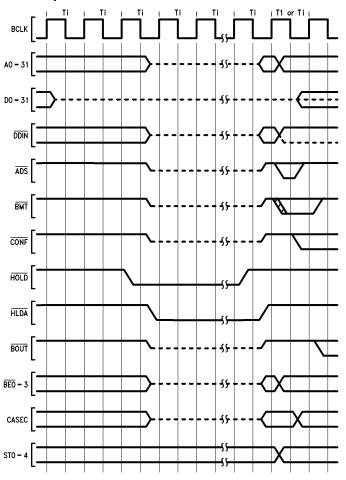

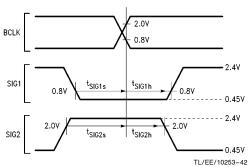

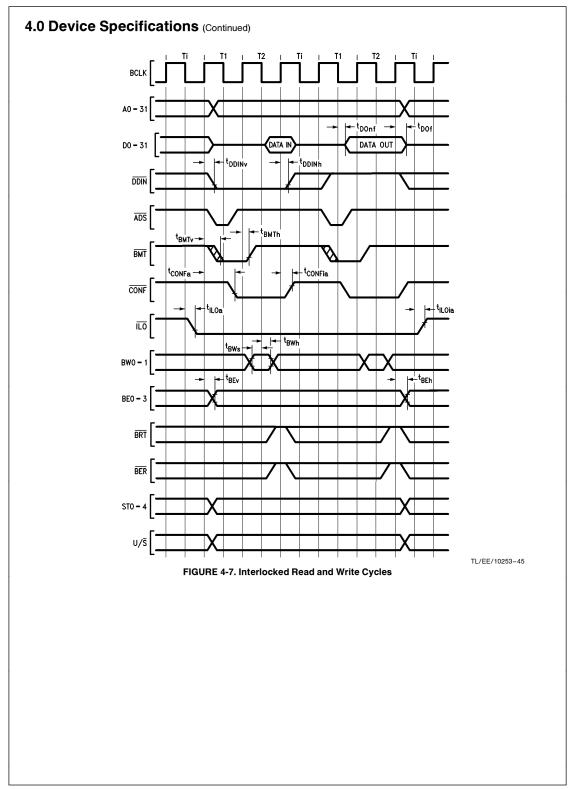

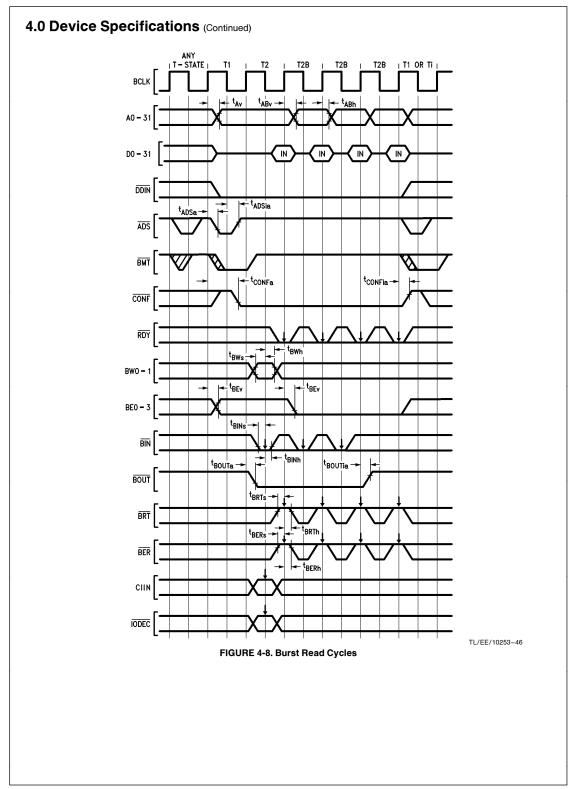

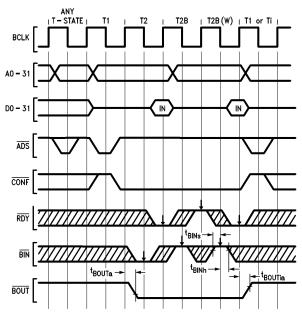

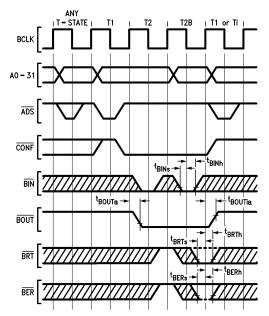

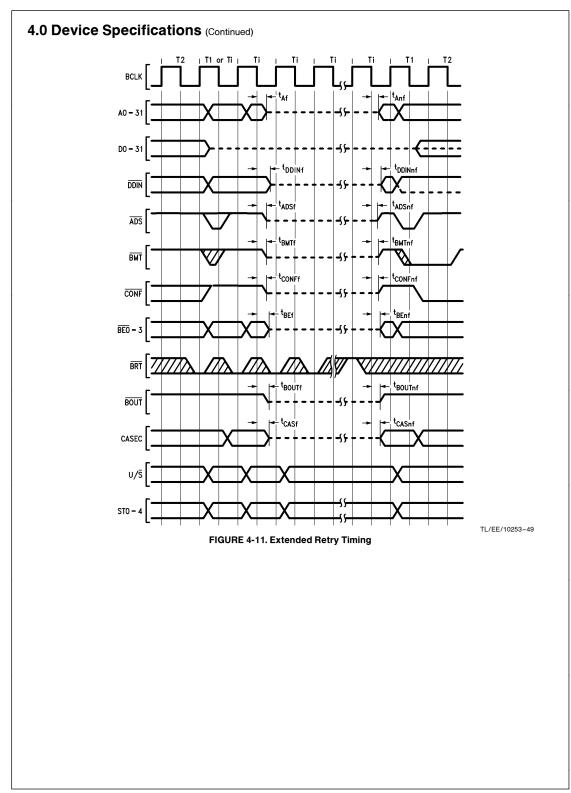

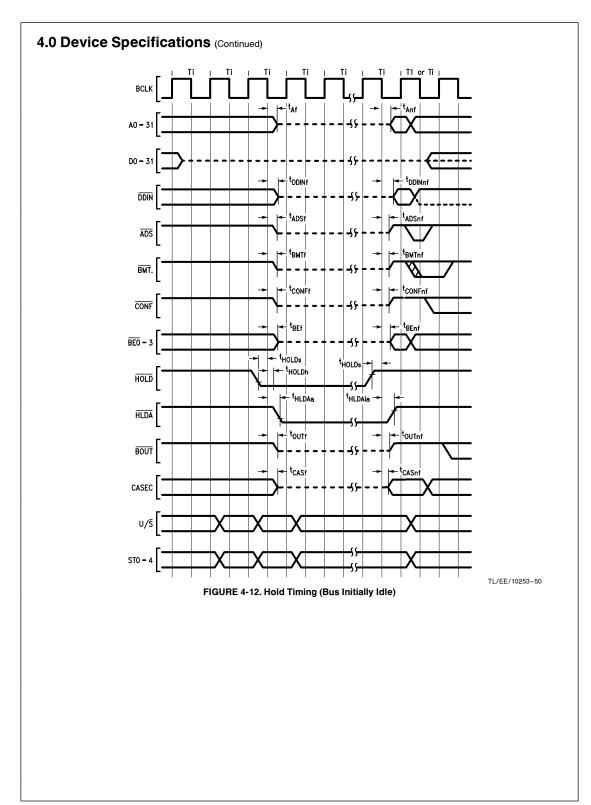

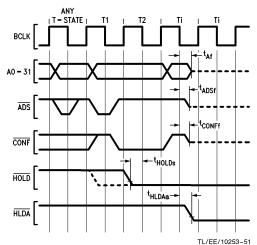

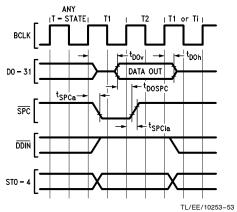

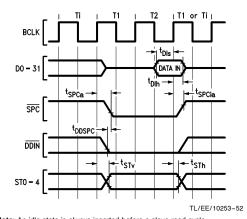

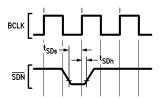

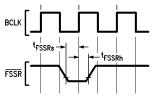

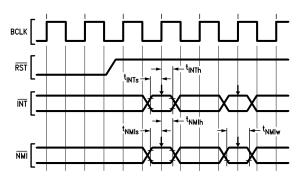

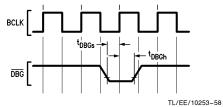

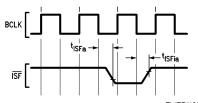

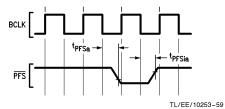

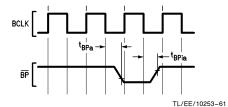

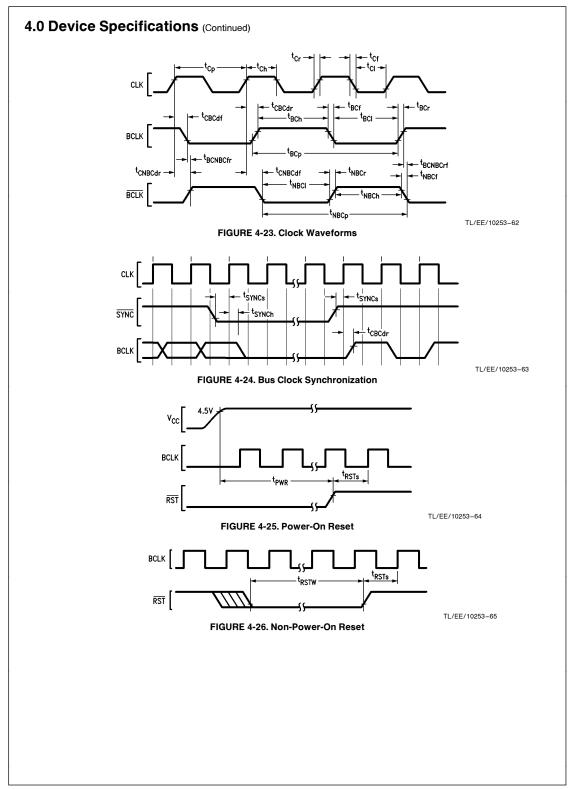

# List of Illustrations (Continued) NS32GX32 Interface Signals 4-1 Output Signals Specification Standard ......4-3 Input Signals Specification Standard ......4-4 Basic Read Cycle Timing ......4-5 Interlocked Read and Write Cycles ......4-7 Burst Read Cycles .....4-8 External Termination of Burst Cycles ......4-9 Extended Retry Timing 4-11 HOLD Timing (Bus Initially Idle) 4-12 Slave Processor Read Timing ......4-14 Slave Processor Write Timing 4-15 Debug Trap Request 4-19 Break Point Signal Timing 4-22 Clock Waveforms 4-23 Bus Clock Synchronization 4-24 Power-On Reset 4-25 Non-Power-On Reset 4-26 **List of Tables** Access Protection Levels 2-1 NS32GX32 Addressing Modes .....2-2 NS32GX32 Instruction Set Summary 2-3 Interrupt Sequences 3-4 Cacheable/Non-Cacheable Data Reads from a 32-Bit Bus Cacheable/Non-Cacheable Data Beads from an 8-Bit Bus 3-10 Data Writes to a 32-Bit Bus 3-11 Data Writes to a 16-Bit Bus

# 1.0 Product Introduction

The NS32GX32 is an extremely sophisticated microprocessor in the Series 32000 family with a full 32-bit architecture and implementation optimized for high-performance applications

By employing a number of mainframe-like features, the device can deliver 15 MIPS peaks performance with no wait states at a frequency of 30 MHz.

The NS32GX32 is fully software compatible will all the other Series 32000 CPUs. The architectural features of the Series 32000 family and particularly the NS32GX32 CPU, are described briefly below.

**Powerful Addressing Modes.** Nine addressing modes available to all instructions are included to access data structures efficiently.

**Data Types.** The architecture provides for numerous data types, such as byte, word, doubleword, and BCD, which may be arranged into a wide variety of data structures.

**Symmetric Instruction Set.** While avoiding special case instructions that compilers can't use, the Series 32000 architecture incorporates powerful instructions for control operations, such as array indexing and external procedure calls, which save considerable space and time for compiled code.

**Memory-to-Memory Operations.** The Series 32000 CPUs represent two-address machines. This means that each operand can be referenced by any one of the addressing modes provided.

This powerful memory-to-memory architecture permits memory locations to be treated as registers for all usefull operations. This is important for temporary operands as well as for context switching.

Large, Uniform Addressing. The NS32GX32 has 32-bit address pointers that can address up to 4 gigabytes without requiring any segmentation.

Modular Software Support. Any software package for the Series 32000 family can be developed independent of all other packages, without regard to individual addressing. In addition, ROM code is totally relocatable and easy to access, which allows a significant reduction in hardware and software costs.

Software Processor Concept. The Series 32000 architecture allows future expansions of the instruction set that can be executed by special slave processors, acting as extensions to the CPU. This concept of slave processors is unique to the Series 32000 family. It allows software compatibility even for future components because the slave hardware is transparent to the software. With future advances in semiconductor technology, the slaves can be physically integrated on the CPU chip itself.

To summarize, the architectural features cited above provide three primary performance advantages and characteristics:

- High-level language support

- · Easy future growth path

- · Application flexibility

# 2.0 Architectural Description

#### 2.1 REGISTER SET

The NS32GX32 CPU has 21 internal registers grouped according to functions as follows: 8 general purpose, 7 address, 1 processor status, 1 configuration, and 4 debug. All registers are 32 bits wide except for the module and procesor status, which are each 16 bits wide. *Figure 2-1* shows the NS32GX32 internal registers.

| ← | Address<br>32 Bits | $\rightarrow$ |

|---|--------------------|---------------|

|   | PC                 |               |

|   | SP0                |               |

|   | SP1                |               |

|   | FP                 |               |

|   | SB                 |               |

|   | INTBASE            |               |

|   |                    | MOD           |

| <b>Processor Status</b> |

|-------------------------|

| PSR                     |

| General Purpose<br>← 32 Bits → |

|--------------------------------|

| R0                             |

| R1                             |

| R2                             |

| R3                             |

| R4                             |

| R5                             |

| R6                             |

| B7                             |

| Debug |

|-------|

| DCR   |

| DSR   |

| CAR   |

| BPC   |

| Configuration |  |

|---------------|--|

| CFG           |  |

FIGURE 2-1. NS32GX32 Internal Registers

#### 2.1.1 General Purpose Registers

There are eight registers (R0-R7) used for satisfying the high speed general storage requirements, such as holding temporary variables and addresses. The general purpose registers are free for any use by the programmer. They are 32 bits in length. If a general purpose register is specified for an operand that is eight or 16 bits long, only the low part of the register is used; the high part is not referenced or modified

#### 2.1.2 Address Registers

The seven address registers are used by the processor to implement specific address functions. A description of them follows.

**PC—Program Counter.** The PC register is a pointer to the first byte of the instruction currently being executed. The PC is used to reference memory in the program section.

SP0, SP1—Stack Pointers. The SP0 register points to the lowest address of the last item stored on the INTERRUPT STACK. This stack is normally used only by the operating system. It is used primarily for storing temporary data, and holding return information for operating system subroutines and interrupt and trap service routines. The SP1 register points to the lowest address of the last item stored on the USER STACK. This stack is used by normal user programs to hold temporary data and subroutine return information.

When a reference is made to the selected Stack Pointer (see PSR S-bit), the terms 'SP Register' or 'SP' are used. SP refers to either SP0 or SP1, depending on the setting of the S bit in the PSR register. If the S bit in the PSR is 0, SP refers to SP0. If the S bit in the PSR is 1 then SP refers to SP1.

The NS32GX32 also allows the SP1 register to be directly loaded and stored using privileged forms of the LPRi and SPRi instructions, regardless of the setting of the PSR S-bit. When SP1 is accessed in this manner, it is referred to as 'USP Register' or simply 'USP'.

Stacks in the Series 32000 family grow downward in memory. A Push operation pre-decrements the Stack Pointer by the operand length. A Pop operation post-increments the Stack Pointer by the operand length.

**FP—Frame Pointer.** The FP register is used by a procedure to access parameters and local variables on the stack. The FP register is set up on procedure entry with the ENTER instruction and restored on procedure termination with the EXIT instruction.

The frame pointer holds the address in memory occupied by the old contents of the frame pointer.

SB—Static Base. The SB register points to the global variables of a software module. This register is used to support relocatable global variables for software modules. The SB register holds the lowest address in memory occupied by the global variables of a module.

**INTBASE—Interrupt Base.** The INTBASE register holds the address of the dispatch table for interrupts and traps (Section 3.2.1).

MOD—Module. The MOD register holds the address of the module descriptor of the currently executing software module. The MOD register is 16 bits long, therefore the module table must be contained within the first 64 kbytes of memory.

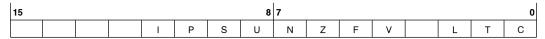

#### 2.1.3 Processor Status Register

The Processor Status Register (PSR) holds status information for the microprocessor.

The PSR is sixteen bits long, divided into two eight-bit halves. The low order eight bits are accessible to all programs, but the high order eight bits are accessible only to programs executing in Supervisor Mode.

- C The C bit indicates that a carry or borrow occurred after an addition or subtraction instruction. It can be used with the ADDC and SUBC instructions to perform multiple-precision integer arithmetic calculations. It may have a setting of 0 (no carry or borrow) or 1 (carry or borrow).

- T The T bit causes program tracing. If this bit is set to 1, a TRC trap is executed after every instruction (Section 3.3.1).

- L The L bit is altered by comparison instructions. In a comparison instruction the L bit is set to "1" if the second operand is less than the first operand, when both operands are interpreted as unsigned integers. Otherwise, it is set to "0". In Floating-Point comparisons, this bit is always cleared.

- V The V-bit enables generation of a trap (OVF) when an integer arithmetic operation overflows.

- F The F bit is a general condition flag, which is altered by many instructions (e.g., integer arithmetic instructions use it to indicate overflow).

- Z The Z bit is altered by comparison instructions. In a comparison instruction the Z bit is set to "1" if the second operand is equal to the first operand; otherwise it is set to "0".

- N The N bit is altered by comparison instructions. In a comparison instruction the N bit is set to "1" if the second operand is less than the first operand, when both operands are interpreted as signed integers. Otherwise, it is set to "0".

- U If the U bit is "1" no privileged instructions may be executed. If the U bit is "0" then all instructions may be executed. When U = 0 the processor is said to be in Supervisor Mode; when U = 1 the processor is said to

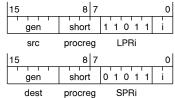

FIGURE 2-2. Processor Status Register (PSR)

be in User Mode. A User Mode program is restricted from executing certain instructions and accessing certain registers which could interfere with the operating system. For example, a User Mode program is prevented from changing the setting of the flag used to indicate its own privilege mode. A Supervisor Mode program is assumed to be a trusted part of the operating system, hence it has no such restrictions.

- S The S bit specifies whether the SP0 register or SP1 register is used as the Stack Pointer. The bit is automatically cleared on interrupts and traps. It may have a setting of 0 (use the SP0 register) or 1 (use the SP1 register).

- P The P bit prevents a TRC trap from occuring more than once for an instruction (Section 3.3.1). It may have a setting of 0 (no trace pending) or 1 (trace pending).

- I If I = 1, then all interrupts will be accepted. If I = 0, only the NMI interrupt is accepted. Trap enables are not affected by this bit.

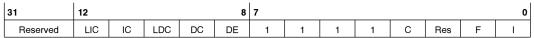

#### 2.1.4 Configuration Register

The Configuration Register (CFG) is 32 bits wide, of which ten bits are implemented. The implemented bits enable various operating modes for the CPU, including vectoring of interrupts, execution of slave instructions, and control of the on-chip caches. In the NS32332 bits 4 through 7 of the CFG register selected between the 16-bit and 32-bit slave protocols and between 512-byte and 4-Kbyte page sizes. The NS32GX32 supports only the 32-bit slave protocol and no memory management: consequently these bits are forced to 1.

When the CFG register is loaded using the LPRi instruction, bit 2 and bits 13 through 31 should be set to 0. Bits 4 through 7 are ignored during loading, and are always returned as 1's when CFG is stored via the SPRi instruction. When the SETCFG instruction is executed, the contents of the CFG register bits 0 through 3 are loaded from the instruction's short field, bits 4 through 7 are ignored and bits 8 through 12 are forced to 0. Bit 2 must be set to 0.

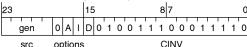

The format of the CFG register is shown in *Figure 2-3*. The various control bits are described below.

- I Interrupt vectoring. This bit controls whether maskable interrupts are handled in nonvectored (I=0) or vectored (I=1) mode. Refer to Section 3.2.3 for more information.

- F Floating-point instruction set. This bit indicates whether a floating-point unit (FPU) is present to execute floating-point instructions. If this bit is 0 when the CPU executes a floating-point instruction, a Trap (UND) occurs. If this bit is 1, then the CPU transfers the instruction and any necessary operands to the FPU using the slave-processor protocol described in Section 3.1.4.1.

- C Custom instruction set. This bit indicates whether a custom slave processor is present to execute custom instructions. If this bit is 0 when the CPU executes a custom instruction, a Trap (UND) occurs. If this bit is 1, the CPU transfers the instruction and any necessary operands to the custom slave processor using the slave-processor protocol described in Section 3.1.4.1.

- Direct-Exception mode enable. This bit enables the Direct-Exception mode for processing exceptions. When this mode is selected, the CPU response time to interrupts and other exceptions is significantly improved. Refer to Section 3.2.1 for more information.

- DC Data Cache enable. This bit enables the on-chip Data Cache to be accessed for data reads and writes. Refer to Section 3.4.2 for more information.

- LDC Lock Data Cache. This bit controls whether the contents of the on-chip Data Cache are locked to fixed memory locations (LDC=1), or updated when a data read is missing from the cache (LDC=0).

- IC Instruction Cache enable. This bit enables the onchip Instruction Cache to be accessed for instruction fetches. Refer to Section 3.4.1 for more information.

- LIC Lock Instruction Cache. This bit controls whether the contents of the on-chip Instruction Cache are locked to fixed memory locations (LIC=1), or updated when an instruction fetch is missing from the cache (LIC=0).

FIGURE 2-3. Configuration Register (CFG) Bits 13 to 31 are Reserved; Bits 4 to 7 are Forced to 1

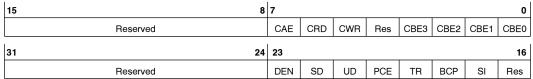

#### 2.1.5 Debug Registers

The NS32GX32 contains 4 registers dedicated for debugging functions.

These registers are accessed using privileged forms of the LPRi and SPRi instructions.

**DCR—Debug Condition Register.** The DCR Register enables detection of debug conditions. The format of the DCR is shown in *Figure 2-4*; the various bits are described below. A debug condition is enabled when the related bit is set to 1.

CBE0 Compare Byte Enable 0; when set, BYTE0 of an aligned double-word is included in the address comparison

CBE1 Compare Byte Enable 1; when set, BYTE1 of an aligned double-word is included in the address comparison

CBE2 Compare Byte Enable 2; when set, BYTE2 of an aligned double-word is included in the address comparison

CBE3 Compare Byte Enable 3; when set, BYTE3 of an aligned double-word is included in the address comparison

CWR Address-compare enable for write referencesCRD Address-compare enable for read references

CAE Address-compare enable

TR Enable Trap (DBG) when a debug condition is detected

PCE PC-match enable

**UD** Enable debug conditions in User-Mode

SD Enable debug conditions in Supervisor Mode

**DEN** Enable debug conditions

The following 2 bits control testing features that can be used during initial system debugging. These features are unique to the NS32GX32 implementation of the Series 32000 architecture; as such, they may not be supported in tuture implementations. For normal operation these 2 bits should be set to 0.

SI Single-Instruction mode enable. This bit, when set to 1, inhibits the overlapping of instruction's execution.

BCP Branch Condition Prediction disable. When this bit is 1, the branch prediction mechanism is disabled. See Section 3.1.3.1.

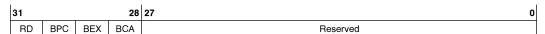

**DSR—Debug Status Register.** The DSR Register indicates debug conditions that have been detected. When the CPU detects an enabled debug condition, it sets the corresponding bit (BC, BEX, BCA) in the DSR to 1. When an address-compare condition is detected, then the RD-bit is loaded to indicate whether a read or write reference was performed. Software must clear all the bits in the DSR when appropriate. The format of the DSR is shown in *Figure 2-5*; the various fields are described below.

RD Indicates whether the last address-compare condition was for a read (RD = 1) or write (RD = 0) reference

BPC PC-match condition detected

BEX External condition detected

BCA Address-compare condition detected

Note 1: The content of the DSR register is not defined if a debug condition was detected on a floating-point instruction in pipelined mode and a trap was generated by a previous floating-point instruction.

Note 2: If an address compare is detected on a read and a write for the same instruction then the RD-bit will remain clear.

**CAR—Compare Address Register.** The CAR Register contains the address that is compared to operand reference addresses to detect an address-compare condition. The address must be double-word aligned; that is, the two least-significant bits must be 0. The CAR is 32 bits wide.

FIGURE 2-4. Debug Condition Register (DCR)

FIGURE 2-5. Debug Status Register (DSR)

BPC—Breakpoint Program Counter. The BPC Register contains the address that is compared with the PC contents to detect a PC-match condition. The BPC Register is 32 bits wide.

#### 2.2 MEMORY ORGANIZATION

The NS32GX32 implements full 32-bit addresses. This allows the CPU to access up to 4 Gbytes of memory. The memory is a uniform linear address space. Memory locations are numbered sequentially starting at zero and ending at  $2^{32}-1$ . The number specifying a memory location is called an address. The contents of each memory location is a byte consisting of eight bits. Unless otherwise noted, diagrams in this document show data stored in memory with the lowest address on the right and the highest address on the left. Also, when data is shown vertically, the lowest address is at the top of a diagram and the highest address at the bottom of the diagram. When bits are numbered in a diagram, the least significant bit is given the number zero, and is shown at the right of the diagram. Bits are numbered in increasing significance and toward the left.

#### Byte at Address A

Two contiguous bytes are called a word. Except where noted, the least significant byte of a word is stored at the lower address, and the most significant byte of the word is stored at the next higher address. In memory, the address of a word is the address of its least significant byte, and a word may start at any address.

| 15 |       | 8 | 7   | 0 |

|----|-------|---|-----|---|

|    | A + 1 |   | Α   |   |

|    | MSB   |   | LSB |   |

Address (Hex)

**FFFFFFF**

#### Word at Address A

Two contiguous words are called a double-word. Except where noted, the least significant word of a double-word is

stored at the lowest address and the most significant word of the double-word is stored at the address two higher. In memory, the address of a double-word is the address of its least significant byte, and a double-word may start at any address.

| 31  | 24 | 23 | 16  | 15 | 8   | 7   | 0 |

|-----|----|----|-----|----|-----|-----|---|

| A+3 |    |    | A+2 |    | A+1 | Α   |   |

| MSB |    |    |     |    |     | LSB |   |

#### Double-Word at Address A

Although memory is addressed as bytes, it is actually organized as double-words. Note that access time to a word or a double-word depends upon its address, e.g. double-words that are aligned to start at addresses that are multiples of four will be accessed more quickly than those not so aligned. This also applies to words that cross a double-word boundary.

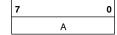

#### 2.2.1 Address Mapping

Figure 2-6 shows the NS32GX32 address mapping.

The NS32GX32 supports the use of memory-mapped peripheral devices and coprocessors. Such memory-mapped devices can be located at arbitrary locations in the address space except for the upper 8 Mbytes of memory (addresses between FF800000 (hex) and FFFFFFF (hex), inclusive), which are reserved by National Semiconductor Corporation. Nevertheless, it is recommended that high-performance peripheral devices and coprocessors be located in a specific 8 Mbyte region of memory (addresses between FF000000 (hex) and FF7FFFFF (hex), inclusive), that is dedicated for memory-mapped I/O. This is because the NS32GX32 detects references to the dedicated locations and serializes reads and writes. See Section 3.1.3.3. When making I/O references to addresses outside the dedicated region, external hardware must indicate to the NS32GX32 that special handling is required.

In this case a small performance degradation will also result. Refer to Section 3.1.3.2 for more information on memory-mapped I/O.

FIGURE 2-6. NS32GX32 Address Mapping

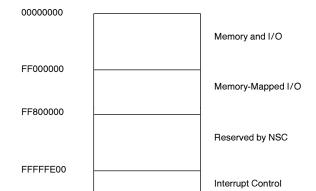

# 2.0 Architectural Description (Continued) 2.3 MODULAR SOFTWARE SUPPORT

The NS32GX32 provides special support for software modules and modular programs.

Each module in a NS32GX32 software environment consists of three components:

#### 1. Program Code Segment.

This segment contains the module's code and constant data

#### 2. Static Data Segment.

Used to store variables and data that may be accessed by all procedures within the module.

#### 3 Link Table

This component contains two types of entries: Absolute Addresses and Procedure Descriptors.

An Absolute Address is used in the external addressing mode, in conjunction with a displacement and the current MOD Register contents to compute the effective address of an external variable belonging to another module.

The Procedure Descriptor is used in the call external procedure (CXP) instruction to compute the address of an external procedure.

Normally, the linker program specifies the locations of the three components. The Static Data and Link Table typically reside in RAM; the code component can be either in RAM or in ROM. The three components can be mapped into noncontiguous locations in memory, and each can be independently relocated. Since the Link Table contains the absolute addresses of external variables, the linker need not assign absolute memory addresses for these in the module itself; they may be assigned at load time.

To handle the transfer of control from one module to another, the NS32GX32 uses a module table in memory and two registers in the CPU.

The Module Table is located within the first 64 kbytes of memory. This table contains a Module Descriptor (also called a Module Table Entry) for each module in the address space of the program. A Module Descriptor has four 32-bit entries corresponding to each component of a module.

- The Static Base entry contains the address of the beginning of the module's static data segment.

- The Link Table Base points to the beginning of the module's Link Table.

- The Program Base is the address of the beginning of the code and constant data for the module.

- · A fourth entry is currently unused but reserved

The MOD Register in the CPU contains the address of the Module Descriptor for the currently executing module.

The Static Base Register (SB) contains a copy of the Static Base entry in the Module Descriptor of the currently executing module, i.e., it points to the beginning of the current module's static data area.

This register is implemented in the CPU for efficiency purposes. By having a copy of the static base entry or chip, the CPU can avoid reading it from memory each time a data item in the static data segment is accessed.

In an NS32GX32 software environment modules need not be linked together prior to loading. As modules are loaded, a linking loader simply updates the Module Table and fills the Link Table entries with the appropriate values. No modification of a module's code is required. Thus, modules may be stored in read-only memory and may be added to a system independently of each other, without regard to their individual addressing. *Figure 2-7* shows a typical NS32GX32 run-time environment.

TL/EE/10253-2

Note: Dashed lines indicate information copied to registers during transfer of control between modules.

FIGURE 2-7. NS32GX32 Run-Time Environment

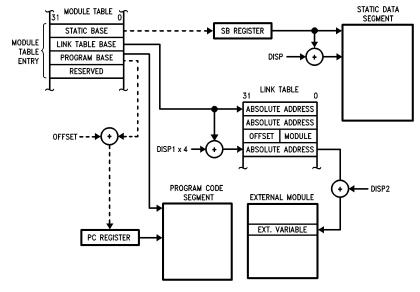

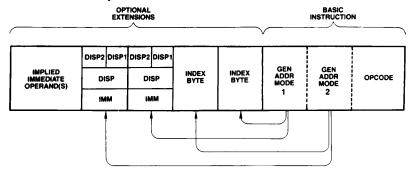

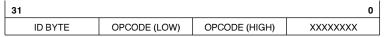

FIGURE 2-8. General Instruction Format

TL/EE/10253-5

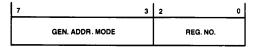

FIGURE 2-9. Index Byte Format

TL/EE/10253-6

#### 2.4 INSTRUCTION SET

#### 2.4.1 General Instruction Format

Figure 2-8 shows the general format of a Series 32000 instruction. The Basic Instruction is one to three bytes long and contains the Opcode and up to two 5-bit General Addressing Mode ("Gen") fields. Following the Basic Instruction field is a set of optional extensions, which may appear depending on the instruction and the addressing modes selected

Index Bytes appear when either or both Gen fields specify Scaled Index. In this case, the Gen field specifies only the Scale Factor (1, 2, 4 or 8), and the Index Byte specifies which General Purpose Register to use as the index, and which addressing mode calculation to perform before indexing. See *Figure 2-9*.

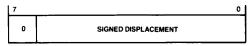

Following Index Bytes come any displacements (addressing constants) or immediate values associated with the selected addressing modes. Each Disp/Imm field may contain one or two displacements, or one immediate value. The size of a Displacement field is encoded with the top bits of that field, as shown in *Figure 2-10*, with the remaining bits interpreted as a signed (two's complement) value. The size of an immediate value is determined from the Opcode field. Both Displacement and Immediate fields are stored most significant byte first. Note that this is different from the memory representation of data (Section 2.2).

Some instructions require additional, 'implied'' immediates and/or displacements, apart from those associated with addressing modes. Any such extensions appear at the end of the instruction, in the order that they appear within the list of operands in the instruction definition (Section 2.4.3).

# 2.4.2 Addressing Modes

The CPU generally accesses an operand by calculating its Effective Address based on information available when the operand is to be accessed. The method to be used in performing this calculation is specified by the programmer as an "addressing mode."

Byte Displacement: Range -64 to +63

#### Word Displacement: Range -8192 to +8191

# Double Word Displacement: Range $-(2^{29}-2^{24})$ to $+(2^{29}-1)^*$

TL/EE/10253-7

#### FIGURE 2-10. Displacement Encodings

\*Note: The pattern "11100000" for the most significant byte of the displacement is reserved by National for future enhancements. Therefore, it should never be used by the user program. This causes the lower limit of the displacement range to be -(229-224) instead of -229.

Addressing modes are designed to optimally support highlevel language accesses to variables. In nearly all cases, a variable access requires only one addressing mode, within the instruction that acts upon that variable. Extraneous data movement is therefore minimized.

Addressing Modes fall into nine basic types:

Register: The operand is available in one of the eight General Purpose Registers. In certain Slave Processor instructions, an auxiliary set of eight registers may be referenced instead.

Register Relative: A General Purpose Register contains an address to which is added a displacement value from the instruction, yielding the Effective Address of the operand in memory.

**Memory Space:** Identical to Register Relative above, except that the register used is one of the dedicated registers PC, SP, SB or FP. These registers point to data areas generally needed by high-level languages.

**Memory Relative:** A pointer variable is found within the memory space pointed to by the SP, SB or FP register. A displacement is added to that pointer to generate the Effective Address of the operand.

**Immediate:** The operand is encoded within the instruction. This addressing mode is not allowed if the operand is to be written.

**Absolute:** The address of the operand is specified by a displacement field in the instruction.

**External:** A pointer value is read from a specified entry of the current Link Table. To this pointer value is added a displacement, yielding the Effective Address of the operand.

**Top of Stack:** The currently-selected Stack Pointer (SP0 or SP1) specifies the location of the operand. The operand is pushed or popped, depending on whether it is written or read

Scaled Index: Although encoded as an addressing mode, Scaled Indexing is an option on any addressing mode except Immediate or another Scaled Index. It has the effect of calculating an Effective Address, then multiplying any Gen-

eral Purpose Register by 1, 2, 4 or 8 and adding it into the total, yielding the final Effective Address of the operand.

Table 2-2 is a brief summary of the addressing modes. For a complete description of their actions, see the Instruction Set Reference Manual.

#### 2.4.3 Instruction Set Summary

Table 2-3 presents a brief description of the NS32GX32 instruction set. The Format column refers to the Instruction Format tables (Appendix A). The Instruction column gives the instruction as coded in assembly language, and the Description column provides a short description of the function provided by that instruction. Further details of the exact operations performed by each instruction may be found in the Instruction Set Reference Manual.

#### **Notations:**

i = Integer length suffix: B = Byte

W = Word

D = Double Word

f = Floating Point length suffix: F = Standard Floating

L = Long Floating

gen = General operand. Any addressing mode can be specified.

short = A 4-bit value encoded within the Basic Instruction (see Appendix A for encodings).

imm = Implied immediate operand. An 8-bit value appended after any addressing extensions.

disp = Displacement (addressing constant): 8, 16 or 32 bits. All three lengths legal.

reg = Any General Purpose Register: R0-R7.

areg = Any Processor Register: Address, Debug, Status, Configuration.

$\mbox{creg} = \mbox{A Custom Slave Processor Register (Implementation Dependent)}.$

${\tt cond} = {\tt Any \ condition \ code}, \ {\tt encoded} \ as \ a \ 4-bit \ field \ within \ the \ {\tt Basic \ Instruction} \ ({\tt see \ Appendix \ A \ for \ encodings}).$

# TABLE 2-2. NS32GX32 Addressing Modes

| ENCODING          | MODE                                     | ASSEMBLER SYNTAX   | EFFECTIVE ADDRESS                                                                                                      |

|-------------------|------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|

| Register          |                                          |                    |                                                                                                                        |

| 00000             | Register 0                               | R0, F0, L0         | None: Operand is in the                                                                                                |

| 00001             | Register 1                               | R1, F1, L1         | specified register.                                                                                                    |

| 00010             | Register 2                               | R2, F2, L2         |                                                                                                                        |

| 00011             | Register 3                               | R3, F3, L3         |                                                                                                                        |

| 00100             | Register 4                               | R4, F4, L4         |                                                                                                                        |

| 00101             | Register 5                               | R5, F5, L5         |                                                                                                                        |

| 00110             | Register 6                               | R6, F6, L6         |                                                                                                                        |

| 00111             | Register 7                               | R7, F7, L7         |                                                                                                                        |

| Register Relative |                                          |                    |                                                                                                                        |

| 01000             | Register 0 relative                      | disp(R0)           | Disp + Register.                                                                                                       |