Release Date: May, 1997

Order Number: 272834-004

The 8XC196KC may contain design defects or errors known as errata. Characterized errata that may cause the 8XC196KC's behavior to deviate from published specifications are documented in this specification update.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

\*Third-party brands and names are the property of their respective owners.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect IL 60056-7641

or call in North America 1-800-879-4683, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other countries 708-296-9333

Copyright © 1996, INTEL CORPORATION

### **CONTENTS**

| CONTENTS                     | iii |

|------------------------------|-----|

| REVISION HISTORY             | 1   |

| PREFACE                      | 2   |

| SUMMARY TABLE OF CHANGES     | 4   |

| IDENTIFICATION INFORMATION   | 10  |

| ERRATA                       | 11  |

| SPECIFICATION CHANGES        | 31  |

| SPECIFICATION CLARIFICATIONS | 31  |

| DOCUMENTATION CHANGES        | 39  |

### **REVISION HISTORY**

This Specification Update supersedes TechBit MC3191 (Notes CWFME1) and contains all the known errata for the 8XC196KC and 8E196KC devices.

| Rev. Date | Version | Description                                                                                                                                                                                                                                                                                                                |

|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07/01/96  | 001     | This is the new Specification Update document. It contains all identified errata published prior to this date.                                                                                                                                                                                                             |

| 11/13/96  | 002     | Corrected the table, Errata - Part I, and reformatted the table to fit on a single page for readability. Note that Errata - Part I shows the products and steppings to which each erratum applies, while Errata - Part II provides a brief description of each erratum and the page number for its associated description. |

| 03/12/97  | 003     | Corrections were made to the errata and identification information markings summary tables.                                                                                                                                                                                                                                |

| 05/13/97  | 004     | Documentation change 054 and specification clarification 022.                                                                                                                                                                                                                                                              |

272834-004 May, 1997 1 of 51

#### PREFACE

As of July, 1996, Intel's Semiconductor Products Group has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### Affected Documents/Related Documents

| Title                                                            | Order  |

|------------------------------------------------------------------|--------|

| 8XC196KC/KC20 Commercial/Express CHMOS Microcontroller datasheet | 270942 |

| Embedded Microcontrollers                                        | 270646 |

| 8XC196KC/KD User's Manual (1992)                                 | 272238 |

| 8XC196KC Quick Reference                                         | 272112 |

| 80C196KC User's Guide                                            | 270704 |

| 8XC196KB/KC/KD Programming Support Fact Sheet                    | 272225 |

| Development Tools Handbook                                       | 272326 |

| ApBUILDER Interactive Application Programming Package Disk       | 272216 |

| Project Builder 196 "FREE" Demo Software                         | 272329 |

#### Nomenclature

**Errata** are design defects or errors. These may cause the published (component, board, system) behavior to deviate from published specifications. Hardware and software designed to be used with any component, board, and system must consider all errata documented.

# intط

#### **8XC196KC SPECIFICATION UPDATE**

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

#### NOTE:

Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

272834-004 May, 1997 3 of 51

#### SUMMARY TABLE OF CHANGES

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the 8XC196KC product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

### Codes Used in Summary Table

### Stepping

X: Errata exists in the stepping indicated. Specification Change

or Clarification that applies to this stepping.

(No mark) or (Blank box): This erratum is fixed in listed stepping or specification change

does not apply to listed stepping.

Page

(Page): Page location of item in this document.

Status

Doc: Document change or update will be implemented.

Fix: This erratum is intended to be fixed in a future step of the com-

ponent.

Fixed: This erratum has been previously fixed. NoFix: There are no plans to fix this erratum.

Eval: Plans to fix this erratum are under evaluation.

Row

Change bar to left of table row indicates this erratum is either

new or modified from the previous version of the document.

### Errata - Part I

|         |          |          | Products and Steppings |          |          |          |          |          |          |          |          |          |          |          |          |          |        |

|---------|----------|----------|------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--------|

|         |          | Α        | Α                      | В        | B1       | B2       | В3       | B2       | C3       | D0       | A1       | D0       | D0       | D1       | В        | Е        |        |

|         | ID       | Α        |                        | Α        | В        | С        | D        | В        | G        | Н        | J        | K        | L        | М        | N        | U        | 1_     |

| Number  | Old<br># | 87C196KC | 8EC196KC               | 8EC196KC | 87C196KC | 87C196KC | 87C196KC | 8EC196KC | 80C196KC | 80C196KC | 80C196KC | 80C196KC | 83C196KC | 87C196KC | 83C196KC | 87C196KC | Status |

| 9600001 | 101      | Χ        | Χ                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600002 | 109      | Χ        | Х                      | Х        | Χ        | Х        | R        |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600003 | 115      | Χ        | Χ                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600004 | 116      | R        | Х                      | Х        | Χ        | Х        | Х        | Χ        | Χ        | Χ        | Χ        | Χ        | Χ        | Χ        | Х        | Х        | NoFix  |

| 9600005 | 123      |          |                        | Х        | Χ        | Х        | R        |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600006 | 126      | Χ        | Х                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600007 | 131      | Χ        | Χ                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600008 | 132      | Χ        | Х                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600009 | 140      | Χ        | Χ                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600010 | 143      | Χ        | Χ                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600011 | 147      | R        | Χ                      | Χ        | Χ        | Χ        | Χ        | Χ        | Χ        | Χ        | Χ        | Χ        | Χ        | Χ        | Χ        | Х        | NoFix  |

| 9600012 | 150      | Χ        | Χ                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600013 | 163      | Χ        | Χ                      | Χ        | Χ        | Χ        | R        |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600014 | 173      | Χ        | Х                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600015 | 174      | Χ        |                        |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600016 | 175      | Χ        |                        |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600017 | 176      | Χ        |                        |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600018 | 177      | Χ        |                        |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600019 | 178      | Χ        |                        |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600020 | 179      | Χ        |                        |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600021 | 180      | Χ        |                        |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600022 | 181      | Χ        |                        |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600023 | 182      |          | Х                      |          |          |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600024 | 214      |          |                        | Χ        | Χ        |          |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600025 | 215      | Χ        | Х                      | Х        | R        | Χ        |          |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600026 | 216      | Χ        | Χ                      | Х        | Х        | Х        | R        |          |          |          |          |          |          |          |          |          | Fixed  |

| 9600027 | 300      |          |                        |          |          |          |          |          | Х        |          |          |          |          |          |          |          | Fixed  |

| 9600028 | 300      | Х        | Х                      | Х        | Х        | Х        | R        | Χ        | X        | Χ        | Х        | Х        | Χ        |          |          |          | Fixed  |

| 9600029 | 300      | Х        | Х                      | Х        | Х        | Х        | R        | Х        | Χ        | Χ        | Х        | Х        | Х        | Х        | Х        | Х        | NoFix  |

| 9600030 | 300      | Х        | Х                      | Х        | Х        | Х        | R        | Х        | Х        | Х        | Х        | Х        | Х        | Х        | Х        | Х        | NoFix  |

| 9600031 | 300      | Χ        | X                      | Х        | X        | X        | R        | X        | X        | X        | X        | X        | Χ        | X        | X        | Х        | NoFix  |

| 9600032 | 300      | X        | X                      | Х        | X        | X        | R        | X        | X        | Х        | X        | X        | X        | X        | X        | Х        | NoFix  |

| 9600033 | 300      |          |                        |          |          |          |          |          | R        | Х        | Х        | Х        | Χ        | Х        |          | Х        | Fixed  |

<sup>&</sup>quot;R" identifies the stepping in which a problem was first reported.

### Errata - Part II

| Number  | Old# | Page | Errata                                                        |  |  |  |  |

|---------|------|------|---------------------------------------------------------------|--|--|--|--|

| 9600001 | 101  | 11   | A/D Cancel Error                                              |  |  |  |  |

| 9600002 | 109  | 11   | Divide Error With HOLD# or READY                              |  |  |  |  |

| 9600003 | 115  | 12   | HSO IOC1 Bits Interchanged                                    |  |  |  |  |

| 9600004 | 116  | 12   | Indirect Shift Count Value                                    |  |  |  |  |

| 9600005 | 123  | 12   | NMI During PTS Skips an Address                               |  |  |  |  |

| 9600006 | 126  | 13   | Port 0 Latched on Wrong Phase                                 |  |  |  |  |

| 9600007 | 131  | 13   | PTS Request During Interrupt Latency                          |  |  |  |  |

| 9600008 | 132  | 14   | NMI During PTS Latency                                        |  |  |  |  |

| 9600009 | 140  | 15   | SIO RI Flag                                                   |  |  |  |  |

| 9600010 | 143  | 15   | TIJMP INDEX_MASK Value Limitation                             |  |  |  |  |

| 9600011 | 147  | 15   | Write Cycle During Reset                                      |  |  |  |  |

| 9600012 | 150  | 17   | Serial Port Framing Error                                     |  |  |  |  |

| 9600013 | 163  | 17   | Glitch on Quasi-bidirectional (QBD) Port Pins During Power Up |  |  |  |  |

| 9600014 | 173  | 18   | A/D Linearity                                                 |  |  |  |  |

| 9600015 | 174  | 18   | Analog Input Latch-up                                         |  |  |  |  |

| 9600016 | 175  | 18   | INST Weakly Driven Low During CCB Fetch                       |  |  |  |  |

| 9600017 | 176  | 19   | 2 CCB Fetches                                                 |  |  |  |  |

| 9600018 | 177  | 19   | 3 Wait States During CCB Fetch                                |  |  |  |  |

| 9600019 | 178  | 19   | ALE, RD#, WR#, BHE, INST, TXD Pullup Too Weak During Reset    |  |  |  |  |

| 9600020 | 179  | 20   | Buswidth Is Permanently 16 Bits                               |  |  |  |  |

| 9600021 | 180  | 20   | Glitch on V <sub>CC</sub> Will Cause Device Reset             |  |  |  |  |

| 9600022 | 181  | 20   | Incomplete Reset At > 12MHz                                   |  |  |  |  |

| 9600023 | 182  | 21   | Default Buswidth Out of Reset is 16 Bits                      |  |  |  |  |

| 9600024 | 214  | 21   | ONCE Mode Entry                                               |  |  |  |  |

| 9600025 | 215  | 21   | Oscillator Noise Sensitivity                                  |  |  |  |  |

| 9600026 | 216  | 25   | Reset Hysteresis                                              |  |  |  |  |

| 9600027 | 300  | 25   | Port 0 CMOS Level                                             |  |  |  |  |

| 9600028 | 300  | 26   | Missing External Interrupt Requests (EXTINT, EXTINT1, NMI)    |  |  |  |  |

| 9600029 | 300  | 27   | BMOVI Windowing Count Register                                |  |  |  |  |

| 9600030 | 300  | 27   | HSI Events (9 or more)                                        |  |  |  |  |

| 9600031 | 300  | 29   | SIO Mode 0 Maximum Baud Rate                                  |  |  |  |  |

| 9600032 | 300  | 29   | Writing HSI_MODE Resets Divide-by-Eight Counter               |  |  |  |  |

| 9600033 | 300  | 30   | IPD Hump                                                      |  |  |  |  |

### Specification Changes

| Number | S | tepping | s | Page | Status                                               | Specification Changes |  |  |  |

|--------|---|---------|---|------|------------------------------------------------------|-----------------------|--|--|--|

| Number | # | #       | # | raye | Status                                               | Specification Changes |  |  |  |

|        |   |         |   |      | None for this revision of this specification update. |                       |  |  |  |

### Specification Clarifications

| Number Steppings |   | Steppings | js | Page | Status | Specification Clarifications                                                                 |  |

|------------------|---|-----------|----|------|--------|----------------------------------------------------------------------------------------------|--|

| Number           | # | #         | #  | rage | Status | Specification Glarifications                                                                 |  |

|                  |   |           |    |      |        | Spec. Clarifications 001-021 apply to document number 272238-001, 8XC196KC/KD User's Manual. |  |

| 001              |   |           |    | 31   | Doc    | Page 5-10                                                                                    |  |

| 002              |   |           |    | 31   | Doc    | Page 8-4                                                                                     |  |

| 003              |   |           |    | 32   | Doc    | Page 8-18                                                                                    |  |

| 004              |   |           |    | 33   | Doc    | Page 9-3                                                                                     |  |

| 005              |   |           |    | 33   | Doc    | Page 10-2                                                                                    |  |

| 006              |   |           |    | 33   | Doc    | Page 11-3                                                                                    |  |

| 007              |   |           |    | 34   | Doc    | Page 12-1                                                                                    |  |

| 800              |   |           |    | 34   | Doc    | Page 13-4                                                                                    |  |

| 009              |   |           |    | 35   | Doc    | Page 13-22                                                                                   |  |

| 010              |   |           |    | 36   | Doc    | Page 14-15                                                                                   |  |

| 011              |   |           |    | 36   | Doc    | Page 14-17                                                                                   |  |

| 012              |   |           |    | 36   | Doc    | Page 14-31                                                                                   |  |

| 013              |   |           |    | 36   | Doc    | Page 14-33                                                                                   |  |

| 014              |   |           |    | 36   | Doc    | Page B-9                                                                                     |  |

| 015              |   |           |    | 37   | Doc    | Page B-9                                                                                     |  |

| 016              |   |           |    | 38   | Doc    | Page C-5                                                                                     |  |

| 017              |   |           |    | 38   | Doc    | Page C-16                                                                                    |  |

| 018              |   |           |    | 38   | Doc    | Page C-33                                                                                    |  |

| 019              |   |           |    | 38   | Doc    | Page C-37                                                                                    |  |

| 020              |   |           |    | 38   | Doc    | Page C-45                                                                                    |  |

| 021              |   |           |    | 38   | Doc    | Page C-51                                                                                    |  |

| 022              |   |           |    | 38   |        | Specification changes in Table 14-12.                                                        |  |

272834-004 May, 1997 7 of 51

### **Documentation Changes** (1 of 2)

| Number | Document Revision | Page | Status | Documentation Changes |

|--------|-------------------|------|--------|-----------------------|

| 001    | 272338-001        | 40   | Doc    | Page 4-1              |

| 002    | 272338-001        | 40   | Doc    | Page 4-2              |

| 003    | 272338-001        | 40   | Doc    | Page 4-4              |

| 004    | 272338-001        | 40   | Doc    | Page 4-9              |

| 005    | 272338-001        | 40   | Doc    | Page 5-4              |

| 006    | 272338-001        | 41   | Doc    | Page 5-6              |

| 007    | 272338-001        | 41   | Doc    | Page 5-7              |

| 800    | 272338-001        | 41   | Doc    | Page 5-7              |

| 009    | 272338-001        | 41   | Doc    | Page 5-8              |

| 010    | 272338-001        | 42   | Doc    | Page 5-9              |

| 011    | 272338-001        | 42   | Doc    | Page 5-16             |

| 012    | 272338-001        | 42   | Doc    | Page 5-16             |

| 013    | 272338-001        | 42   | Doc    | Page 5-18             |

| 014    | 272338-001        | 42   | Doc    | Page 5-19             |

| 015    | 272338-001        | 43   | Doc    | Page 5-25             |

| 016    | 272338-001        | 43   | Doc    | Page 5-26             |

| 017    | 272338-001        | 43   | Doc    | Page 6-10             |

| 018    | 272338-001        | 43   | Doc    | Page 7-1              |

| 019    | 272338-001        | 43   | Doc    | Page 7-8              |

| 020    | 272338-001        | 44   | Doc    | Page 7-9              |

| 021    | 272338-001        | 44   | Doc    | Page 8-11             |

| 022    | 272338-001        | 44   | Doc    | Page 9-2              |

| 023    | 272338-001        | 44   | Doc    | Page 10-2             |

| 024    | 272338-001        | 45   | Doc    | Page 11-1             |

| 025    | 272338-001        | 45   | Doc    | Page 11-2             |

| 026    | 272338-001        | 45   | Doc    | Page 11-3             |

| 027    | 272338-001        | 46   | Doc    | Page 11-6             |

| 028    | 272338-001        | 47   | Doc    | Page 11-8             |

| 029    | 272338-001        | 48   | Doc    | Page 12-2             |

| 030    | 272338-001        | 48   | Doc    | Page 12-7             |

| 031    | 272338-001        | 48   | Doc    | Page 13-2             |

| 032    | 272338-001        | 48   | Doc    | Page 13-9             |

| 033    | 272338-001        | 48   | Doc    | Page 14-9             |

| 034    | 272338-001        | 48   | Doc    | Page 14-11            |

| 035    | 272338-001        | 48   | Doc    | Page 14-12            |

| 036    | 272338-001        | 48   | Doc    | Page 14-15            |

| 037    | 272338-001        | 49   | Doc    | Page 14-19            |

### **Documentation Changes** (2 of 2)

| Number | <b>Document Revision</b> | Page | Status | Documentation Changes         |

|--------|--------------------------|------|--------|-------------------------------|

| 038    | 272338-001               | 49   | Doc    | Page 14-29                    |

| 039    | 272338-001               | 49   | Doc    | Page A-23                     |

| 040    | 272338-001               | 49   | Doc    | Page A-28                     |

| 041    | 272338-001               | 49   | Doc    | Page A-35                     |

| 042    | 272338-001               | 49   | Doc    | Page A-36                     |

| 043    | 272338-001               | 49   | Doc    | Page A-37                     |

| 044    | 272338-001               | 49   | Doc    | Page A-38                     |

| 045    | 272338-001               | 50   | Doc    | Page A-39                     |

| 046    | 272338-001               | 50   | Doc    | Page A-45                     |

| 047    | 272338-001               | 50   | Doc    | Page B-6                      |

| 048    | 272338-001               | 50   | Doc    | Page C-14                     |

| 049    | 272338-001               | 50   | Doc    | Page C-45                     |

| 050    | 272338-001               | 50   | Doc    | Page C-55                     |

| 051    | 272338-001               | 51   | Doc    | Page C-56                     |

| 052    | 272338-001               | 51   | Doc    | Page C-57                     |

| 053    | 272338-001               | 51   | Doc    | Page C-65                     |

| 054    | 272834-004               | 51   |        | Subtitle change on page 8-23. |

272834-004 May, 1997 9 of 51

### **IDENTIFICATION INFORMATION**

### Markings

| Product                | Stepping | Marking (FPO Number Suffix)       |

|------------------------|----------|-----------------------------------|

| 8EC196KC - P629.5, F6  | Α        | none                              |

| 8EC196KC - P629.5, F6  | В        | A                                 |

| 8EC196KC - P629.5, F6  | B-2      | В                                 |

| 87C196KC - P629.5, F6  | Α        | A or none                         |

| 87C196KC - P629.5, F6  | B-1      | В                                 |

| 87C196KC - P629.5, F6  | B-2      | С                                 |

| 87C196KC - P629.5, F6  | B-3      | D                                 |

| 80C196KC - P629.9, F6  | C-3      | G                                 |

| 80C196KC - P629.9, F6  | D-0      | Н                                 |

| 80C196KC - P648.6, F9  | A-1      | J                                 |

| 80C196KC - Alternate   | D-0      | K                                 |

| 83C196KC - P629.9, F6  | D-0      | L                                 |

| 87C196KC - P629.5, F6  | D-1      | M                                 |

| 83C196KC - P648.6, F9  | В        | N                                 |

| 83C196KC - Alternate   | D-1      | Q                                 |

| 83C196KC - P648.6, F9  | В        | R (Has all fixes of 83C196KC B)   |

| 83C196KC - P648.18, F8 | С        | T (Has all fixes of 83C196KC B)   |

| 80C196KC - P648.6, F8  | A-1      | U (Has all fixes of 83C196KC B)   |

| 83C196KC - P629.9s, F6 | E-0      | U (Has all fixes of 83C196KC D-0) |

| 87C196KC - P629.8s, F6 | E-0      | U                                 |

| 80C196KC - P648.39, F8 | Е        | W (Has all fixes of 83C196KC B)   |

| 83C196KC - P648.39, F8 | F        | none                              |

# intها

#### **8XC196KC SPECIFICATION UPDATE**

#### FRRATA

#### 9600001. A/D Cancel Error

**PROBLEM:** If a new A/D conversion is started before the previous conversion is complete, the results may be incorrect.

**IMPLICATION:** All customers using the A/D are affected. Additional software overhead required. Could delay conversion start time.

**WORKAROUND:** Never start a new conversion until the previous one is finished. This can be accomplished by polling the A/D Done bit or with an interrupt.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600002. Divide Error With Hold# or Ready

**PROBLEM:** Result of a signed divide may be off by one if executed while device is held off the bus by HOLD# or READY and the queue is empty. Specific timings of HOLD# or READY going active and inactive must also be met. There are no generic symptoms. The effect will vary depending on how the divide results are used.

**IMPLICATION:** Customer using HOLD# or READY and a signed divide instruction will be affected. The customer impact varies according to each application.

**WORKAROUND:** The problem occurs only in a one-state-time window when DIV or DIVB is the last instruction in the prefetch queue while HOLD# or READY is active.

If HOLD# and READY are not used, the result is always correct. In the case of READY, the problem does not occur if READY is programmed to insert 0, 1, 2, or 3 wait states. The error may occur when infinite number of wait states are selected and 14 or more waitstates are asserted.

For the applications that use HOLD# and the divide instruction, a simple workaround is to disable hold before every divide and enable it after the divide is complete. Assuming an application enables HOLD# throughout the entire program, the following piece of code disables hold before a divide instruction and enables hold when the divide instruction finishes executing.

```

HLDEN_BIT EQU 80H

WSR EQU 14H

...

ANDB WSR,#NOT HLDEN_BIT

NOP

```

```

DIV XX, YY, ZZ ; DIVB if byte operation is desired. ORB WSR, \#HLDEN\_BIT

```

The NOP instruction is necessary to give the HLDEN bit time to change.

For applications that use READY, the simplest solution is to avoid infinite wait states.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600003. HSO IOC1 Bits Interchanged

**PROBLEM:** HSO IOC1 register bits 4 and 6 are interchanged. HSO.4/HSI.2 or HSO.5/HSI.3 not enabled when expected.

**IMPLICATION:** Any customer using HSO.4/HSI.2 and HSO.5/HSI.3 will be affected. Software change for customers using HSO.4/HSI.2 or HSO.5/HSI.3.

WORKAROUND: Need to redefine these bits in the assembler source code.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 9600004. Indirect Shift Count Value

**PROBLEM:** The SHRL and SHLL instructions function correctly with count values 0-31, inclusive. However, a shift count value of XX100000b causes 32 shifts, which results in no shift taking place. With all other count values, the upper 3 bits are masked off and the remaining bits specify the number of shifts. Also, a shift count value of XX1XXXXXB causes the overflow flag and the overflow-trap flag to be set.

**IMPLICATION:** Customers using SHRL and SHLL instructions with a count value greater than 31 will be affected.

WORKAROUND: Ensure that the count value never exceeds 31.

**STATUS:** There are no plans to fix this. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600005. NMI During PTS Skips an Address

**PROBLEM:** When NMI interrupts a PTS routine, the first byte of the instruction following completion of the PTS cycle is lost. Incorrect code execution following NMI.

# intها

#### **8XC196KC SPECIFICATION UPDATE**

**IMPLICATION:** Any customer using the PTS and NMI will be affected. NMI cannot be used during a PTS cycle.

**WORKAROUND:** NMI must be disabled using external hardware during any PTS activity. Practically, this means that NMI cannot be used in any designs that uses the PTS.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600006. Port 0 Latched on Wrong Phase

**PROBLEM:** Port 0 is not latched on the correct phase. This causes problems when it is used as a digital input port. Digital data is not read in correctly on port 0.

**IMPLICATION:** Any customer using port 0 for digital input will be affected. Designs may need external synchronization circuitry.

**WORKAROUND:** If data remains stable on the port while CLKOUT is high, the data will be read correctly.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600007. PTS Request During Interrupt Latency

**PROBLEM:** If a request for a PTS cycle occurs during a normal interrupt service latency, the device vectors incorrectly. The device executes the interrupt service routine (ISR) instead of servicing the interrupt by the PTS. The interrupt pending bit may be cleared by the vector to the ISR, but the PTSSEL bit will still be valid. These will vary according to the application but in general the number of PTS cycles that should have occurred didn't. In some applications this manifests itself as:

Too few A/D results stored for A/D scan mode.

Too few bytes/words transferred to or from the peripherals or memory.

Some can be very difficult to identify. Situations will exist where old data from previously completed PTS cycles may mask when short PTS cycles occur.

**IMPLICATION:** Any customer that uses the PTS while other interrupts are enabled will be affected. With the workaround in place, the only effect to the customer will be an occasional increase in the PTS response time. Without the workaround in place, the effect will be dependent on the application.

**WORKAROUND:** For every interrupt source that is serviced by the PTS, the ISR must be modified to examine the PTSSEL bits. If the PTSSEL bit is set, the error has occurred. The code must then set the interrupt pending bit and exit the ISR. Upon exit, the PTS will then handle the interrupts as originally intended. If the PTSSEL bit is not set, then the count must have reached zero and the interrupt should be handled normally.

The following software solves this problem:

```

PTSx ISR:PUSHA

LDB WSR, #01H

;GET HWINDOW1

JBS PTSSEL, PTSx_BIT, PTXx_ABORT

;SEE IF PTSSEL BIT IS SET

;NO, OK TO CONTINUE

PTSx COUNTO:

;PTS COUNT = 0

LDB WSR,R0

;CLEAR WSR (IF NEEDED)

; PLACE NORMAL ISR ROUTINE HERE

; FOR SERVICING PTSCB, ETC

POPA

RET

PTSx_ABORT:

;THIS ROUTINE ENTERED IF PTSSEL BIT WAS SET.

; CODE NEEDS TO FORCE ANOTHER PTS CYCLE BY

;SETTING THE INTERRUPT PENDING BIT CORRESPONDING

;TO THE INTERRUPT THAT GOT US HERE!

ORB INT_PEND, #PTSx_BIT_MASK

;"INT PEND" COULD BE

;INT_PEND1 OR EPA_PEND

POPA

```

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600008. NMI During PTS Latency

**PROBLEM:** If an NMI occurs during the PTS latency, it is possible that the pending NMI bit is cleared while never being serviced or the NMI is serviced and the PTS pending bit is cleared and never serviced. NMI will not be serviced 100% of the time or PTS cycles will be missed.

**IMPLICATION:** Customers who have not tied NMI low and who are using the PTS will be affected. NMI cannot be used while the PTS is active.

# intها,

#### **8XC196KC SPECIFICATION UPDATE**

**WORKAROUND:** Force NMI low whenever the PTS is enabled.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 9600009. SIO RI Flag

**PROBLEM:** This problem occurs only in mode 0 if the value is greater than 8006H (slower baud rate). After receiving the first byte of data, the RI will not be generated again. The effect is that only one byte of data will be received and then the logic will hang up.

**IMPLICATION:** All customers using the SIO in synchronous mode (mode 0) and with a BAUD\_RATE value greater than 8006H will be affected. Additional code is required in the SIO interrupt service routine.

**WORKAROUND:** Reinitialize the baud rate register after reading the character in SBUF. This is done by writing two bytes to BAUD\_RATE (0EH, Hwindow 0). This action will reset the mode 0 SIO logic.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 9600010. TIJMP INDEX MASK Value Limitation

**PROBLEM:** If the value of the INDEX\_MASK in the TIJMP instruction is greater than 7FH, the table address will be incorrectly calculated. Incorrect operation of the TIJMP instruction.

**IMPLICATION:** Any customer who uses the TIJMP instruction will be affected. Code may have to be modified to ensure that INDEX\_MASK is 7FH or less.

WORKAROUND: Change INDEX\_MASK value to be 7FH or less.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600011. Write Cycle During Reset

**PROBLEM:** The data bus floats asynchronously with RESET#. If reset occurs during an external write cycle, the contents of the external device may be corrupted. This is the normal operating condition for reset, and is not considered a bug. It is included on this list for those customers who may encounter corruption of data in external RAM during reset.

**IMPLICATION:** Anyone who resets a system while writing to external RAM will be affected. May have to add external circuitry if this is a problem.

**WORKAROUND:** Allow reset to occur only at the rising edge of CLKOUT and only if WR# is high. If a reset occurs during an external bus write cycle, RAM data on the external bus may be corrupted. This describes a logic design that will alleviate the problem.

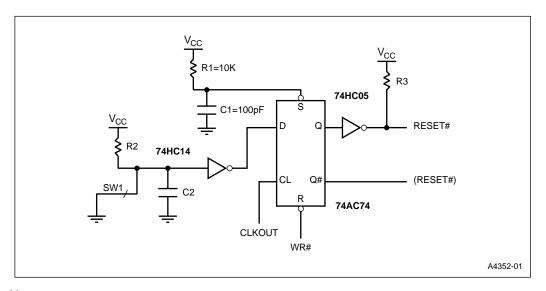

The following circuit will allow a manual reset to occur at the rising edge of CLKOUT only if WR# is high (inactive). If WR# is low (active) then RESET# will stay high (inactive). The 74HC14 and 74HC05 are usually already in the system, so the only additional components are the 74AC74, R1, and C1.

#### Notes:

- 1. R1 = 10K ohms and C1 = 100 pF.

- 2. R2 and C2 should allow for reset state times plus write wait states.

If software resets can occur, use RESET#. If no software resets will occur, eliminate the 74HC05 and use (RESET#).

The R1\*C1 time constant is one microsecond to ensure that the flip-flop comes up 'on' after a power-up. The reset flip-flop at the rising edge of CLKOUT after the R2\*C2 time constant has expired.

# intها

#### **8XC196KC SPECIFICATION UPDATE**

For manual resets, the flip-flop will turn on at the next rising edge of CLKOUT unless WR# is low. If WR# is low, the flip-flop turn on will be delayed until the next rising edge of CLKOUT when WR# is not low. This may occur after any number of wait states. The R2\*C2 time constant must be long enough for the normal reset state times plus the maximum number of write wait states.

**STATUS:** There are no plans to fix this. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600012. Serial Port Framing Error

**PROBLEM:** The stop bit in a normal receive frame is a '1'. If a '0' is received instead of an expected stop bit, the serial port should recognize the '0' as a framing error and set the framing error flag.

An error occurs when the last data bit preceding a stop bit is a '1' and the RXD line glitches low, causing an erroneous '0' stop bit. When this occurs, the receiver interprets the erroneous '0' stop bit as the first data bit for the next frame, corrupting the next frame.

**IMPLICATION:** Any customer using the serial port will be affected.

#### WORKAROUND:

- 1. Use 8-bit mode with parity disabled and use the 7-bit ASCII character set.

- 2. Use 9-bit mode and set the 9th data bit to '0'.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600013. Glitch on Quasi-bidirectional (QBD) Port Pins During Power Up

**PROBLEM:** There is a strong negative glitch on all QBD port pins (P1.x, P2.6, P2.7) on the first falling CLKOUT edge following powerup. This glitch lasts about 5 ns, and only occurs one time following initial application of  $V_{CC}$ . Although the glitch is short, the time for the pin to return to  $V_{CC}$  may be several microseconds, depending on the pin loading capacitance. External devices connected to QBD pins may react to this glitch during power up. Exact symptoms will vary, depending on the design.

**IMPLICATION:** All customers who are using QBD port pins will be affected. External hardware design may have to be altered to allow for this glitch.

**WORKAROUND:** External systems and devices should be disabled from responding to this glitch until after the first CLKOUT falling edge has occurred. One way to do this is to hold the system in reset until the oscillator has stabilized. The length of the glitch can be

controlled by a pullup to  $V_{CC}$ , but stay within the  $V_{OL}$  and  $I_{OL}$  total (port) current limit specifications.

**STATUS:** Fixed. Refer to Summary Table of Changes to determine affected stepping(s).

#### 9600014. A/D Linearity

**PROBLEM:** A/D linearity and absolute error are unacceptably large (±8 LSB in 10-bit mode). Incorrect A/D conversion results.

**IMPLICATION:** Anyone using the A/D converter will be affected. May require special circuitry to maintain  $V_{RFF}$  within  $\pm$  0.25 volts of  $V_{CC}$ . May require more stable  $V_{CC}$  supply.

**WORKAROUND:** If  $V_{REF}$  is held within  $\pm$  0.25 volts of  $V_{CC}$ , absolute error is improved to  $\pm$  3 LSB in 10-bit mode.

**STATUS:** Fixed. Refer to Summary Table of Changes to determine affected stepping(s).

### 9600015. Analog Input Latch-up

**PROBLEM:** Inputs ACH6 and ACH7 to the A/D converter will latch up. The effects are poor A/D performance, ACH6 and ACH7 inputs latched up, high input current.

**IMPLICATION:** Any customer using the A/D converter will be affected. System design may have to be modified to prevent latch-up on these pins.

**WORKAROUND:** Voltage must not be applied to ACH6 or ACH7 before V<sub>CC</sub> is stable.

**STATUS:** Fixed. Refer to Summary Table of Changes to determine affected stepping(s).

### 9600016. INST Weakly Driven Low During CCB Fetch

**PROBLEM:** The INST pin is weakly driven low during the CCB fetch. The weak pulldown will sink about 100  $\mu$ A and remain at V<sub>CL</sub>. CCB can be loaded from wrong memory bank on systems using INST.

**IMPLICATION:** Any customer using INST will be affected. Applications using INST to separate code and data space may not read in the correct CCB. This will result in unpredictable system operation.

**WORKAROUND:** Customers using the INST pin may have to use a 10K pulldown on INST to ensure that the correct memory bank is selected during CCB fetch.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

# intها

#### **8XC196KC SPECIFICATION UPDATE**

#### 9600017. 2 CCB Fetches

**PROBLEM:** A second CCB fetch is attempted from location 201AH. Device does not operate correctly after reset.

**IMPLICATION:** All customers will be affected. May need to modify locations 201AH and 201BH in source code.

WORKAROUND: Set CCB location 201AH to 0FFH, and set location 201BH to 20H.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600018. 3 Wait States During CCB Fetch

**PROBLEM:** Three wait states are always inserted during the CCB fetch, regardless of READY. The microcontroller should recognize the READY signal and insert 3 wait states only if READY is not asserted. Start of program execution after reset takes slightly longer than expected.

**IMPLICATION:** Customers that reset a running system and require a very quick restart time will be affected. Reset of a running system will take 6 state times longer than if no wait states were inserted.

WORKAROUND: None

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600019. ALE, RD#, WR#, BHE, INST, TXD Pullup Too Weak During Reset

**PROBLEM:** Internal weak pullups on ALE, RD#, WR#, BHE, INST, and TXD are not strong enough to guarantee that these pins will be pulled high quickly enough when the device is reset. This may result in the microcontroller entering a test mode following reset.

**IMPLICATION:** All customers will be affected. Possible changes to reset circuitry, or external pullup resistors needed in system.

#### WORKAROUND:

If the external RESET# is held low for several microseconds, this should allow enough time for these pins to pull high (this will depend on the pin loading capacitance).

2. For internal resets (initiated by RST instruction or watchdog timer overflow), or if workaround #1 is not feasible, external 100K pull-up resistors on the ALE, RD#, and WR# pins will correct the problem.

**STATUS:** Fixed. Refer to Summary Table of Changes to determine affected stepping(s).

### 9600020. Buswidth Is Permanently 16 Bits

**PROBLEM:** The buswidth is fixed permanently at 16 bits. Since the bus is in 16-bit mode, port 4 floats after the address has been output. Depending on the port 4 bus loading and the memory type, the CCB data may be read back from the wrong (floating) address. This is not a problem with a 16-bit bus, as all 16 bits are latched. Microcontroller will not operate with 8-bit bus.

**IMPLICATION:** Customers that use an external 8-bit bus will be affected. 8-bit designs will need an additional address latch.

**WORKAROUND:** System must latch all 16 address lines, even if an 8-bit external bus is being used.

STATUS: Fixed. Refer to Summary Table of Changes to determine affected stepping(s).

### 9600021. Glitch on V<sub>CC</sub> Will Cause Device Reset

**PROBLEM:** A glitch on  $V_{CC}$  will cause the device to undergo a complete internal reset. Device resets when not expected.

**IMPLICATION:** All customers will be affected, particularly in electrically noisy environments. Must pay attention to  $V_{CC}$  supply noise and/or circuitry.

WORKAROUND: Keep V<sub>CC</sub> supply as clean as possible.

**STATUS:** Fixed. Refer to Summary Table of Changes to determine affected stepping(s).

### 9600022. Incomplete Reset At > 12MHz

**PROBLEM:** RESET# is active internally for only 4 state times, which is not long enough to completely reset the device at high frequencies. Unpredictable operation after reset.

**IMPLICATION:** All customers who use a clock frequency greater than 12 MHz will be affected. Possible changes to external reset circuitry.

**WORKAROUND:** Hold RESET# low for 16 state times minimum. No workaround for internally generated resets (resets initiated by the RST instruction or a watchdog timer overflow).

# intها

#### **8XC196KC SPECIFICATION UPDATE**

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 9600023. Default Buswidth Out of Reset is 16 Bits

**PROBLEM:** The default buswidth is 16 bits during the CCB fetch and during the first instruction fetch at location 2080H. After that time, the buswidth is determined by CCB.1 and/or the BUSWIDTH pin. Incorrect code execution out of reset on 8-bit bus systems.

**IMPLICATION:** All customers using an emulator or an external 8-bit bus. 8-bit designs will need an additional address latch.

**WORKAROUND:** System must latch all 16 address lines even if an 8-bit external bus is being used. Additionally, if locations 2080H and 2081H are in 8-bit memory, they must contain NOPs.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600024. ONCE Mode Entry

**PROBLEM:** In order to enter the ONCE mode, it is necessary to pull the TXD pin 0.5V below  $V_{SS}$ . Otherwise, the microcontroller will not enter ONCE mode.

**IMPLICATION:** Anyone using ONCE mode will be affected. Modification of test equipment required.

**WORKAROUND:** Test equipment must be modified to pull TXD to  $V_{SS}$  -0.5V.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600025. Oscillator Noise Sensitivity

**PROBLEM:** The oscillator may enter a mode in which the peak-to-peak voltage may not be great enough to consistently trigger the internal clock circuits. This gets worse with ceramic resonators, high temperature, socketed parts, or boards without ground planes.

Under noisy conditions, microcontrollers with the problem may assume any one of three states:

- 1. Normal code execution (oscillator normal)

- CLKOUT is a square wave at oscillator frequency/2

- 2. Failure to execute code (oscillator stopped)

- CLKOUT is stopped, either high or low

- 3. Slow and erratic code execution (oscillator erratic)

- CLKOUT has missing pulses and changing frequency

The oscillator can change from one state to another if there is an appreciable change in the noise level between  $V_{SS}$  (core ground) and  $V_{SS1}$  (port ground). This could occur at device reset, when changing multiple port lines simultaneously, or when switching relays or other high current devices.

More than 1.2 volts of peak-to-peak noise between internal  $V_{SS}$  and  $V_{SS1}$  may cause the oscillator to enter state 2 or state 3. A clean design with good decoupling minimizes the voltage difference between  $V_{SS}$  and  $V_{SS1}$ . Noise can be caused by both internal device switching and external circuitry.

Difficulties are most likely to occur with poor layouts, socketed CPUs, two-layer boards, high voltages, or very high temperatures. The noise sensitivity also varies over frequency and from one manufacturing lot to another. Device-to-device noise sensitivity varies by less than 0.2 volts, so the noise level, not the device, is the major factor.

**IMPLICATION:** Several customers have reported noise sensitivity when using the on-chip oscillator of the 80C196KC. Only devices with either no suffix after the topside tracking number or a "B" suffix are involved. Designs using an external oscillator are not affected. The B-3 stepping with a "C" suffix fixes the problem. All customers who use a crystal or ceramic resonator and do not follow the recommendations will be affected. Customers using an external oscillator will not be affected.

**WORKAROUND:** Designs using the on-chip oscillator are noise sensitive. The following suggestions will reduce the noise level and decrease the noise sensitivity:

- 1. Use a crystal instead of a ceramic resonator.

- 2. Use a multi-layer board with dedicated power planes.

- 3. Solder the 80C196KC directly to the PC board; do not use a socket.

- 4. Locate the crystal as close to the device as possible and keep the XTAL board traces less than 1 cm each.

- 5. Tie  $V_{SS}$  and  $V_{SS1}$  together through the lowest possible impedance path.

- 6. Decouple each  $V_{SS}$  and  $V_{SS1}$  pin to  $V_{CC}$ .

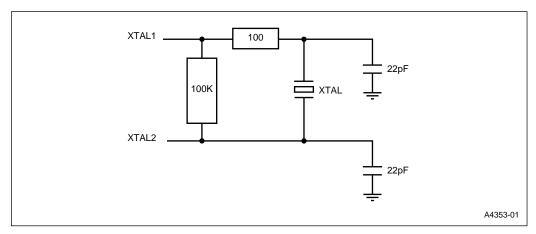

- 7. Place a 100 K resistor between XTAL1 and XTAL2. (See Figure 1.)

- 8. Place a 100 K resistor in series between XTAL1 and the crystal. (See Figure 1.)

- 9. Thoroughly test each system over its operating range.

- 10. Use an external oscillator if possible.

Some or all of these suggestions should allow the oscillator to function properly in a system. We have had no reported failures over commercial temperatures (0° to 70°C) in designs using suggestions 1 through 6.

Figure 1. Options for Decreasing Noise Sensitivity

#### TECHNICAL DESCRIPTION

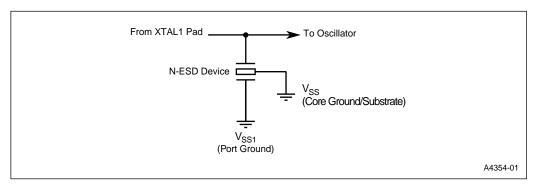

Every pin on the device has ESD (electrostatic discharge) protection designed into the chip. Figure 2 shows the standard cell for negative transient protection:

272834-004 May, 1997 23 of 51

Figure 2. Internal ESD Protection

There are two grounds within the chip, core  $V_{SS}$  and port  $V_{SS1}$ . They are not tied together in the chip in order to isolate the core  $V_{SS}$  from noise on port  $V_{SS1}$ . Normally, noise on  $V_{SS}$  and  $V_{SS1}$  is decoupled externally by filter capacitors and a ground plane. If the grounding and decoupling are not sufficient, a voltage difference can occur between  $V_{SS}$  and  $V_{SS1}$ . From Figure 2, one can see that when  $V_{SS1}$  is around 0.6 volts negative with respect to  $V_{SS}$ , the protection device can start to turn on. The resulting current is well below the leakage specs for the I/O pins and has negligible effect except on the extremely high impedance XTAL1 input.

This minute leakage may cause the DC bias level on XTAL1 to decrease, resulting in reduced gain in the oscillator stage. The oscillation magnitude decreases from the normal rail-to-rail transitions to the point that it may not trigger the internal clocks. CLKOUT then stops or exhibits missing transitions and a decrease in frequency. The signal at XTAL2 drops to about 1.5 volts peak-to-peak centered around 3.5 volts ( $V_{CC} = 5$  volts). The impedance of the internal 2 M-ohm resistor between XTAL2 and XTAL1 is too large to return the oscillator bias level to the region of maximum gain.

As long as internal  $V_{\rm SS}$  and  $V_{\rm SS1}$  are at the same potential, the oscillator will operate normally. Therefore, noise problems are unlikely to occur in surface-mounted, multi-layer boards at commercial temperatures. Note that the noise level may be greater on the chip than at the pins due to lead-frame and bond wire impedances.

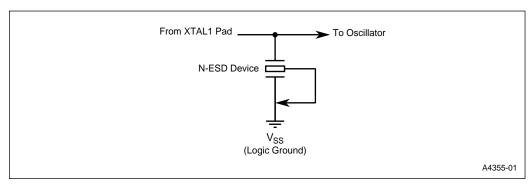

#### INTEL'S ACTION

To eliminate the noise sensitivity, the source of the n-channel ESD device is connected to  $V_{SS}$  instead of  $V_{SS1}$ . The 80C196KC B-3 stepping with a 'C' topside marking implemented

the change in a tape-out in early January, 1991. This is a simple metal mask change that ties both the gate and source of the *n*-channel ESD device to a common, local ground as shown in Figure 3:

Figure 3.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

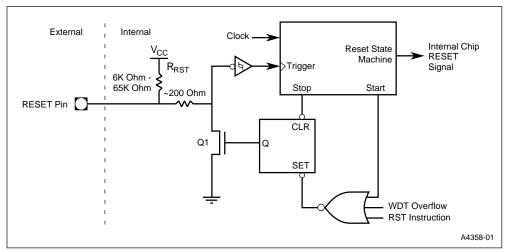

### 9600026. Reset Hysteresis

**PROBLEM:** Reset hysteresis is inadequate and may cause an incomplete reset of the device. The device may not reset correctly, resulting in unpredictable operation.

**IMPLICATION:** All customers will be affected. May need to modify locations 201AH and 201BH in source code.

**WORKAROUND:** An external reset circuit must drive the RESET# pin low for at least 4 state times after the power supply is within tolerance and the oscillator has stabilized. The RESET# signal must have a rise time of less than 50 ns. An open-collector or open-drain driver with a 4.7K pull-up resistor has worked well. Initialize location 201AH to FFH and location 201BH to 20H.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 9600027. Port 0 CMOS Level

**PROBLEM:** When used for digital input, port 0 has CMOS input levels instead of TTL input levels. The device may not recognize a valid TTL "high" input level.

**IMPLICATION:** All customers who use port 0 for digital input will be affected. This erratum does not affect analog operation of port 0. External circuitry may need to be replaced with CMOS output level devices.

**WORKAROUND:** Customers must ensure that external circuitry driving port 0 meets CMOS voltage level requirements as follows:

| Parameter       | Min        | Max             | Units |

|-----------------|------------|-----------------|-------|

| $V_{IL}$        | -0.5 volts | 0.3Vcc          | Volts |

| V <sub>IH</sub> | 0.7Vcc     | Vcc + 0.5 volts | Volts |

The best way to do this is to ensure that any device driving port 0 is a CMOS output level device. Another workaround is to use a pullup resistor on TTL level outputs.

All TTL devices meet the  $V_{II}$  spec, so there is no problem.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600028. Missing External Interrupt Requests (EXTINT, EXTINT1, NMI)

**PROBLEM:** It is possible for the device to fail to recognize an interrupt on EXTINT/P2.2, EXTINT/P0.7, and NMI. The problem is most likely to occur on EXTINT/P0.7 while the device is operating at low voltage (<4.7V), high frequency (16 MHz) and high temperature (>85°C). There is a window of about 2 ns near the falling edge of CLKOUT during which these interrupts may be missed.

**IMPLICATION:** Systems using NMI, EXTINT/P2.2, or EXTINT/P0.7 may experience missed interrupts.

**WORKAROUND:** Latch these signals on the rising edge of CLKOUT using external hardware.

Design Fixes: On the D step of the 8XC196KC products, different fixes were implemented in different devices. The following is a history of the fixes implemented.

80C196KC - P629.9 No fix.

83C196KC - P629.9 Buffer Driver Size Increased.

87C196KC - P629.5 Buffer Driver Size Increased and Latch Added.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

# intها

#### **8XC196KC SPECIFICATION UPDATE**

#### 9600029. BMOVI Windowing Count Register

**PROBLEM:** When using the BMOVI instruction, the count register (or second operand) cannot be windowed. Therefore, the count register must be located in lower RAM address space (1A-FFh). If the count register of the BMOVI instruction is located in the upper register space (100h or above) and an interrupt occurs during the BMOVI instruction execution, the count register will not be updated at the interrupt. The actual number of words moved will be equal to the number of words moved before the interrupt occurred plus the total number of words. The count register is not updated upon the interrupt so it still contains the total number of words after the interrupt completes.

**IMPLICATION:** Customer must verify that the count register for the BMOVI instruction is located in lower address space (1A-FFh).

WORKAROUND: None.

**STATUS:** There are no plans to fix this. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600030. HSI Events (9 or more)

**PROBLEM:** The HSI FIFO can hold seven events/times, and the holding register can hold an additional event/time, for a total of eight events/times. Reading the HSI\_STATUS and HSI\_TIME registers unloads the holding register, allowing the next event/time to move from the FIFO into the holding register.

An error occurs if a ninth event occurs while the FIFO and holding register are full. This ninth event sets an internal HSI event latch. When software unloads the first event from the holding register (by reading HSI\_STATUS and HSI\_TIME), the second event moves into the holding register and the remaining events (events 3 – 8) move down one position in the FIFO, leaving a vacancy in the FIFO. Because the internal HSI event latch is set, the ninth event moves into the FIFO. However, the ninth event has no time tag associated with it. A time tag is created at the time the event moves into the FIFO, and the FIFO\_FULL and HSI\_RDY bits of the IOS1 register reflect the event, so it **appears** that a valid ninth event occurred.

The FIFO\_FULL bit, when set, indicates that the FIFO contains six or more events. The HSI\_RDY bit, when set, indicates that the holding register contains one event. The

following table summarizes the status of the FIFO\_FULL and HSI\_RDY bits after a series of eight events and after a series of nine events:

| Event from FIFO | FIFO_FULL |          | HSI_RDY  |          |

|-----------------|-----------|----------|----------|----------|

|                 | 9 events  | 8 events | 9 events | 8 events |

| 1               | 1         | 1        | 1        | 1        |

| 2               | 1         | 1        | 1        | 1        |

| 3               | 1         | 0        | 1        | 1        |

| 4               | 0         | 0        | 1        | 1        |

| 5               | 0         | 0        | 1        | 1        |

| 6               | 0         | 0        | 1        | 1        |

| 7               | 0         | 0        | 1        | 1        |

| 8               | 0         | 0        | 1        | 1        |

| 9               | 0         | 0        | 1        | 0        |

In summary, the HSI can correctly record only eight events. However, if a ninth event occurs while the FIFO and holding register are both full, the HSI module and the related status bits (FIFO FULL and HSI RDY) behave as though nine events were recorded.

**IMPLICATION:** Any customer using the HSI unit will be affected. Applications should be analyzed to ensure that nine events cannot occur before at least one event is unloaded from the holding register.

**WORKAROUND:** Analyze the application to ensure that nine events cannot occur before at least one event is unloaded from the holding register. The HSI unit can record an event every 9 state times. The maximum interrupt latency is 56 state times for standard interrupts and 43 state times for PTS interrupts. Using this data, determine how frequently events can occur, which interrupt should be used (HSI FIFO Full, HSI FIFO Fourth Entry, or HSI Data Available), and whether to use a standard interrupt service routine or the PTS to service that interrupt.

The following code can be used to ensure that the FIFO is empty before setting up for an HSI event:

# intطا

#### **8XC196KC SPECIFICATION UPDATE**

**STATUS:** There are no plans to fix this. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 9600031. SIO Mode 0 Maximum Baud Rate

**PROBLEM:** In synchronous mode 0, the minimum baud value is 0001H for transmissions and 0002H for receptions.

In asynchronous modes 1, 2, and 3, the minimum baud value is 0000H when using the internal clock signal and 0001H when using an external clock signal on T2CLK. At 16 MHz, the maximum baud rate is 2.76 Mbaud for mode 0 and 1.0 Mbaud for modes 1, 2, and 3.

Bits 14:0 of the BAUD\_RATE register specify the baud value. (Bit 15 selects either the internal clock signal or an external clock signal on T2CLK.) Using a value less than the minimums listed above results in incorrect data. For mode 0 receptions, whatever data is present on the RXD pin when TXD begins clocking is treated as the least-significant bit, each remaining bit is shifted left by one bit, and the most-significant bit from the transmitter is never shifted in.

**IMPLICATION:** Any customer who uses synchronous mode 0 will be affected. Use a baud value that is equal to or greater than the minimum value listed above. This will result in slower baud rates, but should result in correct data.

**WORKAROUND:** None. Use a baud value that is equal to or greater than the minimum value:

- for synchronous mode 0, 0002H for receptions or 0001H for transmissions

- for asynchronous modes 1, 2, and 3, 0001H when using an external clock source or 0000H when using the internal clock signal

**STATUS:** There are no plans to fix this. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600032. Writing HSI MODE Resets Divide-by-Eight Counter

**PROBLEM:** Writing to the HSI\_MODE register always resets the HSI module's divide-by-eight counter. If you write HSI\_MODE to configure an HSI, and another HSI was previously configured for "eight positive transitions" mode, the counter reset causes the previously configured HSI to lose up to seven accumulated events.

**IMPLICATION:** Applications that write to HSI\_MODE after an HSI is configured for "eight positive transitions" mode will be affected.

272834-004 May, 1997 29 of 51

**WORKAROUND:** There are three possible workarounds:

- If any HSI is to be used in "eight positive transitions" mode, use a single write to HSI\_MODE to configure all HSI inputs at once.

- Disable the HSI input by clearing the associated bit(s) in the IOC0 register, poll the HSI\_STATUS register until seven counts have occurred, then enable the HSI to load the FIFO on the eighth transition.

- Configure the HSI for "every transition" mode, and use an external counter to pass through the eight transition.

**STATUS:** There are no plans to fix this. Refer to Summary Table of Changes to determine the affected stepping(s).

### 9600033. IPD Hump

**PROBLEM:** Due to a floating node on the clockout disable circuit, an IPD hump of up to 700  $\mu$ A can be seen. The IPD hump occurs approximately 0.5 seconds to 4 minutes after the device has entered powerdown mode. The hump is a leakage current of up to 700  $\mu$ A that is present for a period of one second to several minutes in length, depending on the temperature. After the hump has occurred, the device returns to and remains at the normal level of powerdown current.

**IMPLICATION:** If the clockout disable bit (IOC3.1) is cleared, then the IPD hump is not seen. If the clockout disable bit is set and powerdown mode is entered, then the IPD hump may occur.

**WORKAROUND:** To avoid this problem, enable CLKOUT (clear IOC3.1) before executing the IDLPD instruction. If noise from CLKOUT is an issue in your system, disable CLKOUT (set IOC3.1) upon return from powerdown.

**STATUS:** This has been fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### **SPECIFICATION CHANGES**

None for this revision of this specification update.

### SPECIFICATION CLARIFICATIONS

### 001. Page 5-10

**PROBLEM:** In section 5.4.3 about NMI, a clarification is necessary regarding the last sentence in this paragraph. It should read as follows for better understanding.

'If your system does not use the NMI interrupt, **connect the NMI pin to V\_{SS}** to prevent spurious interrupts.'

### 002. Page 8-4

**PROBLEM:** Confusion has arisen regarding the fourth paragraph of Section 8.1.3.1. The following paragraph clarifies this text:

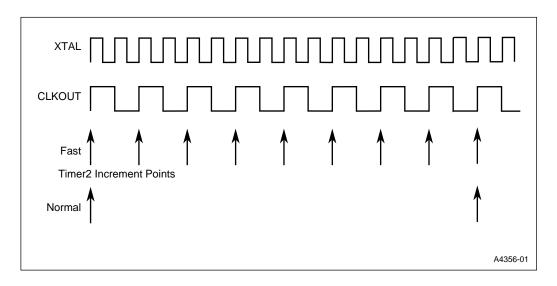

When FAST\_T2\_ENA is set (fast increment mode), Timer 2 increments once every state time, at the rate of Fosc/4. When FAST\_T2\_ENA is cleared (normal increment mode), Timer 2 increments once every eight state times, at the rate of Fosc/32. See the timing diagram below for a depiction of the input clock signal, the CLKOUT signal, and the points at which Timer 2 increments in the fast and normal modes.

### 003. Page 8-18

**PROBLEM:** It is explained in the second paragraph that external events generate the High-Speed Output interrupt (INT03) and internal events generate the Software Timer interrupt (INT05). An external event is defined as a toggle of one or more of the HSO outputs. An internal event is defined as the other HSO triggered events (see User's Manual). This explanation does not cover the HSO\_ALL event interrupt. By these definitions, the HSO\_ALL event would generate the High-Speed Output interrupt. Actually, the HSO\_ALL event (Command Tag = 0Ch) generates the Software Timer interrupt. Therefore, in the Software Timer interrupt service routine it may be necessary to see whether the HSO\_ALL event or one of the internal events (Reset Timer, Start A/D, Software Timers) caused this interrupt. The HSO event bits in the IOS2 register are set when the HSO\_ALL event occurs. Therefore, it will be easy to check if an HSO\_ALL event caused the Software Timer interrupt. This is true for the PTS vectors as well. When an HSO\_ALL event occurs, the Software Timer PTS vector location determines the PTS control block that is used.

### 004. Page 9-3

**PROBLEM:** In Table 9-1 the description for the INT\_PEND register requires some clarification. The second sentence should read, 'Bit 1 is cleared when the interrupt takes the vector located at 2002h.'

### 005. Page 10-2

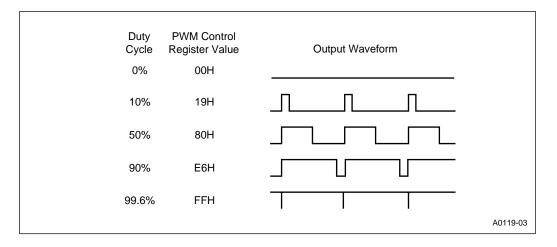

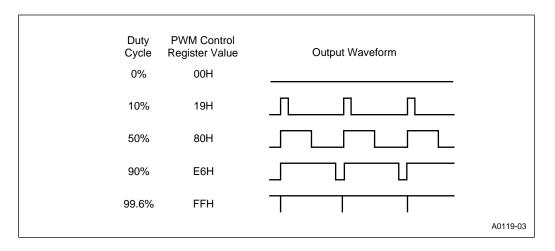

**PROBLEM:** Add the following sentences to the second paragraph after the first sentence: 'Since the value written to the control register is buffered, you can write a new 8-bit value to PWMx\_CONTROL before the counter overflows. The new value is used during the next period of PWMx.'

The following figure replaces Figure 10-2.

## 006. Page 11-3

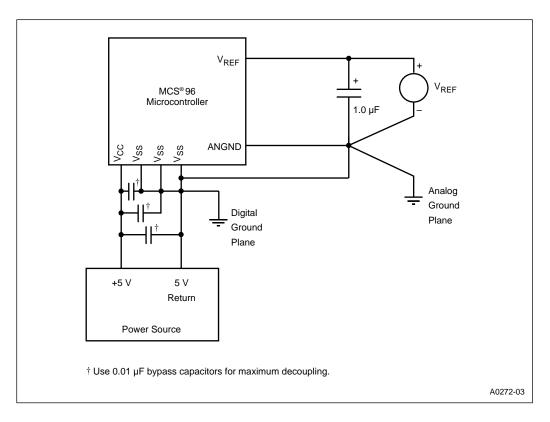

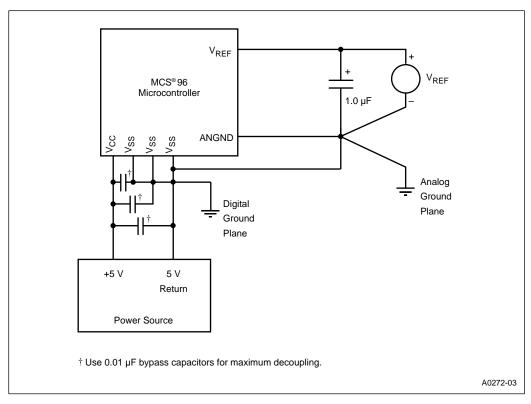

**PROBLEM:** In Figure 11-2, the recommended capacitor value between  $V_{CC}$  and  $V_{SS}$  is 0.01  $\mu F$  or greater. Also the recommended capacitor value between  $V_{REF}$  and ANGND is 1.0  $\mu F$ .

Section 11.2.1 explains the reason for these capacitors. However, the second to last line of the first paragraph should read as follows: 'Connect a 0.01- $\mu$ F bypass capacitor between  $V_{CC}$  and each  $V_{SS}$  pin and a 1.0- $\mu$ F capacitor between  $V_{REF}$  and ANGND.'

272834-004 May, 1997 33 of 51

## 007. Page 12-1

**PROBLEM:** In Section 12.1, the second sentence of the first paragraph should read as follows, 'The CPU stops executing instructions, but the special function registers (SFRs) and register RAM retain their data, and the peripherals and interrupt system continue functioning.'

## 008. Page 13-4

**PROBLEM:** In Section 13.3, the first paragraph does not clearly explain the point made in the last two sentences. 'Some performance degradation can be expected comparing the 16-bit to 8-bit bus systems. A word fetch in a 16-bit bus system is done with a single word

fetch. However, any word fetches in an 8-bit bus system must be done with two byte fetches.'

# 009. Page 13-22

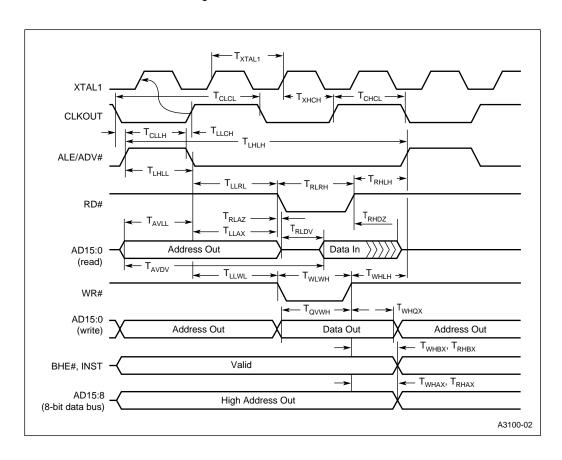

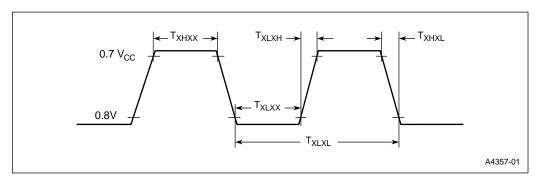

**PROBLEM:** Figure 13-20 displays the system bus timing. However, there are a couple of mistakes. First, the WR# signal shows a range for the transition from high to low. This is incorrect; it should be a single line. Next, the signal labeled BUS should not refer to 16-bit mode only. This BUS signal shows AD0-7 in 8-bit mode and the entire bus (AD0-15) in 16-bit mode. The corrected diagram is as follows:

272834-004 May, 1997 35 of 51

### 010. Page 14-15

**PROBLEM:** The voltage is calculated by using the following formula:

Voltage =

$$\frac{20 \times \text{Test ROM Data}}{256}$$

### 011. Page 14-17

**PROBLEM:** There has been some confusion with Table 14-8. The external EPROM address for the PPW is 2014H/2015H, if the recommended Auto Programming circuit, shown in Figure 14-8, is used. As the text in Section 14.9.1 explains, the circuit in Figure 14-8 replaces previously recommended circuits that did not use P1.0-P1.2 to generate the upper address bits for the external EPROM.

The actual address output on the address/data bus is 4014H/4015H. However, due to remapping, using P1.0-P1.2 for the upper address lines as shown in Figure 14-8, the PPW will be read from 2014H/2015H.

Therefore, since the circuit in Figure 14-8 uses P1.0-P1.2 as the upper address bits for the external EPROM, the PPW should be stored at 2014H/2015H. If the address lines are used to address the external EPROM, then the PPW should be stored at 4014H/4015H.

## 012. Page 14-31

**PROBLEM:** The second sentence should read, 'A zero on P3.0 selects the Dump Word command.'

## 013. Page 14-33

**PROBLEM:** In the second sentence of the first paragraph, reword 'hold EA# high' to 'pull EA# to  $V_{CC}$ '.

## 014. Page B-9

**PROBLEM:** The INST pin has a weak pull-up during reset.

015. Page B-9

PROBLEM: Add a column to Table B-3 titled, Pin Status in ONCE.

| Name        | Status in ONCE |

|-------------|----------------|

| ACH0-ACH7   | float          |

| Port 1      | pull-up        |

| TXD         | float          |

| RXD         | float          |

| EXTINT      | float          |

| T2CLK       | float          |

| T2RST       | float          |

| PWM0        | float          |

| P2.6-P2.7   | pull-up        |

| AD0-AD15    | pull-up        |

| HSI.0,HSI.1 | float          |

| HSI.2/HSO.4 | float          |

| HSI.3/HSO.5 | float          |

| HSO.0-HSO.3 | pull-down      |

| ALE         | float          |

| BHE#        | float          |

| BUSWIDTH    | float          |

| CLKOUT      | float          |

| EA#         | float          |

| INST        | float          |

| NMI         | pull-down      |

| RD#         | float          |

| READY       | float          |

| RESET#      | pull-up        |

| WR#         | float          |

Also add **Note 5**. The output pins are disconnected from internal circuitry in ONCE mode; therefore, the signal floats. The only current present on the pin is device leakage current, which is in the low microamp range.

272834-004 May, 1997 37 of 51

016. Page C-5

PROBLEM: The reset value for T2CAPTURE is 00H. The reset value for SP is XX.

017. Page C-16

**PROBLEM:** The reset state for CCR should be 'XX', since it is defined by application code.

018. Page C-33

**PROBLEM:** The Bit Name for bit 2 should be, 'Enable HSI.1 as HSI input'. The Bit Name for bit 4 should be, 'Enable HSI.2 as HSI input'. The Bit Name for bit 6 should say, 'Enable HSI.3 as HSI input'

019. Page C-37

**PROBLEM:** In the description forbit 4, 1 = KB fast mode and 0 = KB normal mode.

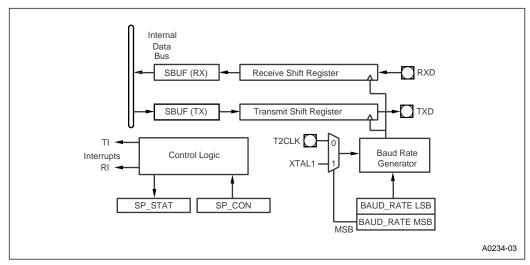

020. Page C-45