## **Electrical Data**

For Electrical Data See Document "Nx586 Electrical Specifications" Order # NxDOC-ES001-01-W

THIS PAGE INTENTIONALLY LEFT BLANK

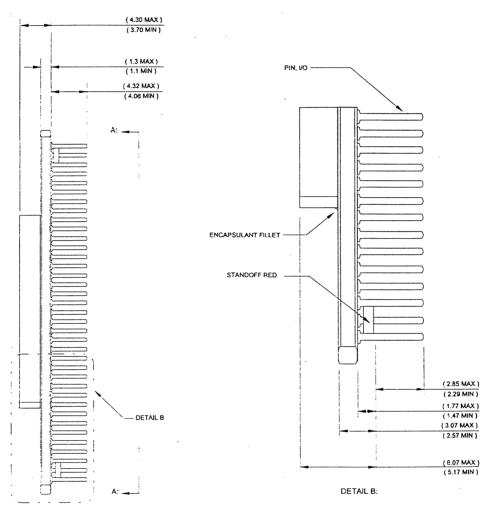

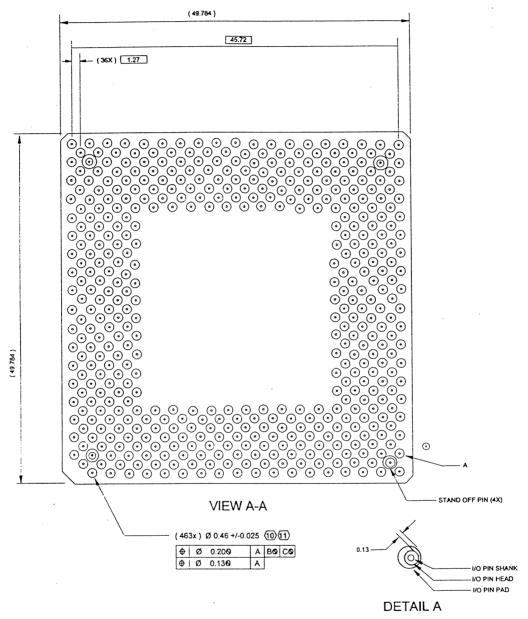

## **Mechanical Data**

Figure 42 Nx586 Package Diagram (top)

Figure 43 Nx586 Package Diagram (side)

Figure 44 Nx586 Package Diagram (bottom)

## Glossary

Access—A bus master is said to "have access to a bus" when it can initiate a bus cycle on that bus. Compare bus ownership.

Adapter—A central processor, memory subsystem, I/O device, or other device that is attached to a slot on the NexBus, VL-Bus, or ISA bus. Also called a *slot*.

Aligned—Data or instructions that have been rotated until the relevant bytes begin in the least-significant byte position.

Allocating Write—A read-to-own (read for exclusive ownership of cacheable data) followed by a write to the cache.

Arbiter—A resource-conflict resolver, such as the NexBus arbiter.

Asserted—For signals, "asserted" means driven to the state which asserts the description of the signal.

Active High—The signal or memory bit drive to its "asserted" state which is logically or physically high. For a memory bit, this would be a "1". For a signal, this would be near VCC voltage level.

Active Low—The signal or memory bit drive to its "asserted" state which is logically or physically low. For a memory bit, this would be a "0". For a signal, this would be near GND voltage level.

b-Bit.

B-Byte.

Bandwidth—The number of bits per second that can be processed by a memory, arithmetic unit, input/output processor, or communication system.

Bank—In a cache, same as set and way. In main memory, a qword-wide group of addressable locations.

Branch Prediction—The use of history, statistical methods, or heuristic rules to predict the outcome of conditional branches.

Buffer—A fraction of real memory or a group of registers that serve as a buffer for data flowing to and from auxiliary memory.

Bus Cycle—A complete transaction between a bus master and a slave. For the Nx586 processor, a bus cycle is typically composed of an address and status phase, a data phase, and any necessary idle phases. Also called a *bus operation*, or simply *operation*.

PRELIMINARY Nx586<sup>™</sup> Processor 79

Bus Operation—Same as bus cycle.

Bus Ownership—A bus is said to be owned by a master when the master can initiate cycles on the bus. The master to which bus ownership is granted controls only its own interface with the arbiter. The arbiter, on behalf of that master, acts as a master on the other buses in the system. It does this so as to support the master in the event that a bus-crossing operation is requested. Compare *access*.

Bus Phase—Part of bus cycle that lasts one or more bus clocks. For example, it may be a transfer of address and status, a transfer of data, or idle clocks.

Bus Sequence—A sequence of bus cycles (or operations) that must occur sequentially due to their being explicitly locked by the continuous assertion of the master's AREQ\* and/or LOCK\* signals, or implicitly locked by the GDCL signal.

Cache Block—A 32-byte unit of data in a cache. The Nx586 processor's caches are organized around such blocks. Each cache block has an associated tag and MESI-protocol state. Cache blocks can be fetched atomically as a contiguous group of 32-bytes or in eight-byte subblock units. Compare cache line

Cache-Block Tag—The high-order address bits of a cache block that identifies the area of memory from which it was copied. During a cache lookup, the high-order address bits of the processor's operand is compared with the tags of all blocks stored in the cache.

Cache Coherence—The protocol among multiprocessors with private caches that assures that each variable in the shared memory space receives writes in a serial order, and no processor sees that sequence of values in any other order.

Cache Hit—An access to a cache block whose state is modified, exclusive, or shared (i.e., not invalid). Compare cache miss.

Cache Line—If a *cache block* can be fetched atomically (rather than in subblock units), the concepts of cache block and cache line are identical. However, in the Nx586 processor, cache blocks are often fetched in eight-byte subblock units, leaving only parts of the cache block valid. Compare *cache block*.

Cache Lookup—Comparison between a processor address and the cache tags and state bits in all four sets (ways) of a cache.

Cache Miss—An access to a cache block whose state is invalid. Compare cache hit.

Caching Master—A bus master that internally caches data originated elsewhere. The caching master must continually monitor the bus to guarantee cache coherency. Masters on buses other than the NexBus can maintain caches, but they must be write-through (not write-back) caches.

Conditional Branch—A computer instruction that alters the sequence of execution if a condition is true, and otherwise falls through to the next instruction in sequence.

Clean—Same as exclusive.

Clock Cycle—Unless otherwise stated, this a *processor-clock cycle* rather than a bus-clock cycle. The Nx586 processor's clock runs at twice the frequency of the NexBus clock (NxCLK). The level-1 cache runs at the same frequency as the processor clock. The level-2 cache runs at the same frequency as the NexBus clock (NxCLK).

Clock Phase—One-half of a processor clock cycle.

Cycle—See bus cycle, clock cycle, bus phase, and clock phase.

D Cache—The level-1 (L1) data cache.

Device—Same as adapter.

Dirty—Same as modified.

Dword—A doubleword. A four-byte (32-bit) unit of data that is addressed on an four-byte boundary. Also called a *dword* (doubleword).

Exclusive—One of the four states that a 32-byte cache block can have in the MESI cache-coherency protocol. *Exclusive* data is owned by a single caching device and is the only known-correct copy of data in the system. Also called *clean* data. When exclusive data is written over, it is called *modified* (or *dirty*) data.

Floating Point Execution Unit—The Floating Point Execution Unit. The logic in the Floating Point Execution unit is integrated into the parallel pipeline of the Nx586 processor.

Flush—(1) To write back a cache block to memory and invalidate the cache location, also called write-back and invalidate, or (2) to invalidate a storage location such as a register without writing the contents to any other location. This is an ambiguous term that is best not used.

Functional Unit—The Decode Unit, Address Unit, Integer Unit, Floating Point Coprocessor, or Cache and Memory Unit.

Group Signal—A NexBus control signal that represents the logical OR of several inputs. These signals typically have signal names that begin with the letter "G".

I Cache—The level-1 (L1) instruction cache.

Invalid—One of the four states that a 32-byte cache block can have in the MESI cache-coherency protocol. *Invalid* data is not correctly associated with the tag for its cache block.

Invalidate—To change the state of a cache block to invalid.

L1 or Level-1—The level-1 or primary cache is located on the Nx586 processor chip.

L2 or Level 2—The level-2 or secondary cache is located in SRAM connected to the processor's SRAM bus and controlled by logic on the Nx586 processor.

Line—See cache block.

Main Memory—See memory.

Master—The Master is a device on the NexBus that initiates a transaction.

Memory—A RAM or ROM subsystem located on any bus, including the *main memory* most directly accessible to a processor. Also called *main memory*.

MESI—The cache-coherency protocol used in the Nx586 processor. In the protocol, cached blocks in the L2 write-back cache can have four states (modified, exclusive, shared, invalid), hence the acronym MESI. See *modified*, *exclusive*, *shared*, and *invalid*.

Modified Write-Once Protocol—The cache-coherency protocol used in the Nx586 processor. See *MESI*.

PRELIMINARY Nx586<sup>™</sup> Processor 81

Modified—One of the four states that a 32-byte cache block can have in the MESI cache-coherency protocol. *Modified* data is *exclusive* data that has been written to after being read from lower-level memory, and is therefore the only valid copy of that data. Also called *dirty or stale*.

MWO—See modified write-once protocol.

NB—Same as NexBus.

Negated— For signals, "negated" means driven to the state which de-asserts the description of the signal. Or the opposite of "asserted".

NexBus—A 64-bit synchronous, multiplexed bus defined by NexGen.

No-Op—A single-qword operation with BE<7:0>\* all negated. No-ops address no bytes and do nothing except consume processor cycles.

Nx586—The Nx586 processor (CPU).

NxVL—A NexBus system controller chip that supports a Nx586 processor, main memory, 82C206 peripheral controller, VL-Bus, and ISA bus.

Octet—A unit of data consisting of eight bytes and addressed on an eight-byte boundary.

Operation—See bus operation.

Owned—A cache block whose state is *exclusive* (owned clean) or *modified* (owned dirty). See also *bus ownership*.

Ownership—See bus ownership.

Peripheral Controller—A chip that supports interrupts, DMA, timer/counters, and a real-time clock.

Phase—See bus phase and clock phase.

PLL—Phase-locked loop.

POST—Power On Self Test. This procedure is performed when power is first applied to check the functionality of the system..

Present—Same as valid.

Processor—Unless otherwise specified, refers to a Nx586 processor.

Processor Clock—The Nx586 processor clock. See *clock cycle*.

Qword—A quadword. A eight-byte unit of data that is addressed on an eight-byte boundary.

Register Renaming—A technique used in processor design that assigns idle registers to serve in the place of program specified registers in order to avoid conflicts that could stall pipeline flow momentarily.

RISC—Reduced Instruction-Set Computer. A computer in which all instructions are simple instructions that take one cycle to execute, except possibly for delays introduced by conditional branches and cache misses.

Scalar Operation—Any operation performed on individual data.

Scalar Processor—A processor whose basic operations manipulate individual data elements rather than vectors or matrices.

Set—In a cache, one of the degrees of associativity. The group of cache blocks in such a set. Same as bank and way.

Shared—One of the four states that a 32-byte cache block can have in the MESI cache-coherency protocol. *Shared* data is valid data that can only be read, not written.

Snoop—To compare an address on a bus with a tag in a cache, so as to detect operations that are inconsistent with cache coherency.

Snoop Hit—A snoop in which the compared data is found to be in a modified state. Compare snoop miss

Snoop Miss—A snoop in which the compared data is not found, or is found to be in a *shared* state. Compare *snoop hit*.

Source—In timing diagrams, the left-hand column of the diagram indicates the "source" of each signal. This is the chip that originated the signal as an output. When signals are driven by multiple sources, all sources are shown, in the order in which they drive the signal. The source of a signal that takes on a different name as it crosses buses through transceivers is shown as the transceivers overwhich the signals cross, subscripted with a symbol indicating the logic that originally output the signals. The source of group-ORed signals (such as GXACK) is likewise subscripted with a symbol indicating the logic that originally output the activating signal (such as XACK\*).

Stale—Same as modified.

System Bus—A bus to which the NexBus interfaces. The system buses include the VL-Bus, PCI-Bus and ISA bus.

System Controller—The device or logic that provides NexBus arbitration and interfacing to main memory and any other buses in the system.

Superscalar—A computer architecture in which multiple scalar instructions are decode in each clock cycle sot that the instruction completed per cycle exceeds 1.0.

T-Byte—An 80-bit floating-point number.

Word—A two-byte (16-bit) unit of data.

Write-Back Cache—A cache in which WRITEs to memory are stored in cache and written to memory only when a rewritten item is removed from cache.

Write-Through Cache—A cache in which WRITEs to memory are recorded concurrently both in cache and in main memory. The result is that the main memory slways contains valid data

PRELIMINARY Nx586™ Processor 83

THIS PAGE INTENTIONALLY LEFT BLANK

## Index

82C206, 59 Access, 83 Active-High Signals, vi Active-Low Signals, v AD, 24 Adapter, 83 ADDRESS, 25 Address and status phase, 24 address and status phase, 24 Address Latch Enable, 19 Address phase, 24, 25, 64, 71 Address Unit, 47 Addressing, vi ALE\*, 4, 19, 74 Aligned, 83 Allocating Write, 83 Alternate bus, 18 Alternate-Bus Request, 17 ANALYZEIN, 33 ANALYZEOUT, 33 Arbiter, 17, 83 Arbitration, 64 Architecture, 41 AREQ\*, 17, 64, 74 asterisk. v B, vi, 83 b. vi. 83 Bank, 83 Basic System Diagram, 42 BE, 25, 26, 71, 72 Binary compatibility, 1 BLKSIZ, 28, 71 Block Size. 28

Buffered Address and Data Bus, 4 Bus, 45 Bus Arbitration, 4 Bus Cycle, 83 Bus Cycle Types, 27 Bus Lock, 18 Bus Operations, 61, 84 Fast NexBus5 Single-Qword Read with a delayed GXACK, 67 Fastest NexBus Single-Qword Read, 65 Fastest NexBus Single-Oword Write, 65 Fastest NexBus5 Single-Qword Read, 67 Fastest NexBus5 Single-Qword Write, 70 Interrupt Acknowledge Cycle, 72 NexBus5 I/O, 71 NexBus5 Intervenor, 74 NexBus5 Single-Oword Read Hits Modified Cache Block, 75 NexBus5 Single-Qword Read with Wait States using a delayed GXACK, 68 NexBus5 Single-Qword Read with Wait States using GXHLD only, 69 NexBus5 Single-Qword Write with Wait States, 70 Bus Ownership, 84 Bus Phase, 84 Bus Sequence, 84 Bus Signals, vi Bus Structure, 41

| Buses Alternate, 18 Cycles, 61 Internal 64-bit Execution Unit Bus, 45 NexBus, 42 NxAD, 4, 24 Operations, 61 Snooping, 54 Structure, 41 Byte Enables, 25 byte-enable bits, 75 | Clock Phase, 84 Clock Phase 1, 30 Clocks, 30, 46 Cycles, 84 Generation, 60 L1-cache, 46 L2-cache, 46 Modes, 60 NexBus, 46 Processor, 46 COEA*, 29 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| CACHBL, 28                                                                                                                                                                   | COEB*, 29                                                                                                                                         |

| Cache, 47                                                                                                                                                                    | Compatibility, 1                                                                                                                                  |

| Cache and Memory Subsystem, 52                                                                                                                                               | CWE, 29                                                                                                                                           |

| Coherency, 53, 54                                                                                                                                                            | Cycle, 85                                                                                                                                         |

| Data, 52                                                                                                                                                                     | Cycle Control, 19                                                                                                                                 |

| Instruction, 52                                                                                                                                                              | D Cache, 52, 85                                                                                                                                   |

| Level-1, 52                                                                                                                                                                  | D/C*, 27                                                                                                                                          |

| Level-2, 29, 45, 52                                                                                                                                                          | Data, vi                                                                                                                                          |

| Level-2 Configuration, 53                                                                                                                                                    | Data or Code*, 27                                                                                                                                 |

| States, 55                                                                                                                                                                   | Data phase, 24, 66, 71                                                                                                                            |

| Cache and Memory Subsystem, 52                                                                                                                                               | DCL*, 21, 57, 59, 74, 75                                                                                                                          |

| Cache and Memory Unit, 47                                                                                                                                                    | Decode Unit, 47                                                                                                                                   |

| Cache Block, 84                                                                                                                                                              | DEVICE, 26                                                                                                                                        |

| Cache Coherency, 53, 54                                                                                                                                                      | Device, 85                                                                                                                                        |

| Cache Control, 21                                                                                                                                                            | Dirty, 85                                                                                                                                         |

| Cache fills, 71                                                                                                                                                              | Dirty Cache Line, 21, 57                                                                                                                          |

| Cache Hit, 84                                                                                                                                                                | DMA, 75                                                                                                                                           |

| Cache Line, 84                                                                                                                                                               | doubleword, vi, 25                                                                                                                                |

| Cache Lookup, 84                                                                                                                                                             | Dword, 85                                                                                                                                         |

| Cache Miss, 84                                                                                                                                                               | dword, vi                                                                                                                                         |

| Cache Hit Pands 51                                                                                                                                                           | Dword Address, 25                                                                                                                                 |

| Cache-Hit Reads, 51                                                                                                                                                          | Electrical Data, 77                                                                                                                               |

| Cacheable, 28, 71 Caching Master, 84                                                                                                                                         | Endian Convention, vi<br>Exclusive, 54, 58, 73, 85                                                                                                |

| CADDR, 29, 61                                                                                                                                                                | External Phase Inputs, 60                                                                                                                         |

| CBANK, 29, 61                                                                                                                                                                | External PLL Mode                                                                                                                                 |

| CDATA, 29, 61                                                                                                                                                                | Clock Input, 30                                                                                                                                   |

| CKMODE, 30, 53, 60                                                                                                                                                           | NxCLK, 30                                                                                                                                         |

| Clean, 84                                                                                                                                                                    | PHE1, 30                                                                                                                                          |

| Clock Cycle, 84                                                                                                                                                              | Skewed NxCLK, 31                                                                                                                                  |

| Clock Input Reference, 31                                                                                                                                                    | XREF, 31                                                                                                                                          |

| Clock Mode, 30                                                                                                                                                               | External Processor Clock, 53, 60                                                                                                                  |

| Clock Mode Select, 31                                                                                                                                                        | Fast NexBus5 Single-Qword Read with a                                                                                                             |

| Clock Output Reference, 31                                                                                                                                                   | delayed GXACK, 67                                                                                                                                 |

I/O operations, 64

87

Fastest NexBus Single-Qword Read, 65 I/O Reads, 51 Fastest NexBus Single-Qword Write, 65 I/O space, 71 Fastest NexBus5 Single-Qword Read, 67 INT instruction, 59 Fastest NexBus5 Single-Qword Write, 70 Integer Unit, 47 Internal 64-bit Execution Unit Bus, 45 Features, 3 Floating Point Execution Unit, 47, 85 Internal Architecture, 47 Floating Point Interrupt Request, 32 Internal PLL Mode Floating-Point Execution Unit, 45 IREF, 31 NxCLK, 30 Flush, 85 Interrupt, 32 Four-Qword Block Read (Cache-Block Fill), 26 Interrupt Acknowledge, 27 Four-Oword Block Write, 26 Functional Unit, 85 Interrupt Acknowledge Cycle, 72 interrupt vector, 71 G, vi GALE, 4, 19, 24, 66, 73, 74 Interrupts, 59 Intervenor operation, 59 Gate Address 20, 32 INTR\*, 4, 18, 32, 59 GATEA20, 4, 18, 32 GBLKNBL, 21, 28, 57, 66, 71 Invalid, 54, 57, 85 Invalidate, 85 GDCL, 21, 57, 74 IPC, 59 Global Reset (Power-Up Reset), 32 IREF, 31 Global Write Enable, 29 GNT\*, 17, 64, 74, 75 **JEDEC** Grant NexBus, 17 Bottom, 16 Pinouts, 11 GREF, 33 Ground Reference, 33 Top, 15 Group Address Latch Enable, 19 k, vi L1,85 Group Block (Burst) Enable, 21 L1-cache clock, 46 Group Dirty Cache Line, 21 Group Shared Data, 22 L2, 85 Group Signal, 85 L2 Cache Address, 29 L2 Cache Bank, 29 Group Signals, 4 Group Transfer Acknowledge, 20 L2 Cache Data, 29 L2 Cache Output Enable A, 29 Group Transfer Hold, 20 L2 Cache Output Enable B, 29 Group Try Again Later, 19 GSHARE, 22, 56, 57, 58, 73 L2 Cache Write Enable, 29 L2-cache clock, 46 GTAL, 19 Level-2 Asynchronous SRAM Accesses, 61 GXACK, 20, 24, 28, 58, 66, 67, 75 GXHLD, 20, 24, 66, 67 Halt, 27, 72 High Non-Overlapping Time, 30, 60 HROM, 33 I Cache, 52, 85 I/O, 26 I/O Data Read, 27 I/O Data Write, 27

| Level-2 Cache, 45                          | Modified Cache-Block Hit During Single-         |

|--------------------------------------------|-------------------------------------------------|

| Asynchronous, 53, 61                       | Qword Operations, 74                            |

| Asynchronous Line Fill, 62                 | modified write-once, 54                         |

| Asynchronous READ, 61                      | Modified Write-Once Protocol, 85                |

| Asynchronous WRITE, 61                     | modified, exclusive, shared, or invalid (MESI), |

| Asynchrounous, 45                          | 54                                              |

| SRAM MODE, 53                              | Multi-Chip-Module, 2                            |

| Synchronous, 53, 63                        | MWO, 54, 86                                     |

| Synchronous READ, 63                       | Names, v                                        |

| Synchronous WRITE, 63                      | NB, 86                                          |

| Synchrounous, 45                           | NC, 33                                          |

| WE*, 29                                    | NexBus, v, 17, 42, 64, 86                       |

| Level-2 Cache Configuration. 53            | NexBus Address and Status, or Data, 24          |

| Level-2 Cache Signals, 29                  | NexBus Arbitration and Address Phase, 64        |

| Level-2 Synchronous SRAM Accesses, 63      | NexBus Clock, 30                                |

| Line, 85                                   | NexBus clock, 46                                |

| LOCK*, 18, 64, 74                          | NexBus Request, 17                              |

| Low Non-Overlapping Time. 30, 60           | NexBus Slot ID, 18                              |

| M, vi                                      | NexBus5, v, 17, 42, 44, 64                      |

| M/IO*, 27                                  | NexBus5 Bus Operations                          |

| Main Memory, 85                            | Halt and Shutdown, 72                           |

| Maskable Interrupt, 32                     | NexBus5 Cache Line Memory Operations, 71        |

| Master ID, 26                              | NexBus5 Halt and Shutdown, 72                   |

| MCM, 2                                     | NexBus5 I/O Operations, 71                      |

| Mechanical                                 | NexBus5 Interrupt-Acknowledge, 71               |

| Bottom, 82                                 | NexBus5 Intervenor Operations, 74               |

| Side, 81                                   | NexBus5 Memory Operations                       |

| Top, 80                                    | Cache Line, 71                                  |

| Mechanical Data, 79                        | Single-Qword, 66                                |

| Memory, 26, 85                             | NexBus5 Single-Qword Memory Operations, 66      |

| Memory Code Read, 27                       | NexBus5 Single-Qword Read Hits Modified         |

| Memory Data Read, 27                       | Cache Block, 75                                 |

| Memory Data Write, 27                      | NexBus5 Single-Qword Read with Wait States      |

| Memory operations, 64                      | using GXHLD only, 69                            |

| Memory or I/O*, 27                         | NexBus5 Single-Qword Read with Wait States      |

| Memory Reads, 51                           | using a delayed GXACK. 68                       |

| Memory Reads on NexBus. 51                 | NexBus5 Single-Qword Write with Wait States,    |

| Memory-Mapped I/O Reads, 51                | 70                                              |

| MESI, 85                                   | NMI*, 4, 18, 32, 59                             |

| MESI cache-coherency protocol, 54          | No-Op, 86                                       |

| MID. 26                                    | Non-Maskable Interrupt, 32                      |

| Modified, 54, 59, 86                       | Notation, v                                     |

| Modified Cache-Block Hit During Four-Qword | NPIRQ*, 32                                      |

| (Block) Operations, 75                     | NREQ*, 17, 64                                   |

|                                            | Nx586, 86                                       |

| Nx586 Features and Signals, 1       | Processor Clock, 46, 86        |

|-------------------------------------|--------------------------------|

| Nx586 Processor with Floating-Point | Processor Clock Phase 1, 31    |

| Execution Unit, 2                   | Publications, vii              |

| NxAD, 24                            | PULLHIGH, 33                   |

| NxAD bus, 4                         | PULLLOW, 33                    |

| NxCLK, 30, 46, 61                   | quadword, vi, 25               |

| NxMC, v                             | Qword, 86                      |

| NxPCI, v                            | qword, vi                      |

| NxVL, v, 86                         | Qword Address, 25              |

| Octet, 86                           | Read Order, 51                 |

| Operating Frequencies, 46           | read-modify-writes, 51         |

| Operation, 72, 86                   | References, vii                |

| Order of Transactions, 51           | Reserved, 25, 27, 28, 33       |

| OWN*, 22, 56, 57, 58                | Reserved Bits and Signals, vi  |

| OWNABL, 22, 56, 57, 58, 66, 73      | Reset, 32                      |

| Ownable, 22, 56                     | Reset CPU (Soft Reset), 32     |

| Owned, 86                           | RESET*, 18, 32                 |

| Ownership, 86                       | RESETCPU*, 18, 32, 72          |

| Ownership Request, 27, 56           | RISC86, 3                      |

| P4REF, 33                           | SCLKE, 30, 53                  |

| Paged devices, 21                   | Serial In, 33                  |

| passive exclusive use, 73           | Serial Out, 33                 |

| Peripheral Controller, 86           | SERIALIN, 33                   |

| PGA Package side view, 81, 82       | SERIALOUT, 33                  |

| PGA Package top view, 80            | Set, 87                        |

| PH1, 61                             | SHARE*, 22, 56, 58, 73, 74     |

| PH2, 61                             | Shared, 54, 58, 87             |

| Phase, 86                           | Shared Data, 22, 56            |

| Phase-Locked Loop, 60               | Shutdown, 27, 72               |

| PHE1, 30, 60                        | signal organization, 4         |

| PHE2, 30                            | Signals, v                     |

| PLL, 60, 86                         | Arbitration, 17                |

| PLL Analog Power, 31                | Cache Control, 21              |

| PLL Mode                            | Clocks, 30                     |

| External, 30, 31                    | Cycle Control, 19              |

| Non-Overlapping Time, 30, 60        | Interrupt, 32                  |

| NxCLK, 30                           | Level-2 Cache, 29              |

| PHE1, 30                            | NexBus, 17                     |

| PHE2, 30, 60                        | NexBus Address and Data, 24    |

| XSEL, 31                            | NexBus5, 17                    |

| POPHOLD, 33                         | NexBus5 Address and Data. 24   |

| Power Reference, 33                 | Reserved, 33                   |

| preemptive exclusive use, 73        | Reset, 32                      |

| Present, 86                         | Test. 33                       |

| Processor, 86                       | Single Oword Read or Write, 26 |

Sirty, 59 SLOTID, 4, 18, 26 SLOTID 0000, 18 Snoop, 87 Snoop Enable, 28, 57 Snoop Hit, 87 Snoop Miss, 87 Snooping, 21, 54 SNPNBL, 28, 57 Source, vi. 87 SRAM, 45 SRAMMODE, 29, 53 Stale, 59, 87 State Transitions, 55 Storage Hierarchy, 48 Synchronous signals, 4 System Bus, 87 System Controller, 87 T-Byte, 87 Test, 33 Test Phase 1 Clock, 33 Test Phase 2 Clock, 33 Test Power, 33 TESTPWR\*, 33 Timing Diagrams, v TPH1, 33 TPH2, 33 Transaction Ordering, 51 Transceiver NexBus Clock Enable, 23 Transceiver-to-NexBus Output Enable, 23 Transceiver-to-NxAD-Bus Output Enable. 23 Transceivers External, 23, 42 Internal, 44 Systems Logic, 43 **XBCKE\***, 23 XBOE\*, 23 XCVERE\*, 23, 42 XNOE\*, 23 transceivers, 23 Transfer Acknowledge, 19 Transfer Hold, 20 Transfer Type, 26 Try Again Later, 19

video adapters, 21 W/R\*, 27 WE\*, 29 Word, 87 word, vi Write or Read\*, 27 Write Order, 51 write queue, 52 Writes, 51 x86 Architecture, vii XACK\*, 19, 66, 67 **XBCKE\***, 23 XBOE\*, 23 XCVERE\*, 23, 42, 44 XHLD\*, 20, 67, 73, 74, 75 XNOE\*, 23 XPH1, 31 XREF, 31 XSEL, 31, 60

VDDA, 31

- 1623 Buckeye Drive Milpitas, CA 95035 Ph 1-800-8NEXGEN Fax (408) 435-0262

18 bis rue du montceau 77133 Féricy (France) Ph 33 (1) 64.23.68.65 Fax 33 (1) 64.23.61.91