intellec 41

Mod 40

Microcomputer

Microcoment

Development

System Reference Manual

intellec Al Intellec Mod Al Mod AO Microcomputer Development System System Reference Manual

CAUTION

CAUTION

CAUTION

CAUTION

CAUTION

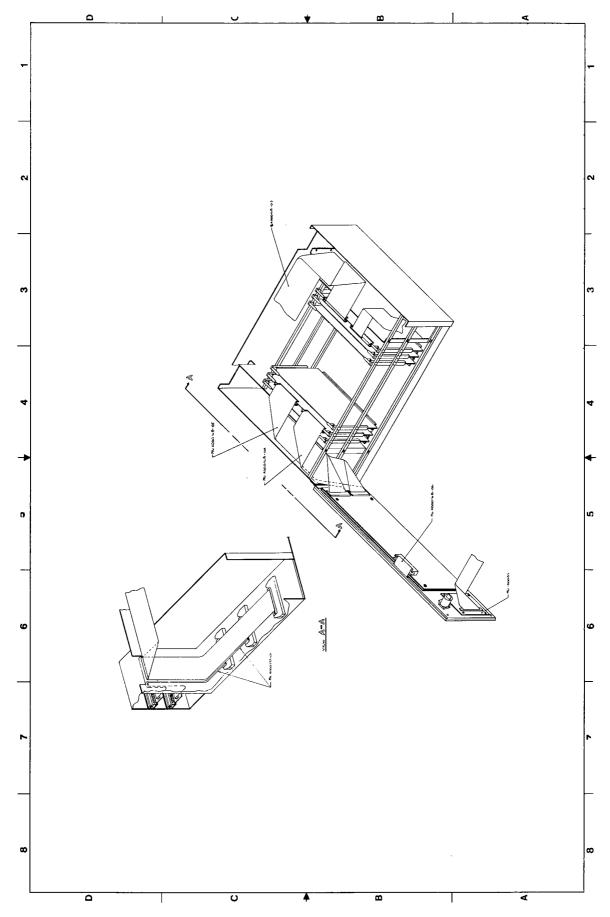

Cover removed.

A!Mod 40 system with the cover removed.

A!Mod 40 system with the cover removed.

CAUTION

Cover residence in the inferior of cooling air may cause over heating and damage.

The resulting diversion of cooling air may cause over heating and damage.

The resulting power supplies.

# TABLE OF CONTENTS

|       | Stop                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vii   | Interrupt                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | Test                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| vii   |                                       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| vii   | Clock Reference Oscillator And Timing |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| viii  | Generator                             | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ix    | Module Memory                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ix    | Teletype Interface                    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| x     | UTILIZATION                           | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| x     | Installation                          | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | Memory Expansion Provisions           | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ×     | Input/Output Expansion                | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| хi    | Program RAM                           | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0 xii | Pin List                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | CHAPTER 3                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| xii   |                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1     |                                       | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1     |                                       | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2     |                                       | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | —                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                       | 4.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                       | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                       | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | _                                     | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| -     | •                                     | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | • • •                                 | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | · · · · · · · · · · · · · · · · · · · | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | ·                                     | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | ·                                     | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                       | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15    | Input Port And Latch                  | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | vii viii ix ix x x xi 0 xii  1        | vii PERIPHERAL LOGIC vii Clock Reference Oscillator And Timing viii Generator ix Module Memory ix Teletype Interface x UTILIZATION x Installation    Memory Expansion Provisions Input/Output Expansion xi Program RAM 0 xii Pin List  CHAPTER 3 xii THE imm6-28 RAM MEMORY MODULE    FUNCTIONAL DESCRIPTION 1 2102 RANDOM ACCESS MEMORY ELEMENT 1 THEORY OF OPERATION OF THE RAM 1 MEMORY MODULE    UTILIZATION 1 Installation    Pin List 4 CHAPTER 4 5 THE CONTROL MODULE 6 FUNCTIONAL DESCRIPTION OF THE MODULE 7 Reflexive Read (Program Mode) 6 CMA Write (Console Memory Access) 7 Transitive Write (WPM) 8 Transitive Read (RPM) 9 Miscellaneous Control Functions 9 THEORY OF OPERATION 9 Timing Generator 10 Address Multiplexer 11 Write Data Multiplexer |

i

| Output Port And Latch                | 50 | THEORY OF OPERATION                      | 81  |

|--------------------------------------|----|------------------------------------------|-----|

| Write Enable                         | 52 | UTILIZATION                              | 82  |

| CMA Enable                           | 52 | Installation                             | 82  |

| Write Generator                      | 52 | Expanding The Instruction Storage        | 84  |

| Memory Selection                     | 52 | Pin List                                 | 84  |

| Reset Generator                      | 53 | OHARTER                                  |     |

| Stop Generator                       | 53 | CHAPTER 8                                | -   |

| Use With INTELLEC® 4/MOD 4 System    | 53 | THE imm4-24 DATA STORAGE MODULE          | 87  |

| UTILIZATION                          | 53 | FUNCTIONAL DESCRIPTION OF THE            |     |

| Installation                         | 53 | MODULE                                   | 87  |

| Pin List                             | 54 | THEORY OF OPERATION                      | 88  |

|                                      | ٠. | UTILIZATION                              | 88  |

| CHAPTER 5                            |    | Installation                             | 88  |

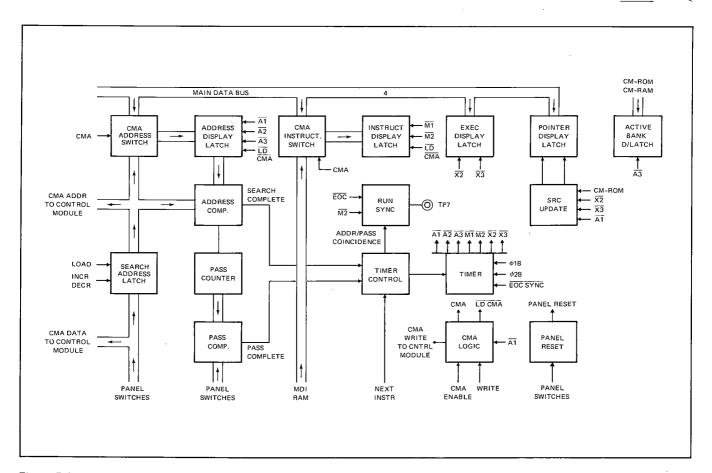

| THE CONTROL AND DISPLAY PANEL        | 59 | Expanding Data Storage                   | 90  |

| FUNCTIONAL DESCRIPTION OF THE        |    | Pin List                                 | 90  |

| CONTROL AND DISPLAY PANEL            | 59 | CHAPTER 9                                |     |

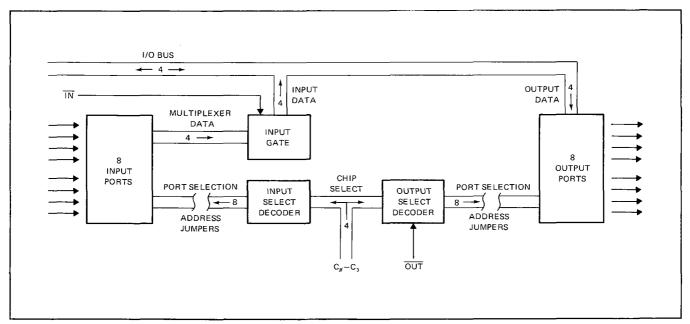

| Timer                                | 59 | THE imm4-60 INPUT/OUTPUT MODULE          | 97  |

| Display Latches                      | 59 | FUNCTIONAL DESCRIPTION OF THE I/O        |     |

| Search Mode                          | 60 | MODULE                                   | 97  |

| Run Mode                             | 62 | The System During I/O Transactions       | 97  |

| CMA Mode                             | 62 | Functional Description Of The I/O Module | 97  |

| Reset                                | 62 | THEORY OF OPERATION OF THE I/O           | •   |

| THEORY OF OPERATION                  | 62 | MODULE                                   | 98  |

| Timer                                | 62 | Input                                    | 98  |

| Display Latches                      | 63 | Output                                   | 98  |

| SRC Update                           | 63 | UTILIZATION                              | 100 |

| Search Address Latch                 | 63 | Installation                             | 100 |

| Search Comparator                    | 65 | Pin List                                 | 101 |

| Pass Counter                         | 65 |                                          |     |

| Pass Comparator                      | 65 | CHAPTER 10                               |     |

| Timer Control                        | 65 | INTELLEC®4/MOD 40 MAINFRAME              | 107 |

| Run SYNC                             | 66 | POWER SUPPLIES                           | 107 |

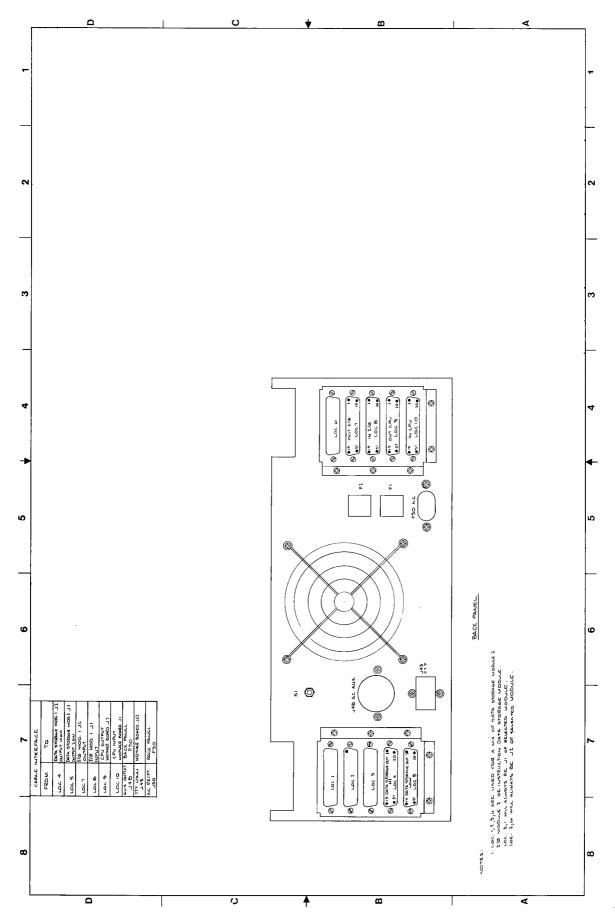

| CMA Logic                            | 66 | CHASSIS LAYOUT                           | 107 |

| Panel Reset                          | 66 | SYSTEM INTERCONNECTION                   | 107 |

| UTILIZATION                          | 66 | CHAPTER 11                               |     |

| Environment                          | 66 | THE imm6-76 PROM PROGRAMMER MODULE       | 113 |

| Electrical Connections               | 66 | THE 4702A PROGRAMMABLE READ ONLY         |     |

| Power Requirements                   | 67 | MEMORY                                   | 113 |

| Signal Requirements                  | 67 | FUNCTIONAL DESCRIPTION OF THE            |     |

| Pin List                             | 67 | MODULE                                   | 114 |

| CHARTER                              |    | THEORY OF OPERATION OF THE MODULE        | 114 |

| CHAPTER 6                            |    | Data Distribution                        | 116 |

| THE imm4-22 INSTRUCTION/DATA STORAGE |    | Control And Timing                       | 116 |

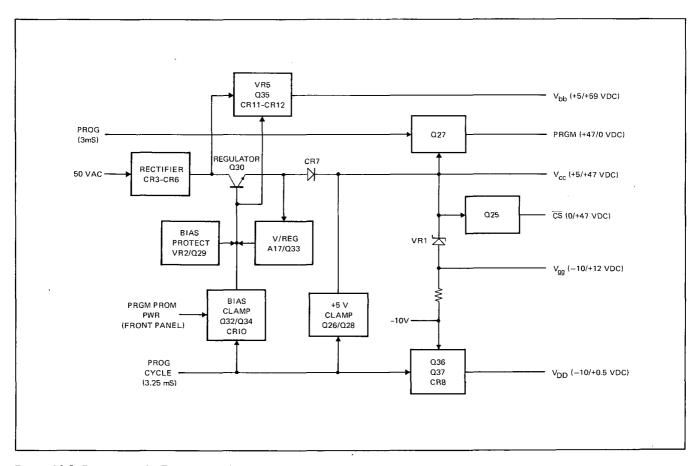

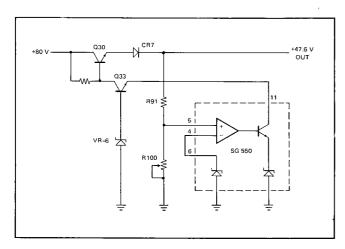

| MODULE                               | 71 | Power Supply                             | 116 |

| FUNCTIONAL DESCRIPTION OF THE        |    | UTILIZATION                              | 119 |

| MODULE                               | 71 | Installation                             | 119 |

| THEORY OF OPERATION                  | 72 | Pin List                                 | 119 |

| Chip Decoding                        | 72 | 1 111 -100                               | 113 |

| Instruction Fetch                    | 74 | CHAPTER 12                               |     |

| ROM Input                            | 74 | INSTALLATION AND INTERFACING             | 123 |

| ROM Output                           | 74 | OPERATING PRECAUTIONS                    | 123 |

| RAM Memory Reference                 | 74 | INSTALLATION OF THE INTELLEC® 4/MOD      |     |

| UTILIZATION                          | 74 | 40 SYSTEM                                | 123 |

| Installation                         | 74 | Power Requirements                       | 123 |

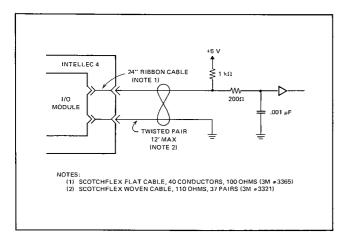

| Pin List                             | 74 | Interface Requirements                   | 123 |

| CHAPTER 7                            |    | TELETYPE                                 | 129 |

| THE imm6-26 PROM MEMORY MODULE       | 81 | The Model ASR 33 Teletype Set            | 129 |

| FUNCTIONAL DESCRIPTION OF THE        | 01 | Modification Of The Teletype Set         | 130 |

| MODULE                               | 81 | Installing The Teletype Set              | 133 |

|                                      |    |                                          |     |

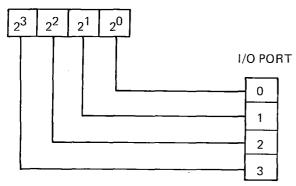

| I/O Programming                          | 133 | INDEX REGISTER TO ACCUMULATOR    |       |

|------------------------------------------|-----|----------------------------------|-------|

| imm4-90 HIGH-SPEED PAPER TAPE            |     | INSTRUCTIONS                     | xvi   |

| READER                                   | 137 | ACCUMULATOR INSTRUCTIONS         | xvi   |

| Installing The Reader                    | 137 | IMMEDIATE INSTRUCTIONS           | xvii  |

| Functional Description Of The High-Speed |     | TRANSFER OF CONTROL INSTRUCTIONS | xvii  |

| Reader                                   | 139 | SUBROUTINE LINKAGE INSTRUCTIONS  | xviii |

| I/O Programming                          | 139 | NOP INSTRUCTION                  | xviii |

|                                          |     | MEMORY SELECTION INSTRUCTIONS    | xviii |

|                                          |     | I/O AND RAM INSTRUCTIONS         | xix   |

| APPENDIX A                               |     | 4040 ONLY INSTRUCTIONS           | xix   |

| INSTRUCTION SUMMARY                      | χV  | APPENDIX B                       |       |

| INDEX REGISTER INSTRUCTIONS              | xvi | EXECUTION CYCLE                  | xxi   |

# LIST OF FIGURES

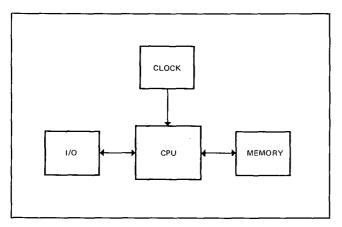

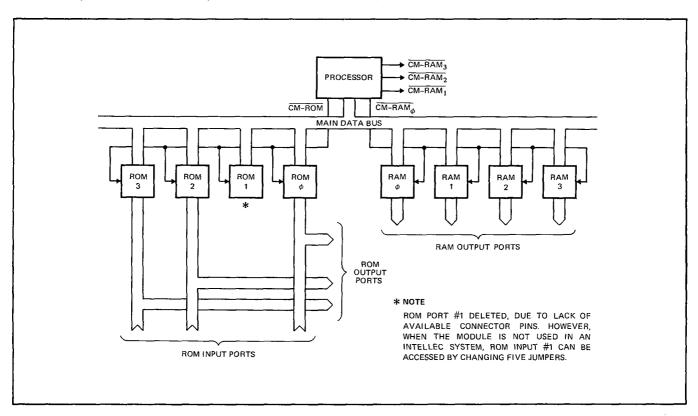

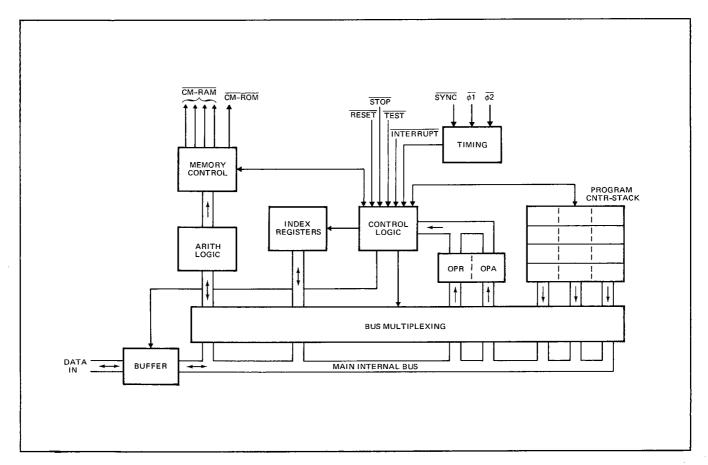

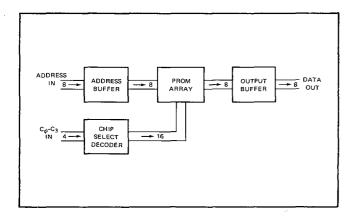

| 1-1.  | INTELLEC® 4 System Block Diagram           | 2   | 7-1.             | PROM Module Functional Block Diagram  | 82         |

|-------|--------------------------------------------|-----|------------------|---------------------------------------|------------|

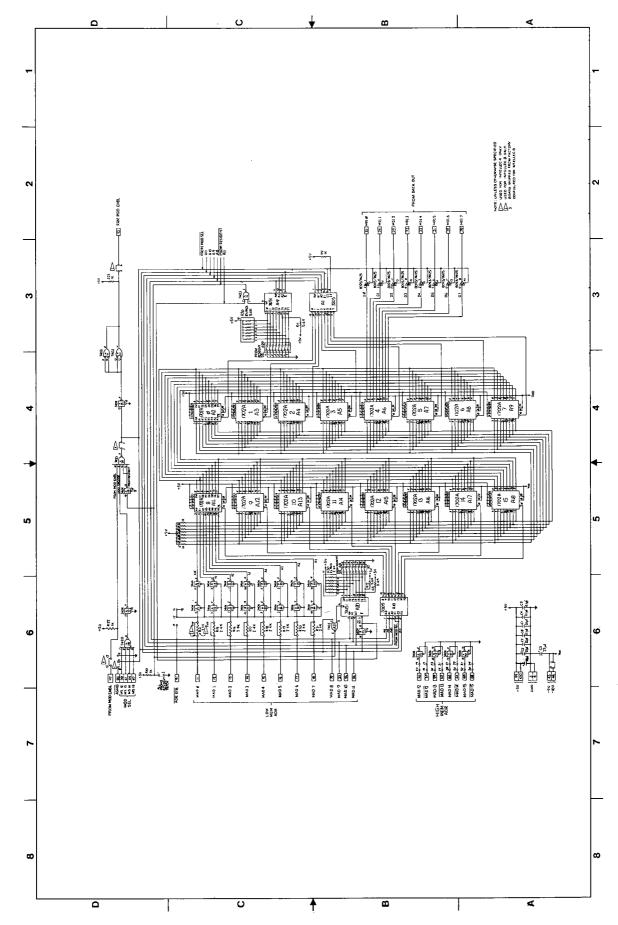

| 2-1.  | Central Processor Module: Functional       |     | 7-2.             | PROM Module Schematic Diagram         | 83         |

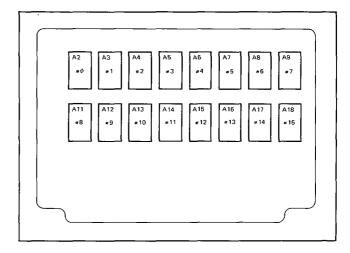

|       | Block Diagram                              | 4   | 7-3.             | PROM Location Diagram                 | 84         |

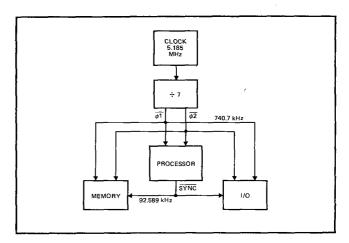

| 2-2.  | System Synchronization                     | 4   | 8-1.             | Data Storage Module Functional Block  | 87         |

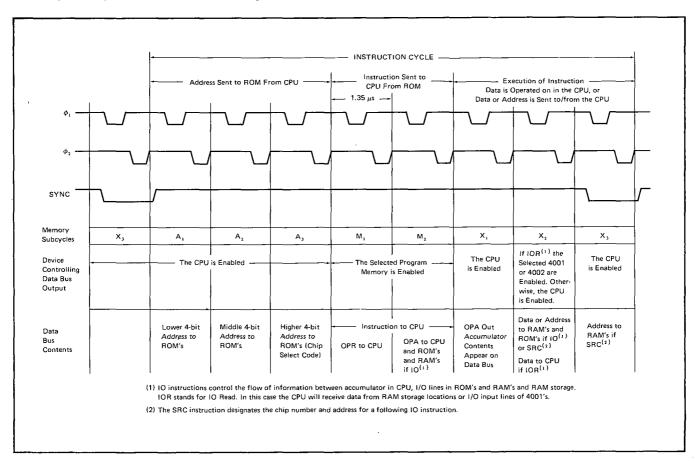

| 2-3.  | System Timing Diagram                      | 5   | 8-2.             | Data Storage Module Schematic Diagram | 89         |

| 2-4.  | Memory And I/O Control                     | 6   | 8-3.             | RAM Location Diagram                  | 91         |

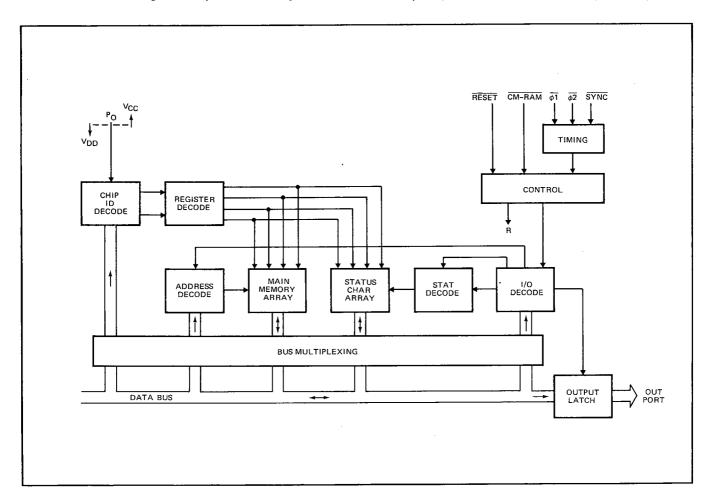

| 2-5.  | 4040 Processor Functional Block            | 11  | 9-1,             | I/O Module Functional Block           | 98         |

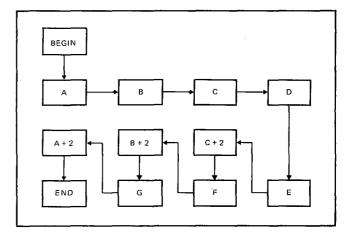

| 2-6.  | Program Jump                               | 12  | 9-2.             | I/O Module Schematic Diagram          | 99         |

| 2-7.  | Subroutine Jump                            | 12  |                  |                                       |            |

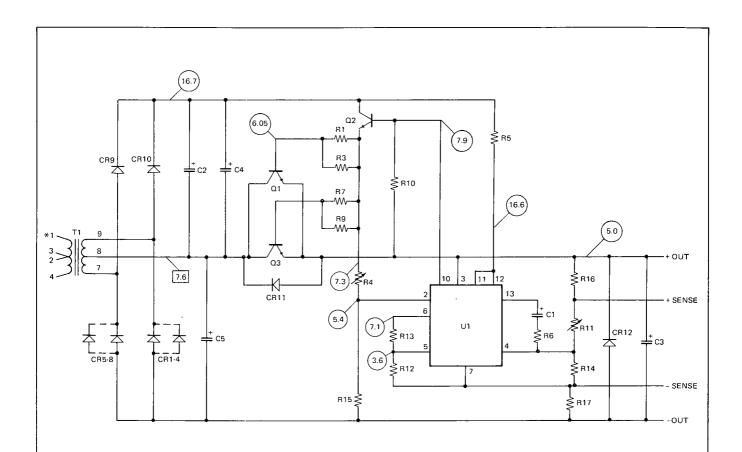

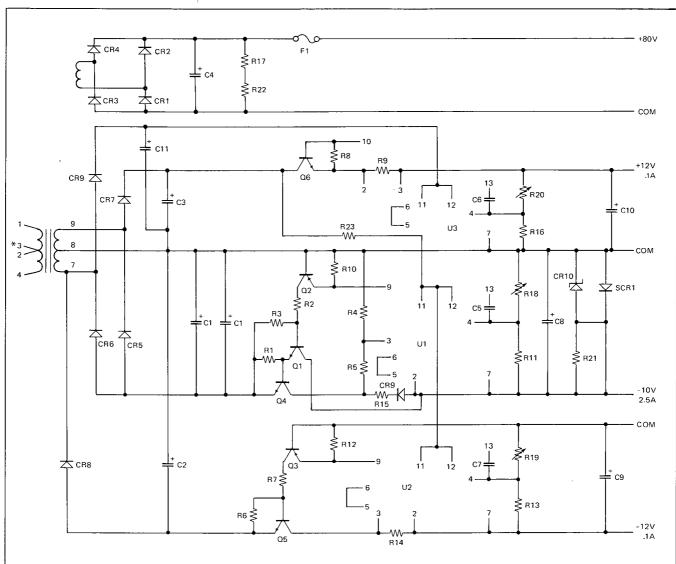

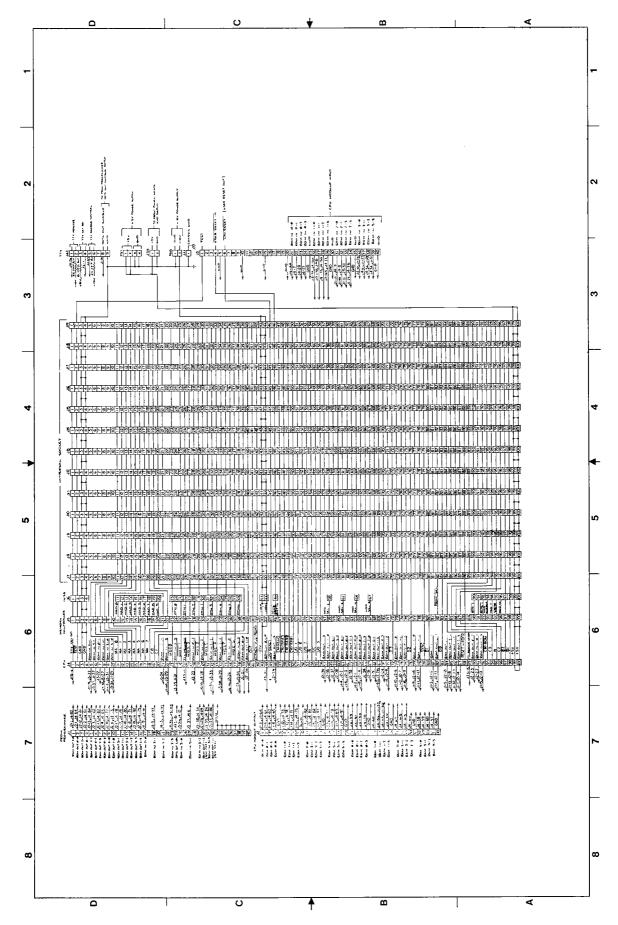

| 2-8.  | Nested Subroutines                         | 12  | 10-1.            | Power Supply Schematic (±5 VDC)       | 108        |

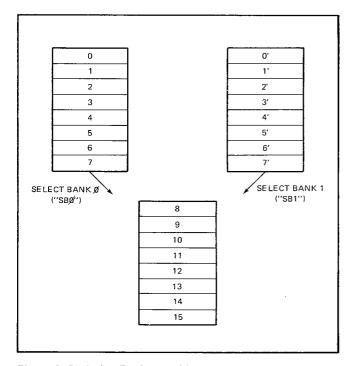

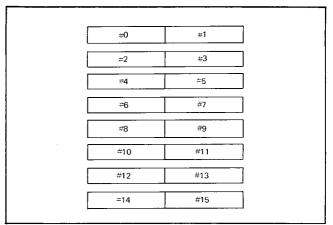

| 2-9.  | Index Register Addressing                  | 13  | 10-2.            | Power Supply Schematic (-10 VDC And   |            |

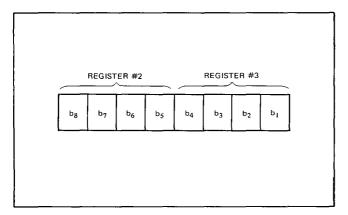

| 2-10. | Paired Index Registers                     | 13  |                  | +80 VDC)                              | 109        |

| 2-11. | Central Processor Module Data Bussing      | 18  | 10-3.            | INTELLEC® 4 Chassis Layout            | 110        |

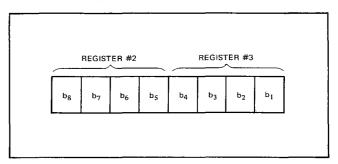

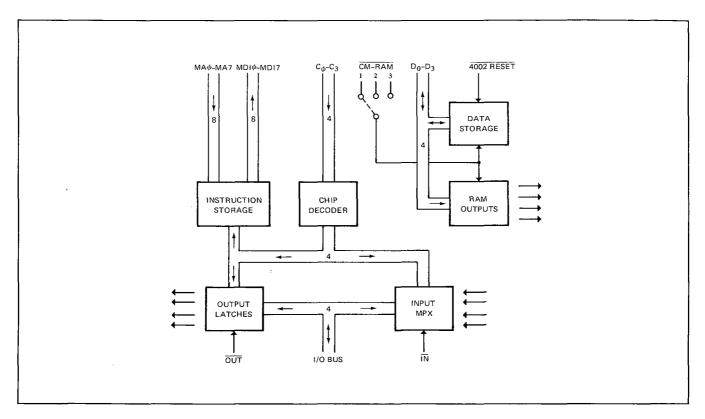

| 2-12. | 4002 RAM Functional Block Diagram          | 19  | 10-4.            | INTELLEC® 4 Mother Board Schematic    | 111        |

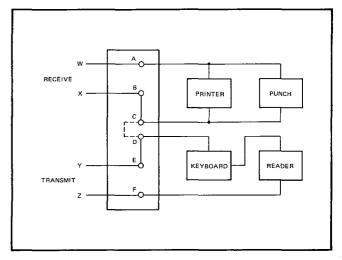

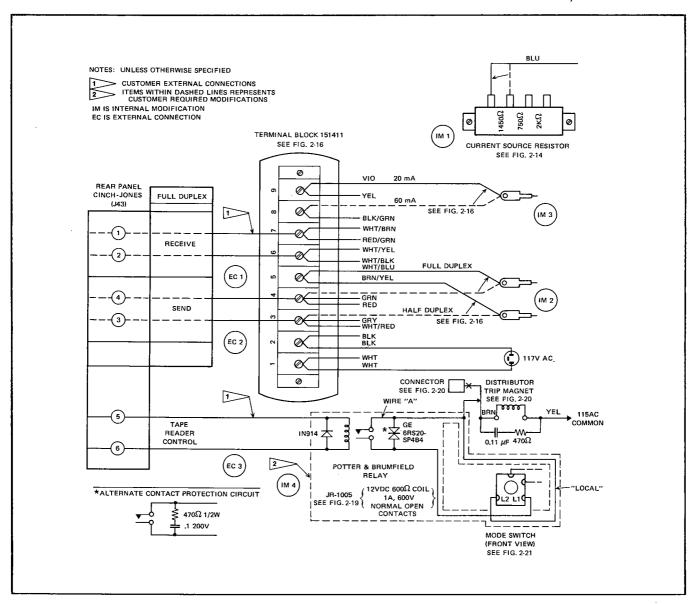

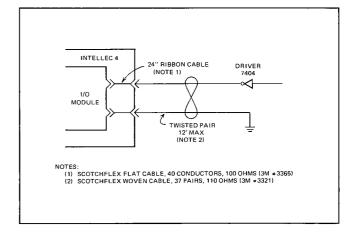

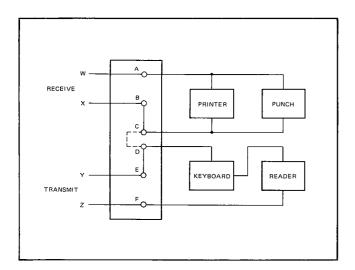

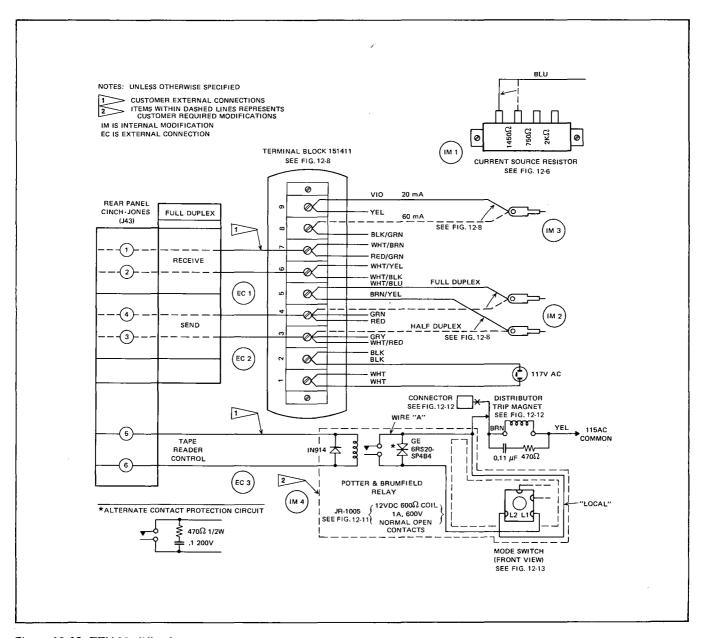

| 2-13. | TTY: Half Duplex/Full Duplex               | 21  | 10-5.            | Internal Cabling                      | 112        |

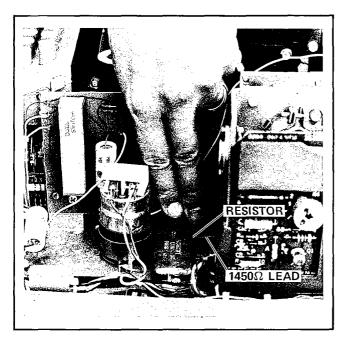

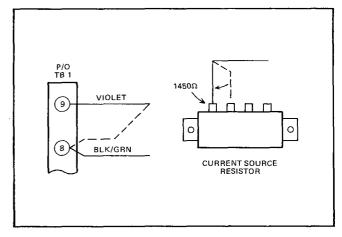

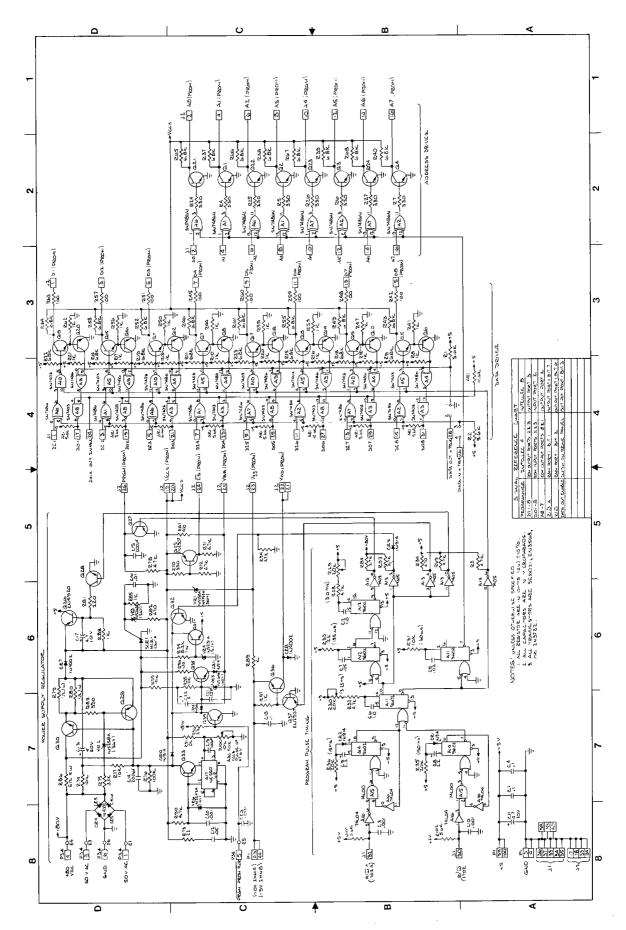

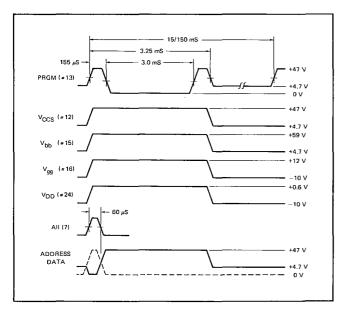

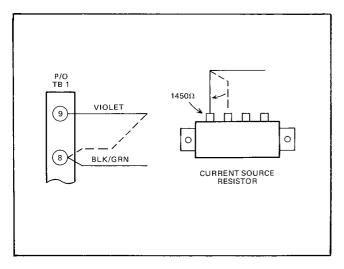

| 2-14. | Current Source Resistor                    | 25  | 11-1.            | PROM Programmer Schematic Diagram     | 115        |

| 2-15. | TTY: 20 mA Wiring                          | 25  | 11-2.            | PROM Programmer Timing                | 117        |

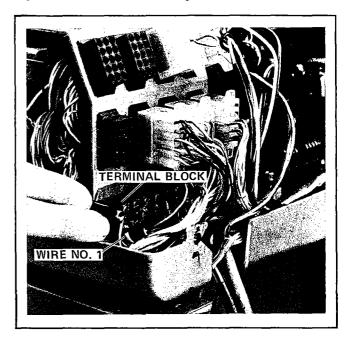

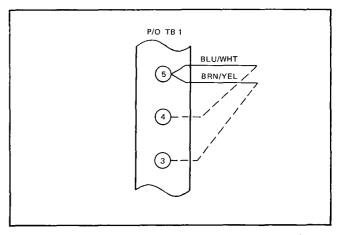

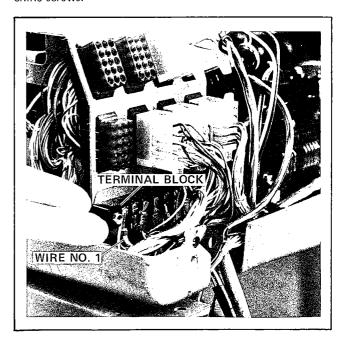

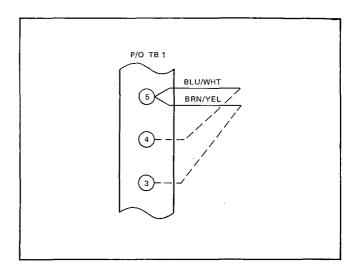

| 2-16. | Terminal Block Location                    | 25  | 11-3.            | Power Supply Functional Block         | 117        |

| 2-17. | TTY: Full Duplex Wiring                    | 25  | 11-4.            | Voltage Regulator Loop: Simplified    |            |

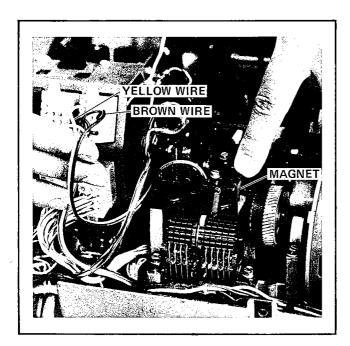

| 2-18. | TTY Modifications                          | 26  |                  | Schematic Equivalent                  | 118        |

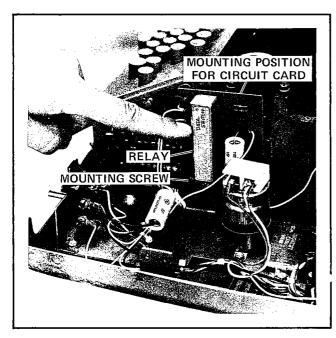

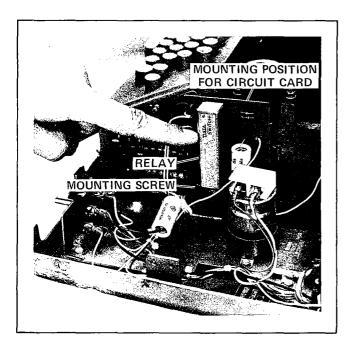

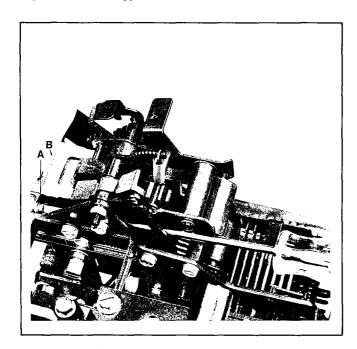

| 2-19. | Relay Board Location                       | 27  | 12-1.            | ROM Port Output Characteristics       | 124        |

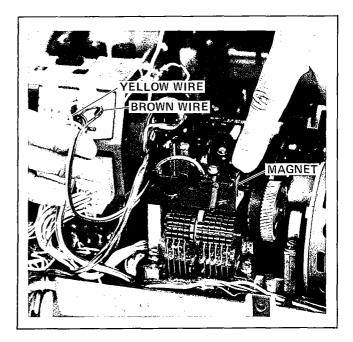

| 2-20. | ESU Wiring                                 | 27  | 12-1.<br>12-2.   | INTELLEC® 4: Rear Panel Layout        | 124        |

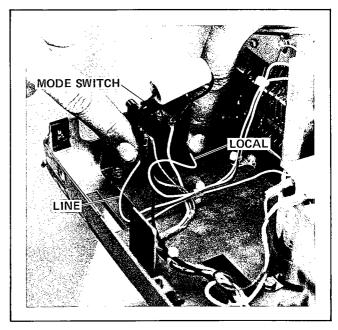

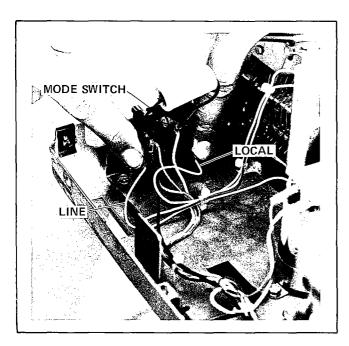

| 2-21. | Teletype Mode Switch                       | 27  | 12-2.<br>12-3,   | INTELLEC® 4: Output Interface         | 127        |

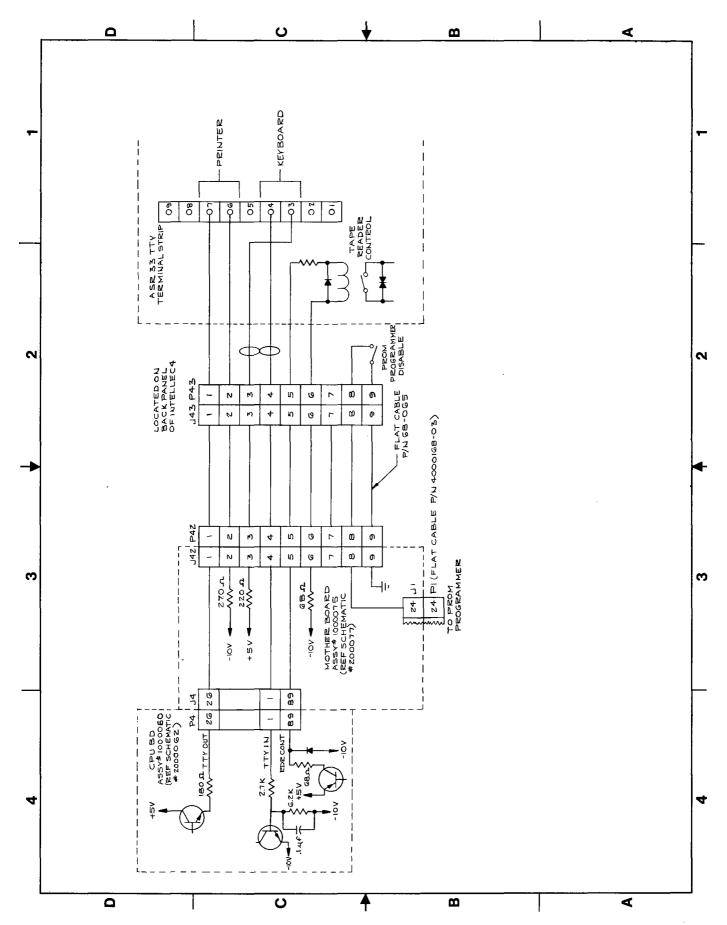

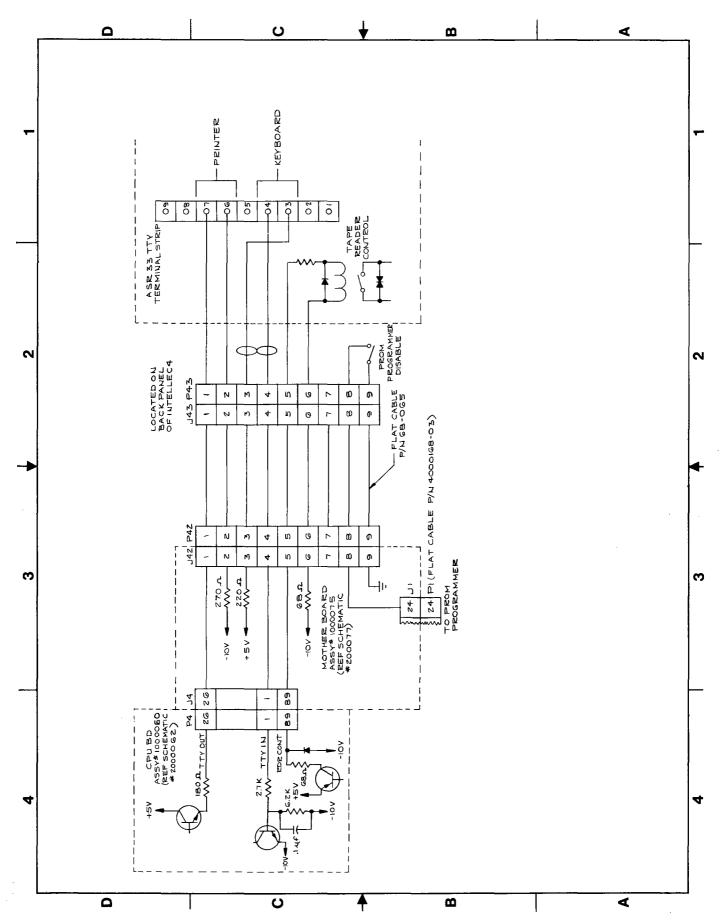

| 2-22. | TTY Interface                              | 28  | 12-3.<br>12-4.   | INTELLEC® 4: Output Interface         |            |

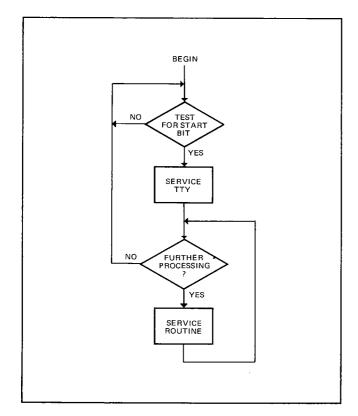

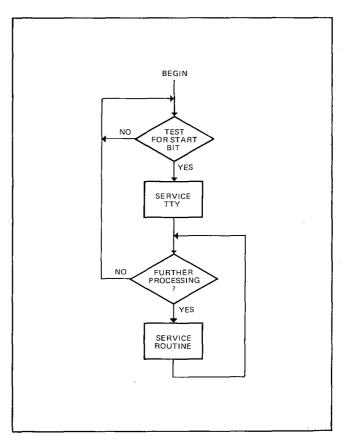

| 2-23. | Teletype Input Routine                     | 29  | 12-4.<br>12-5.   | TTY: Half Duplex/Full Duplex          | 128<br>131 |

| 2-24. | Teletype Character Input                   | 30  | 12-5.<br>12-6.   | Current Source Resistor               | 131        |

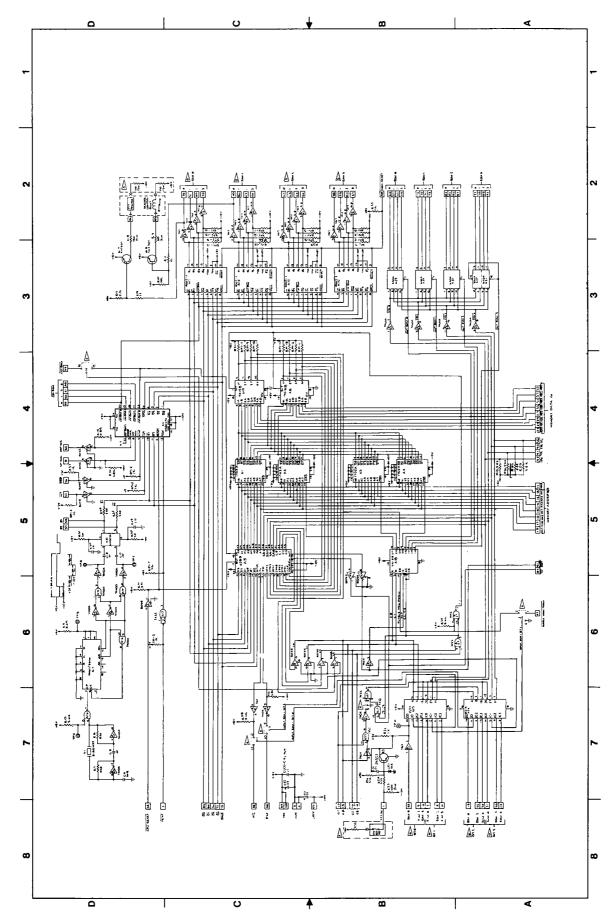

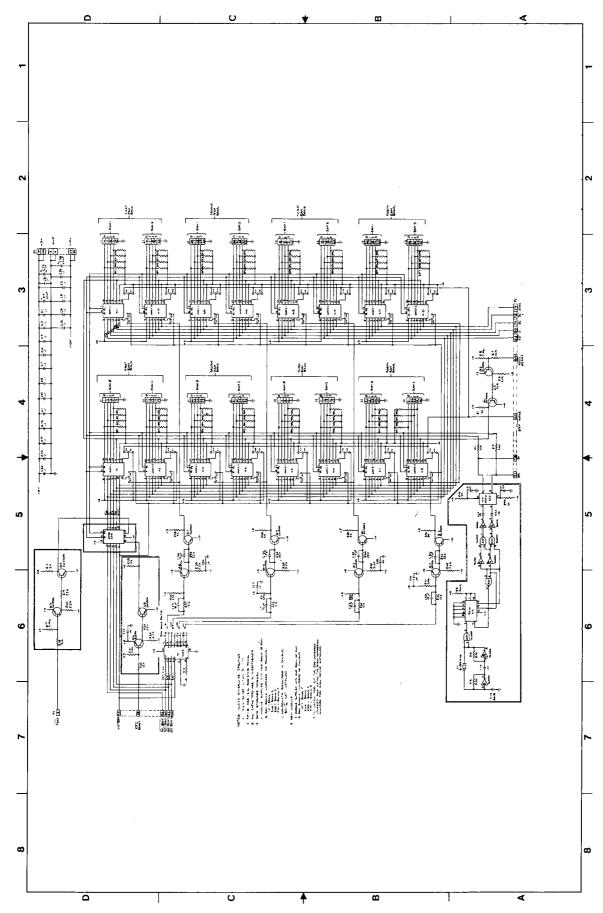

| 2-25. | Central Processor Module Schematic         | 31  | 12-6.<br>12-7,   | TTY: 20 mA Wiring                     | 131        |

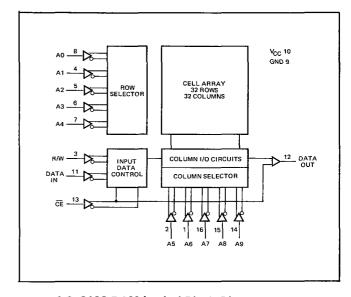

| 3-1.  | RAM Memory Module Functional Block         | 35  | 12-7.<br>12-8.   | Terminal Block Location               | 131        |

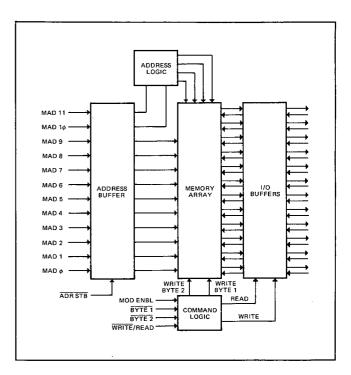

| 3-2.  | 2102 RAM Logical Block Diagram             | 36  | 12-6.<br>12-9.   | TTY: Full Duplex Wiring               | 132        |

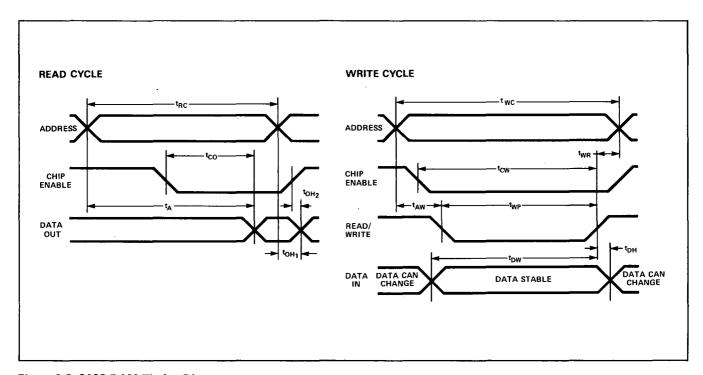

| 3-3.  | 2102 RAM Timing Diagram                    | 36  | 12-9.<br>12-10.  | TTY Modifications                     | 132        |

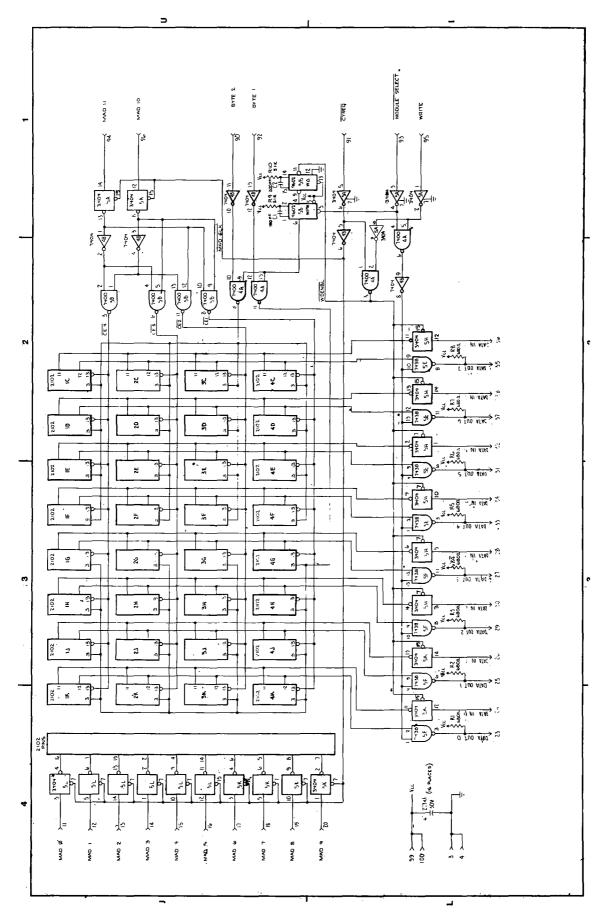

| 3-4.  | RAM Memory Module Schematic                | 38  | 12-10.<br>12-11. |                                       | 133        |

|       | ·                                          |     | 12-11.<br>12-12. | Relay Board Location ESU Wiring       | 133        |

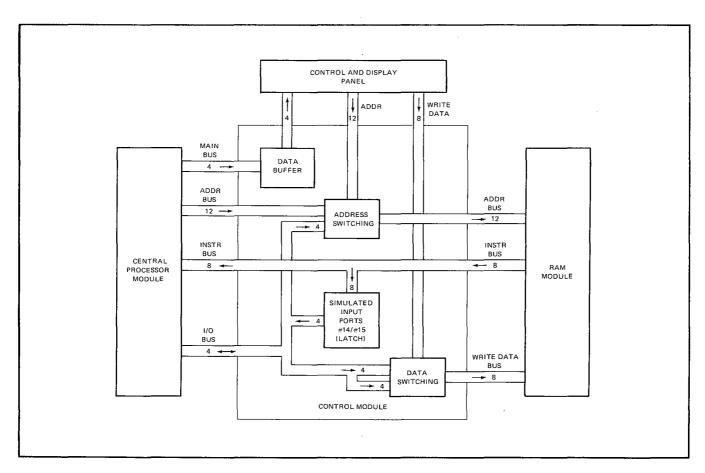

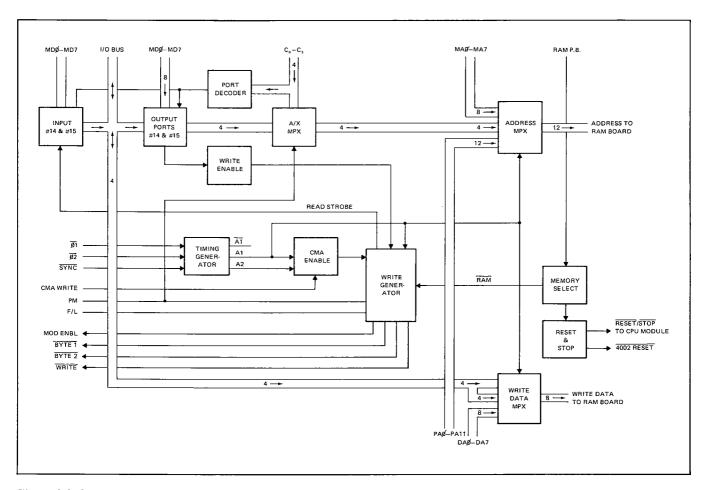

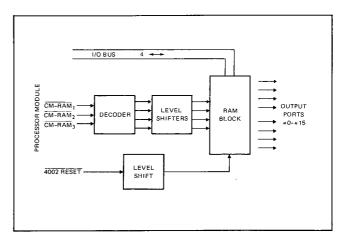

| 4-1.  | Control Module Functional Block            | 45  | 12-12.<br>12-13. | Teletype Mode Switch                  | 134        |

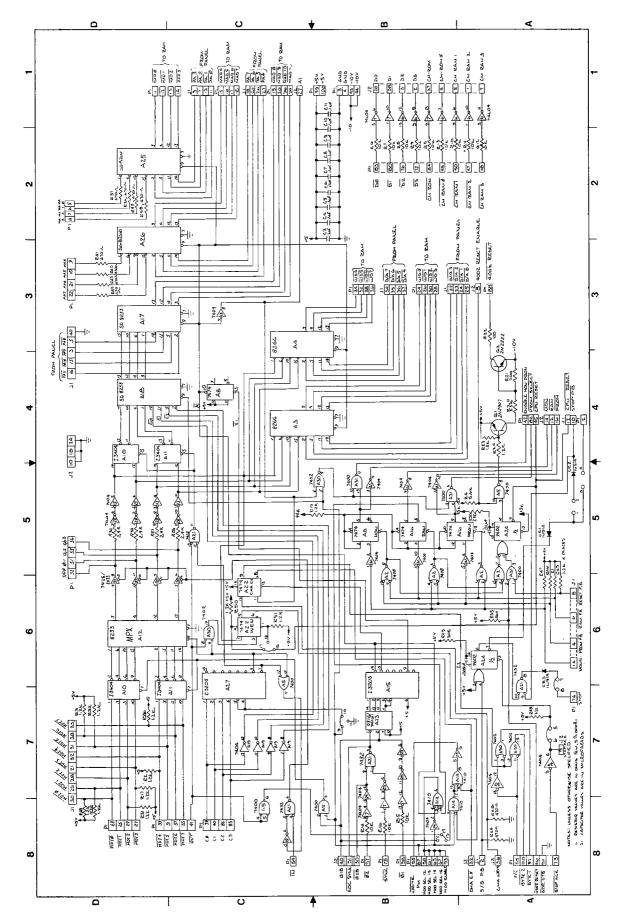

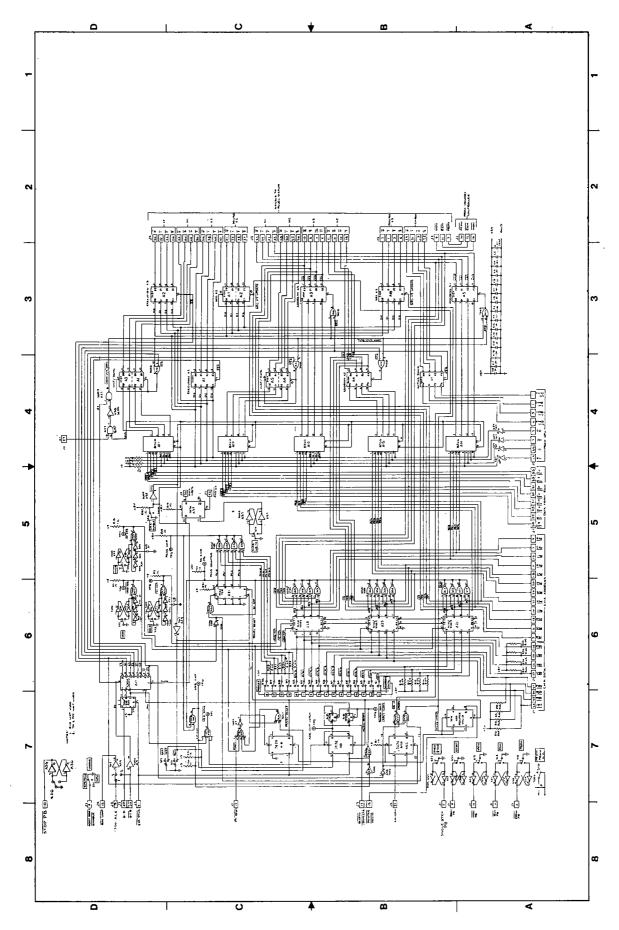

| 4-2.  | Control Module Schematic                   | 51  | 12-13.<br>12-14. | Fanfold Guide Installation            | 134        |

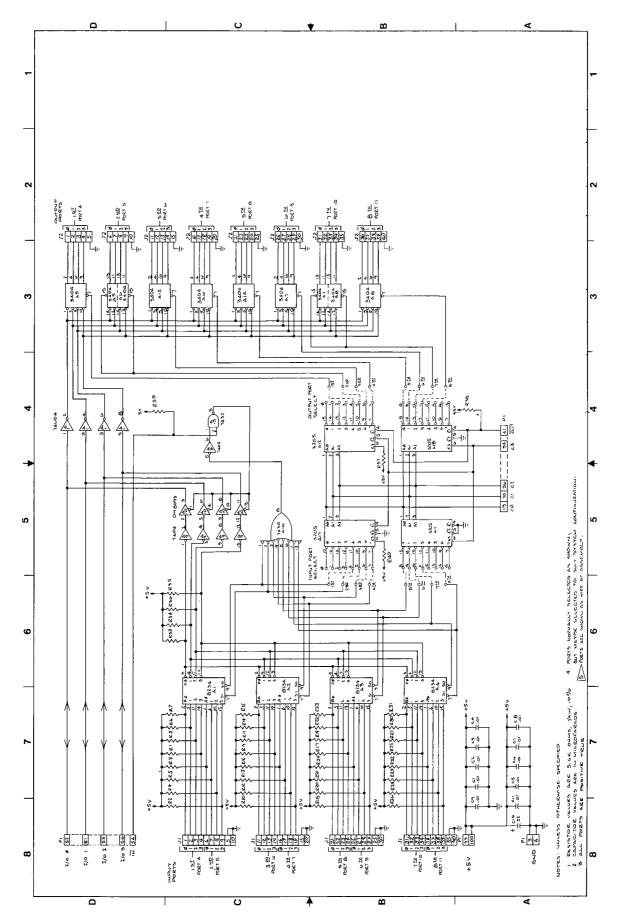

| 5-1.  | Control And Display Panel Functional Block | 60  |                  |                                       | 135        |

| 5-2.  | Control And Display Panel Schematic        | 64  | 12-15.<br>12-16. | Teletype Installation                 | 139        |

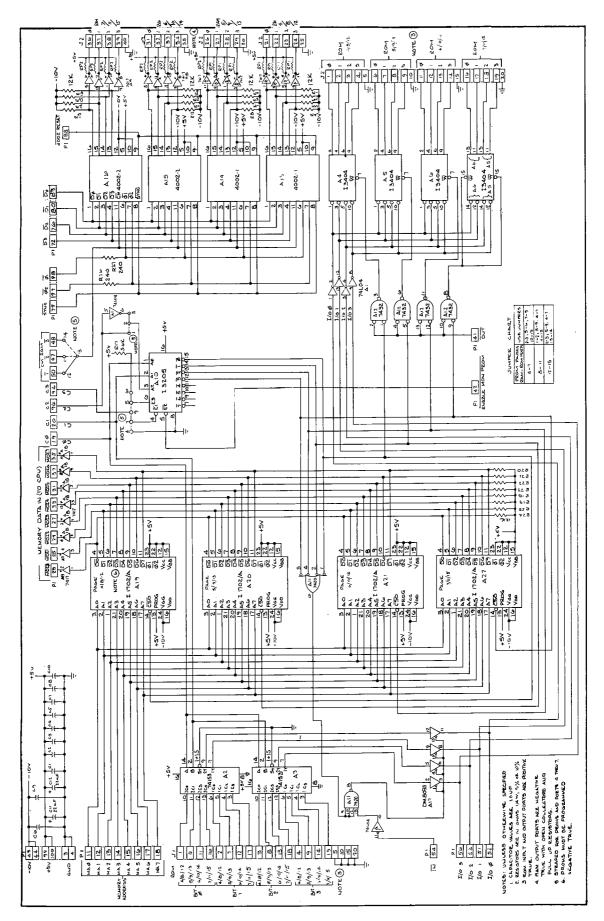

| 6-1.  | imm4-72 Functional Block Diagram           | 72  | 12-16.<br>12-17. | Teletype Input Routine                | 134        |

| 6-2.  | imm4-22 Schematic Diagram                  | 73  | 12-17.<br>12-18. | Teletype Character Input              | 139        |

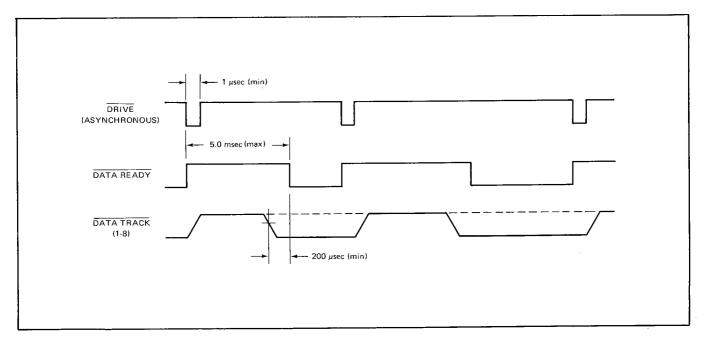

|       | == Sonomatio Diagram                       | , , | 12-18.           | Tape Reader Timing                    | 139        |

# LIST OF TABLES

| 0-1. | INTELLEC® 4/MOD 40 Specifications | xii      | 8-1.  | RAM Identification              | 88  |

|------|-----------------------------------|----------|-------|---------------------------------|-----|

| 0.1  | 4002 Chin Idontification          | 20       | 8-2.  | Data Storage Expansion          | 91  |

| 2-1. | 4002 Chip Identification          | 20       | 8-3.  | P1 Pin List                     | 92  |

| 2-2. | P1 Pin List                       | 32       | 8-4.  | J1 Pin List                     | 94  |

| 3-1. | P1 Pin List                       | 41       | 8-5.  | J2 Pin List                     | 95  |

| 4-1. | P1 Pin List                       | 55       | 9-1.  | P1 Pin List                     | 102 |

| 4-2. | J1 Pin List                       | 57       | 9-2.  | J1 Pin List                     | 104 |

| 4-3. | J2 Pîn List                       | 58       | 9-3.  | J2 Pin List                     | 105 |

| 5-1. | Mating Connectors                 | 67       | 11-1. | P1 Pin List                     | 120 |

| 5-2. | J1 Pin List                       | 68       | 11-2. | J1 Pin List                     | 121 |

| 5-3. | J2 Pin List                       | 69       | 11-3. | J2 Pin List                     | 121 |

| 5-4. | J3 Pin List                       | 70       | 11-4. | J3 Pin List                     | 122 |

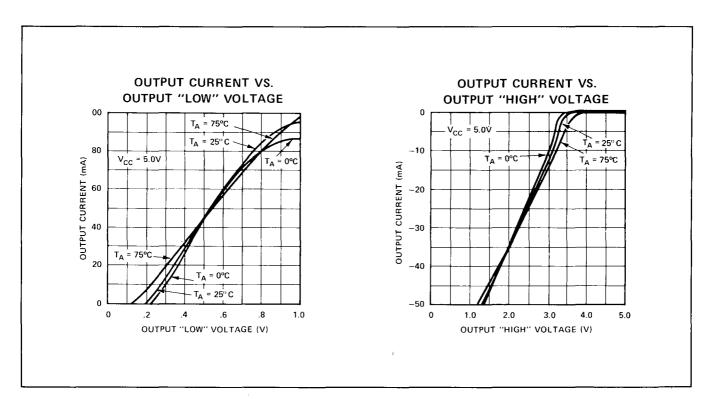

| 6-1. | imm4-22 Capability                | 71       | 12-1. | RAM Port Output Characteristics | 124 |

| 6-2. | Chip ID Wiring Options            | 75       | 12-2. | ROM Port Input Characteristics  | 125 |

| 6-3. | P1 Pin List                       | 76       | 12-3. | Input Connector                 | 126 |

| 6-4. | J1 Pin List                       |          | 12-4. | Output Connector                | 126 |

|      |                                   | 78<br>70 | 12-5. | I/O Port Usage                  | 128 |

| 6-5. | J2 Pin List                       | 79       | 12-6. | Teletype Connector (J43)        | 133 |

| 7-1. | P1 Pin List                       | 85       | 12-7. | High-Speed Reader Wiring        | 138 |

٧

vi

# INTRODUCTION

#### SCOPE OF THIS MANUAL

The INTELLEC® 4/MOD 40 Reference Manual is part of a three-volume set which describes the INTELLEC® 4/MOD 40 microcomputer development system. The INTELLEC® 4 Operator's Manual tells how to operate the system, and describes the use of its standard software provisions. The 4004/4040 Assembly Language Programming Manual explains how to program the system using the special INTELLEC® 4/MOD 40 assembly language mnemonics.

This manual describes the capabilities of the IN-TELLEC®4/MOD 40 system, with special reference to the design concepts that underlie them. It covers the entire system, and it covers the system's individual modular components. It describes the theory of operation of each module both at the functional level and at the circuit level. And it provides guidelines for those who intend to use selected modules in other microcomputer systems.

All the information necessary to install, use and fix the system is included here. But the book is not a maintenance and repair manual. It is principally a guide for those concerned with the system's hardware aspects. Because the INTELLEC® 4 is basically a design aid, its users will include system designers, who use the INTELLEC® system in the modeling and development of their own specialized microcomputer systems. Others who will refer to this book are designers who use individual INTELLEC® modules in other system applications. It is reasonable to assume that users in these categories will not be disadvantaged by the lack of step-by-step procedures.

This manual contains twelve chapters. Chapter 1, which follows this introduction, describes the functional operation of the INTELLEC®4/MOD 40, at the system level. Chapters 2 through 11 describe the operation and utilization of each of the individual modules. Chapter 12 discusses installation and interfacing.

Appendix A at the rear of this manual contains a summary of the instruction set used to program the

INTELLEC® 4/MOD 40 system. Appendix C summarizes activity on the system's main data bus, during the execution of each program instruction.

This manual also contains a number of schematic diagrams, to facilitate the discussion of individual INTELLEC modules. These drawings are provided for convenient reference, but may not reflect the latest engineering changes. The drawing package furnished with the instrument itself is the final authority for such changes.

### GENERAL DESCRIPTION OF THE INTELLEC® 4 SYSTEM

#### **Capabilities**

The INTELLEC® 4/MOD 40 is a general purpose, stored program, digital computer, which uses components of Intel's MCS-40<sup>TM</sup>microcomputer set. Its general purpose configuration permits it to simulate dedicated, stored program, digital computers, which use components of the MCS-40 microcomputer set. It is thus a design and development aid.

The heart of the MCS-40 set is the Intel 4040 Central Processing Unit, a monolithic MOS chip that performs all the functions normally associated with the arithmetic and control units of larger machines. This chip functions as a four-bit parallel processor, in conjunction with several specialized memory and I/O components.

Two kinds of memory components are used in MCS-40 microcomputers. We distinguish between the program memory, or that used for the storage of instructions, and read/write memory, that used for the storage of intermediate results. This distinction may seem strange at first to those accustomed to working with large-scale equipment.

Processors that work under the supervision of an operator generally use the same memory bank, both for

the storage of the program and for the storage of results. The processor may write anywhere in memory, with indifference, or even alter its own instructions. Microprocessors, on the other hand, often work in control applications, with no supervision whatever. Since there is no one present to correct obvious blunders, their programs must be foolproof. Program memory must be invariable under all circumstances; that is, firm.

But processors that handle any appreciable volume of data also need memory for the storage of intermediates. The processor's internal registers simply cannot cope with any realistic flow of data, without some help. Thus, a true read/write memory is also a necessity.

It should be obvious that these two requirements are mutually inconsistent. Memory which is firm cannot receive data from the processor, and read/write memory cannot be invariably constant. To meet these differing needs, two kinds of memory are included in the basic MCS-40™set.

The 4001 256 × 8 Bit Read Only Memory and Four-Bit Input/Output Port is the basic program memory element in systems designed around the MCS-40™ set. It stores eight-bit instructions and is programmed in manufacture, to user specifications. The specifications include not only the data contents of the memory, but also the use of each of the four I/O lines (input or output). Mask programming in manufacture further establishes the chip's addressable identity, as one element in a bank containing as many as sixteen 4001s. Program memory requirements can also be satisfied by 4308 Read Only Memory elements. The 4308 element is functionally identical to four 4001 chips. It provides 1024 × 8 bits of program storage and sixteen I/O lines (four ports of four lines each). Like the 4001, the 4308 is mask programmed in manufacture, to user specifications.

The 4002 320  $\times$  4 Bit Random Access Memory and Four-Bit Output Port is the basic read/write memory element in the MCS-40. It is a true working memory, organized to store four-bit words, and to retrieve them upon command from the processor. Like the 4001, the 4002 is a dual purpose component designed to perform both memory and I/O functions. Its addressable four-line port, however, is used exclusively for output. The chip is mask-programmed, to specify its identity, but this programming is much less comprehensive than that which the 4001 receives. Only two variations exist. The two kinds of RAM elements are designated 4002-1 or 4002-2, to distinguish them from one another. Chapter 2 of this manual explains in detail how the processor identifies and addgresses these memories.

The 4001, 4308 and the 4002 all contain a good deal of control logic, which enables them to perform their respective functions with a minimum of direct processor control. They are thus economical and versatile components, when used for the mass production of OEM microcomputers. The production virtues of the ROM, however, make it something of a liability during the development phases of a project. Program memory, by

virtue of its design, cannot be read by its own processor for purposes of output. This makes it difficult to "dump" the contents, for examination by the programmer. Moreover, the re-programming of a segment committed to ROM involves re-ordering of elements from the factory, and that often entails unacceptable delays. To circumvent these difficulties, and to facilitate the development of OEM systems, the INTELLEC®4 was introduced. The next section describes the special features of the INTELLEC®4 system that enable it to serve as a development aid.

In addition to the 4040 processor, which recognizes and responds to 60 program instructions, the system contains 1K X 8 bits of basic program memory and 320 X 4 bits of working storage. It also contains a special 4K X 8 RAM memory, described in the next section, and provision for up to 4K X 8 bits of programmable read-only memory (PROM), a special purpose program memory. Three 4-line input ports and eight 4-line output ports are provided. The standard system is expandable to accommodate up to 2560 X 4 bits of read/write memory, 16 input ports, and 48 output ports. These figures, however, reflect only the limits inherent in the system's basic addressing structure. If the user is willing to provide a modest amount of additional decoding logic, even greater expansion is feasible. The flexible, general purpose design of the IN-TELLEC® 4 system thus permits bench simulation of almost any conceivable OEM configuration.

#### Special Features

The INTELLEC® 4/MOD 40 contains provisions that simplify and expedite the development process.

The 1K X 8 program memory of the standard system is occupied by the firmware instructions of the INTELLEC® 4/MOD 40 System Monitor, a general-purpose program designed expressly to simplify and speed the process of developing specialized, application-oriented programs. Additional memory must therefore be provided in which to store the instructions of the program actually being developed and tested. For that purpose, the system's 1K X 8 program memory is augmented by a 4K X 8 memory of special design, based on the use of 2102 RAM memory components and known as program RAM. (Program RAM is used solely for program storage and should not be confused functionally with the 4002 data RAM memory described previously.) This memory is arranged to simulate the operation of 4001 program memory, but with an important exception. Special instruction sequences permit the operator to read and alter the contents of program RAM, using the standard system software.

Moreover, the INTELLEC® 4/MOD 40 system incorporates a Control and Display Panel which not only performs the routine functions of power control and RESET, but also monitors the contents of any selected location in program RAM. The operator can alter the contents of that location simply and quickly, using switches on the panel. This mode of operation is known as console memory access (CMA).

Still another feature of the panel is the search and display function. In the search mode, the operator presets the panel controls to a given address in program memory. He also presets a specific number of passes of that location, as desired. The console display will latch and hold the information on the internal main data bus during the entire cycle in which the specified number of passes of the specified address occurs. This information, including the program address, the instruction stored there, and any data in or out of the processor, can be inspected by the operator at leisure.

In addition, the INTELLEC® 4/MOD 40 system contains a built-in teletype interface, enabling direct communication through a Model ASR 33 teletype set. With the minor modifications described in Chapter 12 the teletype set can function as operator's console, paper tape reader, paper tape punch, and listing device. A convenient point of interface is thereby established for the testing and debugging of programs.

#### System Software

The foregoing provisions furnish very powerful and effective programming, debugging, and development aids. They are supported by a versatile software package, included with the standard system.

The System Monitor is a firmware program which is built right into the system's Central Processor Module. It is selectable by means of a switch on the Control and Display Panel. It contains a teletype I/O routine, and service routines which permit:

- a) Loading program RAM from paper tape

- b) Dumping the contents of program RAM

- c) Modification of individual RAM instructions

- d) Writing program RAM onto paper tape

- e) Programming of Programmable Read Only Memory (PROM)

Refer to the INTELLEC® 4/MOD 40 Operator's Manual for a full description of the System Monitor and its capabilities.

The software package includes an Assembler, furnished on perforated tape, which permits the rapid and convenient assembly of object level programs. The INTELLEC® 4 Assembler is a three-pass assembler. That is, the user's source program must be read three times in order to produce an object program tape on a listing of the assembly. During the first pass, the assembler collects information from the source program and builds internal tables, but produces no output. During the second pass, a listing of the assembled program including any errors detected is printed. During the third pass, an object program tape in the form of a hexadecimal file readable by the Monitor is produced on the Teletype paper tape punch. Once the first pass has been completed, the second and third passes may be done in any order, or either may be omitted. Use of the Assembler

consists of the following steps:

- The teletype console, in the off-line mode, is used to prepare a paper tape containing the entire assembly language listing of the program.

- 2) With the teletype (or high-speed paper tape reader) on-line, and with the System Monitor selected, the tape containing the Assembler program is run through the teletype's (or the high-speed) tape reader. This loads the Assembler into program RAM.

- The program RAM memory is selected, using the console RAM switch.

- 4) The tape containing the assembly language listing is run through the tape reader (teletype or highspeed) for the first pass.

- 5) The assembly language listing is run through the reader again. The user can specify pass 2, which will produce a listing of the assembled program, or can specify pass 3, which will produce an object program tape. Once the first pass is completed, the second and third passes may be done in any order, or either may be omitted.

- 6) If pass 3 has been executed (i.e., if an object tape has been punched), the System Monitor is again selected, using the console switch, and the object tape is run through the reader to be loaded into program RAM.

- 7) Program RAM is again selected, and execution may begin.

This procedure eliminates entirely the laborious and time-consuming process of translating instructions into binary machine code by hand. Because it is much easier for a programmer to remember and use mnemonic words like HLT (for "halt") than it is to remember and write the equivalent machine code (00000001) a great deal of time and expense are saved in the course of programming the system.

#### **Programmable Read Only Memory**

The INTELLEC® 4/MOD 40 system has provision for another kind of memory, intermediate between program RAM and 4001 or 4308 ROM. This is the 4702A Programmable Read Only Memory, known as PROM.

The 4702A is a 256  $\times$  8 bit read only memory, but one considerably different from the 4001 ROM. The most significant difference is that the 4702A may be programmed by the user, with higher-than-usual current pulses from an electronically controlled power supply. Moreover, the PROM is erasable, by deliberate exposure to a threshold ultraviolet level, permitting it to be erased and reprogrammed as often as desired.

The 4702A PROM thus has obvious advantages over the 4001 or 4308 ROM, as a vehicle of program development. This suggests the possibility of a substitution, using the

4702A to simulate the 4001 or 4308. Unfortunately, the PROM has neither the internal control logic nor the I/O provisions contained in the 4001 and 4308 ROM.

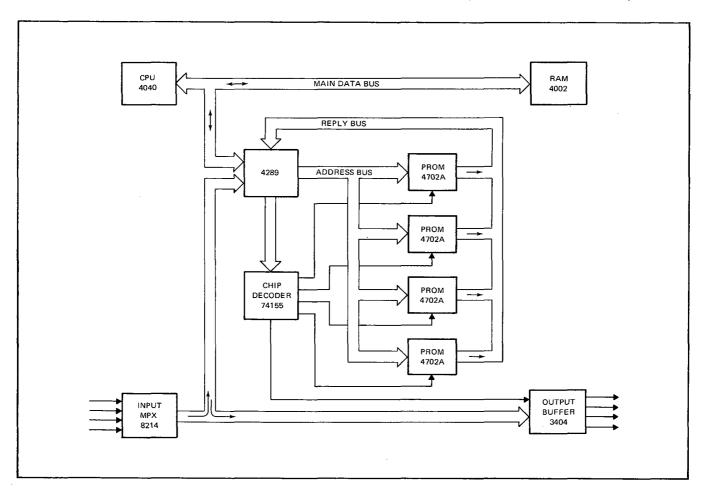

A special logic element, the 4289 Standard Memory Interface, permits the simulation of ROM, using PROM. This element is incorporated into the Central Processor Module of the INTELLEC®4/MOD 40 system.

The standard system has no user-programmed PROMs. Four factory-programmed PROMs, however, are used to contain the System Monitor. These are mounted in sockets on the Central Processor Module. Under certain circumstances, the user may wish to replace them with PROMs of his own choice. That is perfectly feasible.

Optional modules are available, however, to implement an extended PROM memory capacity. Up to 4K X 8 bits may be accommodated, with no modifications required. The modules simply plug in, and the PROM program memory is switch-selected at the control panel.

A PROM Programmer Module is also provided, giving the user complete PROM programming capability. The System Monitor contains a routine which permits the automatic transfer of information from program RAM to non-volatile, firmware storage in PROM. Thus, still another dimension of flexibility is added to the INTELLEC \*4/MOD 40 system.

#### **Developing An OEM System**

Given the convenience features built into the INTELLEC® 4/MOD 40 system; it is easy to visualize a straightforward, fast, and inexpensive procedure for developing specialized MCS-40™microcomputer systems. Steps in development will include:

- a) the design and construction of interfaces;

- b) the writing of an assembly language program;

- c) assembly of the program, using system software;

- d) preliminary testing and de-bugging of the system, using system software;

- e) commission of the program to semi-permanent storage in PROM, using the system software;

- f) final checkout of the system;

- g) transfer of the program to paper tape, automatically formatted by the system software for 4001 or 4308 ROMs from Intel.

With the advent of the INTELLEC® 4 system, the most formidable obstacles of OEM microcomputer development have been removed. Once the program is firm, it becomes a relatively routine matter of preparing the printed circuit artwork and ordering components for the production of a tailor-made microcomputer system.

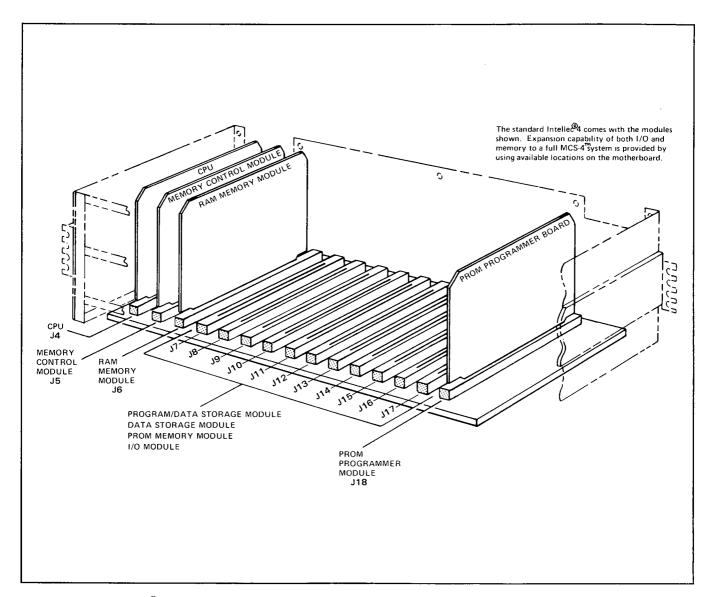

#### The Physical System

The hardware of the INTELLEC® 4/MOD 40 system is based on a mainframe assembly which consists of a chassis, a mother board and power supplies furnishing +5 Volts,

-10 Volts and +80 Volts DC (for PROM programming). The standard system includes the Control and Display Panel, and four plug-in modules:

- a) the Central Processor Module;

- b) the Control Module;

- c) the RAM Memory Module;

- d) the PROM Programmer Module.

The Central Processor Module is essentially a self-contained computer on a card, with processor, memory, and I/O provisions included. The RAM Memory Module contains the program RAM. The Control Module interfaces between the two. The PROM Programmer Module enables programming of 4702 PROMs.

The standard INTELLEC® 4/MOD 40 system includes a furnished cabinet enclosure, with cooling fan.

Expansion of the system's basic capability is accomplished through the addition of plug-in modules. The available modules include:

- a) the Data Storage Module;

- b) the Input/Output Module;

- c) the PROM Memory Module;

- d) the Instruction/Data Storage Module;

- e) the Universal Prototype Module;

- f) the Module Extender;

- g) drawer slides and extenders for rack mounting.

### MODULAR COMPONENTS OF THE INTELLEC® 4/MOD 40 SYSTEM